Integrated On-Chip Transformers: Recent Progress in the Design, Layout, Modeling and Fabrication

Abstract

1. Introduction

2. Figures-of-Merit for On-Chip Transformers

2.1. Q-Factor of Primary and Secondary Coil, Q

2.2. Coupling Coefficient, k

2.3. Self-Resonance Frequency (fSR)

2.4. Power Gain (G)

2.5. Transformer’s Characteristic Resistance (TCR)

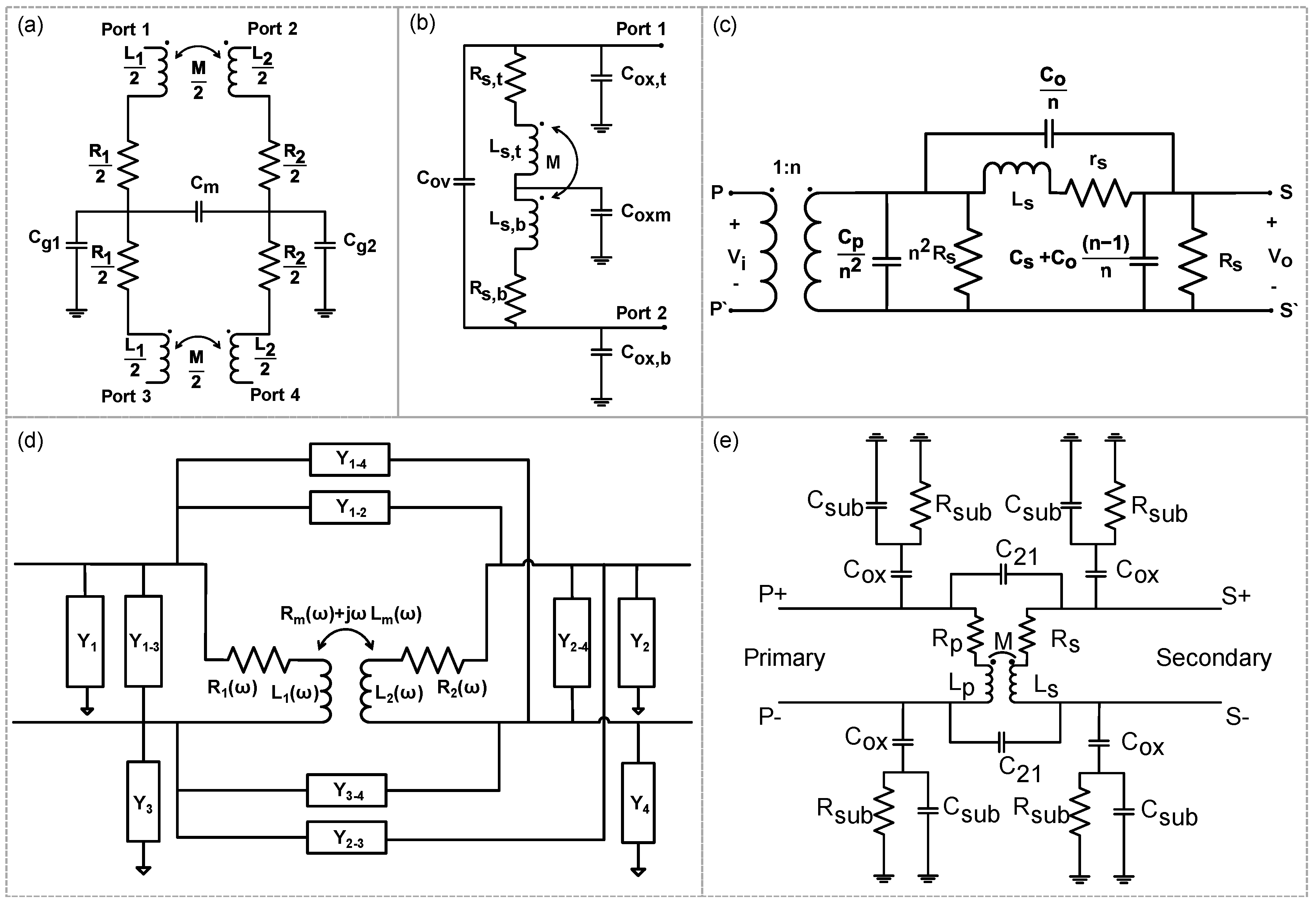

3. Modeling and Characterization of On-Chip Transformers

4. On-Chip Transformers Based on Standard IC Process Flow

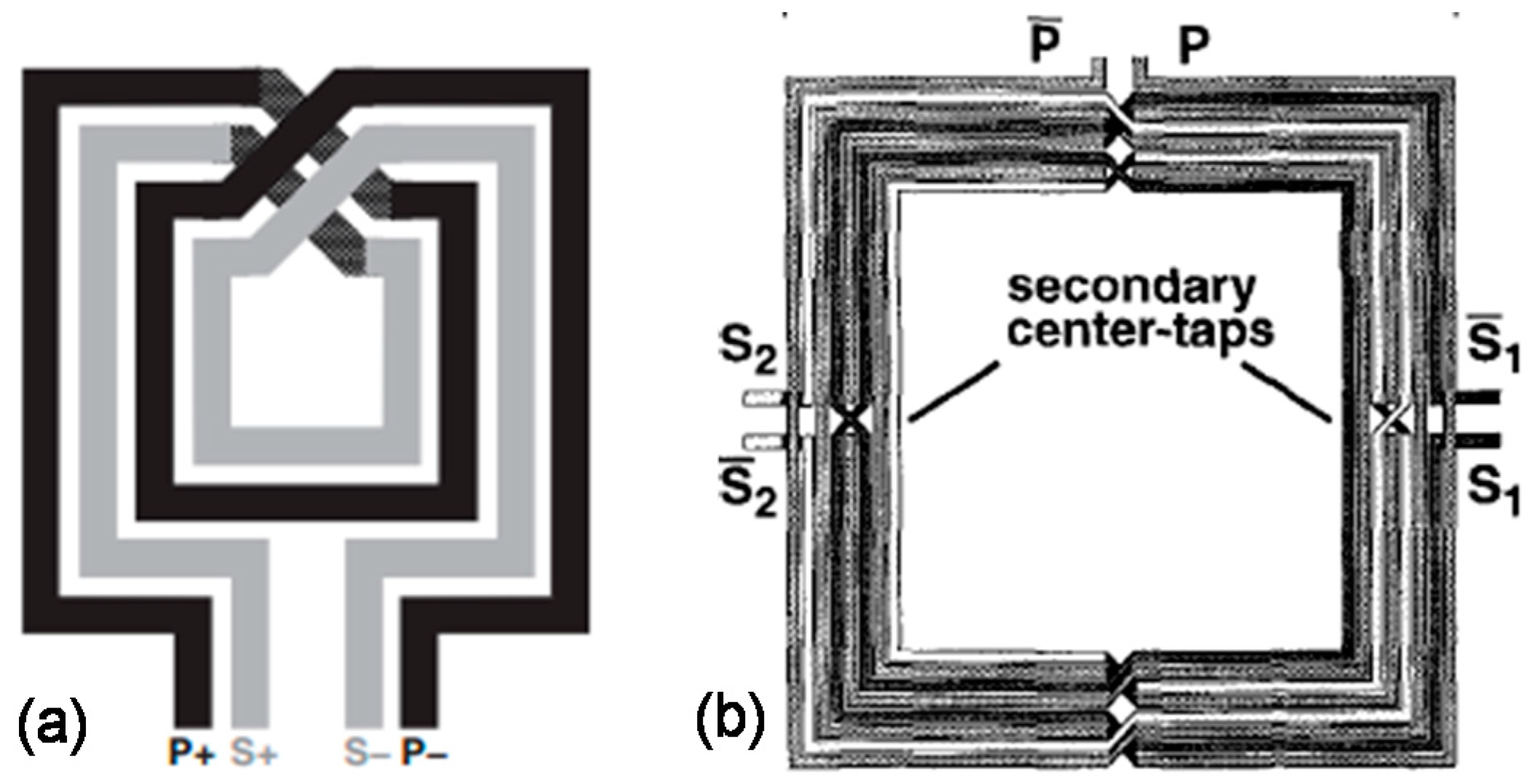

4.1. Spiral Interleaved Layout

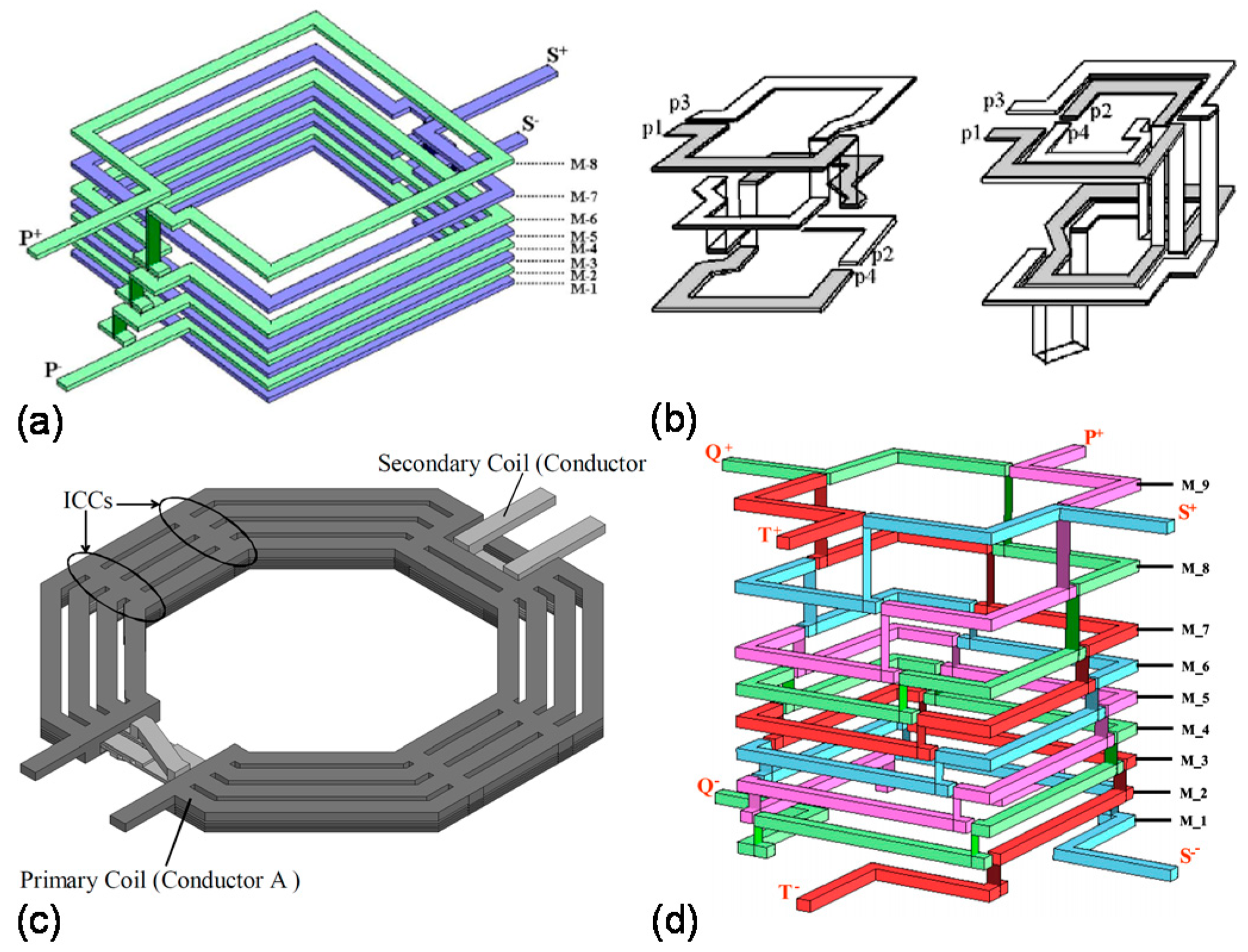

4.2. Stacked Layout

5. Design Strategies and MEMS Process Flows to Improve On-Chip Transformer Performance

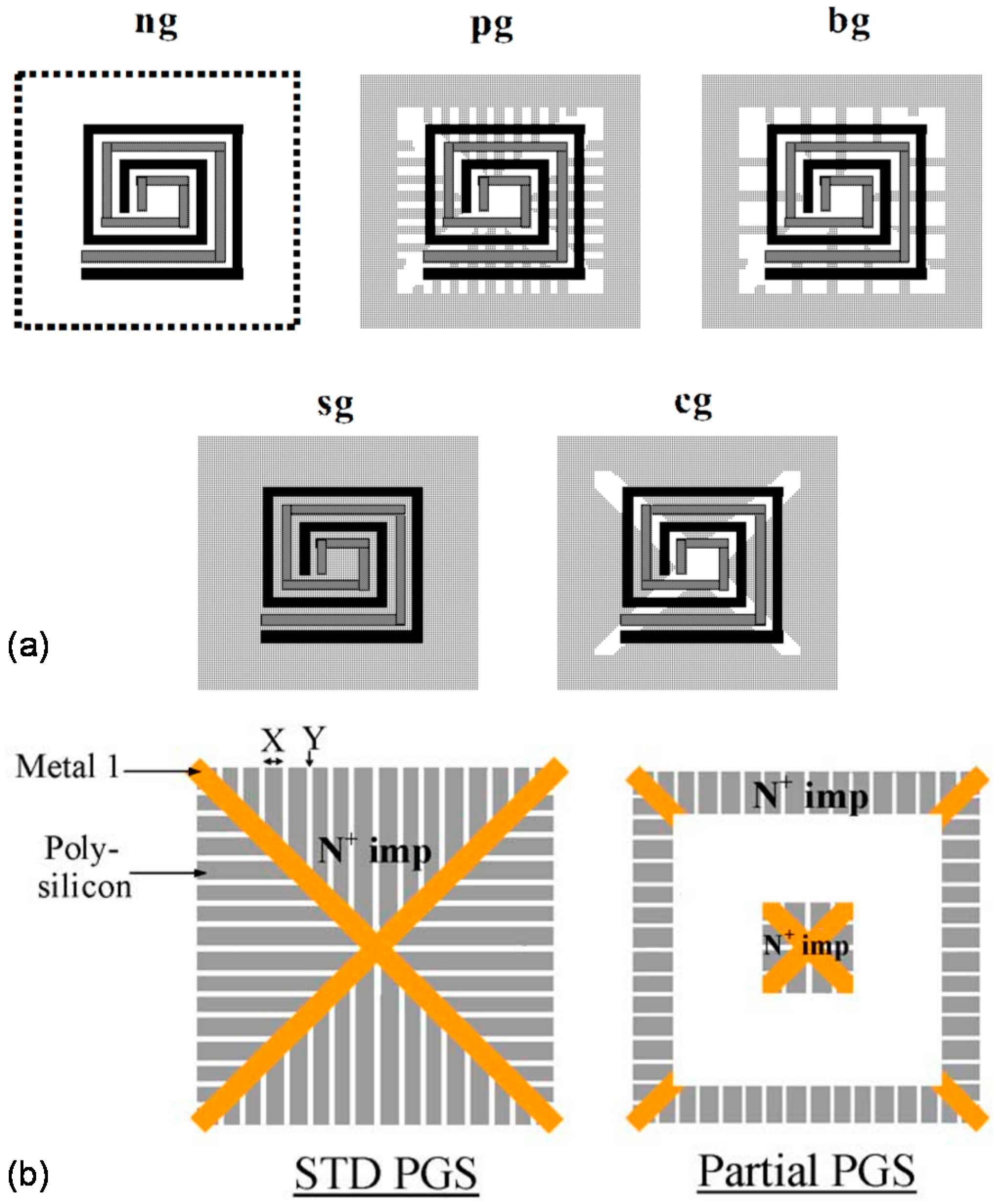

5.1. Patterned Ground Shield (PGS)

5.2. MEMS Processes and Post-IC Integration Techniques

5.3. On-Chip Transformers with Integrated Magnetic Cores

6. Applications of On-Chip Transformers

6.1. Balun

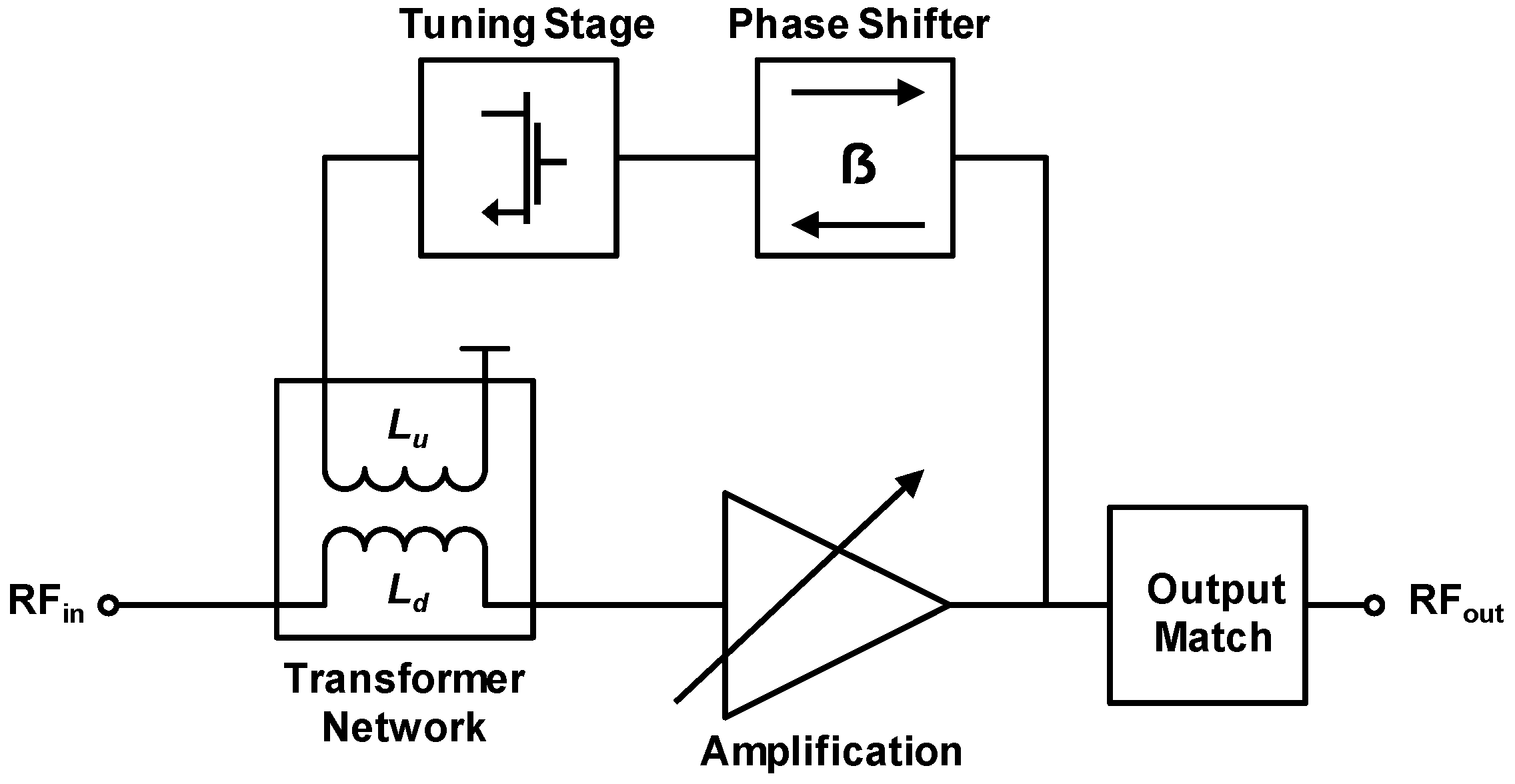

6.2. Low Noise Amplifier (LNA)

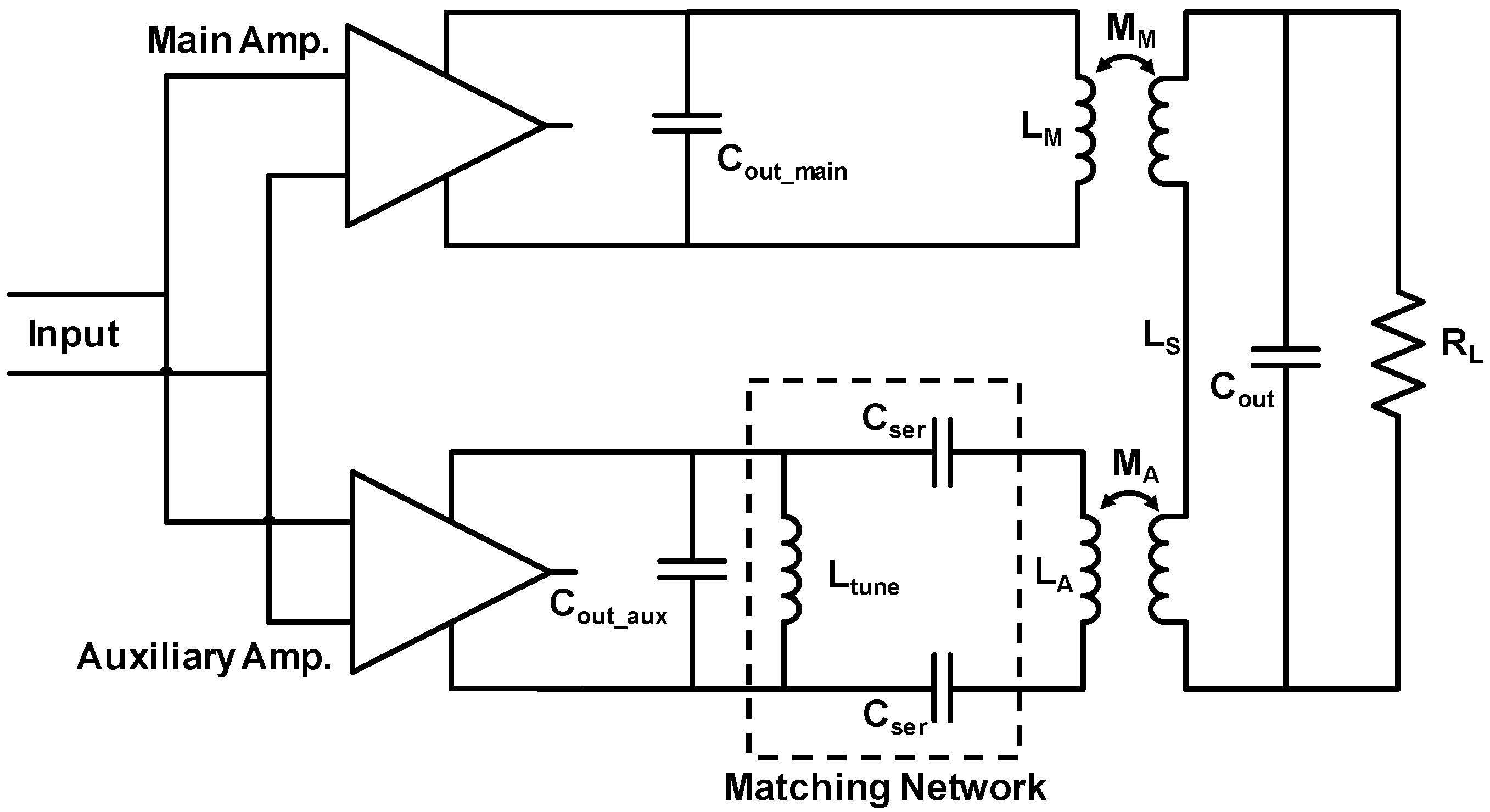

6.3. Power Amplifier (PA)

6.4. Voltage-Controlled Oscillator (VCO)

7. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Kihara, T.; Matsuda, S.; Yoshimura, T. Analysis and Design of Differential LNAs with On-Chip Transformers in 65-nm CMOS Technology. In Proceedings of the 2016 14th IEEE International New Circuits and Systems Conference (NEWCAS), Vancouver, BC, Canada, 26–29 June 2016; pp. 1–4. [Google Scholar]

- Zhou, J.J.; Allstot, D.J. Monolithic Transformers and Their Application in a Differential CMOS RF Low-Noise Amplifier. IEEE J. Solid State Circuits 1998, 33, 2020–2027. [Google Scholar] [CrossRef]

- Ko, S.; Kim, J.G.; Song, T.; Yoon, E.; Hong, S. K- and Q-Bands CMOS Frequency Sources With X-Band Quadrature VCO. IEEE Trans. Microw. Theory Tech. 2005, 53, 2789–2799. [Google Scholar]

- Cheung, T.S.; Long, J.R.; Hadaway, R.A.; Harame, D.L. Monolithic Transformers for Silicon RF IC Design. In Proceedings of the Bipolar/Bicmos Circuits and Technology Meeting, Minneapolis, MN, USA, 27–29 September 1998; pp. 105–108. [Google Scholar]

- Issaa, H.; Ghayyib, S.M.; Ezzulddin, A.S. Toward a fully integrated 2.4 GHz differential pair class-E power amplifier using on-chip RF power transformers for Bluetooth systems. AEU Int. J. Electron. Commun. 2015, 69, 182–187. [Google Scholar] [CrossRef]

- Dickson, T.; LaCroix, M.; Boret, S.; Gloria, D.; Beerkens, R.; Voinigescu, S.P. Si-based inductors and transformers for 30–100 GHz applications. In Proceedings of the IEEE MTT-S International Microwave Symposium Digest, Fort Worth, TX, USA, 6–11 June 2004; pp. 205–208. [Google Scholar]

- Huang, C.; Chen, C. Characterization of CMOS on-chip transformer for digital transmission line driver applications. In Proceedings of the 2013 Asia-Pacific Symposium on Electromagnetic Compatibility (APEMC), Melbourne, Australia, 20–23 May 2013; pp. 1–4. [Google Scholar]

- Gohma, S.; Langat, K. On-chip 60 GHz transformers for next generation of wireless communication in a 0.13μ BiCMOS technology. In Proceedings of the Conference on Information Communications Technology and Society (ICTAS), Durban, South Africa, 8–9 March 2018; pp. 1–4. [Google Scholar]

- Jian, F.; Niansong, M.; Yumei, H.; Zhiliang, H. CMOS high linearity PA driver with an on-chip transformer for W-CDMA application. J. Semicond. 2011, 32, 1–6. [Google Scholar]

- Chen, B. Fully Integrated Isolated DC-DC Converter Using Micro-Transformers. In Proceedings of the Twenty-Third Annual IEEE Applied Power Electronics Conference and Exposition, Austin, TX, USA, 24–28 February 2008; pp. 335–338. [Google Scholar]

- Wu, R.; Liao, N.; Fang, X.; Sin, J.K.O. A Silicon-Embedded Transformer for High-Efficiency, High-Isolation, and Low-Frequency On-Chip Power Transfer. IEEE Trans. Electron. Devices 2015, 62, 220–223. [Google Scholar] [CrossRef]

- Kim, K.J.; Lim, T.H.; Ahn, K.H. The Novel High Efficiency on Chip Transformers for the CMOS Power Amplifier. In Proceedings of the 12th International Symposium on Integrated Circuits, Singapore, 14–16 December 2009; pp. 401–404. [Google Scholar]

- Ercoli, M.; Dragomirescu, D.; Plana, R. Reduced size high performance transformer balun at 60 GHz in CMOS 65nm Technology. Microelectron. J. 2012, 43, 737–744. [Google Scholar] [CrossRef]

- Wu, Z.; Wang, X.; Yin, W.Y.; Li, X. Three-solenoid windings transformer baluns on CMOS-grade silicon substrate. Microelectron. Eng. 2010, 87, 150–158. [Google Scholar] [CrossRef]

- Frlan, E.; Meszaros, S.; Cuhaci, M.; Wight, J.S. Computer Aided Design of Square Spiral Transformers and Inductors. In Proceedings of the IEEE MTT-S International Microwave Symposium Digest, Long Beach, CA, USA, 13–15 June 1989; pp. 661–664. [Google Scholar]

- Boulouard, A.; Rouzic, M.L. Analysis of Rectangular Spiral Transformers for MMIC applications. IEEE Trans. Microw. Theory Tech. 1989, 37, 1257–1260. [Google Scholar] [CrossRef]

- Long, J.R. Monolithic Transformers for Silicon RF IC Design. IEEE J. Solid State Circuits 2000, 35, 1368–1382. [Google Scholar] [CrossRef]

- Mohan, S.; Yue, C.P.; Hershenson, M.D.M.; Wong, S.S.; Lee, T.H. Modeling and Characterization of On-Chip Transformers. In Proceedings of the International Electron Devices Meeting 1998. Technical Digest, San Francisco, CA, USA, 6–9 December 1998; pp. 531–534. [Google Scholar]

- Zhou, J.J.; Allstot, D.J. A Fully Integrated CMOS 900MHz LNA utilizing Monolithic Transformers. In Proceedings of the 1998 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, ISSCC. First Edition, San Francisco, CA, USA, 5–7 February 1998; pp. 132–133. [Google Scholar]

- Ng, K.T.; Rejaei, B.; Burghartz, J.N. Substrate Effects in Monolithic RF Transformers on Silicon. IEEE Trans. Microw. Theory Technol. 2002, 50, 377–383. [Google Scholar] [CrossRef]

- Hsu, H. Implementation of High-Coupling and Broadband transformer in RFCMOS. IEEE Trans. Electron. Devices 2005, 52, 1410–1414. [Google Scholar] [CrossRef]

- Hsu, H.; Chen, K. High Turn Ratio and High Coupling Coefficient transfomer 90nm cmos. IEEE Electron Device Lett. 2009, 30, 535–537. [Google Scholar]

- Hsu, H.; Chien, C. Multiple Turn Ratios of On-Chip Transformer With Four Intertwining Coils. IEEE Trans. Electron. Devices 2014, 61, 44–47. [Google Scholar] [CrossRef]

- Hsu, H.; Huang, J.; Peng, T.; Liu, N. Design of Coil Length of On-Chip Transformer With High Turn Ratio and High Coupling Performance. IEEE Trans. Electron. Devices 2012, 59, 3061–3068. [Google Scholar]

- Hsu, H.; Lai, S.; Hsu, C. Compact Layout of On-Chip Transformer. IEEE Trans. Electron. Devices 2010, 57, 1076–1083. [Google Scholar] [CrossRef]

- Khan, F.; Zhu, Y.; Lu, J.; Pal, J. A novel single metal layer MEMS-based step-down transformer. Microelectron. J. 2016, 57, 48–51. [Google Scholar] [CrossRef]

- Katz, S.; Brouk, I.; Stolyarova, S.; Shapira, S.; Nemirovsky, Y. High performance MEMS 0.18 mm RF-CMOS transformers. Microelectron. J. 2012, 43, 13–16. [Google Scholar] [CrossRef]

- Choi, Y.; Yoon, J.; Kim, B.; Yoon, E. A High-Performance MEMS Transformer for Silicon RF ICS. In Proceedings of the Technical Digest. MEMS 2002 IEEE International Conference. Fifteenth IEEE International Conference on Micro Electro Mechanical Systems, Las Vegas, NV, USA, 24 January 2002; pp. 653–656. [Google Scholar]

- Ribas, R.P.; Lescot, J.; Leclercq, J.L.; Karam, J.M.; Ndagijimana, F. Micromachined Microwave Planar Spiral Inductors and Transformers. IEEE Trans. Microw. Theory Tech. 2000, 48, 1326–1335. [Google Scholar] [CrossRef]

- Hsu, H.; Tseng, C.; Chan, K. Characterization of On-Chip Transformer Using Microwave Technique. IEEE Trans. Electron. Devices 2008, 55, 833–837. [Google Scholar] [CrossRef]

- Lin, Y.; Chen, C.; Liang, H.; Tsai, P.; Chen, C.; Chang, J.; Wang, T.; Lu, S. A High-Performance Micromachined RF Monolithic Transformer With Optimized Pattern Ground Shields (OPGS) for UWB RFIC Applications. IEEE Trans. Electron. Devices 2007, 54, 609–613. [Google Scholar] [CrossRef]

- Gu, L.; Li, X. On-chip embedded toroidal solenoid inductors and transformers formed by post-CMOS micromachining techniques. Microelectron. Eng. 2008, 85, 697–703. [Google Scholar] [CrossRef]

- Hikmat, O.F.; Ali, M.S.M. RF MEMS Inductors and Their Applications—A Review. J. Microelectromech. Syst. 2017, 26, 17–43. [Google Scholar] [CrossRef]

- Yunas, J.; Hamzah, A.A.; Majlis, B.Y. Surface micromachined on-chip transformer fabricated on glass substrate. Microsyst. Technol. 2009, 15, 547–552. [Google Scholar] [CrossRef]

- Ng, K.T.; Rejaei, B.; Burghartz, J.N. Ground Pattern for Improved Characteristics of Spiral RF Transformers on Silicon. In Proceedings of the 2001 Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, Ann Arbor, MI, USA, 14 September 2001; pp. 75–78. [Google Scholar]

- Chong, K.; Xie, Y. High-Performance On-Chip Transformers. IEEE Electron Device Lett. 2005, 26, 557–559. [Google Scholar] [CrossRef]

- Wu, R.; Sin, J.K.O.; Hui, S.Y. Novel Silicon-Embedded Coreless Transformer for On-Chip Isolated Signal Transfer. IEEE Magn. Lett. 2011, 2, 6500103. [Google Scholar]

- Mayevskiy, Y.; Watson, A.; Francis, P.; Hwang, K.; Weisshaar, A. A New Compact Model for Monolithic Transformers in Silicon-Based RFICs. IEEE Microw. Wirel. Compon. Lett. 2005, 15, 419–421. [Google Scholar] [CrossRef]

- Carrara, F.; Italia, A.; Ragonese, E.; Palmisano, G. Design Methodology for the Optimization of Transformer-Loaded RF Circuits. IEEE Trans. Circuits Syst. I Regul. Pap. 2006, 53, 761–768. [Google Scholar] [CrossRef]

- Niknejad, M.; Meyer, R.G. Analysis of Eddy-Current Losses Over Conductive Substrates with Applications to Monolithic Inductors and Transformers. IEEE Trans. Microw. Theory Technol. 2001, 49, 166–176. [Google Scholar] [CrossRef]

- Valkodai, A.; Manku, T. Modeling and designing silicon thin-film inductors and transformers using HSPICE for RFIC applications. Integr. VLSI J. 1997, 24, 159–171. [Google Scholar] [CrossRef]

- Greenhouse, H. Design of Planar Rectangular Microelectronic Inductors. IEEE Trans. Parts Hybrids Packag. 1974, 10, 101–109. [Google Scholar] [CrossRef]

- Hsu, H.; Tseng, C.; Liao, H. Analysis on the mutual inductance of planar transformer in CMOS Technology. Microelectron. Eng. 2008, 85, 227–232. [Google Scholar] [CrossRef]

- El-Gharniti, O.; Kerherve, E.; Begueret, J. Modeling and Characterization of On-Chip Transformers for Silicon RFIC. IEEE Trans. Microw. Theory Tech. 2007, 55, 607–615. [Google Scholar] [CrossRef]

- Yue, P.; Wong, S.S. On-Chip Spiral Inductors with Patterned Ground Shields for Si-Based RF IC’s. IEEE J. Solid State Circuits 1998, 33, 743–752. [Google Scholar] [CrossRef]

- Hsu, H. Analytical Formula for Inductance of Metal of Various Widths in Spiral Inductors. IEEE Trans. Electron. Devices 2004, 51, 1343–1346. [Google Scholar] [CrossRef]

- Hsu, H.; Lai, S.; Chen, M.; Liao, H. Investigation on the Mutual Inductance of On-Chip Transformers. In Proceedings of the 2012 2nd IEEE CPMT Symposium Japan, Kyoto, Japan, 10–12 December 2012; pp. 1–4. [Google Scholar]

- Tsui, C.; Tong, K.Y. Modelling of multilayer on-chip transformers. IEEE Proc. Microw. Antennas Propag. 2006, 153, 483–486. [Google Scholar] [CrossRef]

- Hasaneen, M. Modeling of On-Chip Inductor and Transformer for RF Integrated Circuits. In Proceedings of the 2006 Eleventh International Middle East Power Systems Conference, El-Minia, Egypt, 19–21 December 2006; pp. 65–69. [Google Scholar]

- Tiemeijer, L.F.; Pijper, R.M.T.; Andrei, C.; Grenados, E. Analysis, Design, Modeling, and Characterization of Low-Loss Scalable On-Chip Transformers. IEEE Trans. Microw. Theory Tech. 2013, 61, 2545–2557. [Google Scholar] [CrossRef]

- Liao, H.; Wang, C. A New Approach to Parameter Extraction for On-Chip Symmetric Transformers. In Proceedings of the IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Singapore, 9 January–11 December 2009; pp. 257–260. [Google Scholar]

- Klemens, G.; Bhagat, M.; Jessie, D.; Fredenick, N. Analysis and circuit modeling of on-chip transformers. In Proceedings of the Topical Meeting onSilicon Monolithic Integrated Circuits in RF Systems, Atlanta, GA, USA, 8–10 September 2004; pp. 167–170. [Google Scholar]

- Lin, L.; Yin, W.; Mao, J.; Yang, K. Performance Characterization of Circular Silicon Transformers. IEEE Trans. Magn. 2008, 44, 4684–4688. [Google Scholar]

- Wang, C.; Liao, H.; Xiong, Y.; Li, C.; Huang, R.; Wang, Y. A Physics-Based Equivalent-Circuit Model for On-Chip Symmetric Transformers With Accurate Substrate Modeling. IEEE Trans. Microw. Theory Tech. 2009, 57, 980–990. [Google Scholar] [CrossRef]

- Liu, J.; Sun, L.; Yu, Z. An Accurate Compact Model for On-Chip Vertically Coiled Transformers. IEEE Electron. Device Lett. 2013, 34, 484–486. [Google Scholar] [CrossRef]

- Wei, J.; Wang, Z.; Li, Z.; Tang, L. A new equivalent circuit model for on-chip spiral transformers in CMOS RFICs. J. Semicond. 2012, 33, 1–5. [Google Scholar] [CrossRef]

- Dickson, T.O.; LaCroix, M.A.; Boret, S.; Gloria, D.; Beerkens, R.; Voinigescu, S.P. 30–100-GHz Inductors and Transformers for Millimeter-Wave (Bi)CMOS Integrated Circuits. IEEE Trans. Microw. Theory Tech. 2005, 53, 123–133. [Google Scholar] [CrossRef]

- Chowdhury, D.; Reynaert, P.; Niknejad, A.M. Design Considerations for 60 GHz Transformer-Coupled CMOS Power Amplifiers. IEEE J. Solid State Circuits 2009, 44, 2733–2744. [Google Scholar] [CrossRef]

- Leite, B.; Kerherve, E.; Begueret, J.; Belot, D. An Analytical Broadband Model for Millimeter-Wave Transformers in Silicon Technologies. IEEE Trans. Electron. Devices 2012, 59, 582–589. [Google Scholar] [CrossRef]

- Hou, D.; Hong, W.; Goh, W.L.; Xiong, Y.Z.; Arasu, M.A.; He, J.; Chen, J.; Madihian, M. Distributed Modeling of Six-Port Transformer for Millimeter-Wave SiGe BiCMOS Circuits Design. IEEE Trans. Microw. Theory Tech. 2012, 60, 3728–3738. [Google Scholar] [CrossRef]

- Gao, Z.; Kang, K.; Zhao, C.; Wu, Y.; Ban, Y.; Sun, L.; Hong, W.; Xue, Q. A Broadband and Equivalent-Circuit Model for Millimeter-Wave On-Chip M:N Six-Port Transformers and Baluns. IEEE Trans. Microw. Theory Tech. 2015, 63, 3109–3121. [Google Scholar] [CrossRef]

- Hsu, H.; Tsai, M.; Huang, K. An on-chip transformer in silicon-based technology. J. Micromech. Microeng. 2007, 17, 1504–1510. [Google Scholar] [CrossRef]

- Luong, H.C.; Yin, J. Transformer Design and Characterization in CMOS process. In Transformer-Based Design Techniques for Oscillators and Frequency Dividers; Springer: Cham, Switzerland, 2016; pp. 7–19. [Google Scholar]

- Ren, Z.; Zhang, K.; Li, C.; Liu, Z.; Chen, X.; Liu, D.; Zou, X. On-chip Transformer Using Multipath Technique with Arithmetic-Progression Step Sub-Path Width. In Proceedings of the IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Singapore, 1–4 June 2015; pp. 597–600. [Google Scholar]

- Xu, X.; Li, P.; Cai, M.; Han, B. Design of Novel High-Q-Factor Multipath Stacked On-Chip Spiral Inductors. IEEE Trans. Electron. Devices 2012, 59, 2011–2018. [Google Scholar] [CrossRef]

- Hsu, H.; Tseng, C. Design of On-Chip Transformer With Various Coil Widths to Achieve Minimal Metal Resistance. IEEE Electron Device Lett. 2007, 28, 1029–1032. [Google Scholar] [CrossRef]

- Hsu, H.; Lai, S.; Tseng, C.; Fu, G. Layout Design of On-Chip Transformer with Uniform Variation of Coil Widths. In Proceedings of the 2009 European Microwave Conference (EuMC), Rome, Italy, 29 September–1 October 2009; pp. 1199–1202. [Google Scholar]

- Fong, N.; Plouchart, J.O.; Zamdmer, N.; Kim, J.; Jenkins, K.; Plett, C.; Tarr, G. High-Performance and Area-Efficient Stacked Transformers for RF CMOS Integrated Circuits. In Proceedings of the IEEE MTT-S International Microwave Symposium Digest, Philadelphia, PA, USA, 8–13 June 2003; pp. 967–970. [Google Scholar]

- Ghadiri, A.; Moez, K. Bandwidth Enhancement of On-Chip Transformers Using Negative Capacitance. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 648–652. [Google Scholar] [CrossRef]

- Chen, W.; Hsu, K. Miniaturized 3-Dimensional Transformer Design. In Proceedings of the IEEE 2005 Custom Integrated Circuits Conference 2005, San Jose, CA, USA, 21 September 2005; pp. 285–288. [Google Scholar]

- Lim, C.C.; Yeo, K.S.; Chew, K.W.; Lim, S.F.; Boon, C.C.; Qiu, P.; Do, M.A.; Chan, L. An Area Efficient High Turn Ratio Monolithic Transformer for Silicon RFIC. In Proceedings of the 2008 IEEE Radio Frequency Integrated Circuits Symposium, Atlanta, GA, USA, 15–17 June 2008; pp. 167–170. [Google Scholar]

- Wu, R.; Chen, J.; Liao, N.; Fang, X. On-chip transformers with shielding structures for high dV/dt immunity isolated gate drive. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–6. [Google Scholar]

- Shi, J.; Yin, W.; Kang, K.; Maom, J.; Li, L. Frequency-Thermal Characterization of On-Chip Transformers With Patterned Ground Shields. IEEE Trans. Microw. Theory Tech. 2007, 55, 1–12. [Google Scholar] [CrossRef]

- Lin, Y.; Chen, C.; Liang, H.; Chen, C. High-Performance On-Chip Transformers With Partial Polysilicon Patterned Ground Shields (PGS). IEEE Trans. Electron. Devices 2007, 54, 157–160. [Google Scholar] [CrossRef]

- Lin, Y.; Liang, H.; Wang, T.; Lu, S. An Analysis of Perfect-Magnetic-Coupling Ultra-Low-Loss Micromachined SMIS RF Transformers for RFIC Applications. In Proceedings of the IEEE Radio and Wireless Symposium, San Diego, CA, USA, 17–19 October 2006; pp. 55–58. [Google Scholar]

- Huang, W.; Zhou, J.; Froeter, P.J.; Walsh, K.; Liu, S.; Kraman, M.D.; Li, M.; Michaels, J.A.; Sievers, D.J.; Gong, S.; et al. Three-dimensional radio-frequency transformers based on a self-rolled-up membrane platform. Nat. Electron. 2018, 1, 305–313. [Google Scholar] [CrossRef]

- Yunas, J.; Majlis, B.Y. Comparative study of stack interwinding micro-transformers on Silicon Monolithic. Microelectron. J. 2008, 39, 1564–1567. [Google Scholar] [CrossRef]

- Gu, L.; Li, X. A Post-CMOS Concave-Suspending MEMS Process in Standard Silicon Wafers for High-Performance Solenoidal-DNA-Configured Micro-Transformers. In Proceedings of the International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 2006; pp. 1–4. [Google Scholar]

- Bajwa, R.; Yapici, M.K. Intrinsic stress-induced bending as a platform technology for controlled self-assembly of high-Q on-chip RF inductors. J. Micromech. Microeng. 2019, 29, 064002. [Google Scholar] [CrossRef]

- Kahlouche, F.; Youssouf, K.; Bechir, M.H.; Capraro, S.; Siblini, A.; Chatelon, J.P.; Buttay, C.; Rousseau, J.J. Fabrication and characterization of a planar interleaved micro-transformer with magnetic core. Microelectron. J. 2014, 45, 893–897. [Google Scholar] [CrossRef]

- Zhang, H.W.; Liu, Y.L.; Zhong, Z.Y. An improved microchip thin film transformer formed by vacuum evaporation and sputtering. Vacuum 2001, 62, 1–6. [Google Scholar] [CrossRef]

- Wu, H.; Lekas, M.; Davies, R.; Shepard, K.L.; Sturcken, N. Integrated Transformers With Magnetic Thin Films. IEEE Trans. Magn. 2016, 52, 1–4. [Google Scholar] [CrossRef]

- Khan, F.; Zhu, Y.; Lu, J.; Pal, J.; Dao, D.V. Micromachined Coreless Single-Layer Transformer Without Crossovers. IEEE Magn. Lett. 2015, 6, 1–4. [Google Scholar] [CrossRef]

- Wang, N.; Kulkarni, S.; Jamieson, B.; Rohan, J.; Casey, D.; Roy, S.; O’Mathuna, C. High Efficiency Si Integrated Micro-transformers Using Stacked Copper Windings for Power Conversion Applications. In Proceedings of the Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 5–9 February 2012; pp. 411–416. [Google Scholar]

- Lin, Y.; Liang, H.; Chen, C.; Wang, T.; Lu, S. A High Quality Factor and Low Power Loss Micromachined RF Bifilar Transformer for UWB RFIC Applications. IEEE Electron Device Lett. 2006, 27, 684–687. [Google Scholar]

- Dechev, N.; Mills, J.K.; Cleghorn, W.L. Mechanical Fastener Designs for use in the Microassembly of 3D Microstructures. In Proceedings of the ASME 2004 International Mechanical Engineering Congress and Exposition, Anaheim, CA, USA, 13–19 November 2004; pp. 447–456. [Google Scholar]

- Mundotiya, B.M.; Dinulovic, D.; Rissing, L.; Wurz, M.C. Fabrication and characterization of a Ni-Fe-W core microtransformer for high-Frequency power applications. Sen. Actuators A Phys. 2017, 267, 42–47. [Google Scholar] [CrossRef]

- Ahmed, M.Z.; Bhuyan, M.S.; Tariqul Islam, A.K.M.; Majlis, B.Y. Design and Fabrication of a MEMS 3D Micro-transformer for Low Frequency Applications. Asian J. Sci. Res. 2015, 8, 237–244. [Google Scholar] [CrossRef][Green Version]

- Tsai, T.H.; Kuo, L.S.; Chen, P.H.; Lee, D.S.; Yang, C.T. Applications of Ferro-Nanofluid on a Micro-Transformer. Sensors 2010, 10, 8161–8172. [Google Scholar] [CrossRef]

- Mariappan, S.G.; Moazenzadeh, A.; Wallrabe, U. Polymer Magnetic Composite Core Based Microcoils and Microtransformers for Very High Frequency Power Applications. Micromachines 2016, 7, 60. [Google Scholar] [CrossRef]

- Yapici, M.K.; Ozmetin, A.E.; Zou, J.; Naugle, D.G. Development and Experimental Characterization of Micromachined Electromagnetic Probes for Biological Manipulation and Stimulation Applications. Sen. Actuators A Phys. 2008, 144, 213–221. [Google Scholar] [CrossRef]

- Zhang, D.; Yu, H.; Kumar, T.B.; Men, K.; Lu, M.; Yu, X.; Yeo, K.S. Design of Millimeter-wave Transformer Balun with Isolation Circuit in Silicon Based Technology. In Proceedings of the International Symposium on Integrated Circuits (ISIC), Singapore, 12–14 December 2016; pp. 1–3. [Google Scholar]

- Yeh, H.C.; Chiong, C.C.; Aloui, S.; Wang, H. Analysis and Design of Millimeter-Wave Low-Voltage CMOS Cascode LNA with Magnetic Coupled Technique. IEEE Trans. Microw. Theory Tech. 2012, 60, 4066–4079. [Google Scholar] [CrossRef]

- Long, J.R.; Copeland, M.A. A 1.9 GHz Low-Voltage Silicon bipolar Receiver Front-End for Wireless Personal Communications Systems. IEEE J. Solid State Circuits 1995, 30, 1438–1448. [Google Scholar] [CrossRef]

- Aneja, A.; Li, X.J. Design and Analysis of a Continuously Tunable Low Noise Amplifier for Software Defined Radio. Sensors 2019, 19, 1273. [Google Scholar] [CrossRef]

- Brown, J.L.; Neihart, N.M. An Analytical Study of a Magnetically Tuned Matching Network. In Proceedings of the IEEE International Symposium on Circuits and Systems, Seoul, Korea, 20–23 May 2012; pp. 1979–1982. [Google Scholar]

- Simburger, W.; Wohlmuth, H.D.; Weger, P.A.; Heinz, A. Monolithic Transformer Coupled 5-W Silicon Power Amplifier with 59% PAE at 0.9 GHz. IEEE J. Solid State Circuits 1999, 34, 1881–1892. [Google Scholar] [CrossRef]

- Chowdhury, D.; Reynaert, P.; Niknejad, A.M. A 60 GHz 1V +12.3 dBm Transformer-Coupled Wideband PA in 90 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference-Digest of Technical Papers, San Francisco, CA, USA, 3–7 February 2008; pp. 560–635. [Google Scholar]

- Kaymaksut, E.; Zhao, D.; Reynaert, P. Transformer-Based Doherty Power Amplifiers for mm-Wave Applications in 40-nm CMOS. IEEE Trans. Microw. Theory Tech. 2015, 63, 1186–1192. [Google Scholar] [CrossRef]

- Lim, A.; Tan, A.; Kong, Z.H.; MA, K. A Design Methodology and Analysis for Transformer-Based Class-E Power Amplifier. Electronics 2019, 8, 494. [Google Scholar] [CrossRef]

- Vasjanov, A.; Barzdenas, V. A Review of Advanced CMOS RF Power Amplifier Architecture Trends for Low Power 5G Wireless Networks. Electronics 2018, 7, 271. [Google Scholar] [CrossRef]

- Cripps, S.C. RF Power Amplifiers for Wireless Communications, 2nd ed.; Artech House, Inc.: Norwood, MA, USA, 2006. [Google Scholar]

- Li, C.; Wang, T.; Kuo, C.; Chuang, M.; Wang, H. A 21 GHz Complementary Transformer Coupled CMOS VCO. IEEE Microw. Wirel. Compon. Lett. 2008, 18, 278–280. [Google Scholar]

- Straayer, M.; Cabanillas, J.; Rebeiz, G.M. A Low-Noise Transformer-based 1.7 GHz CMOS VCO. In Proceedings of the 2002 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 7 February 2002; pp. 286–287. [Google Scholar]

- Baek, D.; Song, T.; Yoon, E.; Hong, S. 8-GHz CMOS Quadrature VCO Using Transformer-Based LC Tank. IEEE Microw. Wirel. Compon. Lett. 2003, 13, 446–448. [Google Scholar] [CrossRef]

- Oh, N.J.; Lee, S.G. 11-GHz CMOS Differential VCO with Back-Gate Transformer Feedback. IEEE Microw. Wirel. Compon. Lett. 2005, 15, 733–735. [Google Scholar]

- Scuderi, A.; Palmisano, G. A Low-Phase-Noise Voltage-Controlled Oscillator for 17-GHz Applications. IEEE Microw. Wirel. Compon. Lett. 2006, 16, 191–193. [Google Scholar] [CrossRef]

| Turn Ratio N | QMAX | fSR (GHz) | Secondary Inductance LS (nH) | Primary Inductance LP (nH) | Mutual Inductance M (nH) | k | GMAX | Outer Dimension DOUT (µm) | |

|---|---|---|---|---|---|---|---|---|---|

| [36] | 4:5 | 9.3 | 11.4 | 3.4 | - | - | 0.7 | 0.77 | 280 |

| [36] | 4:5 | 8.3 | 15.5 | 2.9 | - | - | 0.7 | 0.74 | 196 |

| [36] | 4:5 | 3.1 | 4.5 | 3.4 | - | - | 0.7 | 0.53 | 280 |

| [36] | 4:5 | 2.22 | 5.4 | 2.9 | - | - | 0.69 | 0.46 | 196 |

| [30] | 3:2 | - | 16 | 1.42 | 2.53 | 1.25 | 0.66 | 0.79 | 202 |

| [30] | 3:2 | - | 13.6 | 1.28 | 1.45 | 1.28 | 0.66 | 0.85 | 254 |

| [4] | 5 | - | - | 9.75 | 0.39 | 1.482 | 0.76 | - | 400 |

| [64] | 3:3 | - | - | - | - | - | 0.83 | 0.575 | 367 |

| [64] | 3:3 | - | - | - | - | - | 0.90 | 0.576 | 367 |

| [66] | 4:4 | 9.86 | 9.2 | 3.96 | - | 3.02 | - | - | 142 |

| [66] | 4:4 | 8.53 | 10.4 | 3.93 | - | 3.04 | - | - | 118 |

| Turn Ratio N | QMAX | fSR (GHz) | Secondary Inductance LS (nH) | Primary Inductane LP (nH) | Mutual Inductance M (nH) | k | GMAX | Outer Dimension DOUT (µm) | |

|---|---|---|---|---|---|---|---|---|---|

| [44] | 4 | - | - | 0.41 | 2.98 | - | 0.41 | - | 210 |

| [24] | 5.59 | 4.25 | - | 10.52 | 0.34 | 1.31 | 0.70 | 0.58 | 100 |

| [24] | 1.32 | 5.92 | - | 3.54 | 2.04 | 2.49 | 0.93 | 0.738 | 100 |

| [25] | 1 | - | - | 12.90 | 12.90 | 12.87 | 0.99 | 0.79 | 100 |

| [25] | 5.68 | - | - | 0.40 | 12.90 | 1.08 | 0.48 | 0.44 | 100 |

| [22] | 1.9 | - | - | 2.43 | 8.78 | 4.11 | 0.89 | - | 0.92 |

| [22] | 1.57 | - | - | 4.83 | 11.94 | 7.26 | 0.96 | - | 124 |

| [71] | 5.8 | 9.05 | - | - | - | 8.07 | 0.67 | - | - |

| [38] | 1.94 | - | - | 1.06 | 3.99 | 1.47 | 0.71 | - | 180 |

| [70] | 1 | - | - | 2.86 | 2.86 | - | 0.45 | - | 52 |

| [21] | 1 | - | 30.8 | 0.431 | 0.695 | 0.4948 | 0.92 | - | 140 |

| [68] | 1 | 10 | 6 | - | 1 | - | 0.96 | - | 200 |

| Self-Inductance of Coil L (nH) | Self-Resonance Frequency fSR (GHz) | Quality Factor Q | k | GMAX | f (QMAX) (GHz) | Process Technology | |

|---|---|---|---|---|---|---|---|

| [77] | 28.6, 33.4, 35 | 0.11, 0.17, 0.10 | 0.5, 0.57, 0.34 | 0.79, 0.4, 0.87 | - | 0.06, 0.09, 0.06 | Surface micromachining |

| [34] | 28.6, 29.3 | 0.08, 0.064 | 0.61, 0.35 | 0.9, 0.97 | - | 0.055 | Bulk micromachining and Wafer bonding |

| [83] | 7.14 | - | 5.92 | 0.75 | 0.68 | 0.5 | Metal-MUMPs |

| [11] | 88 | 0.051 | 5.9 | 0.98 | 0.80 | 0.01 | Through-silicon-via technology |

| [84] | 210 | - | - | - | 0.75 | - | Surface micromachining |

| [26] | 10.7 | 5.5 | 8.8 | 0.60 | 0.76 | 1 | Metal-MUMPs |

| [27] | 0.5 | 21 | 11 | - | 0.7 | 10 | Front-side mask less etching |

| [85] | 1.03 | - | 26.3 | - | 0.85 | 10 | Substrate removal underneath the device using deep-trench technique |

| [14] | 2.5 | 14 | 14 | - | 0.87 | 7.5 | Concave-suspending bulk micromachining process |

| [20] | 8 | 13.5 | 8.1 | 0.6 | 0.64 | 5 | Substrate transfer technique and patterned ground shielding |

| [32] | 4.3, 9.6 | 6.5, 3.6 | 9.1, 6.9 | 0.61, 0.65 | - | 0.8, 0.6 | Bulk micromachining |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bajwa, R.; Yapici, M.K. Integrated On-Chip Transformers: Recent Progress in the Design, Layout, Modeling and Fabrication. Sensors 2019, 19, 3535. https://doi.org/10.3390/s19163535

Bajwa R, Yapici MK. Integrated On-Chip Transformers: Recent Progress in the Design, Layout, Modeling and Fabrication. Sensors. 2019; 19(16):3535. https://doi.org/10.3390/s19163535

Chicago/Turabian StyleBajwa, Rayan, and Murat Kaya Yapici. 2019. "Integrated On-Chip Transformers: Recent Progress in the Design, Layout, Modeling and Fabrication" Sensors 19, no. 16: 3535. https://doi.org/10.3390/s19163535

APA StyleBajwa, R., & Yapici, M. K. (2019). Integrated On-Chip Transformers: Recent Progress in the Design, Layout, Modeling and Fabrication. Sensors, 19(16), 3535. https://doi.org/10.3390/s19163535