Advanced Doherty Power Amplifier Architectures for 5G Handset Applications: A Comprehensive Review of Linearity, Back-Off Efficiency, Bandwidth, and Thermal Management

Abstract

1. Introduction

- (1)

- Nonlinear Phase Distortion from Asymmetric AM-AM/AM-PM Responses of Class-AB and Class-C Amplifiers

- (2)

- Efficiency and Bandwidth Degradation Under 3.4 V Supply Compared to Traditional 5 V Systems

- (3)

- Thermal Management in Chips

2. Key Technology Discussion

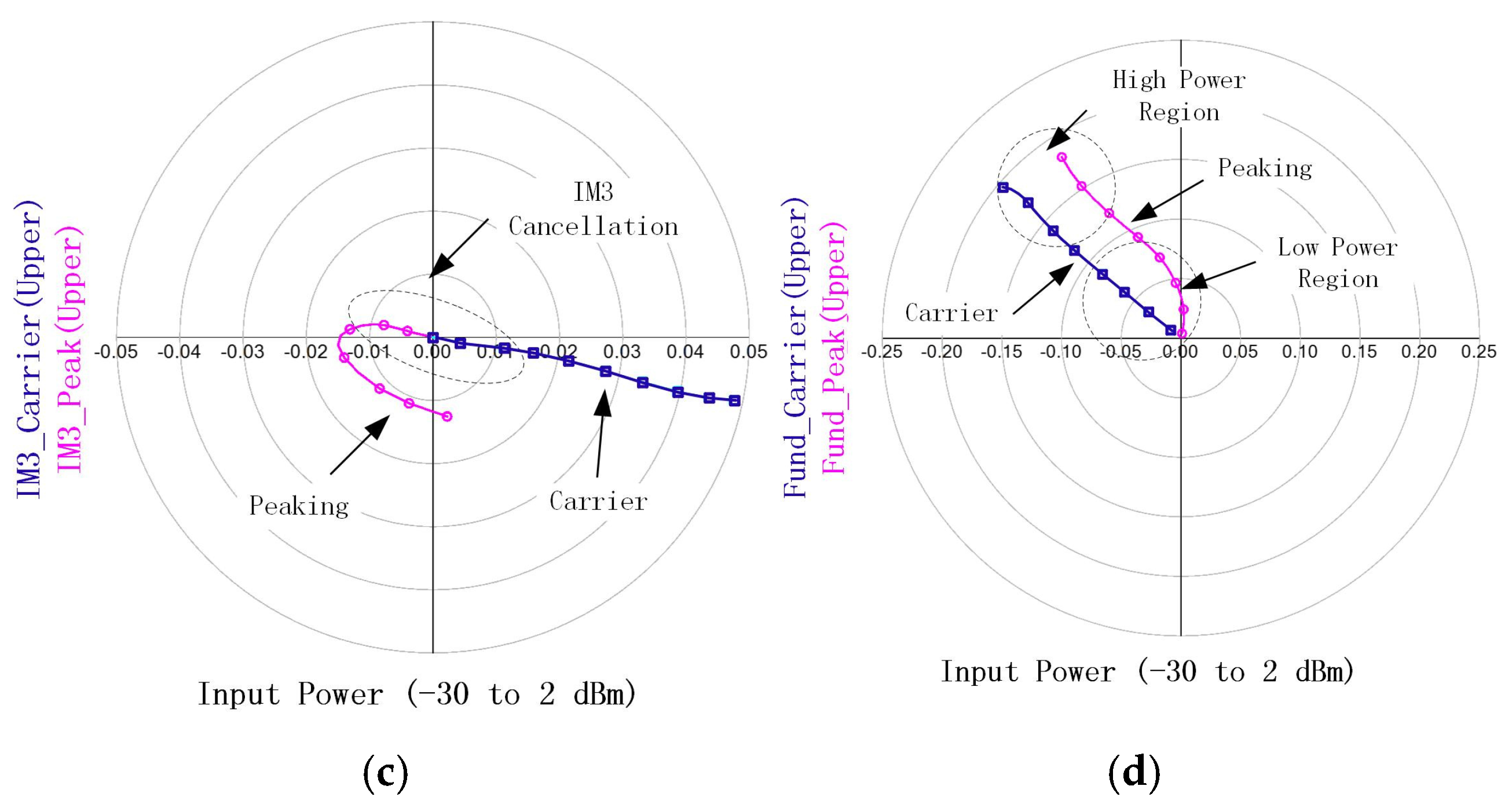

2.1. Linearity Enhancement Techniques

2.2. Back-Off Efficiency Improvement

- (1)

- Asymmetric Power Cell Designs:

- (2)

- Adaptive Bias Control:

- (3)

- Three-Way Doherty Configuration:

2.3. Bandwidth Extension with Low Supply Voltage

- (1)

- Parallel-Plate Couplers:

- (2)

- Multi-Section Output Networks:

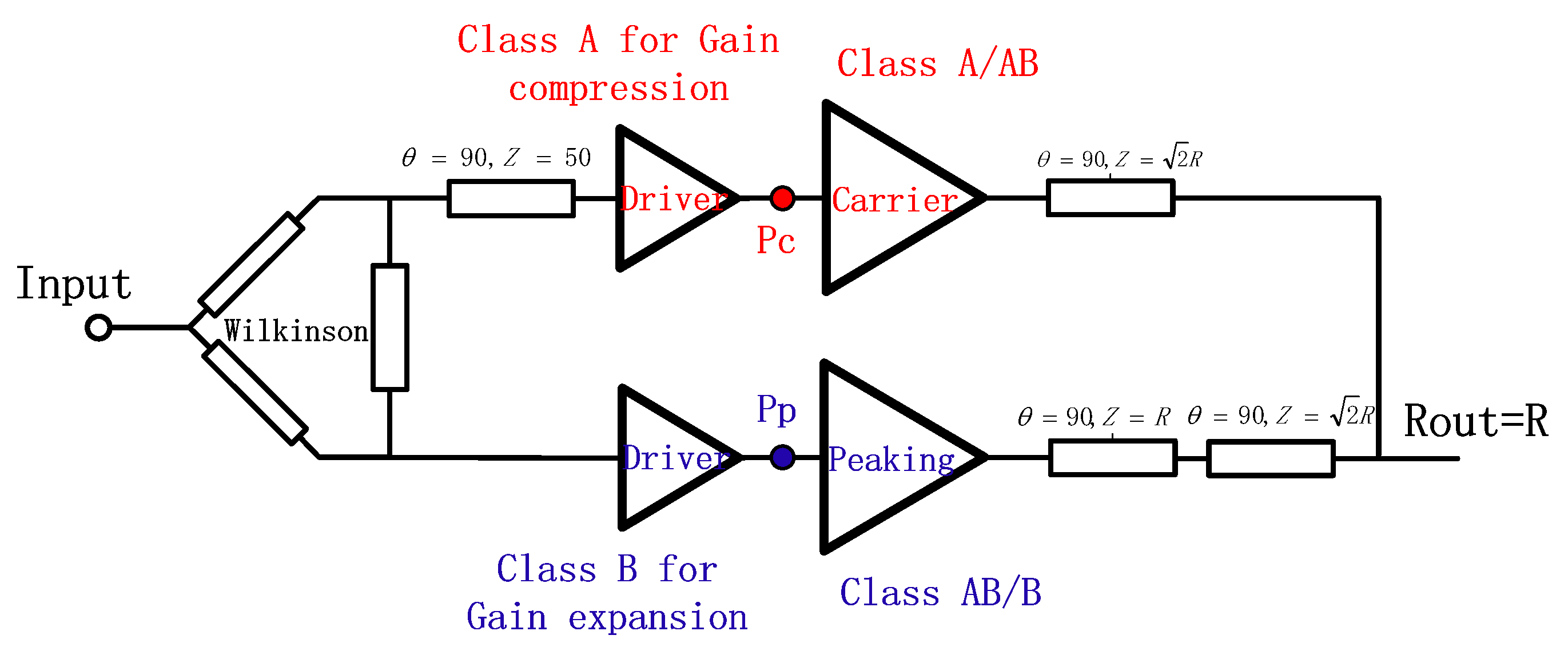

3. Doherty Power Amplifier Circuit Design

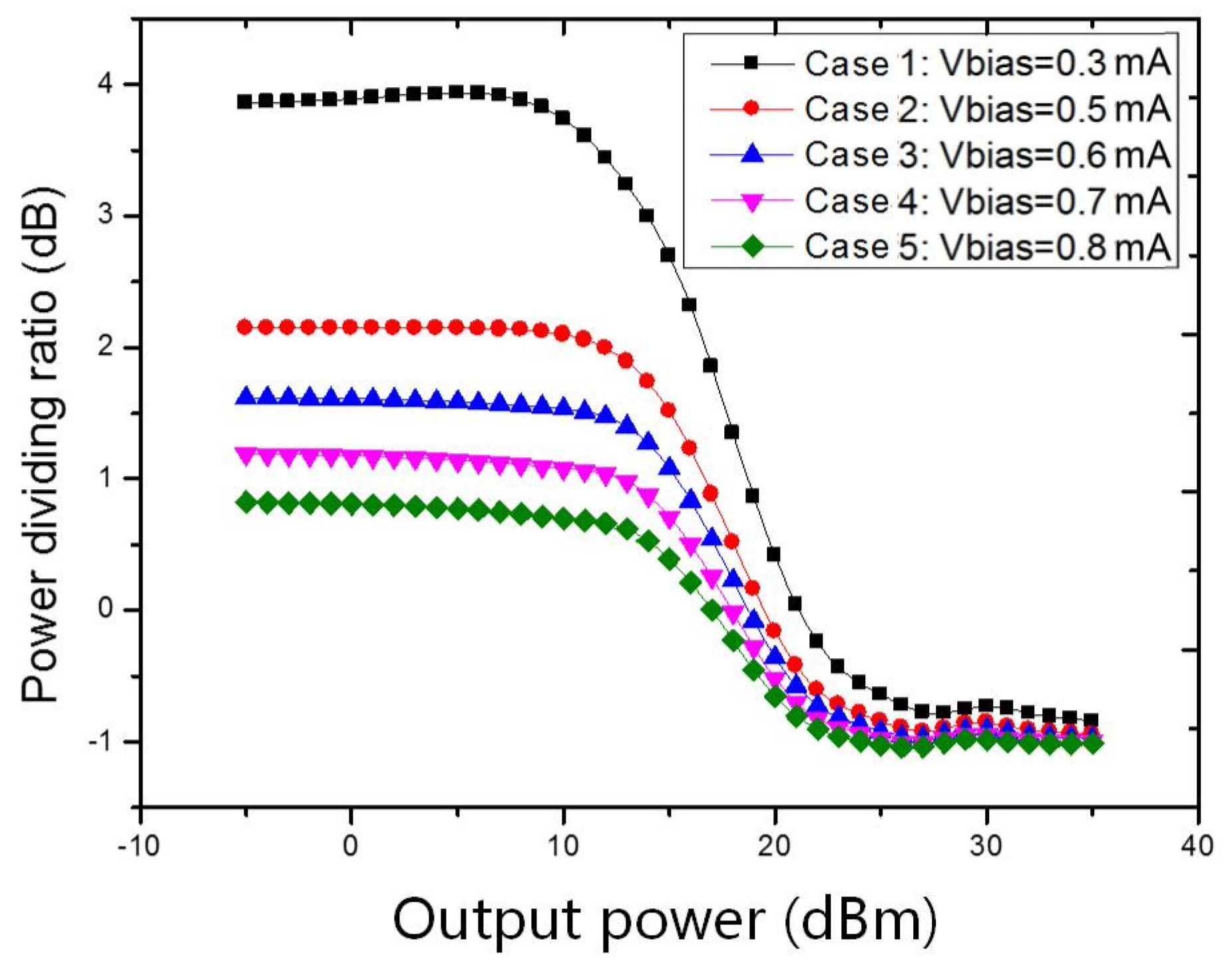

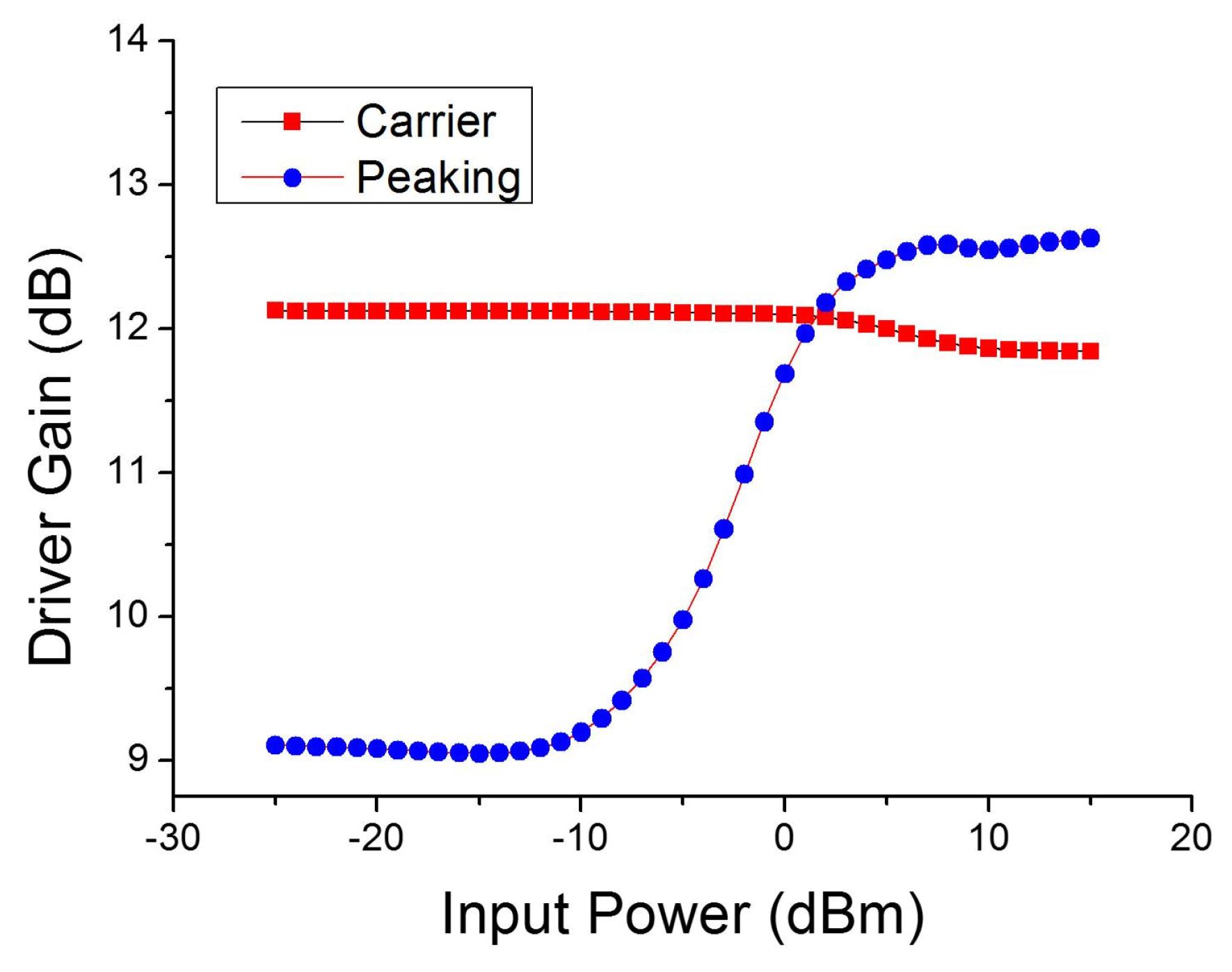

3.1. Tunable Power Allocation by Driver Amplifier

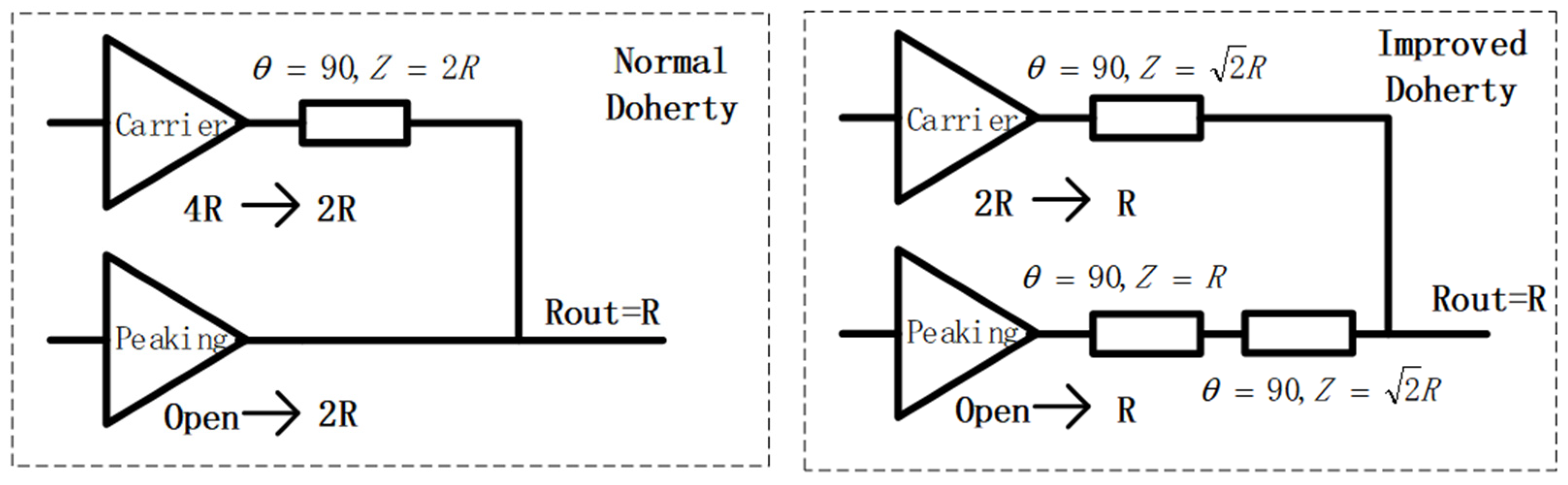

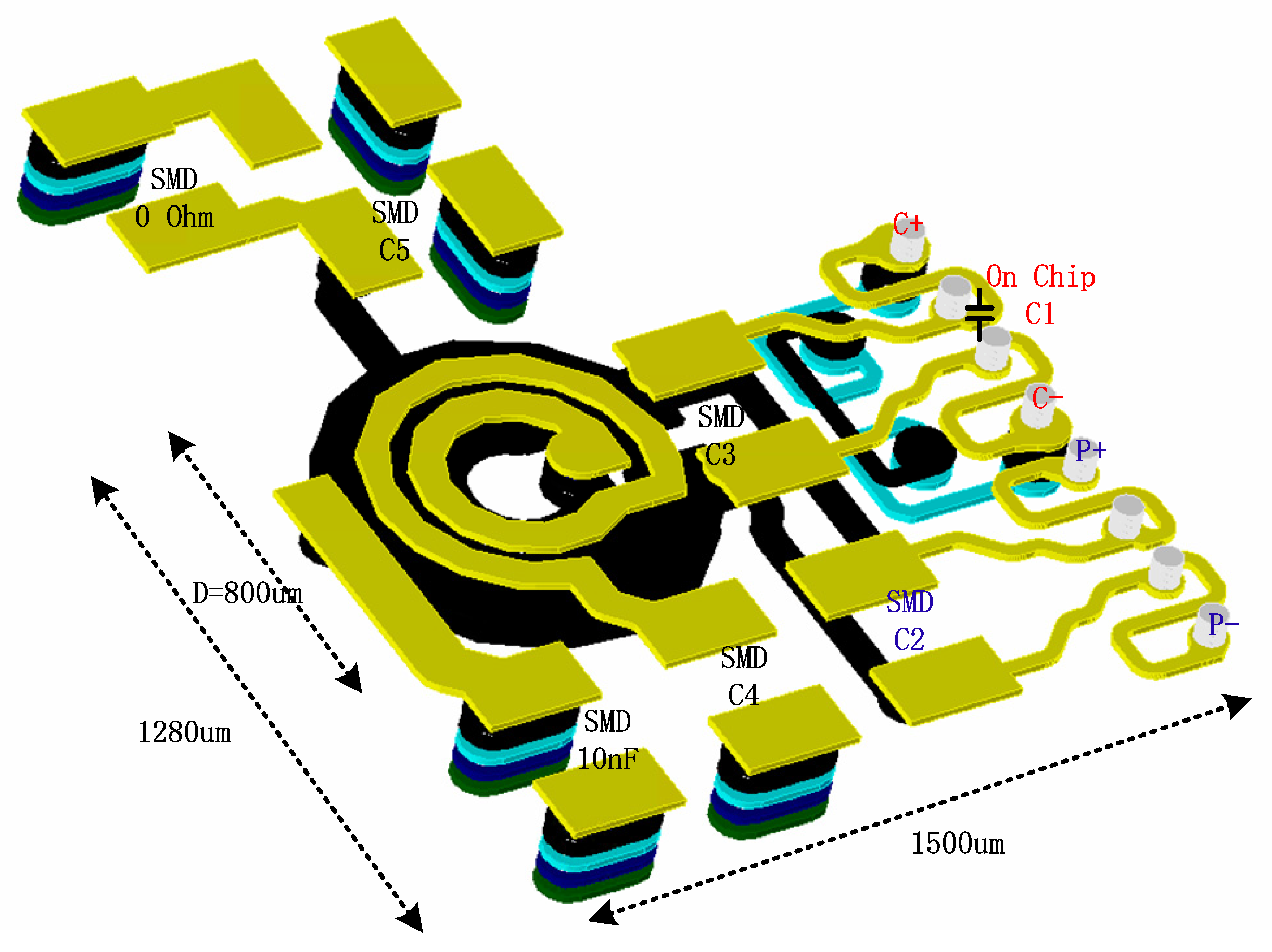

3.2. Output Network Design

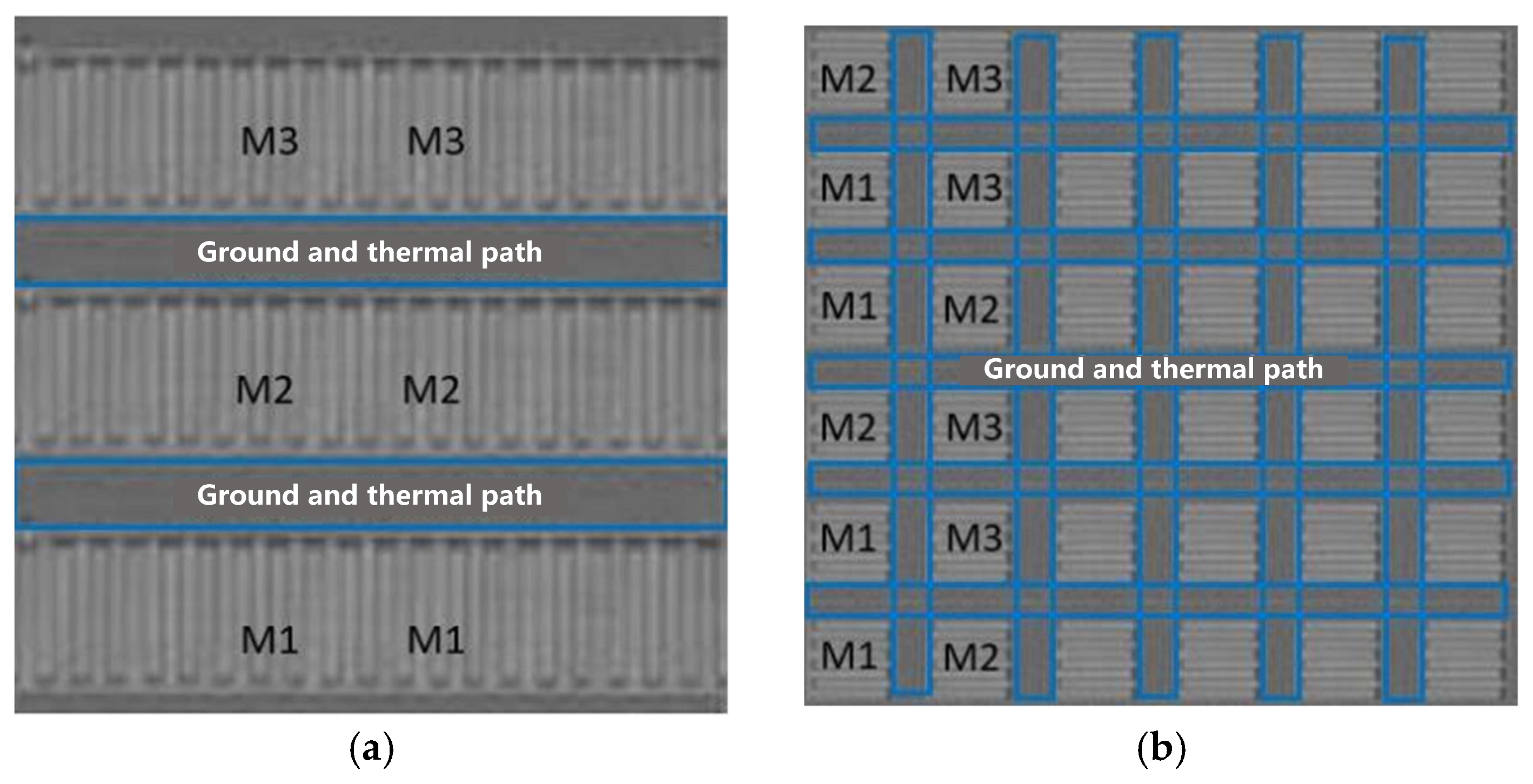

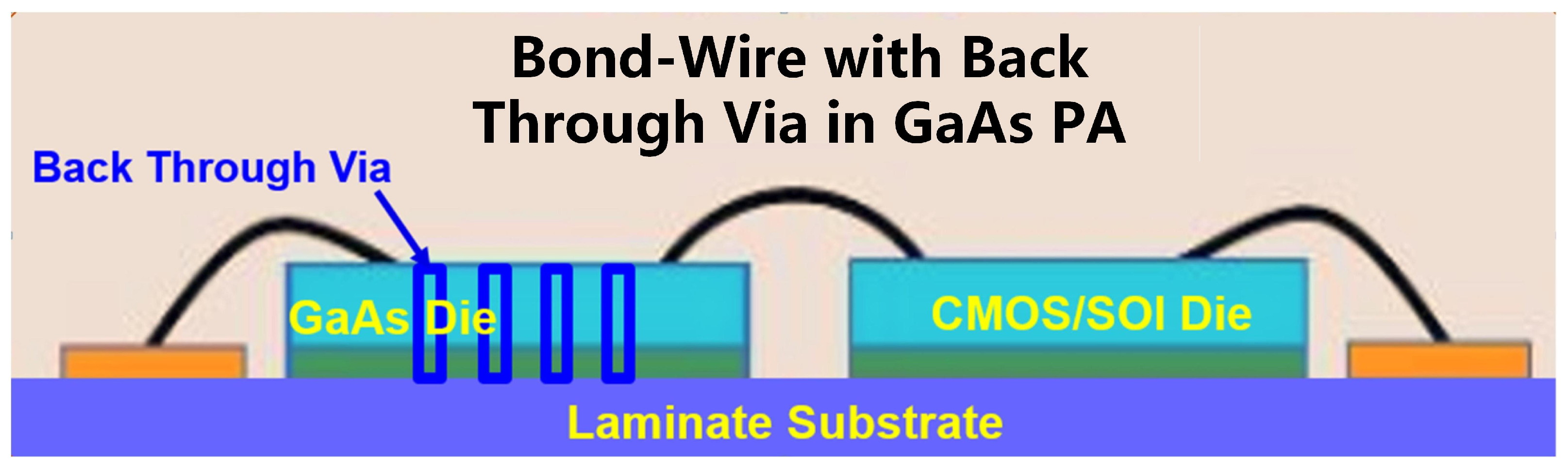

3.3. Thermal Management

4. Implementation Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Kim, B.; Cho, Y. Design of linear Doherty power amplifier for handset application. In Proceedings of the 2016 IEEE MTT-S International Microwave Symposium (IMS), San Francisco, CA, USA, 22–27 May 2016; pp. 1–3. [Google Scholar]

- Cho, Y.; Kang, D.; Kim, J.; Moon, K.; Park, B.; Kim, B. Linear Doherty Power Amplifier with an Enhanced Back-Off Efficiency Mode for Handset Applications. IEEE Trans. Microw. Theory Tech. 2014, 62, 567–578. [Google Scholar] [CrossRef]

- Shihai, H.; Liang, J.; Linjian, X.; Meng, H.; Qian, Y. A High Efficiency and High Linearity GaAs HBT Doherty Power Amplifier for 5G NR 3.4V Application. In Proceedings of the 2024 IEEE/MTT-S International Microwave Symposium—IMS 2024, Washington, DC, USA, 16–21 June 2024; pp. 370–373. [Google Scholar] [CrossRef]

- Oh, H.; Choi, W.; Koo, H.; Shin, J.; Chen, Y.; Jeon, H.; Choi, Y.; Jung, H.; Hwang, J.; Yang, Y. 2.8–3.8 GHz Broadband InGaP/GaAs HBT Doherty Power Amplifier IC for 5G New Radio Handset. In Proceedings of the 2022 IEEE/MTT-S International Microwave Symposium—IMS 2022, Denver, CO, USA, 19–24 June 2022; pp. 849–852. [Google Scholar]

- Yu, H.; Sahlabadi, M.H.; Traore, E.; Eladwy, M.; Ma, H.; Boumaiza, S. 37–43 GHz Wide-Band Doherty Power Amplifier with Enhanced AM-PM Characteristic. In Proceedings of the 2023 IEEE/MTT-S International Microwave Symposium—IMS 2023, San Diego, CA, USA, 11–16 June 2023; pp. 935–938. [Google Scholar]

- Imai, S.; Okabe, H.; Tanaka, S. A Bandwidth-Optimized Transformer-Based Doherty Power Amplifier for 5G Power Class 2 Handset operation at 2.2 GHz–2.7 GHz. In Proceedings of the 2021 IEEE MTT-S International Microwave Symposium (IMS), Atlanta, GA, USA, 7–25 June 2021; pp. 791–794. [Google Scholar]

- He, S.; Peng, F.; Xu, L.; Meng, H.; Qian, Y. Compact High Efficiency and High Power Front-end Module for GSM/EDGE/TD-SCDMA/TD-LTE Applications in 0.13 um CMOS. In Proceedings of the 2018 IEEE Asian Solid-State Circuits Conference (A-SSCC), Tainan, Taiwan, 5–7 November 2018; pp. 289–292. [Google Scholar] [CrossRef]

- Uchida, Y.; He, S.; Yang, X.; Liu, Q.; Yoshimasu, T. 5-GHz band linear CMOS power amplifier IC with a novel integrated linearizer for WLAN applications. In Proceedings of the 2012 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Singapore, 21–23 November 2012; pp. 240–242. [Google Scholar] [CrossRef]

- He, S.; Uchida, Y.; Yang, X.; Liu, Q.; Yoshimasu, T. 5.25 GHz linear CMOS power amplifier with a diode-connected NMOS bias circuit. In Proceedings of the 2012 International Conference on Microwave and Millimeter Wave Technology (ICMMT), Shenzhen, China, 5–8 May 2012; pp. 1–4. [Google Scholar] [CrossRef]

- Takenaka, K.; Noguchi, Y.; Takenouchi, Y.; Okabe, H.; Wada, T. Parallel Plate Coupler Based Doherty Power Amplifier Design for 5G NR Handset Applications. In Proceedings of the 2021 IEEE MTT-S International Microwave Symposium (IMS), Atlanta, GA, USA, 7–25 June 2021; pp. 523–526. [Google Scholar]

- Takenaka, K.; Noguchi, Y.; Arayashiki, S.; Wada, T. Multiband Doherty Power Amplifier Design for 5G NR Sub-6 GHz Handset Applications. In Proceedings of the 2022 Asia-Pacific Microwave Conference (APMC), Yokohama, Japan, 9 November–2 December 2022; pp. 749–751. [Google Scholar]

- Takenaka, K.; Sato, T.; Matsumoto, H.; Kawashima, M.; Nakajima, N. New compact Doherty power amplifier design for handset applications. In Proceedings of the 2017 IEEE Topical Conference on RF/Microwave Power Amplifiers for Radio and Wireless Applications (PAWR), Phoenix, AZ, USA, 15–18 January 2017; pp. 81–83. [Google Scholar]

- He, S.; Xu, L.; Meng, H. A Performance Study of Layout in 0.13 um CMOS Power Amplifier for 4G Mobile Front-End Module. In Proceedings of the 2024 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Chengdu, China, 28–30 August 2024; pp. 1–3. [Google Scholar]

- Srinivasan, P.; Gonzalez, O.H.; Restrepo, O.D.; Lestage, J.; Syed, S.; Taylor, W.; Bandyopadhyay, A.; Gall, M.; Ludvik, S. Thermal Considerations on RF Reliability and Aging in SOI CMOS Based Power Amplifiers. In Proceedings of the 2024 IEEE International Reliability Physics Symposium (IRPS), Grapevine, TX, USA, 14–18 April 2024; pp. 1–6. [Google Scholar] [CrossRef]

- Alluri, S.; Jayamon, J.; Hanafi, B.; Asbeck, P. Simulation Technique for Thermal Resistance in CMOS-SOI Power Amplifier Integrated Circuits. In Proceedings of the 2020 IEEE Topical Conference on RF/Microwave Power Amplifiers for Radio and Wireless Applications (PAWR), San Antonio, TX, USA, 26–29 January 2020; pp. 9–11. [Google Scholar] [CrossRef]

- Choi, S.; Peake, G.M.; Keeler, G.A.; Geib, K.M.; Briggs, R.D.; Beechem, T.E.; Shaffer, R.A.; Clevenger, J.; Patrizi, G.A.; Klem, J.F.; et al. Thermal Design and Characterization of Heterogeneously Integrated InGaP/GaAs HBTs. IEEE Trans. Compon. Packag. Manuf. Technol. 2016, 6, 740–748. [Google Scholar] [CrossRef]

- Pelk, M.J.; Neo, W.C.E.; Gajadharsing, J.R.; Pengelly, R.S.; de Vreede, L.C.N. A High-Efficiency 100-W GaN Three-Way Doherty Amplifier for Base-Station Applications. IEEE Trans. Microw. Theory Tech. 2008, 56, 1582–1591. [Google Scholar] [CrossRef]

- Zhou, H.; Perez-Cisneros, J.-R.; Hesami, S.; Buisman, K.; Fager, C. A Generic Theory for Design of Efficient Three-Stage Doherty Power Amplifiers. IEEE Trans. Microw. Theory Tech. 2022, 70, 1242–1253. [Google Scholar] [CrossRef]

- Kim, I.; Moon, J.; Jee, S.; Kim, B. Optimized Design of a Highly Efficient Three-Stage Doherty PA Using Gate Adaptation. IEEE Trans. Microw. Theory Tech. 2010, 58, 2562–2574. [Google Scholar] [CrossRef]

- Musolff, C.; Kamper, M.; Abou-Chahine, Z.; Fischer, G. Linear and Efficient Doherty PA Revisited. IEEE Microw. Mag. 2014, 15, 73–79. [Google Scholar] [CrossRef]

- Cho, Y.; Kang, D.; Moon, K.; Jeong, D.; Kim, B. A Handy Dandy Doherty PA: A Linear Doherty Power Amplifier for Mobile Handset Application. IEEE Microw. Mag. 2017, 18, 110–124. [Google Scholar] [CrossRef]

- Courty, A.; Quindroit, C.; Bouny, J.-J.; Ferris, P.; Rochas, P.; Moronval, X. A 3.7–4.2GHz MMIC Doherty Power Amplifier Linearized over 500MHz Instantaneous Bandwidth. In Proceedings of the 2023 IEEE Topical Conference on RF/Microwave Power Amplifiers for Radio and Wireless Applications, Las Vegas, NV, USA, 22–25 January 2023; pp. 29–31. [Google Scholar] [CrossRef]

- Cho, Y.; Moon, K.; Park, B.; Kim, J.; Kim, B. Voltage-Combined CMOS Doherty Power Amplifier Based on Transformer. IEEE Trans. Microw. Theory Tech. 2016, 64, 3612–3622. [Google Scholar] [CrossRef]

- Park, H.C.; Kim, S.; Lee, J.; Jung, J.; Baek, S.; Kim, T.; Kang, D.; Minn, D.; Yang, S.G. Single Transformer-Based Compact Doherty Power Amplifiers for 5G RF Phased-Array ICs. IEEE J. Solid-State Circuits 2022, 57, 1267–1279. [Google Scholar] [CrossRef]

- Bo, S.F.; Ou, J.-H.; Peng, Y.J.; Xuan, K.; Xu, J.-X.; Zhang, X.Y. Broadband GaAs HBT Doherty Power Amplifier for 5G NR Mobile Handset. IEEE Trans. Circuits Syst. II Express Briefs 2024, 71, 527–531. [Google Scholar] [CrossRef]

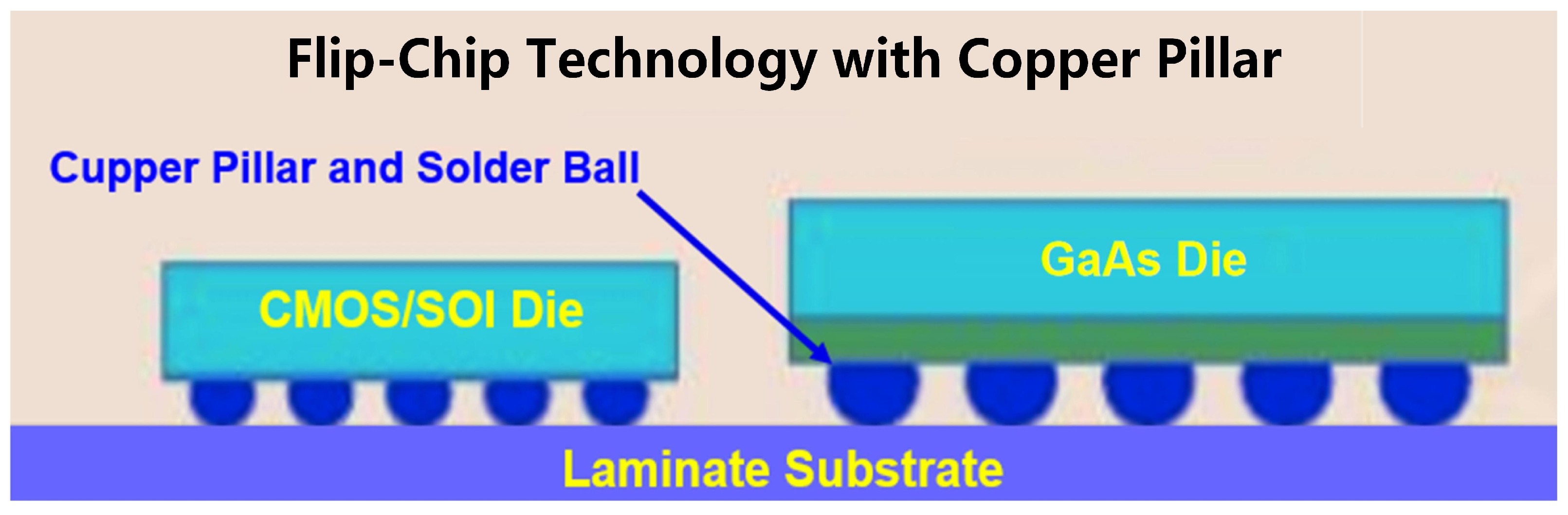

| Bond-Wire in GaAs | Flip-Chip in GaAs | |

|---|---|---|

| Advantages |

|

|

| Disadvantages |

|

|

| Ref. | [10] 2021 IMS | [4] 2022 IMS | [21] 2023 TCSII | [3] 2024 IMS |

|---|---|---|---|---|

| Supply Voltage (V) | 3.8 | 4.5 | 5 V | 3.4 V |

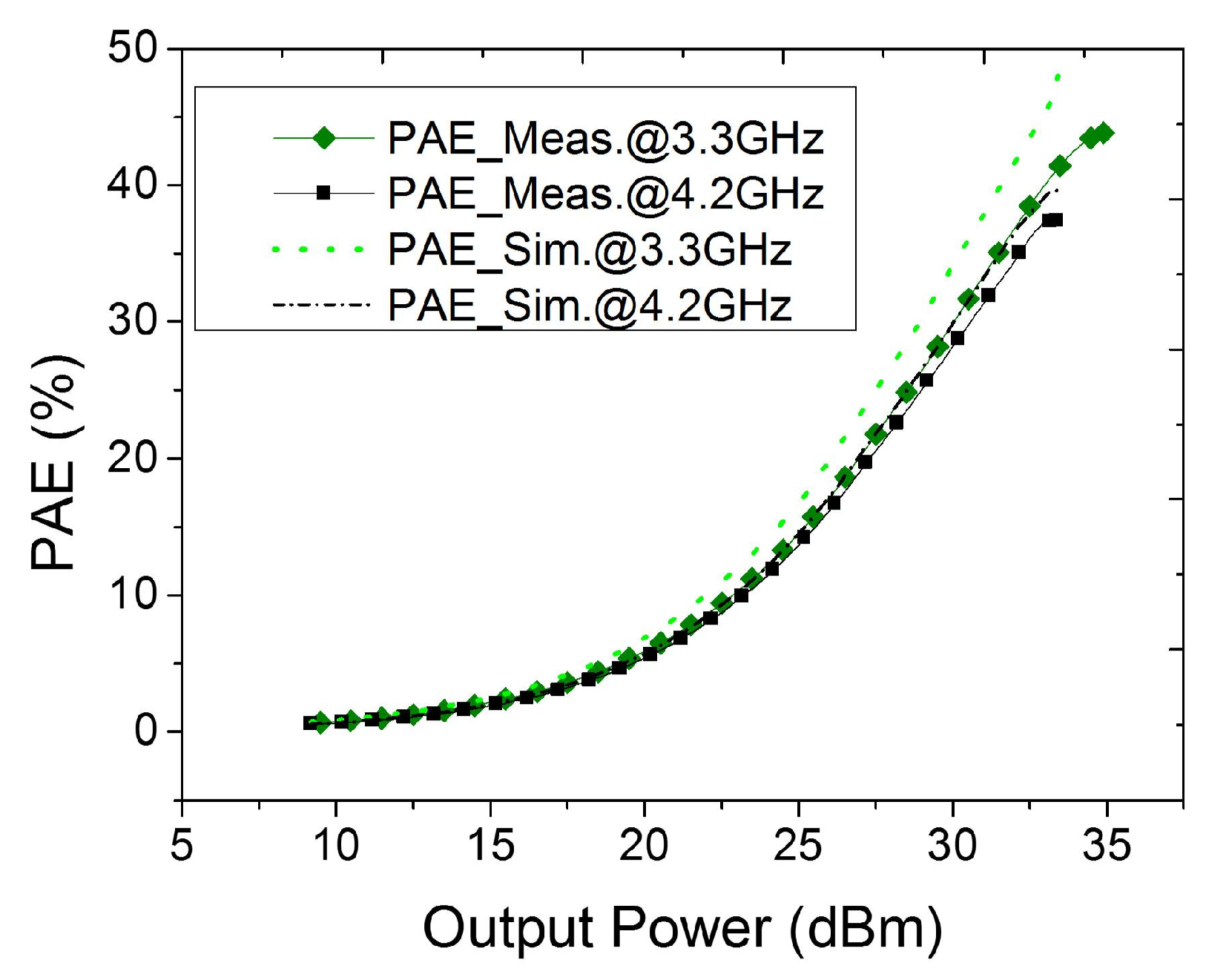

| Frequency (GHz) | 3.35–4.15 | 2.8–3.8 | 3.3–4.2 | 3.35–4.15 |

| PA Process | GaAs HBT (Flip-chip) | GaAs HBT (Flip-chip) | GaAs HBT M3 (Bond-wire) | GaAs HBT M2 (Flip-chip) |

| PA Die Area (mm2) | 1.11.1 | 1.51 | 1.341.44 | 1.11.3 |

| Module Area (mm2) | 3.52.5 *, Laminate | 2.11.8, Laminate | 1.693.85, Laminate | 1.3 2.5, Laminate |

| CW Psat (dBm) | - | - | 36 | 33.4–34.8 |

| CW PAE (%) @Sat. | - | 32.2–47.3 | 39–44 | 38–43 |

| CW Gain | 33–36 * | 31.9–38.3 | 25.8–27.2 | 26.2–28.1 |

| NR Pout (dBm) | 27.8 | 26–27.8 | 30 | 30–31 |

| NR PAE (%) | 35–42 | 22–30.6 | 26.2–30.3 | 31–34 |

| NR ACPR (dBc) | −35 | −33 | −32.1 | −36 |

| Using DPD | Yes | NO | NO | NO |

| Structure | Single-end Doherty | Differential Doherty | Quadrature + single-differential Doherty | Wilkinson + differential Doherty |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

He, S.; Chen, H. Advanced Doherty Power Amplifier Architectures for 5G Handset Applications: A Comprehensive Review of Linearity, Back-Off Efficiency, Bandwidth, and Thermal Management. Chips 2025, 4, 20. https://doi.org/10.3390/chips4020020

He S, Chen H. Advanced Doherty Power Amplifier Architectures for 5G Handset Applications: A Comprehensive Review of Linearity, Back-Off Efficiency, Bandwidth, and Thermal Management. Chips. 2025; 4(2):20. https://doi.org/10.3390/chips4020020

Chicago/Turabian StyleHe, Shihai, and Huan Chen. 2025. "Advanced Doherty Power Amplifier Architectures for 5G Handset Applications: A Comprehensive Review of Linearity, Back-Off Efficiency, Bandwidth, and Thermal Management" Chips 4, no. 2: 20. https://doi.org/10.3390/chips4020020

APA StyleHe, S., & Chen, H. (2025). Advanced Doherty Power Amplifier Architectures for 5G Handset Applications: A Comprehensive Review of Linearity, Back-Off Efficiency, Bandwidth, and Thermal Management. Chips, 4(2), 20. https://doi.org/10.3390/chips4020020