Hierarchical Transfer Learning for Cycle Time Forecasting for Semiconductor Wafer Lot under Different Work in Process Levels

Abstract

:1. Introduction

- (1)

- (2)

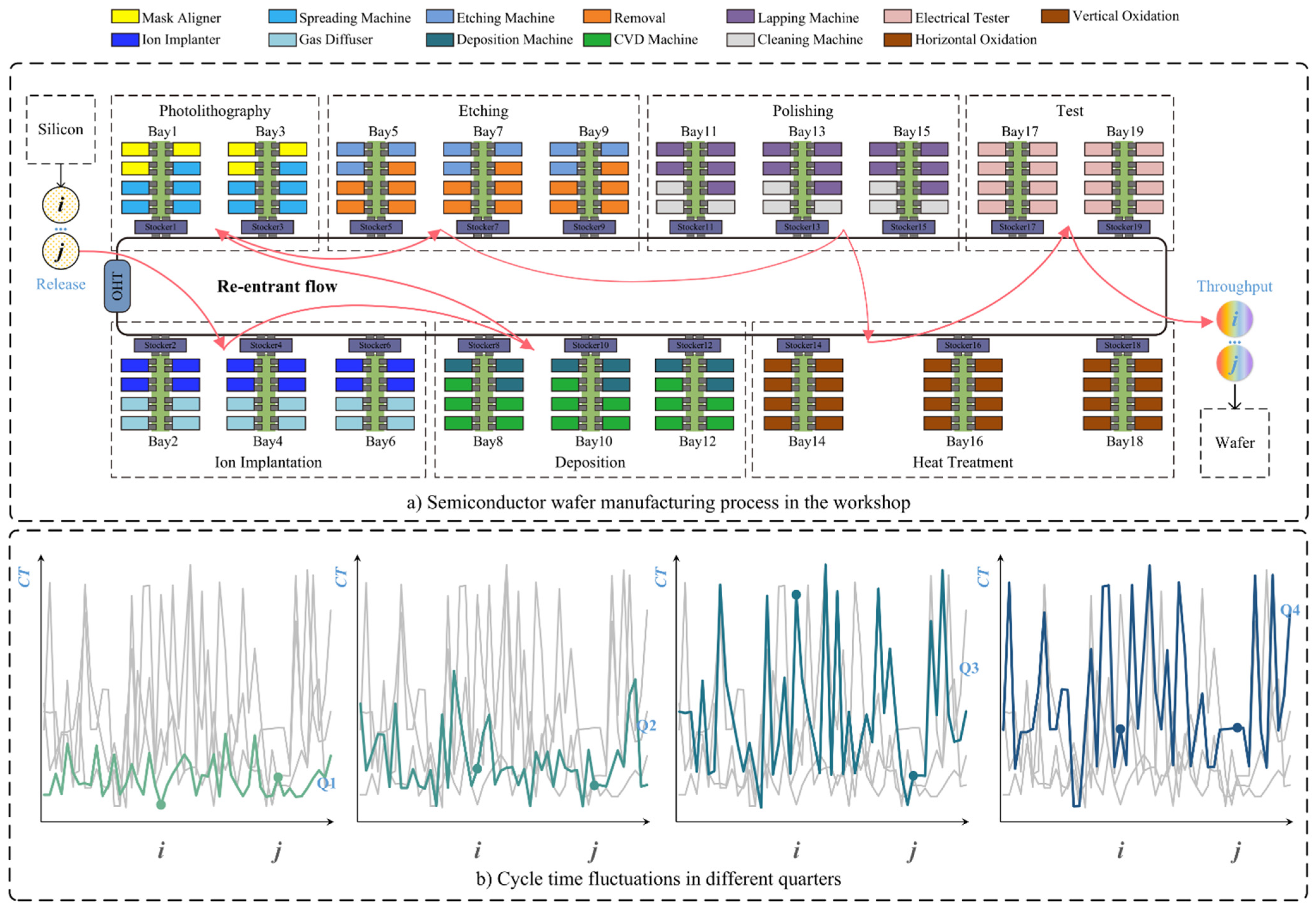

- The wafer CT fluctuates (as shown in Figure 1b) after the make-to-stock strategies are changed; however, at this time, there are little data available to predict the wafer CT.

2. Related Works

3. Methods

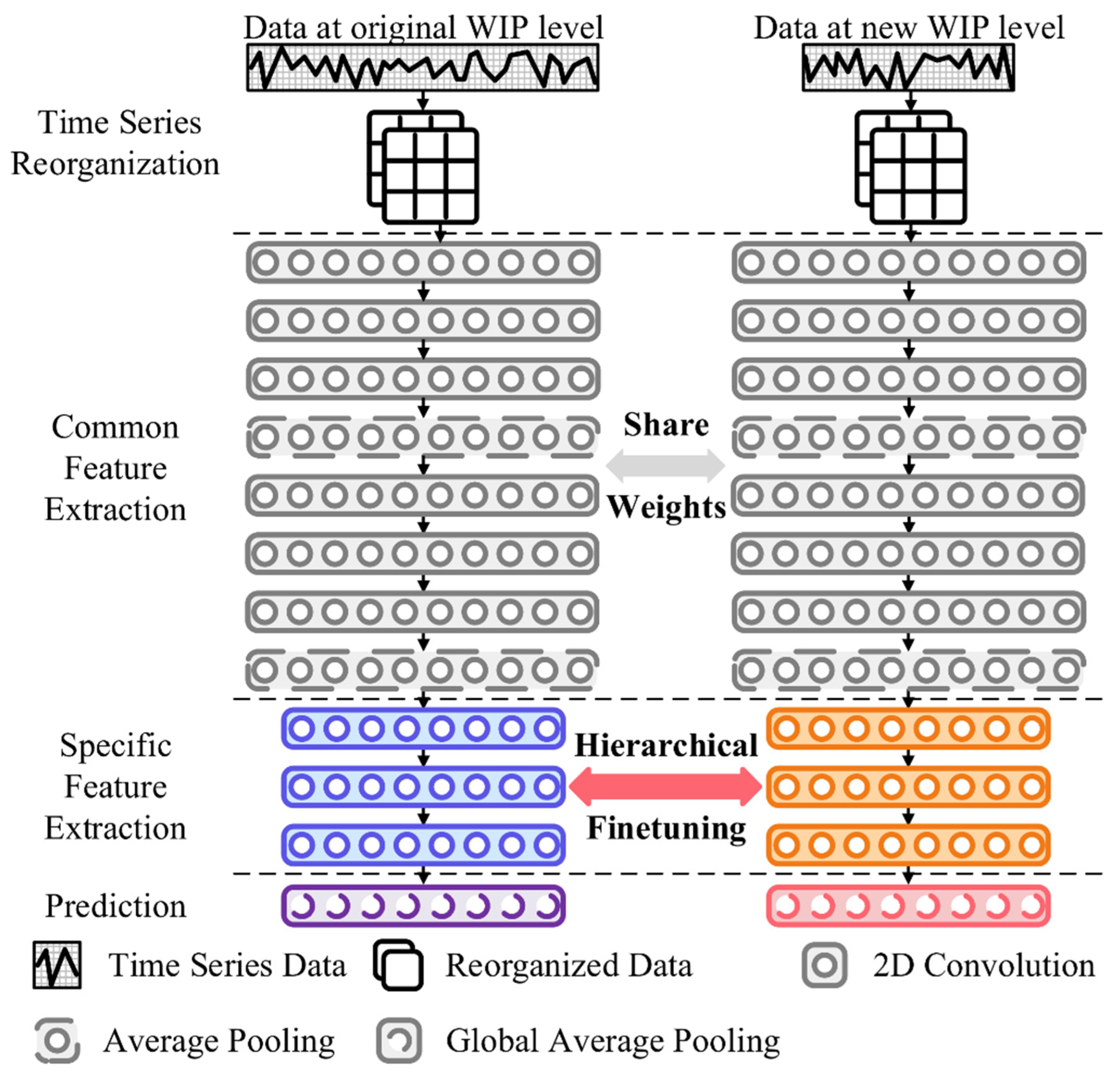

3.1. Architecture of Hierarchical Finetuning Transfer Network

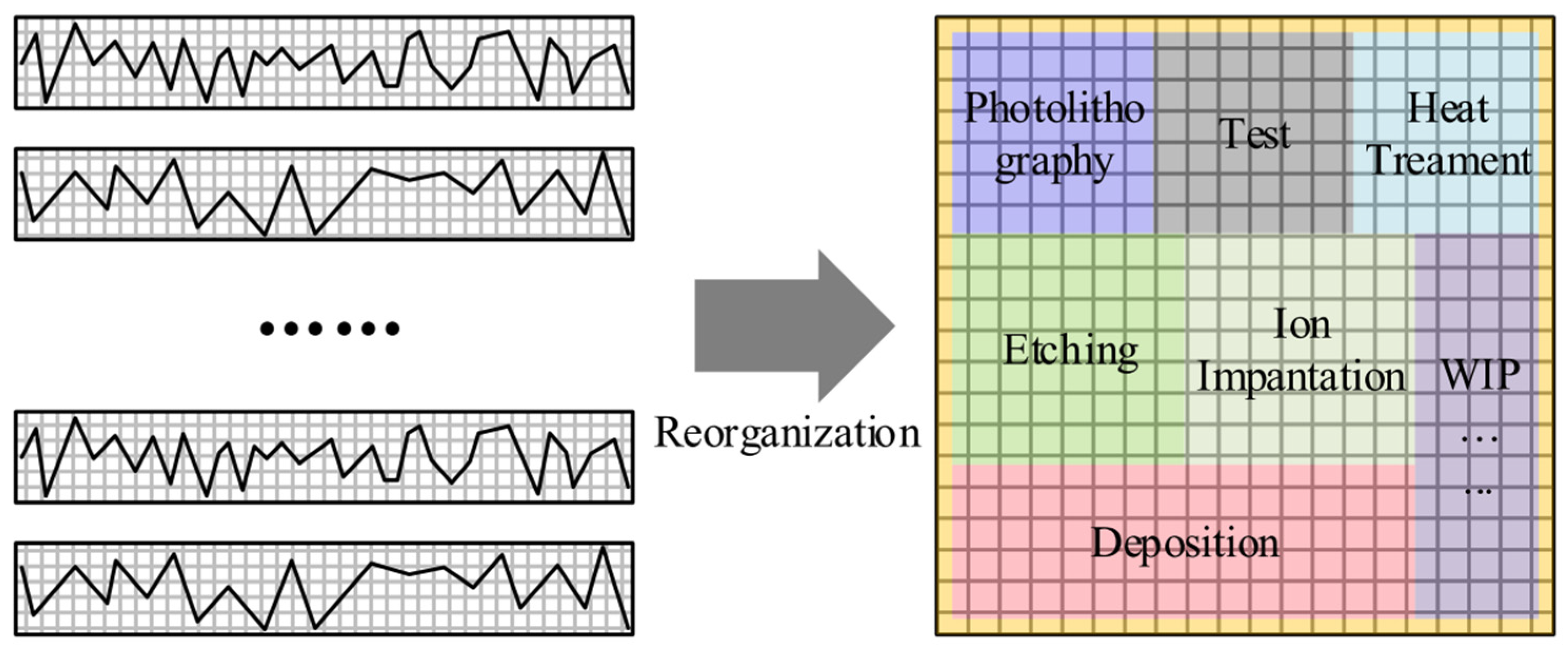

- Input layer

- Convolution layer

- Output layer

3.2. Training Process of HFTN

- Training process of basic network

- Hierarchical finetuning transfer training

4. Results and Discussions

4.1. Dataset and Metrics

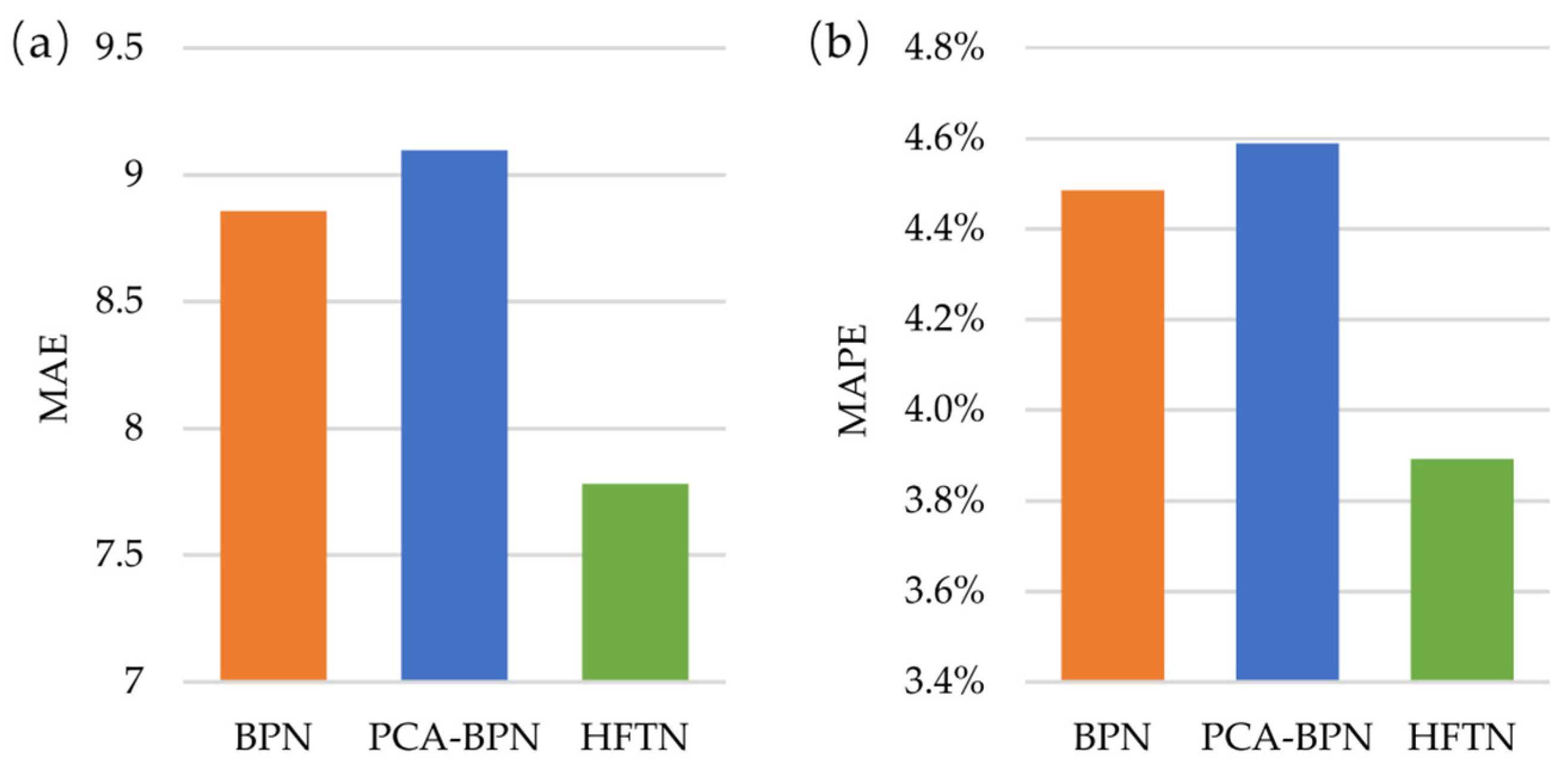

4.2. Comparison with Existing Methods

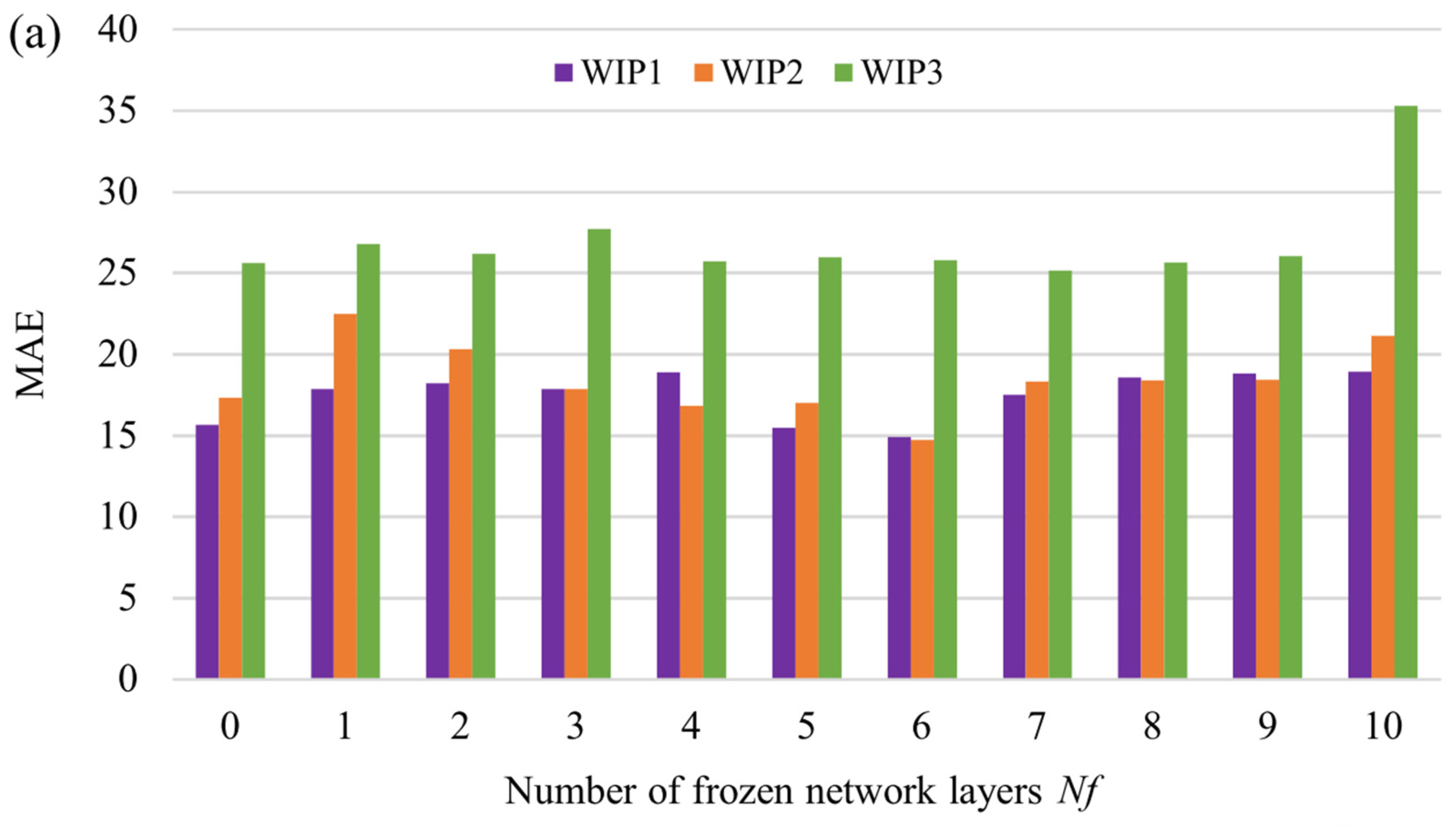

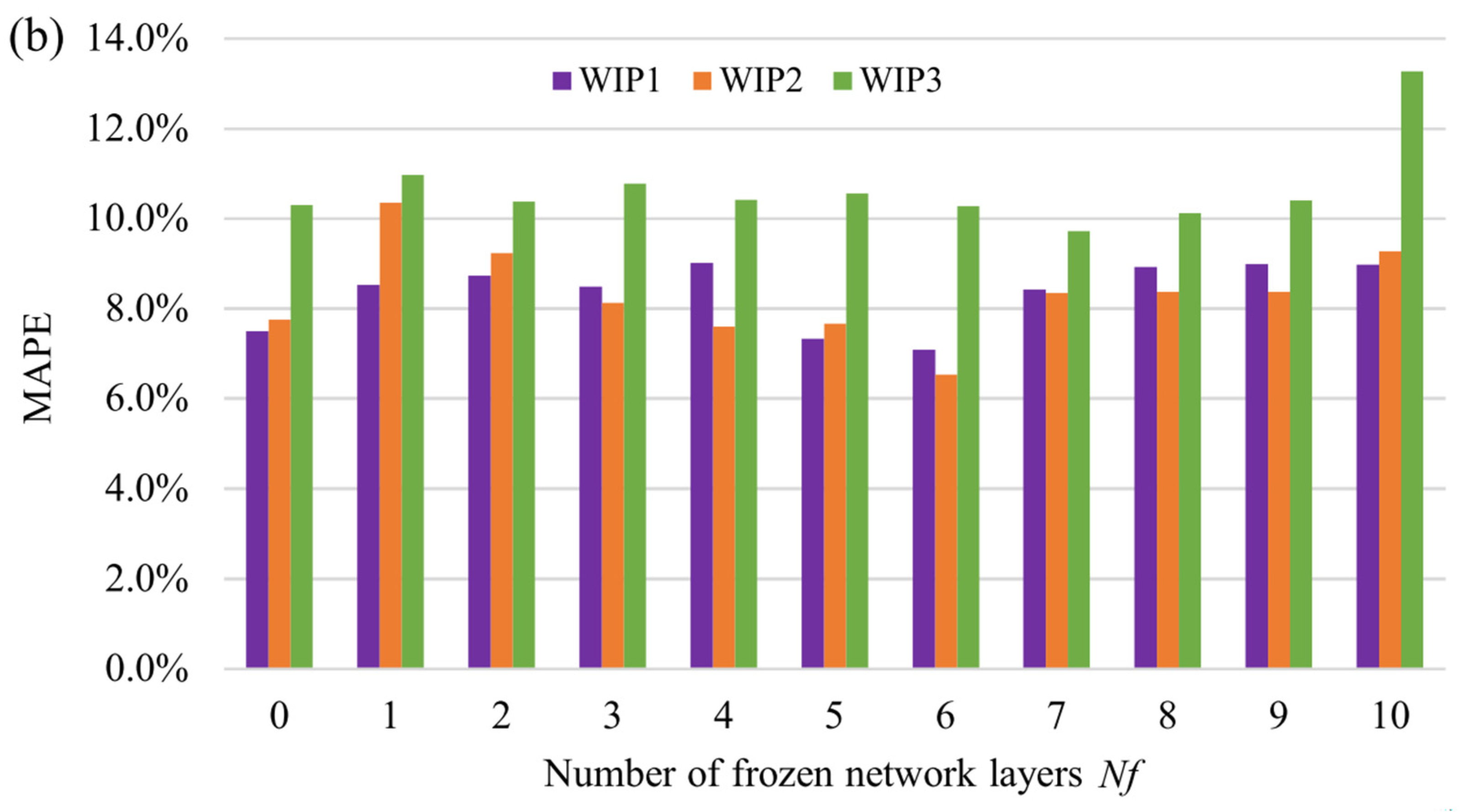

4.3. Hierarchical Optimization

5. Conclusions

- (1)

- The processing area characteristics of the multiple re-entrant flow wafer fabrication were taken into account, and the 2D convolutional neural network was utilized to extract the spatial-temporal characteristics from the wafer fabrication data, and the CT prediction of a single WIP level was achieved in this way.

- (2)

- The transfer learning strategy based on the hierarchical optimization and the underlying structure sharing the weights was designed to extract the common characteristics of the manufacturing system at different WIP levels. Through pooling twice, the common characteristics were highly integrated into specific characteristics. So, the finetuning training was conducted on the high-level architecture to extract the specific characteristics. Finally, the prediction of wafer CT at a new WIP level was achieved through hierarchical transfer learning.

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Uzsoy, R.; Fowler, J.W.; Moench, L. A survey of semiconductor supply chain models Part II: Demand planning, inventory management, and capacity planning. Int. J. Prod. Res. 2018, 56, 4546–4564. [Google Scholar] [CrossRef]

- Chidambaram, P.R.; Bowen, C.; Chakravarthi, S.; Machala, C.; Wise, R. Fundamentals of silicon material properties for successful exploitation of strain engineering in modern CMOS manufacturing. IEEE Trans. Electron. Devices 2006, 53, 944–964. [Google Scholar] [CrossRef]

- Moench, L.; Uzsoy, R.; Fowler, J.W. A survey of semiconductor supply chain models part III: Master planning, production planning, and demand fulfilment. Int. J. Prod. Res. 2018, 56, 4565–4584. [Google Scholar] [CrossRef]

- Wang, J.; Xu, C.; Zhang, J.; Zhong, R. Big data analytics for intelligent manufacturing systems: A review. J. Manuf. Syst. 2021, in press. [Google Scholar] [CrossRef]

- Hopp, W.J.; Spearman, M.L. Factory Physics: Foundations of Manufacturing Management, 2nd ed.; Irwin/McGraw-Hill: Boston, MA, USA, 2001. [Google Scholar]

- Wang, J.; Zheng, P.; Zhang, J. Big data analytics for cycle time related feature selection in the semiconductor wafer fabrication system. Comput. Ind. Eng. 2020, 143, 106362. [Google Scholar] [CrossRef]

- Wang, J.; Yang, J.; Zhang, J.; Wang, X.; Zhang, W. Big data driven cycle time parallel prediction for production planning in wafer manufacturing. Enterp. Inf. Syst. 2018, 12, 714–732. [Google Scholar] [CrossRef]

- Zhang, C.; Bard, J.F.; Chacon, R. Controlling work in process during semiconductor assembly and test operations. Int. J. Prod. Res. 2017, 55, 7251–7275. [Google Scholar] [CrossRef] [Green Version]

- Wang, J.; Xu, C.; Yang, Z.; Zhang, J.; Li, X. Deformable convolutional networks for efficient mixed-type wafer defect pattern recognition. IEEE Trans. Semicond. Manuf. 2020, 33, 587–596. [Google Scholar] [CrossRef]

- Yang, F.; Ankenman, B.E.; Nelson, B.L. Estimating cycle time percentile curves for manufacturing systems via simulation. Inf. J. Comput. 2008, 20, 628–643. [Google Scholar] [CrossRef]

- Tai, Y.T.; Pearn, W.L.; Lee, J.H. Cycle time estimation for semiconductor final testing processes with Weibull-distributed waiting time. Int. J. Prod. Res. 2012, 50, 581–592. [Google Scholar] [CrossRef]

- Sha, D.Y.; Storch, R.L.; Liu, C.H. Development of a regression-based method with case-based tuning to solve the due date assignment problem. Int. J. Prod. Res. 2007, 45, 65–82. [Google Scholar] [CrossRef]

- Schelasin, R. Using static capacity modeling and queuing theory equations to predict factory cycle time performance in semiconductor manufacturing. In Proceedings of the 2011 Winter Simulation Conference, Phoenix, AZ, USA, 11–14 December 2011; pp. 2040–2049. [Google Scholar] [CrossRef]

- Guo, Z.; Baruah, S.K. A neurodynamic approach for real-time scheduling via maximizing piecewise linear utility. IEEE Trans. Neural Netw. Learn. Syst. 2016, 27, 238–248. [Google Scholar] [CrossRef] [PubMed]

- Li, X.; Bai, R. Freight vehicle travel time prediction using gradient boosting regression tree. In Proceedings of the 2016 15th IEEE International Conference on Machine Learning and Applications (ICMLA), New York, NY, USA, 18–20 December 2016; pp. 1010–1015. [Google Scholar] [CrossRef]

- Ke, G.; Meng, Q.; Finley, T.; Wang, T.; Chen, W.; Ma, W.; Ye, Q.; Liu, T.Y. Lightgbm: A highly efficient gradient boosting decision tree. Adv. Neural Inf. Process. Syst. 2017, 30, 3146–3154. [Google Scholar]

- Liu, J.; Zio, E. SVM hyperparameters tuning for recursive multi-step-ahead prediction. Neural Comput. Appl. 2017, 28, 3749–3763. [Google Scholar] [CrossRef]

- Chu, Z.; Zhu, D.; Yang, S.X. Observer-based adaptive neural network trajectory tracking control for remotely operated vehicle. IEEE Trans. Neural Netw. Learn. Syst. 2017, 28, 1633–1645. [Google Scholar] [CrossRef]

- Backus, P.; Janakiram, M.; Mowzoon, S.; Runger, G.C.; Bhargava, A. Factory cycle-time prediction with a data-mining approach. IEEE Trans. Semicond. Manuf. 2006, 19, 252–258. [Google Scholar] [CrossRef]

- Pearn, W.L.; Chung, S.H.; Lai, C.A. Due-date assignment for wafer fabrication under demand variate environment. IEEE Trans. Semicond. Manuf. 2007, 20, 165–175. [Google Scholar] [CrossRef]

- Tirkel, I. Forecasting flow time in semiconductor manufacturing using knowledge discovery in databases. Int. J. Prod. Res. 2013, 51, 5536–5548. [Google Scholar] [CrossRef]

- Chang, P.C.; Liao, T.W. Combining SOM and fuzzy rule base for flow time prediction in semiconductor manufacturing factory. Appl. Soft. Comput. 2006, 6, 198–206. [Google Scholar] [CrossRef]

- Chen, T.; Wang, Y.C. Incorporating the FCM–BPN approach with nonlinear programming for internal due date assignment in a wafer fabrication plant. Robot. Com.-Int. Manuf. 2010, 26, 83–91. [Google Scholar] [CrossRef]

- Zhu, X.; Qiao, F. Cycle time prediction method of wafer fabrication system based on industrial big data. Comput. Integ. Manuf. Sys. 2017, 23, 2172–2179. [Google Scholar] [CrossRef]

- Wang, J.; Zhang, J.; Wang, X. Bilateral LSTM: A two-dimensional long short-term memory model with multiply memory units for short-term cycle time forecasting in re-entrant manufacturing systems. IEEE Trans. Ind. Inf. 2018, 14, 748–758. [Google Scholar] [CrossRef]

- Bai, Y.; Li, C.; Sun, Z.; Chen, H. Deep neural network for manufacturing quality prediction. In Proceedings of the 2017 Prognostics and System Health Management Conference (phm-Harbin), Harbin, China, 9–12 July 2017; pp. 307–311. [Google Scholar]

- Wang, C.; Jiang, P. Deep neural networks based order completion time prediction by using real-time job shop RFID data. J. Intell. Manuf. 2019, 30, 1303–1318. [Google Scholar] [CrossRef]

- Sun, C.; Ma, M.; Zhao, Z.; Tian, S.; Yan, R.; Chen, X. Deep transfer learning based on sparse autoencoder for remaining useful life prediction of tool in manufacturing. IEEE Trans. Ind. Inform. 2019, 15, 2416–2425. [Google Scholar] [CrossRef]

- Xu, C.; Wang, J.; Zhang, J.; Li, X. Anomaly detection of power consumption in yarn spinning using transfer learning. Comput. Ind. Eng. 2021, 152, 107015. [Google Scholar] [CrossRef]

- Wang, R.; Peng, C.; Gao, J.; Gao, Z.; Jiang, H. A dilated convolution network-based LSTM model for multi-step prediction of chaotic time series. Comput. Appl. Math. 2020, 39, 30. [Google Scholar] [CrossRef]

- Xiao, Y.; Yin, H.; Zhang, Y.; Qi, H.; Zhang, Y.; Liu, Z. A dual-stage attention-based Conv-LSTM network for spatio-temporal correlation and multivariate time series prediction. Int. J. Intell. Syst. 2021, 36, 2036–2057. [Google Scholar] [CrossRef]

- Wang, J.; Xu, C.; Dai, L.; Zhang, J.; Zhong, R. An unequal learning approach for 3D point cloud segmentation. IEEE Trans. Ind. Inf. 2021, 1. [Google Scholar] [CrossRef]

- Goodfellow, I.; Bengio, Y.; Courville, A. Deep Learning; Adaptive Computation and Machine Learning; The MIT Press: Cambridge, MA, USA, 2016. [Google Scholar]

- Chen, H.; Yang, B.; Wang, G.; Liu, J.; Xu, X.; Wang, S.; Liu, D. A novel bankruptcy prediction model based on an adaptive fuzzy K-Nearest neighbor method. Knowl.-Based Syst. 2011, 24, 1348–1359. [Google Scholar] [CrossRef]

- Versaci, M.; Morabito, F.C. Fuzzy time series approach for disruption prediction in tokamak reactors. IEEE Trans. Magn. 2003, 39, 1503–1506. [Google Scholar] [CrossRef]

- Wang, H.; Zheng, L.; Meng, X. Traffic accidents prediction model based on fuzzy logic. Commun. Comput. Inf. Sci. 2011, 201, 101–108. [Google Scholar] [CrossRef]

- Zhu, B.; Chen, M.; Wade, N.; Ran, L. A prediction model for wind farm power generation based on fuzzy modeling. Procedia Environ. Sci. 2012, 12, 122–129. [Google Scholar] [CrossRef] [Green Version]

| Type | Parameters | Symbol |

|---|---|---|

| Wafer state parameters | Processing time for each process | |

| Equipment state parameters | Current use ratio of each device | |

| Waiting queue length of each device | ||

| Workshop state parameters | WIP quantity |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, J.; Gao, P.; Li, Z.; Bai, W. Hierarchical Transfer Learning for Cycle Time Forecasting for Semiconductor Wafer Lot under Different Work in Process Levels. Mathematics 2021, 9, 2039. https://doi.org/10.3390/math9172039

Wang J, Gao P, Li Z, Bai W. Hierarchical Transfer Learning for Cycle Time Forecasting for Semiconductor Wafer Lot under Different Work in Process Levels. Mathematics. 2021; 9(17):2039. https://doi.org/10.3390/math9172039

Chicago/Turabian StyleWang, Junliang, Pengjie Gao, Zhe Li, and Wei Bai. 2021. "Hierarchical Transfer Learning for Cycle Time Forecasting for Semiconductor Wafer Lot under Different Work in Process Levels" Mathematics 9, no. 17: 2039. https://doi.org/10.3390/math9172039

APA StyleWang, J., Gao, P., Li, Z., & Bai, W. (2021). Hierarchical Transfer Learning for Cycle Time Forecasting for Semiconductor Wafer Lot under Different Work in Process Levels. Mathematics, 9(17), 2039. https://doi.org/10.3390/math9172039