Exploring the Frontier of Integrated Photonic Logic Gates: Breakthrough Designs and Promising Applications

Abstract

1. Introduction

2. Types and Characteristics of LGs

3. Materials for Photonic LGs

| Material | Type | Key Properties and Characteristics | Response Time | χ2 (pm/V) | χ3 (esu) |

|---|---|---|---|---|---|

| Silicon Nitride (Si3N4) [52,53] | Nonlinear | n2: ~10−16 cm2/W; Visible to MIR; Negligible two-photon absorption in telecom bands | ~ps | (centrosymmetric) | ~1 × 10−14 |

| Liquid Crystals [54,55] | Nonlinear | n2: up to 10−4 cm2/W; Visible to NIR; Exceptionally large optical nonlinearity | ms–µs | (centrosymmetric) | ~10−7 to 10−6 |

| Phthalocyanines (e.g., CuPc) [56,57] | Nonlinear | n2: ∼10−5 cm2/W; Visible; High third-order nonlinearity for optical switching | ns–ps | (centrosymmetric) | ~10−8 to 10−7 |

| Lithium Niobate (LiNbO3) [58] | EOs | r33: ~30 pm/V; 0.4–5 µm; Strong Pockels effect | ~ps | ~30 | ~10−14 to 10−13 |

| Barium Titanate (BaTiO3) [59] | EOs | r33: ~100 pm/V; 0.4–5 µm; Very high EO coefficient | ~ps | ~100–160 | ~10−12 |

| Ge2Sb2Te5 (GST) [60,61] | O-PCM | Large Δn; 1–18.5 µm; Fast phase change for nonvolatile switching | ~ns | (centrosymmetric) | ~10−11 to 10−10 |

| Ge2Sb2Se4Te1 (GSST) [62,63] | O-PCM | Δn ~2.0; 1–18.5 µm; Better transparency and loss profile | ~ns | (centrosymmetric) | ~10−11 to 10−10 |

| Vanadium Dioxide (VO2) [64] | O-PCM | Transition at ~68 °C; Visible to MIR; Ultrafast switching via insulator–metal transition | ~fs–ps | (centrosymmetric) | ~10−11 |

3.1. Nonlinear Materials

3.2. EO Materials

3.3. Optical Phase-Change Materials (O-PCMs)

4. Challenges in System Architecture, Programming, and Performance Metrics

5. Applications of Integrated Photonic LGs

5.1. Optical Phase-Change Materials (O-PCMs)

5.2. Data Center Optimization and Optical Network Management

5.3. Quantum Information Processing and Quantum Communication

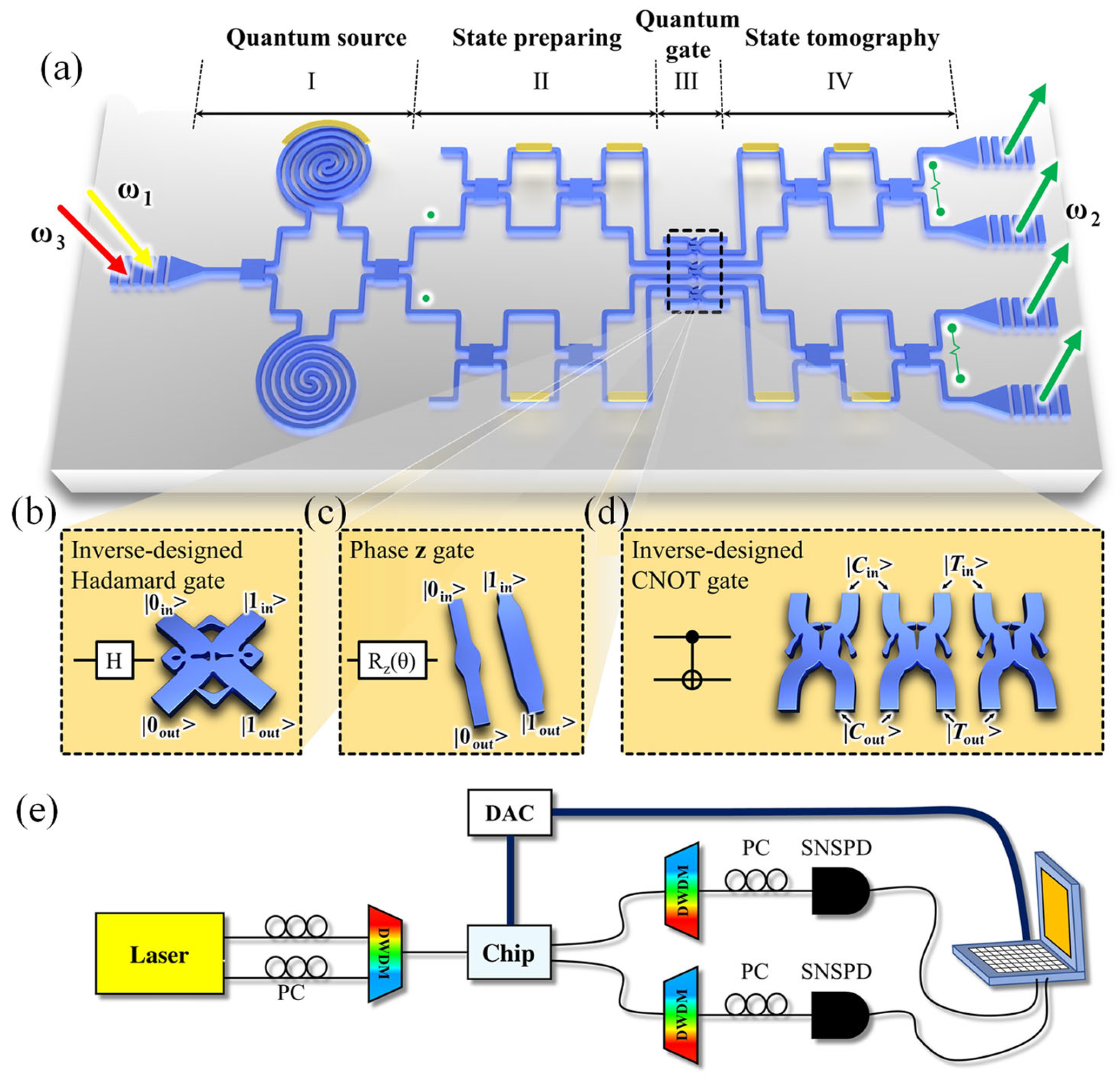

5.4. Neuromorphic and AI Hardware Acceleration

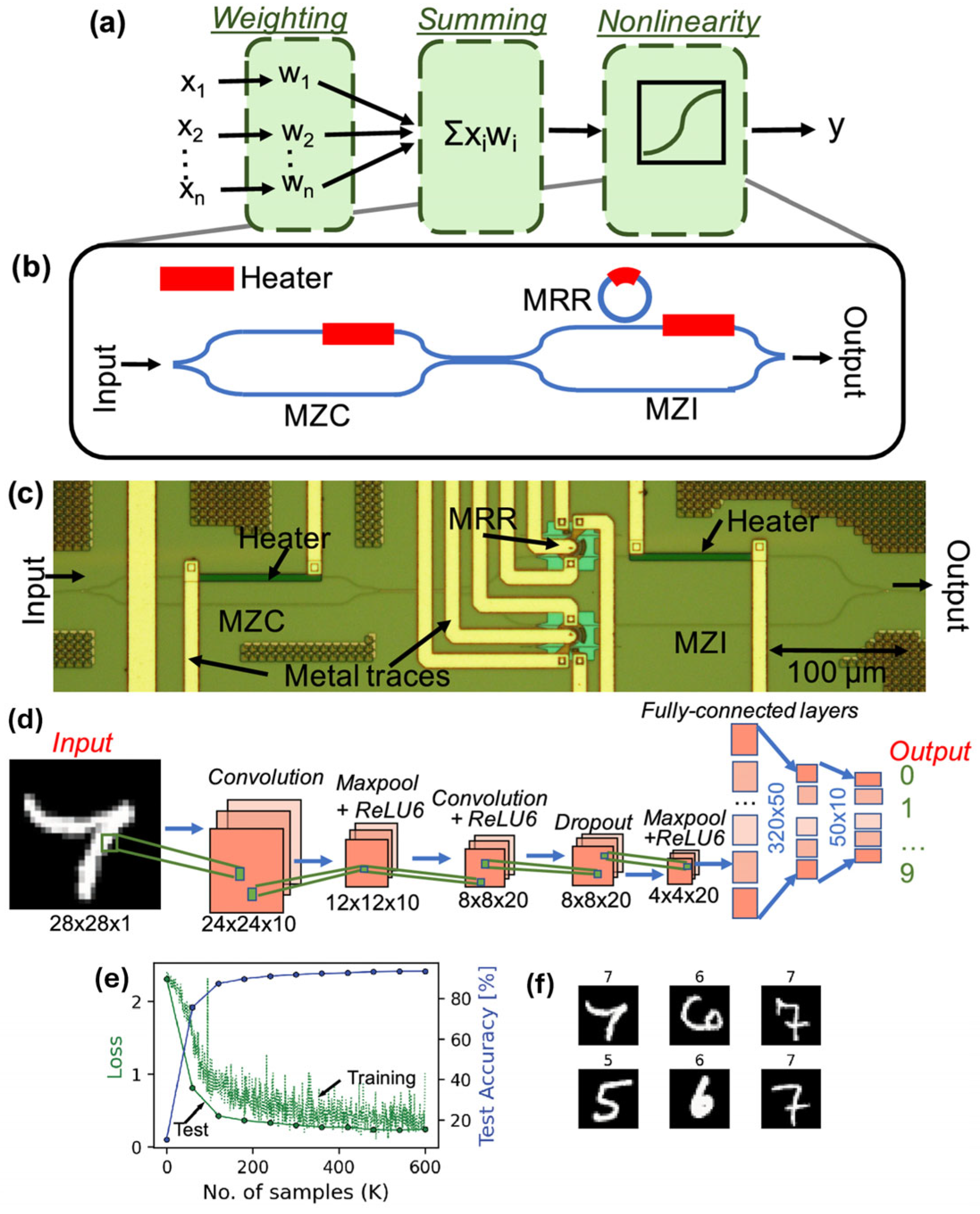

5.5. Secure Communication and Cryptographic Systems

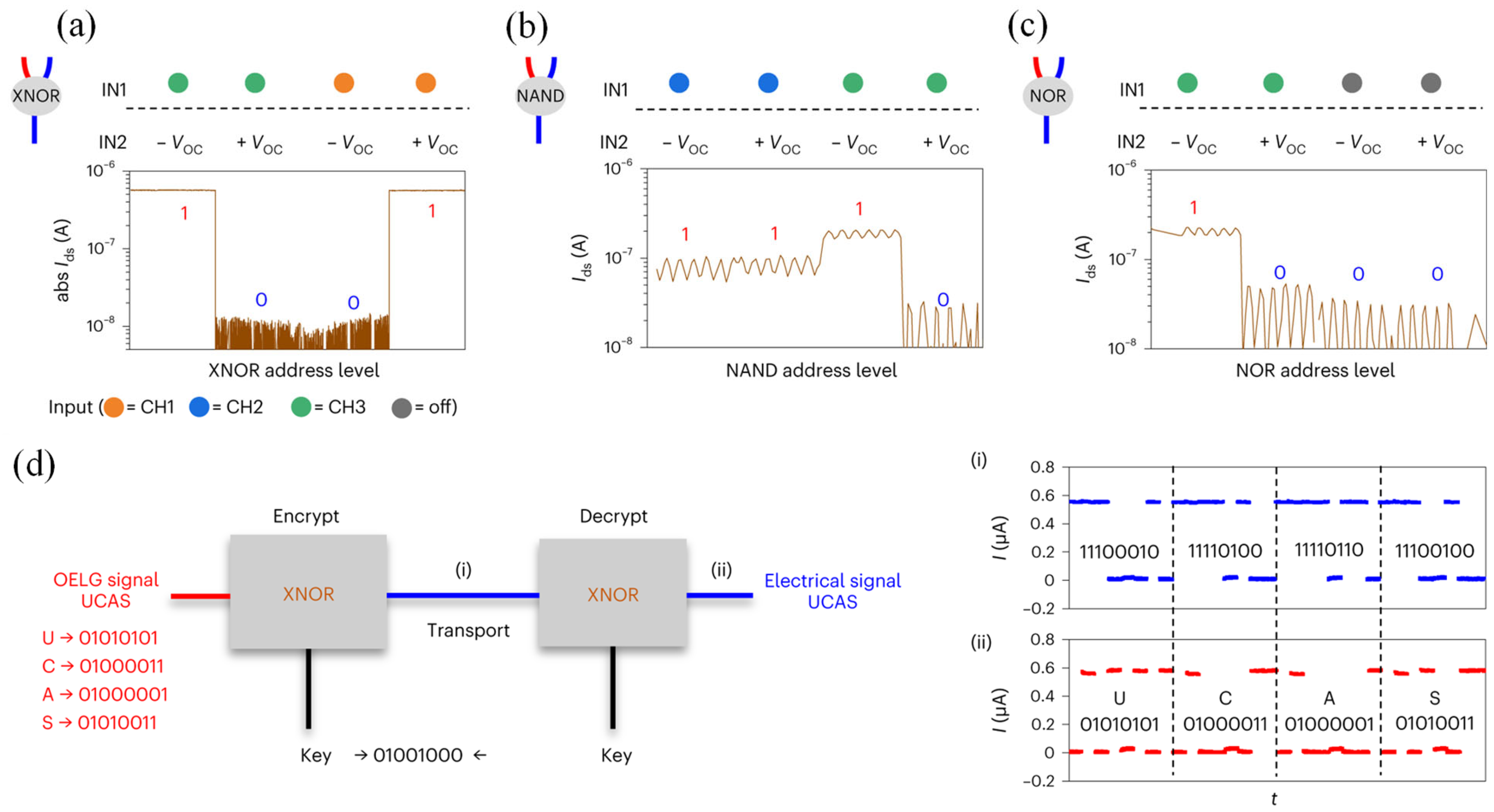

6. Roadmap for Integrated Photonic LGs

7. Challenges and Prospects

8. Concluding Remarks

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Correction Statement

References

- El Srouji, L.; Krishnan, A.; Ravichandran, R.; Lee, Y.; On, M.; Xiao, X.; Ben Yoo, S.J. Photonic and Optoelectronic Neuromorphic Computing. APL Photonics 2022, 7, 051101. [Google Scholar] [CrossRef]

- Ishihara, T.; Shiomi, J.; Hattori, N.; Masuda, Y.; Shinya, A.; Notomi, M. An Optical Neural Network Architecture Based on Highly Parallelized WDM-Multiplier-Accumulator. In Proceedings of the 2019 IEEE/ACM Workshop on Photonics-Optics Technology Oriented Networking, Information and Computing Systems (PHOTONICS), Denver, CO, USA, 18 November 2019; pp. 15–21. [Google Scholar]

- Kazanskiy, N.L.; Butt, M.A.; Khonina, S.N. Optical Computing: Status and Perspectives. Nanomaterials 2022, 12, 2171. [Google Scholar] [CrossRef]

- Zhang, Y.; Arias-Muñoz, J.C.; Cui, X.; Sun, Z. Prospect of Optical Chirality Logic Computing. Appl. Phys. Lett. 2023, 123, 240501. [Google Scholar] [CrossRef]

- Chen, H.; Chen, H.; Chan, E.H.W. Simple and Reconfigurable All-Optical Logic Gate. Opt. Laser Technol. 2024, 170, 110297. [Google Scholar] [CrossRef]

- Caballero, L.P.; Povinelli, M.L.; Ramirez, J.C.; Guimarães, P.S.S.; Neto, O.P.V. Photonic Crystal Integrated Logic Gates and Circuits. Opt. Express 2022, 30, 1976–1993. [Google Scholar] [CrossRef] [PubMed]

- Zhang, Y.; Peng, Z.; Wang, Z.; Wu, Y.; Hu, Y.; Wu, J.; Yang, J. Non-Volatile Reconfigurable Compact Photonic Logic Gates Based on Phase-Change Materials. Nanomaterials 2023, 13, 1375. [Google Scholar] [CrossRef] [PubMed]

- Jandieri, V.; Khomeriki, R.; Onoprishvili, T.; Werner, D.H.; Berakdar, J.; Erni, D. Functional All-Optical Logic Gates for True Time-Domain Signal Processing in Nonlinear Photonic Crystal Waveguides. Opt. Express 2020, 28, 18317–18331. [Google Scholar] [CrossRef]

- Zhang, Z.; Yang, J.; Bai, W.; Han, Y.; He, X.; Huang, J.; Chen, D.; Xu, S.; Xie, W. All-Optical Switch and Logic Gates Based on Hybrid Silicon-Ge2Sb2Te5 Metasurfaces. Appl. Opt. 2019, 58, 7392–7396. [Google Scholar] [CrossRef]

- Chapman, R.J.; Häusler, S.; Finco, G.; Kaufmann, F.; Grange, R. Quantum Logical Controlled-NOT Gate in a Lithium Niobate-on-Insulator Photonic Quantum Walk. Quantum Sci. Technol. 2023, 9, 015016. [Google Scholar] [CrossRef]

- Caballero, L.E.P.; Povinelli, M.; Ramirez, J.C.; Guimarães, P.; Neto, O.P.V. Design of Compact Integrated Photonic Crystal NAND and NOR Logic Gates. In Proceedings of the 2020 23rd Euromicro Conference on Digital System Design (DSD), Kranj, Slovenia, 26–28 August 2020; pp. 420–427. [Google Scholar]

- Kim, W.; Ahn, D.; Lee, M.; Lim, N.; Kim, H.; Pak, Y. From Light to Logic: Recent Advances in Optoelectronic Logic Gate. Small Sci. 2024, 4, 2400264. [Google Scholar] [CrossRef]

- Zhang, H.; Wang, B.; Wang, S. A Novel Method of High-Speed All-Optical Logic Gate Based on Metalens. Opt. Commun. 2025, 574, 131132. [Google Scholar] [CrossRef]

- Mahmoud, K.Z.; Smith, W.E.; Fishkin, M.; Miller, T.N. Data-Driven Logic Synthesizer for Acceleration of Forward Propagation in Artificial Neural Networks. In Proceedings of the 2015 33rd IEEE International Conference on Computer Design (ICCD), New York, NY, USA, 18–21 October 2015; pp. 435–438. [Google Scholar]

- Chandra, S.S.; Kannan, R.J.; Balaji, B.S.; Veeramachaneni, S.; Noor Mahammad, S. Efficient Design and Analysis of Secure CMOS Logic through Logic Encryption. Sci. Rep. 2023, 13, 1145. [Google Scholar] [CrossRef] [PubMed]

- Giorgio, A. Project and Implementation of a Quantum Logic Gate Emulator on FPGA Using a Model-Based Design Approach. IEEE Access 2024, 12, 41317–41353. [Google Scholar] [CrossRef]

- Zhu, H.; Lin, H.; Wu, S.; Luo, W.; Zhang, H.; Zhan, Y.; Wang, X.; Liu, A.; Kwek, L.C. Quantum Computing and Machine Learning on an Integrated Photonics Platform. Information 2024, 15, 95. [Google Scholar] [CrossRef]

- Fan, S.; Wang, Z.; Miller, D.A.B.; Villeneuve, P.R.; Haus, H.A.; Joannopoulos, J.D. Photonic Crystal for Communication Applications. In Proceedings of the Active and Passive Optical Components for WDM Communications II, Boston, MA, USA, 29 July–1 August 2002; SPIE: Bellingham, WA, USA, 2001; Volume 4870, pp. 339–347. [Google Scholar]

- Andalib, P.; Granpayeh, N. All-Optical Ultracompact Photonic Crystal AND Gate Based on Nonlinear Ring Resonators. JOSA B 2009, 26, 10–16. [Google Scholar] [CrossRef]

- He, T.; Ma, H.; Wang, Z.; Li, Q.; Liu, S.; Duan, S.; Xu, T.; Wang, J.; Wu, H.; Zhong, F.; et al. On-Chip Optoelectronic Logic Gates Operating in the Telecom Band. Nat. Photonics 2024, 18, 60–67. [Google Scholar] [CrossRef]

- van Niekerk, M.; Rizzo, A.; Rubio, H.; Leake, G.; Coleman, D.; Tison, C.; Fanto, M.; Bergman, K.; Preble, S. Massively Scalable Wavelength Diverse Integrated Photonic Linear Neuron. Neuromorphic Comput. Eng. 2022, 2, 034012. [Google Scholar] [CrossRef]

- Brites, C.D.S. Enlightening Molecular Logic: Basics, Tools and Techniques for Newcomers. Mater. Horiz. 2025, 12, 4016–4026. [Google Scholar] [CrossRef]

- Kaiser, J.; Datta, S. Probabilistic Computing with P-Bits. Appl. Phys. Lett. 2021, 119, 150503. [Google Scholar] [CrossRef]

- Erbas-Cakmak, S.; Kolemen, S.; Sedgwick, A.C.; Gunnlaugsson, T.; James, T.D.; Yoon, J.; Akkaya, E.U. Molecular Logic Gates: The Past, Present and Future. Chem. Soc. Rev. 2018, 47, 2228–2248. [Google Scholar] [CrossRef]

- Dias, G.G.; Souto, F.T. Architecture of Molecular Logic Gates: From Design to Application as Optical Detection Devices. Organics 2024, 5, 114–162. [Google Scholar] [CrossRef]

- Kim, J.; Han, J.-K.; Maeng, H.-Y.; Han, J.; Jeon, J.W.; Jang, Y.H.; Woo, K.S.; Choi, Y.-K.; Hwang, C.S. Fully CMOS-Based p-Bits with a Bistable Resistor for Probabilistic Computing. Adv. Funct. Mater. 2024, 34, 2307935. [Google Scholar] [CrossRef]

- Mokshin, P.V.; Golovashkin, D.L.; Pavelyev, V.S. Interference Logic Elements Based on a Y-Shaped Defect Photonic Crystal. Comput. Opt. 2023, 47, 895–900. [Google Scholar] [CrossRef]

- Baker, S.E.; Pocha, M.D.; Chang, A.S.P.; Sirbuly, D.J.; Cabrini, S.; Dhuey, S.D.; Bond, T.C.; Létant, S.E. Detection of Bio-Organism Simulants Using Random Binding on a Defect-Free Photonic Crystal. Appl. Phys. Lett. 2010, 97, 113701. [Google Scholar] [CrossRef]

- Englund, D.; Majumdar, A.; Faraon, A.; Toishi, M.; Stoltz, N.; Petroff, P.; Vučković, J. Resonant Excitation of a Quantum Dot Strongly Coupled to a Photonic Crystal Nanocavity. Phys. Rev. Lett. 2010, 104, 073904. [Google Scholar] [CrossRef] [PubMed]

- Knight, J.C.; Birks, T.A.; Russell, P.S.J.; Atkin, D.M. All-Silica Single-Mode Optical Fiber with Photonic Crystal Cladding. Opt. Lett. 1996, 21, 1547–1549. [Google Scholar] [CrossRef] [PubMed]

- Butt, M.A.; Khonina, S.N.; Kazanskiy, N.L. Recent Advances in Photonic Crystal Optical Devices: A Review. Opt. Laser Technol. 2021, 142, 107265. [Google Scholar] [CrossRef]

- Mohebzadeh-Bahabady, A.; Olyaee, S. All-Optical NOT and XOR Logic Gates Using Photonic Crystal Nano-Resonator and Based on an Interference Effect. IET Optoelectron. 2018, 12, 191–195. [Google Scholar] [CrossRef]

- Rao, D.G.S.; Swarnakar, S.; Kumar, S. Design of All-Optical Reversible Logic Gates Using Photonic Crystal Waveguides for Optical Computing and Photonic Integrated Circuits. Appl. Opt. 2020, 59, 11003–11012. [Google Scholar] [CrossRef]

- Kazanskiy, N.L.; Khonina, S.N. Metasurfaces and Perspectives of Computer Optics. Comput. Opt. 2025, 49, 349–361. [Google Scholar]

- Kizhakkakath, F.; Ravindran, S.; Park, K.; Alameh, K.; Lee, Y.T. Realization and Optimization of Optical Logic Gates Using Bias Assisted Carrier-Injected Triple Parallel Microring Resonators. Results Opt. 2021, 4, 100090. [Google Scholar] [CrossRef]

- Xu, Q.; Lipson, M. All-Optical Logic Based on Silicon Micro-Ring Resonators. Opt. Express 2007, 15, 924–929. [Google Scholar] [CrossRef] [PubMed]

- Kizhakkakath, F.; Ravindran, S. Microring Resonator Based Optical Logic Gates. ISSS J. Micro Smart Syst. 2022, 11, 295–316. [Google Scholar] [CrossRef]

- Al-Musawi, H.K.; Al-Janabi, A.K.; Al-abassi, S.A.W.; Abusiba, N.A.-H.A.; Al-Fatlawi, N.A.-H.Q. Plasmonic Logic Gates Based on Dielectric-Metal-Dielectric Design with Two Optical Communication Bands. Optik 2020, 223, 165416. [Google Scholar] [CrossRef]

- El Haffar, R.; Mahboub, O.; Farkhsi, A.; Figuigue, M. All-Optical Logic Gates Using a Plasmonic MIM Waveguide and Elliptical Ring Resonator. Plasmonics 2022, 17, 831–842. [Google Scholar] [CrossRef]

- Butt, M.A. Insight into Plasmonics: Resurrection of Modern-Day Science (Invited). Comput. Opt. 2024, 48, 5–17. [Google Scholar] [CrossRef]

- Alizadeh, A.H.; Rashidi, A. Implementation of Optical OR and NOR Gates Using Mach-Zehnder Interferometers. J. Phys. Commun. 2020, 4, 085014. [Google Scholar] [CrossRef]

- Singh, P.; Tripathi, D.K.; Jaiswal, S.; Dixit, H.K. Design and Analysis of All-Optical AND, XOR and OR Gates Based on SOA–MZI Configuration. Opt. Laser Technol. 2015, 66, 35–44. [Google Scholar] [CrossRef]

- Kim, J.-Y.; Kang, J.-M.; Kim, T.-Y.; Han, S.-K. All-Optical Multiple Logic Gates with XOR, NOR, OR, and NAND Functions Using Parallel SOA-MZI Structures: Theory and Experiment. J. Light. Technol. 2006, 24, 3392. [Google Scholar]

- Dan, Y.; Fan, Z.; Sun, X.; Zhang, T.; Xu, K. All-Type Optical Logic Gates Using Plasmonic Coding Metamaterials and Multi-Objective Optimization. Opt. Express 2022, 30, 11633–11646. [Google Scholar] [CrossRef]

- Liu, L.; Liu, P.; Ga, L.; Ai, J. Advances in Applications of Molecular Logic Gates. ACS Omega 2021, 6, 30189–30204. [Google Scholar] [CrossRef]

- Emanuelson, C.; Bardhan, A.; Deiters, A. DNA Computing: NOT Logic Gates See the Light. ACS Synth. Biol. 2021, 10, 1682–1689. [Google Scholar] [CrossRef] [PubMed]

- Ahmed, W.S.; Yaseen, N.A.; Al-Chaabawi, N.J. Design, Simulation, and Investigation of Basic Logic Gates by Using NAND Logic Gate. AIP Conf. Proc. 2023, 2591, 020006. [Google Scholar] [CrossRef]

- Kotb, A.; Guo, C. All-Optical Multifunctional AND, NOR, and XNOR Logic Gates Using Semiconductor Optical Amplifiers. Phys. Scr. 2020, 95, 085506. [Google Scholar] [CrossRef]

- Jo, S.B.; Kang, J.; Cho, J.H. Recent Advances on Multivalued Logic Gates: A Materials Perspective. Adv. Sci. 2021, 8, 2004216. [Google Scholar] [CrossRef]

- Mercado-Zúñiga, C.; Vargas-García, J.R.; Cervantes-Sodi, F.; Trejo-Valdez, M.; Torres-Martínez, R.; Torres-Torres, C. Photoconductive Logic Gate Based on Platinum Decorated Carbon Nanotubes. Appl. Opt. 2013, 52, E22–E27. [Google Scholar] [CrossRef]

- Amiri, I.S.; Palai, G.; Tripathy, S.K.; Nayak, S.R. Realisation of All Photonic Logic Gates Using Plasmonic-Based Photonic Structure through Bandgap Analysis. Optik 2019, 194, 163123. [Google Scholar] [CrossRef]

- Tan, D.T.H.; Ooi, K.J.A.; Ng, D.K.T. Nonlinear Optics on Silicon-Rich Nitride—A High Nonlinear Figure of Merit CMOS Platform [Invited]. Photonics Res. 2018, 6, B50–B66. [Google Scholar] [CrossRef]

- Ding, B.; Yu, X.; Lu, H.; Xiu, X.; Zhang, C.; Yang, C.; Jiang, S.; Man, B.; Ning, T.; Huo, Y. Third-Order Optical Nonlinearity in Silicon Nitride Films Prepared Using Magnetron Sputtering and Application for Optical Bistability. J. Appl. Phys. 2019, 125, 113102. [Google Scholar] [CrossRef]

- Yu, P.; Chen, X.; Zhang, D.; Gao, J.; Ma, C.; Zhang, C.; He, Z.; Wang, D.; Miao, Z. Polymer-Dispersed Liquid Crystal Films on Flexible Substrates with Excellent Bending Resistance and Spacing Stability. Langmuir 2023, 39, 610–618. [Google Scholar] [CrossRef]

- Maingot, B.; Neradovskaia, E.; Claudet, C.; Forget, N.; Jullien, A. Measurement of Nonlinear Refractive Indices of Bulk and Liquid Crystals by Nonlinear Chirped Interferometry. Opt. Lett. 2023, 48, 3243–3246. [Google Scholar] [CrossRef] [PubMed]

- Li, F.; He, Z.; Li, M.; Lu, P. Three-Photon Absorption of Copper Phthalocyanine Solution by Femtosecond Z-Scan Technique. Mater. Lett. 2013, 111, 81–84. [Google Scholar] [CrossRef]

- Zou, D.; Zhao, W.; Yang, C. Magnetic Field-Driven Spintronic Logic Gates in One-Dimensional Manganese Phthalocyanine Nanoribbons Based Molecular Spintronic Devices. Org. Electron. 2019, 69, 120–127. [Google Scholar] [CrossRef]

- Rabiei, P.; Ma, J.; Khan, S.; Chiles, J.; Fathpour, S. Heterogeneous Lithium Niobate Photonics on Silicon Substrates. Opt. Express 2013, 21, 25573–25581. [Google Scholar] [CrossRef]

- Karvounis, A.; Timpu, F.; Vogler-Neuling, V.V.; Savo, R.; Grange, R. Barium Titanate Nanostructures and Thin Films for Photonics. Adv. Opt. Mater. 2020, 8, 2001249. [Google Scholar] [CrossRef]

- Liang, J.; Chen, G.; Niu, X.; Zhu, Z.; Dong, Y.; Wang, Y.; Wei, Q.-H.; Pan, J.; Li, Y.; Gu, C.; et al. Enhanced Surface Effects and Optical Property Modulation of Ge2Sb2Te5 by Pulsed Laser Irradiation. Opt. Mater. Express 2023, 13, 566–574. [Google Scholar] [CrossRef]

- Panda, A.; Vigneswaran, D.; Pukhrambam, P.D.; Ayyanar, N.; Nguyen, T.K. Design and Performance Analysis of Reconfigurable 1D Photonic Crystal Biosensor Employing Ge2Sb2Te5 (GST) for Detection of Women Reproductive Hormones. IEEE Trans. NanoBiosci. 2022, 21, 21–28. [Google Scholar] [CrossRef]

- Delaney, M.; Zeimpekis, I.; Lawson, D.; Hewak, D.W.; Muskens, O.L. A New Family of Ultralow Loss Reversible Phase-Change Materials for Photonic Integrated Circuits: Sb2S3 and Sb2Se3. Adv. Funct. Mater. 2020, 30, 2002447. [Google Scholar] [CrossRef]

- Zhang, Y.; Chou, J.B.; Li, J.; Li, H.; Du, Q.; Yadav, A.; Zhou, S.; Shalaginov, M.Y.; Fang, Z.; Zhong, H.; et al. Broadband Transparent Optical Phase Change Materials for High-Performance Nonvolatile Photonics. Nat. Commun. 2019, 10, 4279. [Google Scholar] [CrossRef]

- Wang, B.; Chen, S.; Huang, Z.; Fu, M. Optical Nonlinearities of Nanostructured VO2 Thin Films with Low Phase Transition Temperature. Appl. Surf. Sci. 2012, 258, 5319–5322. [Google Scholar] [CrossRef]

- Miyoshi, Y.; Ikeda, K.; Tobioka, H.; Inoue, T.; Namiki, S.; Kitayama, K. Ultrafast All-Optical Logic Gate Using a Nonlinear Optical Loop Mirror Based Multi-Periodic Transfer Function. Opt. Express 2008, 16, 2570–2577. [Google Scholar] [CrossRef]

- Xu, X.; Cui, Z.; Yang, Y.; Zhang, Y.; Li, Q.; Tong, L.; Li, J.; Zhang, X.; Wu, Y. Large Optical Nonlinearity Enhancement and All-Optical Logic Gate Implementation in Silver-Modified Violet Phosphorus. Laser Photonics Rev. 2025, 19, 2401521. [Google Scholar] [CrossRef]

- Fujisawa, T.; Koshiba, M. All-Optical Logic Gates Based on Nonlinear Slot-Waveguide Couplers. JOSA B 2006, 23, 684–691. [Google Scholar] [CrossRef]

- Zhang, L.; Agarwal, A.M.; Kimerling, L.C.; Michel, J. Nonlinear Group IV Photonics Based on Silicon and Germanium: From near-Infrared to Mid-Infrared. Nanophotonics 2014, 3, 247–268. [Google Scholar] [CrossRef]

- Palatnikov, M.N.; Kadetova, A.V.; Smirnov, M.V.; Sidorova, O.V.; Vorobev, D.A. Nonlinear Optical Properties of Lithium Niobate Crystals Doped with Alkaline Earth and Rare Earth Elements. Opt. Mater. 2022, 131, 112631. [Google Scholar] [CrossRef]

- Slovick, B.; Zipp, L.; Krishnamurthy, S. Indium Phosphide Metasurface with Enhanced Nonlinear Absorption. Sci. Rep. 2017, 7, 17245. [Google Scholar] [CrossRef]

- García-Beltrán, G.; Mercado-Zúñiga, C.; Gallegos-García, G.; Kumari, P.; Martínez-González, C.L.; Torres-Torres, C. All-Optical Flip-Flop by Carbon/Metal Nanostructures in a Multi-Wave Mixing. Optik 2024, 301, 171693. [Google Scholar] [CrossRef]

- Ghadi, A.; Darzi, B. All-Optical Nano Logical Gates AND, NOR, OR, and NOT Based on Plasmonic Waveguides with Kerr Nonlinear Cavity. Opt. Laser Technol. 2023, 157, 108651. [Google Scholar] [CrossRef]

- Sharifi, H.; Hamidi, S.M.; Navi, K. All-Optical Photonic Crystal Logic Gates Using Nonlinear Directional Coupler. Photonics Nanostruct.-Fundam. Appl. 2017, 27, 55–63. [Google Scholar] [CrossRef]

- Lu, C.; Zhu, B.; Zhu, C.; Ge, L.; Liu, Y.; Chen, Y.; Chen, X. All-Optical Logic Gates and a Half-Adder Based on Lithium Niobate Photonic Crystal Micro-Cavities. Chin. Opt. Lett. 2019, 17, 072301. [Google Scholar] [CrossRef]

- Yang, X.; Hu, X.; Yang, H.; Gong, Q. Ultracompact All-Optical Logic Gates Based on Nonlinear Plasmonic Nanocavities. Nanophotonics 2017, 6, 365–376. [Google Scholar] [CrossRef]

- Ying, Z.; Feng, C.; Zhao, Z.; Soref, R.; Pan, D.; Chen, R.T. Integrated Multi-Operand Electro-Optic Logic Gates for Optical Computing. Appl. Phys. Lett. 2019, 115, 171104. [Google Scholar] [CrossRef]

- Sarkar, M.; Chakraborty, R.; Taki, G.S.; Chakraborty, A.K. Design of Basic Logic Gates Using Optical Threshold Logic. Eng. Res. Express 2021, 3, 035021. [Google Scholar] [CrossRef]

- Kaur, S.; Singh, M.L.; Priyanka; Singh, M. Performance Comparison of All-Optical Logic Gates Using Electro-Optic Effect in MZI-Based Waveguide Switch at 1.46 µm. J. Opt. Commun. 2023, 44, s231–s243. [Google Scholar] [CrossRef]

- Kumar, M.; Kumar, A.; Jindal, S.K.; Raghuwanshi, S.K. Comprehensive Study of All-in-One Simultaneous Multiple Optical Logic Gate Devices Using Mach–Zehnder Interferometer Based on the Electro-Optic Effect. IETE Tech. Rev. 2022, 39, 662–674. [Google Scholar] [CrossRef]

- Das, S.; Sinha, N.; Pal, S.; Bhowmik, B.B. An Electro-Optic Reconfigurable OR to Ex-OR Gate Based on Microring Resonator Loaded on Mach–Zehnder Interferometric Structure. Results Opt. 2022, 9, 100299. [Google Scholar] [CrossRef]

- Das, S.K.; Pahari, N. A New Scheme of 2:1 Photonic Multiplexer and Multiplexer-Based NOT, OR, AND Logic Gates in Electro-Optic Mach–Zehnder Interferometer. E-Prime-Adv. Electr. Eng. Electron. Energy 2023, 6, 100375. [Google Scholar] [CrossRef]

- Yadav, A.; Kumar, A.; Prakash, A. Design and Analysis of Optical Switches Using Electro-Optic Effect Based Mach-Zehnder Interferometer Structures. Mater. Today Proc. 2022, 56, 462–467. [Google Scholar] [CrossRef]

- Ooi, K.J.A.; Chu, H.S.; Bai, P.; Ang, L.K. Electro-Optical Graphene Plasmonic Logic Gates. Opt. Lett. 2014, 39, 1629–1632. [Google Scholar] [CrossRef]

- Ghosh, R.R.; Dhawan, A. Integrated Non-Volatile Plasmonic Switches Based on Phase-Change-Materials and Their Application to Plasmonic Logic Circuits. Sci. Rep. 2021, 11, 18811. [Google Scholar] [CrossRef]

- Wang, X.; Qi, H.; Hu, X.; Yu, Z.; Ding, S.; Du, Z.; Gong, Q. Advances in Photonic Devices Based on Optical Phase-Change Materials. Molecules 2021, 26, 2813. [Google Scholar] [CrossRef] [PubMed]

- Prabhathan, P.; Sreekanth, K.V.; Teng, J.; Ko, J.H.; Yoo, Y.J.; Jeong, H.-H.; Lee, Y.; Zhang, S.; Cao, T.; Popescu, C.-C.; et al. Roadmap for Phase Change Materials in Photonics and Beyond. iScience 2023, 26, 107946. [Google Scholar] [CrossRef] [PubMed]

- Lawson, D.; Blundell, S.; Ebert, M.; Muskens, O.L.; Zeimpekis, I. Optical Switching beyond a Million Cycles of Low-Loss Phase Change Material Sb2Se3. Opt. Mater. Express 2024, 14, 22–38. [Google Scholar] [CrossRef]

- Tripathi, D.; Hegde, R.S. Phase Change Material Metasurface Loading Enables an Ultrafast All-Optically Switchable, Compact, Narrowband Freespace Optical Filter. Opt. Commun. 2024, 569, 130788. [Google Scholar] [CrossRef]

- Wredh, S.; Wang, Y.; Yang, J.K.W.; Simpson, R.E. Multi-Level Optical Switching by Amorphization in Single- and Multi-Phase Change Material Structures. Adv. Opt. Mater. 2024, 12, 2301835. [Google Scholar] [CrossRef]

- Mohebbi, Z.; Nozhat, N.; Emami, F. High Contrast All-Optical Logic Gates Based on 2D Nonlinear Photonic Crystal. Opt. Commun. 2015, 355, 130–136. [Google Scholar] [CrossRef]

- Wang, C.-Y.; Chen, C.-W.; Jau, H.-C.; Li, C.-C.; Cheng, C.-Y.; Wang, C.-T.; Leng, S.-E.; Khoo, I.-C.; Lin, T.-H. All-Optical Transistor- and Diode-Action and Logic Gates Based on Anisotropic Nonlinear Responsive Liquid Crystal. Sci. Rep. 2016, 6, 30873. [Google Scholar] [CrossRef]

- Ying, Z.; Soref, R. Electro-Optical Logic Using Dual-Nanobeam Mach-Zehnder Interferometer Switches. Opt. Express 2021, 29, 12801–12812. [Google Scholar] [CrossRef]

- Ríos Ocampo, C.A.; Zhang, Y.; Shalaginov, M.; Gu, T.; Hu, J. 6—New Phase-Change Materials for Photonic Computing and Beyond. In Phase Change Materials-Based Photonic Computing; Bhaskaran, H., Pernice, W.H.P., Eds.; Materials Today; Elsevier: Amsterdam, The Netherlands, 2024; pp. 145–192. ISBN 978-0-12-823491-4. [Google Scholar]

- Cheng, Z.; Ríos, C.; Youngblood, N.; Wright, C.D.; Pernice, W.H.P.; Bhaskaran, H. Device-Level Photonic Memories and Logic Applications Using Phase-Change Materials. Adv. Mater. 2018, 30, 1802435. [Google Scholar] [CrossRef]

- Ruhul Fatin, M.A.; Gostimirovic, D.; Ye, W.N. Reconfigurable Optical Logic in Silicon Platform. Sci. Rep. 2024, 14, 5950. [Google Scholar] [CrossRef]

- Vadukanathan, A.; Suyambrakasam, G.; Sivaraj, P. Design of All-Optical NOR and NAND Gate Using Hybrid Material Corner Scatters in Photonic Crystal Ring Resonators. Phys. Scr. 2025, 100, 045527. [Google Scholar] [CrossRef]

- Zhang, H.; Gießübel, M.; Dharpure, P.; Albert, A.; Niestierkina, V.; Mulvaney, P.; Thelakkat, M.; Köhler, J. Demonstration of an All-Optical AND Gate Mediated by Photochromic Molecules. Adv. Funct. Mater. 2025, 2507180. [Google Scholar] [CrossRef]

- Shreya, K.; Shaik, E.H.; Balaji, V.R.; Dhanabalan, S.S.; Sridarshini, T.; Hegde, G. PhC Structure for High Contrast XOR/OR/NOT Logic. Opt. Quantum Electron. 2024, 56, 854. [Google Scholar] [CrossRef]

- Chen, T.; Dang, Z.; Ding, Z.; Zhang, Z. Programmable Parallel Optical Logic Gates on a Multimode Waveguide Engine. Photonics 2022, 9, 736. [Google Scholar] [CrossRef]

- Ashtiani, F. Universal Optical Logic Gates on a Programmable Silicon Photonic Platform. In Proceedings of the Optical Fiber Communication Conference (OFC) 2024 (2023), San Diego, CA, USA, 24–28 March 2024; Optica Publishing Group: Washington, DC, USA, 2024; W3B.3. [Google Scholar]

- He, L.; Zhang, W.X.; Zhang, X.D. Topological All-Optical Logic Gates Based on Two-Dimensional Photonic Crystals. Opt. Express 2019, 27, 25841–25859. [Google Scholar] [CrossRef] [PubMed]

- Lin, C.-E.; Lu, Y.-H.; Zhou, M.-T.; Chen, C.-C. Reconfigurable Electro-Optical Logic Gates Using a 2-Layer Multilayer Perceptron. Sci. Rep. 2022, 12, 14203. [Google Scholar] [CrossRef] [PubMed]

- Fernandes, C.A.R.; de Oliveira, M.E.N.; Rocha, D.S.; de Alexandria, A.R.; Guimarães, G.F. Design of Optical Logic Gates Using Mach–Zehnder Interferometers and Machine Learning. J. Light. Technol. 2022, 40, 6240–6248. [Google Scholar] [CrossRef]

- Boletti, A.; Giacomuzzi, D.; Parladori, G.; Boffi, P.; Martinelli, M. Performance Comparison between Electrical and Optical Backplanes. In Proceedings of the 2013 Conference on Lasers & Electro-Optics Europe & International Quantum Electronics Conference CLEO EUROPE/IQEC, Munich, Germany, 12–16 May 2013; p. 1. [Google Scholar]

- Tang, G.; Li, C.; Zhang, X.; Rhee, D.M. Thermal Management Solutions and Design Guidelines for Silicon Based Photonic Integrated Modules. In Proceedings of the 2015 IEEE 17th Electronics Packaging and Technology Conference (EPTC), Singapore, 2–4 December 2015; pp. 1–6. [Google Scholar]

- Pandey, S.; Teixeira, A.; Lima, M. Temperature Monitoring in PIC Surface. Photonics 2025, 12, 54. [Google Scholar] [CrossRef]

- Ouyang, J.; Liu, S.; Yang, Z.; Wang, W.; Feng, X.; Li, Y.; Huang, Y. 16-Channel Photonic Solver for Optimization Problems on a Silicon Chip. Chip 2025, 4, 100117. [Google Scholar] [CrossRef]

- Kazakov, D.; Opačak, N.; Pilat, F.; Wang, Y.; Belyanin, A.; Schwarz, B.; Capasso, F. Cluster Synchronization in a Semiconductor Laser. APL Photonics 2024, 9, 026104. [Google Scholar] [CrossRef]

- Pirzadi, M.; Mir, A.; Bodaghi, D. Realization of Ultra-Accurate and Compact All-Optical Photonic Crystal OR Logic Gate. IEEE Photonics Technol. Lett. 2016, 28, 2387–2390. [Google Scholar] [CrossRef]

- Zhang, Z.-K.; Zhang, T.; Chong, M.-Z.; Dang, Z.; Dai, Y.; Shang, H.; Zhou, Y.; Zheng, Z.; Zhang, H.; Liu, P.-K.; et al. All-Optical Single-Channel Plasmonic Logic Gates. Nano Lett. 2025, 25, 1367–1372. [Google Scholar] [CrossRef]

- Haque, M.A.; Rahad, R.; Faruque, M.O. Optical Computing at the Subwavelength Scale: A Multifunctional MIM Plasmonic Logic Gate. Appl. Opt. 2024, 63, 6364–6370. [Google Scholar] [CrossRef]

- Cassinerio, M.; Ciocchini, N.; Ielmini, D. Logic Computation in Phase Change Materials by Threshold and Memory Switching. Adv. Mater. 2013, 25, 5975–5980. [Google Scholar] [CrossRef]

- Hoffer, B.; Wainstein, N.; Neumann, C.M.; Pop, E.; Yalon, E.; Kvatinsky, S. Stateful Logic Using Phase Change Memory. IEEE J. Explor. Solid-State Comput. Devices Circuits 2022, 8, 77–83. [Google Scholar] [CrossRef]

- Smith, S.D. Optical Bistability, Photonic Logic, and Optical Computation. Appl. Opt. 1986, 25, 1550–1564. [Google Scholar] [CrossRef] [PubMed]

- Singh, J.J.; Dhawan, D.; Gupta, N. All-Optical Photonic Crystal Logic Gates for Optical Computing: An Extensive Review. Opt. Eng. 2020, 59, 110901. [Google Scholar] [CrossRef]

- Zhao, Z.; Wang, Z.; Ying, Z.; Dhar, S.; Chen, R.T.; Pan, D.Z. Optical Computing on Silicon-on-Insulator-Based Photonic Integrated Circuits. In Proceedings of the 2017 IEEE 12th International Conference on ASIC (ASICON), Guiyang, China, 25–28 October 2017. [Google Scholar]

- Kita, S.; Nozaki, K.; Takata, K.; Shinya, A.; Notomi, M. Ultrashort Low-Loss Ψ Gates for Linear Optical Logic on Si Photonics Platform. Commun. Phys. 2020, 3, 1–8. [Google Scholar] [CrossRef]

- Thankaraj, B.S.; Ramasamy, A. Revolution of Optical Computing Logic Gates Based on Its Applications: An Extensive Survey. Opt. Eng. 2022, 61, 110901. [Google Scholar] [CrossRef]

- Hu, J.; Mengu, D.; Tzarouchis, D.C.; Edwards, B.; Engheta, N.; Ozcan, A. Diffractive Optical Computing in Free Space. Nat. Commun. 2024, 15, 1525. [Google Scholar] [CrossRef]

- Zhu, H.H.; Zou, J.; Zhang, H.; Shi, Y.Z.; Luo, S.B.; Wang, N.; Cai, H.; Wan, L.X.; Wang, B.; Jiang, X.D.; et al. Space-Efficient Optical Computing with an Integrated Chip Diffractive Neural Network. Nat. Commun. 2022, 13, 1044. [Google Scholar] [CrossRef]

- Shahi, M.; Sepahvandi, V.; Saghaei, H.; Nurmohammadi, T.; Bahloul, F.; Jafari, B.; Karar, A.S.; Soroosh, M.; Adibnia, E. Design of a Photonic Crystal 4 × 2 Encoder Based on All-Optical NOT and XOR Logic Gates. Opt. Quantum Electron. 2025, 57, 221. [Google Scholar] [CrossRef]

- Khonina, S.N.; Kazanskiy, N.L.; Skidanov, R.V.; Butt, M.A. Exploring Types of Photonic Neural Networks for Imaging and Computing—A Review. Nanomaterials 2024, 14, 697. [Google Scholar] [CrossRef] [PubMed]

- Zhu, A.; Song, L.; Cheng, L.; Hu, C.; Mahapatra, R. An Ultra-Compact and Highly Stable Optical Numerical Comparator Based on Y-Shaped Graphene Nanoribbons. Eur. Phys. J. D 2023, 77, 169. [Google Scholar] [CrossRef]

- Wang, H.; Xu, H.; Huang, H.; Zhou, N.; Zhang, H.; Li, J. Ultra-Broadband and Ultra-Compact Chip-Integrated Logic Gates Based on an Inverse Design Method. Opt. Laser Technol. 2024, 169, 110192. [Google Scholar] [CrossRef]

- Zarei, S.; Khavasi, A. Realization of Optical Logic Gates Using On-Chip Diffractive Optical Neural Networks. Sci. Rep. 2022, 12, 15747. [Google Scholar] [CrossRef]

- Andriolli, N.; Giorgetti, A.; Castoldi, P.; Cecchetti, G.; Cerutti, I.; Sambo, N.; Sgambelluri, A.; Valcarenghi, L.; Cugini, F.; Martini, B.; et al. Optical Networks Management and Control: A Review and Recent Challenges. Opt. Switch. Netw. 2022, 44, 100652. [Google Scholar] [CrossRef]

- Barry, L.P.; Wang, J.; McArdle, C.; Kilper, D. Optical Switching in Datacenters: Architectures Based on Optical Circuit Switching. In Optical Switching in Next Generation Data Centers; Testa, F., Pavesi, L., Eds.; Springer International Publishing: Cham, Switzerland, 2018; pp. 23–44. ISBN 978-3-319-61052-8. [Google Scholar]

- Chander, U.B. Analysis on Implementation of Optical Network Management Solution with Hadoop Architecture. In Proceedings of the 2018 Tenth International Conference on Advanced Computing (ICoAC), Chennai, India, 13–15 December 2018; pp. 7–12. [Google Scholar]

- Furdek, M.; Natalino, C.; Giglio, A.D.; Schiano, M. Optical Network Security Management: Requirements, Architecture, and Efficient Machine Learning Models for Detection of Evolving Threats [Invited]. J. Opt. Commun. Netw. 2021, 13, A144–A155. [Google Scholar] [CrossRef]

- Cheng, Q.; Bahadori, M.; Glick, M.; Rumley, S.; Bergman, K. Recent Advances in Optical Technologies for Data Centers: A Review. Optica 2018, 5, 1354–1370. [Google Scholar] [CrossRef]

- Dong, M.; Wang, H.; Yang, H.; Zhou, N.; Lu, C.; Xu, H.; Zhang, Z. Ultra-Broadband Multi-Character Logic Gates Integrated by Inverse Designed Logic Units. Opt. Commun. 2025, 579, 131545. [Google Scholar] [CrossRef]

- Dalaka, E.; Hill, J.S.; Booth, J.H.H.; Popczyk, A.; Pulver, S.R.; Gather, M.C.; Schubert, M. Deformable Microlaser Force Sensing. Light Sci. Appl. 2024, 13, 129. [Google Scholar] [CrossRef] [PubMed]

- Bogaerts, W.; Pérez, D.; Capmany, J.; Miller, D.A.B.; Poon, J.; Englund, D.; Morichetti, F.; Melloni, A. Programmable Photonic Circuits. Nature 2020, 586, 207–216. [Google Scholar] [CrossRef] [PubMed]

- Li, Y.; Zhang, H.; Zhu, H.H.; Kwek, L.C.; Liu, A.Q. Quantum Photonic Chip-Based Realization of Logic Gates. In Proceedings of the CLEO 2023 (2023), San Jose, CA, USA, 7–12 May 2023; Optica Publishing Group: Washington, DC, USA, 2023; FM3A.3. [Google Scholar]

- Shen, Y.; Harris, N.C.; Skirlo, S.; Prabhu, M.; Baehr-Jones, T.; Hochberg, M.; Sun, X.; Zhao, S.; Larochelle, H.; Englund, D.; et al. Deep Learning with Coherent Nanophotonic Circuits. Nat. Photonics 2017, 11, 441–446. [Google Scholar] [CrossRef]

- Shi, S.; Xu, B.; Zhang, K.; Ye, G.-S.; Xiang, D.-S.; Liu, Y.; Wang, J.; Su, D.; Li, L. High-Fidelity Photonic Quantum Logic Gate Based on near-Optimal Rydberg Single-Photon Source. Nat. Commun. 2022, 13, 4454. [Google Scholar] [CrossRef]

- Ma, S.; Chen, Z.; Sun, H.; Dutta, N.K. High Speed All Optical Logic Gates Based on Quantum Dot Semiconductor Optical Amplifiers. Opt. Express 2010, 18, 6417–6422. [Google Scholar] [CrossRef]

- De, P.; Ranwa, S.; Mukhopadhyay, S. Implementation of All-Optical Toffoli Gate by 2D Si–Air Photonic Crystal. IET Optoelectron. 2021, 15, 139–148. [Google Scholar] [CrossRef]

- He, L.; Liu, D.; Gao, J.; Zhang, W.; Zhang, H.; Feng, X.; Huang, Y.; Cui, K.; Liu, F.; Zhang, W.; et al. Super-Compact Universal Quantum Logic Gates with Inverse-Designed Elements. Sci. Adv. 2023, 9, eadg6685. [Google Scholar] [CrossRef]

- Xu, Y.; Zhang, X.; Fu, Y.; Liu, Y. Interfacing Photonics with Artificial Intelligence: An Innovative Design Strategy for Photonic Structures and Devices Based on Artificial Neural Networks. Photonics Res. 2021, 9, B135–B152. [Google Scholar] [CrossRef]

- Hassija, V.; Chamola, V.; Mahapatra, A.; Singal, A.; Goel, D.; Huang, K.; Scardapane, S.; Spinelli, I.; Mahmud, M.; Hussain, A. Interpreting Black-Box Models: A Review on Explainable Artificial Intelligence. Cogn. Comput. 2024, 16, 45–74. [Google Scholar] [CrossRef]

- Junior, R.L.R.; Rech, P. Reliability of Google’s Tensor Processing Units for Convolutional Neural Networks. In Proceedings of the 2022 52nd Annual IEEE/IFIP International Conference on Dependable Systems and Networks-Supplemental Volume (DSN-S), Baltimore, MD, USA, 27–30 June 2022; pp. 25–27. [Google Scholar]

- Yu, S.; Liu, W.; Tao, S.-J.; Li, Z.-P.; Wang, Y.-T.; Zhong, Z.-P.; Patel, R.B.; Meng, Y.; Yang, Y.-Z.; Wang, Z.-A.; et al. A Von-Neumann-like Photonic Processor and Its Application in Studying Quantum Signature of Chaos. Light Sci. Appl. 2024, 13, 74. [Google Scholar] [CrossRef]

- Shastri, B.J.; Tait, A.N.; Ferreira de Lima, T.; Nahmias, M.A.; Peng, H.-T.; Prucnal, P.R. Neuromorphic Photonics, Principles Of. In Encyclopedia of Complexity and Systems Science; Meyers, R.A., Ed.; Springer: Berlin/Heidelberg, Germany, 2018; pp. 1–37. ISBN 978-3-642-27737-5. [Google Scholar]

- Kutluyarov, R.V.; Zakoyan, A.G.; Voronkov, G.S.; Grakhova, E.P.; Butt, M.A. Neuromorphic Photonics Circuits: Contemporary Review. Nanomaterials 2023, 13, 3139. [Google Scholar] [CrossRef]

- Lin, C.-E.; Sun, C.-P.; Chen, C.-C. Utilizing Optical Neural Network to Establish High-Performance OR and XOR Logic Gates. Eng. Appl. Artif. Intell. 2023, 119, 105788. [Google Scholar] [CrossRef]

- Lin, X.; Zhang, K.; Liao, K.; Huang, H.; Fu, Y.; Zhang, X.; Feng, S.; Hu, X. Polarization-Based All-Optical Logic Gates Using Diffractive Neural Networks. J. Opt. 2024, 26, 035701. [Google Scholar] [CrossRef]

- Zhang, H.; Gu, M.; Jiang, X.D.; Thompson, J.; Cai, H.; Paesani, S.; Santagati, R.; Laing, A.; Zhang, Y.; Yung, M.H.; et al. An Optical Neural Chip for Implementing Complex-Valued Neural Network. Nat. Commun. 2021, 12, 457. [Google Scholar] [CrossRef]

- Singh, C.M.; Singh, H.B.; Ahmad, G. Implementation of Logic Gates and Combinational Circuits Using Neural Network On FPGA For Neuromorphic Hardware. In Proceedings of the 2023 IEEE World Conference on Applied Intelligence and Computing (AIC), Sonbhadra, India, 29–30 July 2023; pp. 113–118. [Google Scholar]

- Parandin, F.; Yahya, S.I.; Rezaeenia, M.; Askarian, A.; Roshani, S.; Roshani, S.; Ghadi, Y.Y.; Jamshidi, M.; Rezaee, S. A Neural Networks Approach for Designing Compact All-Optical Photonic Crystal Based AND Logic Gate. J. Opt. Commun. 2024, 45, s2627–s2636. [Google Scholar] [CrossRef]

- Hamedi, S.; Dehdashti Jahromi, H. Performance Analysis of All-Optical Logical Gate Using Artificial Neural Network. Expert Syst. Appl. 2021, 178, 115029. [Google Scholar] [CrossRef]

- Jha, A.; Huang, C.; Prucnal, P.R. Reconfigurable All-Optical Nonlinear Activation Functions for Neuromorphic Photonics. Opt. Lett. 2020, 45, 4819–4822. [Google Scholar] [CrossRef]

- Agarwal, V.; Anurag, R.; Ganesh, H.S.; Ramaiah, Y.S. An Ultrafast All Optical Encryption Decryption Scheme Based on XOR Logic for Secure Transmission in Optical Networks. J. Phys. Conf. Ser. 2021, 1804, 012187. [Google Scholar] [CrossRef]

- Rachana, M.; Swarnakar, S.; Krishna, S.V.; Kumar, S. Design and Analysis of an Optical Three-Input AND Gate Using a Photonic Crystal Fiber. Appl. Opt. 2022, 61, 77–83. [Google Scholar] [CrossRef] [PubMed]

- Chang, D.Y.-H. Silicon Photonics and Photonic Integrated Circuits 2025-2035: Technologies, Market, Forecasts. 2025. Available online: https://www.idtechex.com/en/research-report/silicon-photonics-and-photonic-integrated-circuits-2025/1067 (accessed on 1 July 2025).

- Zaghloul, Y.A.; Zaghloul, A.R.M.; Adibi, A. Passive All-Optical Polarization Switch, Binary Logic Gates, and Digital Processor. Opt. Express 2011, 19, 20332–20346. [Google Scholar] [CrossRef] [PubMed][Green Version]

- Kurian, A.; Unnikrishnan, K.P.; Gopinath, P.; Paul, B.; Nampoori, V.P.N.; Vallabhan, C.P.G. Realization of Optical Logic Gates Using Thermal Lens Effect. In Proceedings of the Photonic Systems and Applications, Singapore, 29 October 2001; SPIE: Bellingham, WA, USA, 2001; Volume 4595, pp. 100–106. [Google Scholar]

- Vyshnevyy, A.; Ermolaev, G.; Grudinin, D.; Arsenin, A.; Volkov, V.; Novoselov, K. Overcoming the Limits of Integrated Photonics by van Der Waals Materials. In Proceedings of the 2024 IEEE Silicon Photonics Conference (SiPhotonics), Tokyo Bay, Japan, 15–18 April 2024; pp. 1–2. [Google Scholar]

- Li, J.; Yun, Y.; Xu, K.; Zhang, J.; Lin, H.; Zhang, Y.; Hu, J.; Gu, T. Performance Limits of Phase Change Integrated Photonics. IEEE J. Sel. Top. Quantum Electron. 2024, 30, 1–9. [Google Scholar] [CrossRef]

- Vallaitis, T.; Bogatscher, S.; Alloatti, L.; Dumon, P.; Baets, R.; Scimeca, M.L.; Biaggio, I.; Diederich, F.; Koos, C.; Freude, W.; et al. Optical Properties of Highly Nonlinear Silicon-Organic Hybrid (SOH) Waveguide Geometries. Opt. Express 2009, 17, 17357–17368. [Google Scholar] [CrossRef] [PubMed]

- Hossain, M.N.; Ahmed, F.; Khan, M.S.; Ahmed, K.; Sharma, M.; Dhasarathan, V. Highly Nonlinear Silicon Nanocrystal Doped Photonic Crystal Fibers with Low Confinement Loss. Phys. B Condens. Matter 2020, 577, 411802. [Google Scholar] [CrossRef]

- Lin, Q.; Painter, O.J.; Agrawal, G.P. Nonlinear Optical Phenomena in Silicon Waveguides: Modeling and Applications. Opt. Express 2007, 15, 16604–16644. [Google Scholar] [CrossRef]

- Xie, Y.; Wu, J.; Hong, S.; Wang, C.; Liu, S.; Li, H.; Ju, X.; Ke, X.; Liu, D.; Dai, D. Towards Large-Scale Programmable Silicon Photonic Chip for Signal Processing. Nanophotonics 2024, 13, 2051–2073. [Google Scholar] [CrossRef]

- Li, K.; Simmons, E.; Briggs, A.; Nordin, L.; Xu, J.; Podolskiy, V.; Wasserman, D. Subdiffraction Limited Photonic Funneling of Light. Adv. Opt. Mater. 2020, 8, 2001321. [Google Scholar] [CrossRef]

- Kyatam, S.; Mukherjee, D.; Neto, H.; Mendes, J.C. Thermal Management of Photonic Integrated Circuits: Impact of Holder Material and Epoxies. Appl. Opt. 2019, 58, 6126–6135. [Google Scholar] [CrossRef]

- Krochin-Yepez, P.-A.; Scholz, U.; Zimmermann, A. CMOS-Compatible Measures for Thermal Management of Phase-Sensitive Silicon Photonic Systems. Photonics 2020, 7, 6. [Google Scholar] [CrossRef]

- Madarbux, M.R.; Van Laer, A.; Watts, P.M.; Jones, T.M. Towards Zero Latency Photonic Switching in Shared Memory Networks. Concurr. Comput. Pract. Exp. 2014, 26, 2551–2566. [Google Scholar] [CrossRef]

- Anagha, E.G.; Jeyachitra, R.K. Review on All-Optical Logic Gates: Design Techniques and Classifications–Heading toward High-Speed Optical Integrated Circuits. Opt. Eng. 2022, 61, 060902. [Google Scholar] [CrossRef]

- Geerthana, S.; Syedakbar, S.; Sridarshini, T.; Balaji, V.R.; Sitharthan, R.; Shanmuga Sundar, D. 2D- PhC Based All Optical AND, OR and EX-OR Logic Gates with High Contrast Ratio Operating at C Band. Laser Phys. 2022, 32, 106201. [Google Scholar] [CrossRef]

- Jindal, P.; Abou Houran, M.; Goyal, D.; Choudhary, A. A Review of Different Techniques Used to Design Photonic Crystal-Based Logic Gates. Optik 2023, 280, 170794. [Google Scholar] [CrossRef]

- Hsu, W.-C.; Nujhat, N.; Kupp, B.; Conley, J.F.; Wang, A.X. On-Chip Wavelength Division Multiplexing Filters Using Extremely Efficient Gate-Driven Silicon Microring Resonator Array. Sci. Rep. 2023, 13, 5269. [Google Scholar] [CrossRef] [PubMed]

- Steglich, P.; Mai, C.; Villringer, C.; Dietzel, B.; Bondarenko, S.; Ksianzou, V.; Villasmunta, F.; Zesch, C.; Pulwer, S.; Burger, M.; et al. Silicon-Organic Hybrid Photonics: An Overview of Recent Advances, Electro-Optical Effects and CMOS Integration Concepts. J. Phys. Photonics 2021, 3, 022009. [Google Scholar] [CrossRef]

- Vyas, K.; Espinosa, D.H.; Hutama, D.; Jain, S.K.; Mahjoub, R.; Mobini, E.; Awan, K.M.; Lundeen, J.; Dolgaleva, K. Group III-V Semiconductors as Promising Nonlinear Integrated Photonic Platforms. Adv. Phys. X 2022, 7, 2097020. [Google Scholar] [CrossRef]

- Qiu, H.; Yu, Z.; Zhao, T.; Zhang, Q.; Xu, M.; Li, P.; Li, T.; Bao, W.; Chai, Y.; Chen, S.; et al. Two-Dimensional Materials for Future Information Technology: Status and Prospects. Sci. China Inf. Sci. 2024, 67, 160400. [Google Scholar] [CrossRef]

- Schuman, C.D.; Kulkarni, S.R.; Parsa, M.; Mitchell, J.P.; Date, P.; Kay, B. Opportunities for Neuromorphic Computing Algorithms and Applications. Nat. Comput. Sci. 2022, 2, 10–19. [Google Scholar] [CrossRef]

- Maxwell, G. Hybrid Integration Technology for High Functionality Devices in Optical Communications. In Proceedings of the OFC/NFOEC 2008-2008 Conference on Optical Fiber Communication/National Fiber Optic Engineers Conference, San Diego, CA, USA, 24–28 February 2008. [Google Scholar]

- Jia, E.; Xie, C.; Yang, Y.; Ma, X.; Sun, S.; Li, Y.; Zhang, X.; Hu, M. Additive and Subtractive Hybrid Manufacturing Assisted by Femtosecond Adaptive Optics. Photonics Res. 2024, 12, 2772–2783. [Google Scholar] [CrossRef]

| LG | Logic Function | Key Characteristics | Applications |

|---|---|---|---|

| AND | Outputs high (1) only when all inputs are high (1) | Conditional logic, reliability, simple binary multiplication | Used in decision-making circuits, digital security systems, and arithmetic units |

| OR | Outputs high (1) if at least one input is high (1) | Logical addition, inclusive operation, easy to implement | Used in alarm systems, enabling conditions, and simple control logic |

| NOT | Inverts input signal (0 to 1 or 1 to 0) | Single input, inversion property, essential in combinational circuits | Used in digital signal processing, toggling outputs, and creating control signals |

| NAND | Outputs low (0) only when all inputs are high (1) | Universal gate, can form any logic function, efficient for large circuits | Used in memory storage (flash, RAM), microprocessors, and control logic |

| NOR | Outputs high (1) only when all inputs are low (0) | Another universal gate, reliable for minimal logic designs | Used in latch circuits, digital timers, and control systems |

| XOR | Outputs high (1) when an odd number of inputs are high | Parity-based function, selective switching, is essential in arithmetic | Used in arithmetic circuits, binary adders, parity checkers, and encryption |

| XNOR | Outputs high (1) when an even number of inputs are high | Equality detection, complementary to XOR, checks signal match | Used in parity generators, digital comparators, and data verification systems |

| Material Type | Key Characteristics | Best-Suited Photonic LGs | Advantages | Challenges | Logic Fingerprint |

|---|---|---|---|---|---|

| Nonlinear Materials [19,75,90,91] | High third-order nonlinearity, ultrafast response, supports soliton propagation, intensity-dependent refractive index change | AND, OR, NAND, NOR, XOR, NOT (especially soliton-based and threshold-driven) | All-optical ultrafast operation; time-domain stability | High power consumption; optical losses; fabrication precision | Threshold output based on intensity; logic encoded in soliton formation (e.g., output “1” only above intensity threshold) |

| EO Materials [5,92] | Pockels effect: refractive index changes under applied voltage; fast and tunable response | Reconfigurable AND, OR, XOR, NOT (electrically controlled) | Fast switching; low losses; reconfigurable | Needs electrical input; integration complexity; not purely optical | Externally tunable transmission/reflection states mapped to logic (e.g., applied voltage sets logic “1” or “0”) |

| PCMs [93,94,95] | Reversible switching between amorphous and crystalline states with high optical contrast | Memory-assisted AND, OR, NOT (nonvolatile gates) | Nonvolatile optical logic; memory functionality; low static power | Slower speed; endurance limits; thermal issues | State-dependent output (e.g., “1” = crystalline, “0” = amorphous); persistent logic state without input |

| Parameter | Photonic LGs (Typical) | CMOS Logic (Typical) |

|---|---|---|

| Gate Density | ~104–105 gates/mm2 (plasmonic, PhC) [7] | ~107–108 gates/mm2 |

| Power per Bit | ~200 μW/gate (plasmonic), sub-nW (PCM) [75] | 10–100 pJ/bit |

| Speed/Switching Time | 50 fs–10 ps [114,115] | ~10–100 ps |

| Bandwidth | >1 Tbps [73] | ~10–100 Gbps |

| Footprint per Gate | 0.5–2.4 μm2 (with optimized layouts) [7] | <1 μm2 |

| Insertion Loss/Extinction | Up to 28 dB CR (e.g., EO and PCM gates) [84] | N/A (not optical) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kazanskiy, N.L.; Oseledets, I.V.; Nikonorov, A.V.; Chertykovtseva, V.O.; Khonina, S.N. Exploring the Frontier of Integrated Photonic Logic Gates: Breakthrough Designs and Promising Applications. Technologies 2025, 13, 314. https://doi.org/10.3390/technologies13080314

Kazanskiy NL, Oseledets IV, Nikonorov AV, Chertykovtseva VO, Khonina SN. Exploring the Frontier of Integrated Photonic Logic Gates: Breakthrough Designs and Promising Applications. Technologies. 2025; 13(8):314. https://doi.org/10.3390/technologies13080314

Chicago/Turabian StyleKazanskiy, Nikolay L., Ivan V. Oseledets, Artem V. Nikonorov, Vladislava O. Chertykovtseva, and Svetlana N. Khonina. 2025. "Exploring the Frontier of Integrated Photonic Logic Gates: Breakthrough Designs and Promising Applications" Technologies 13, no. 8: 314. https://doi.org/10.3390/technologies13080314

APA StyleKazanskiy, N. L., Oseledets, I. V., Nikonorov, A. V., Chertykovtseva, V. O., & Khonina, S. N. (2025). Exploring the Frontier of Integrated Photonic Logic Gates: Breakthrough Designs and Promising Applications. Technologies, 13(8), 314. https://doi.org/10.3390/technologies13080314