A Compact Size Wideband RF-VGA Based on Second Generation Controlled Current Conveyors

Abstract

1. Introduction

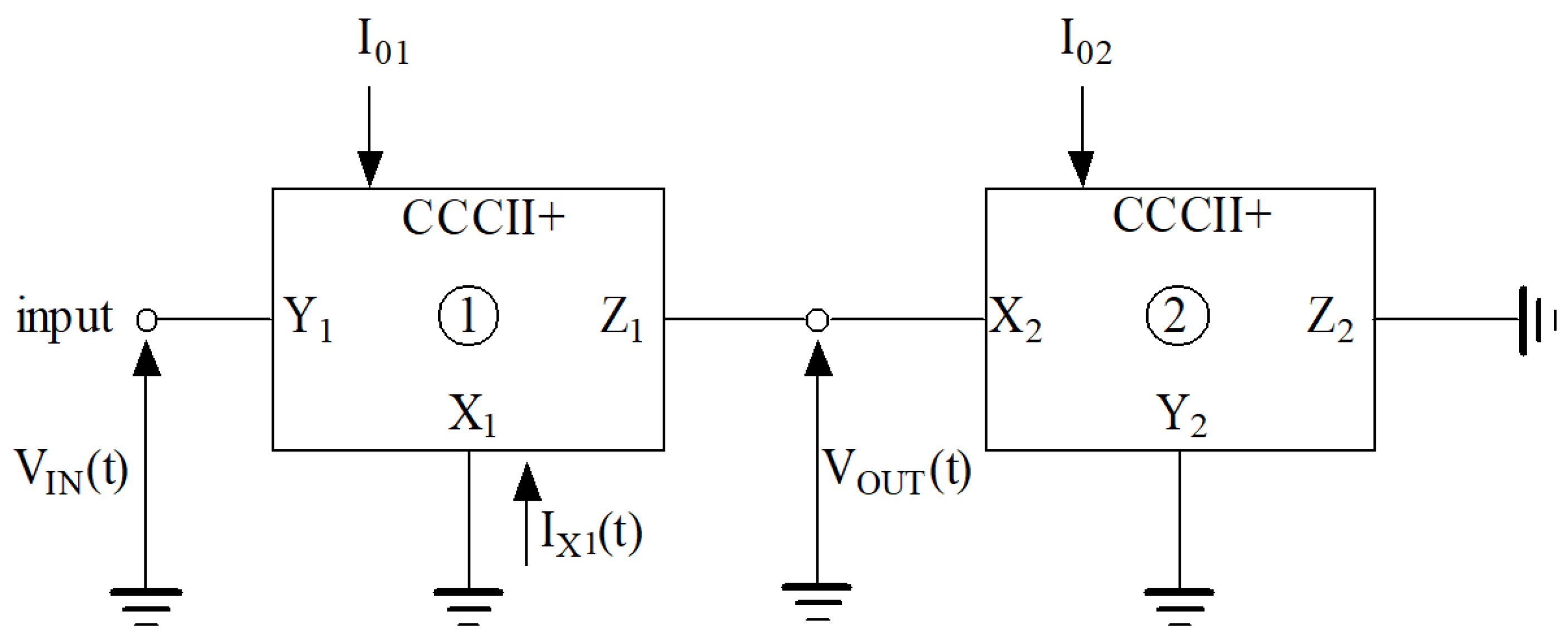

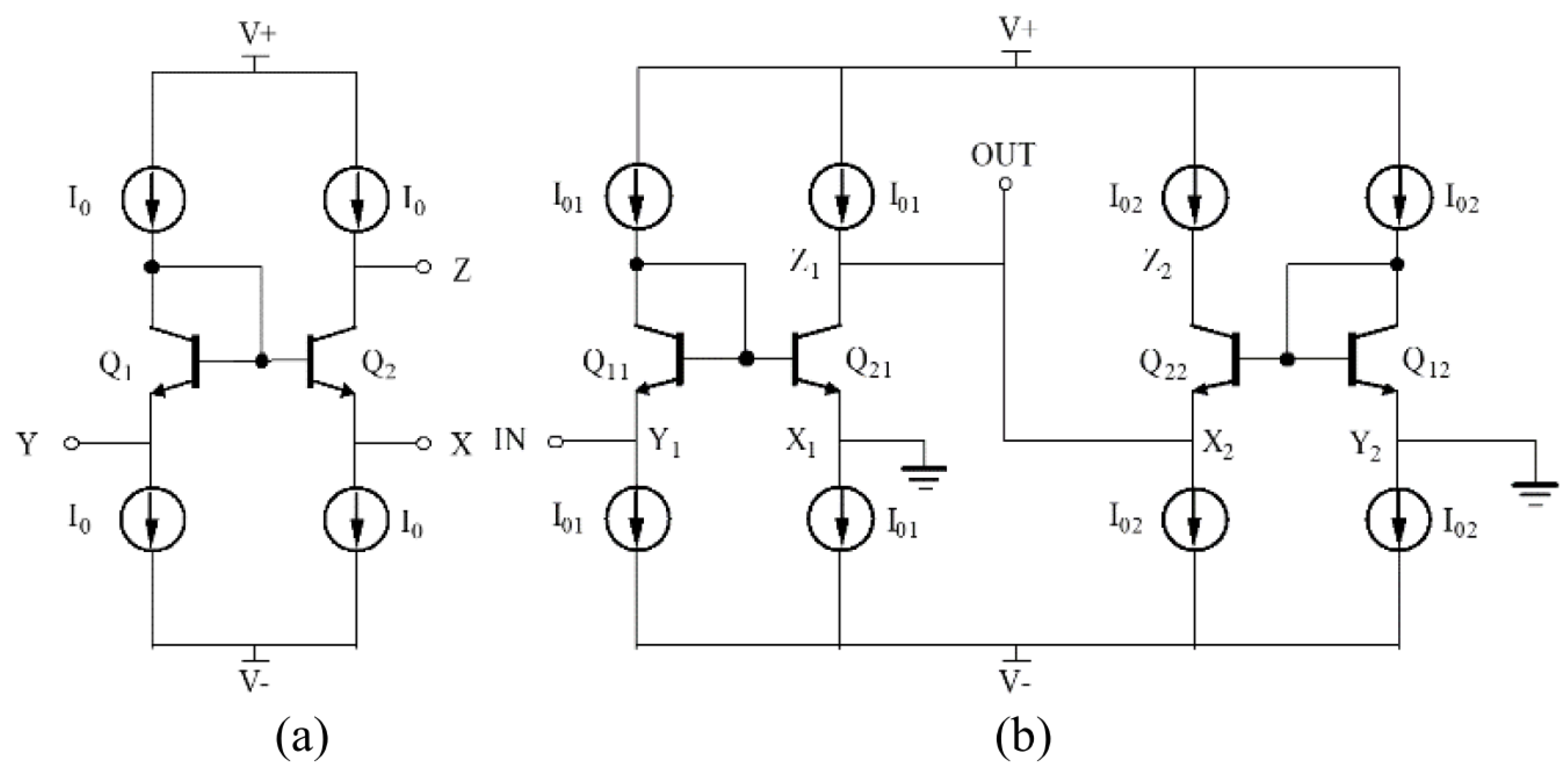

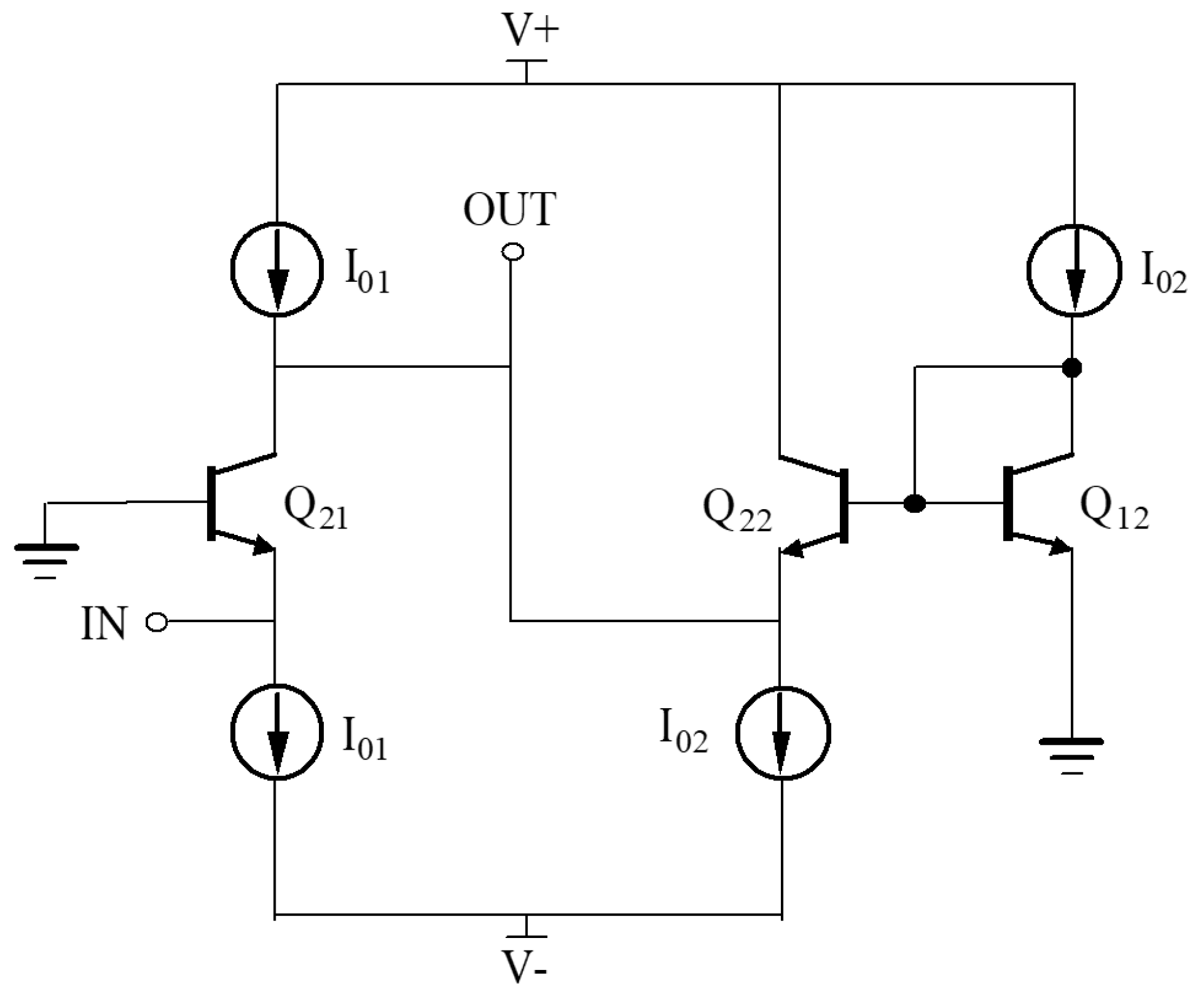

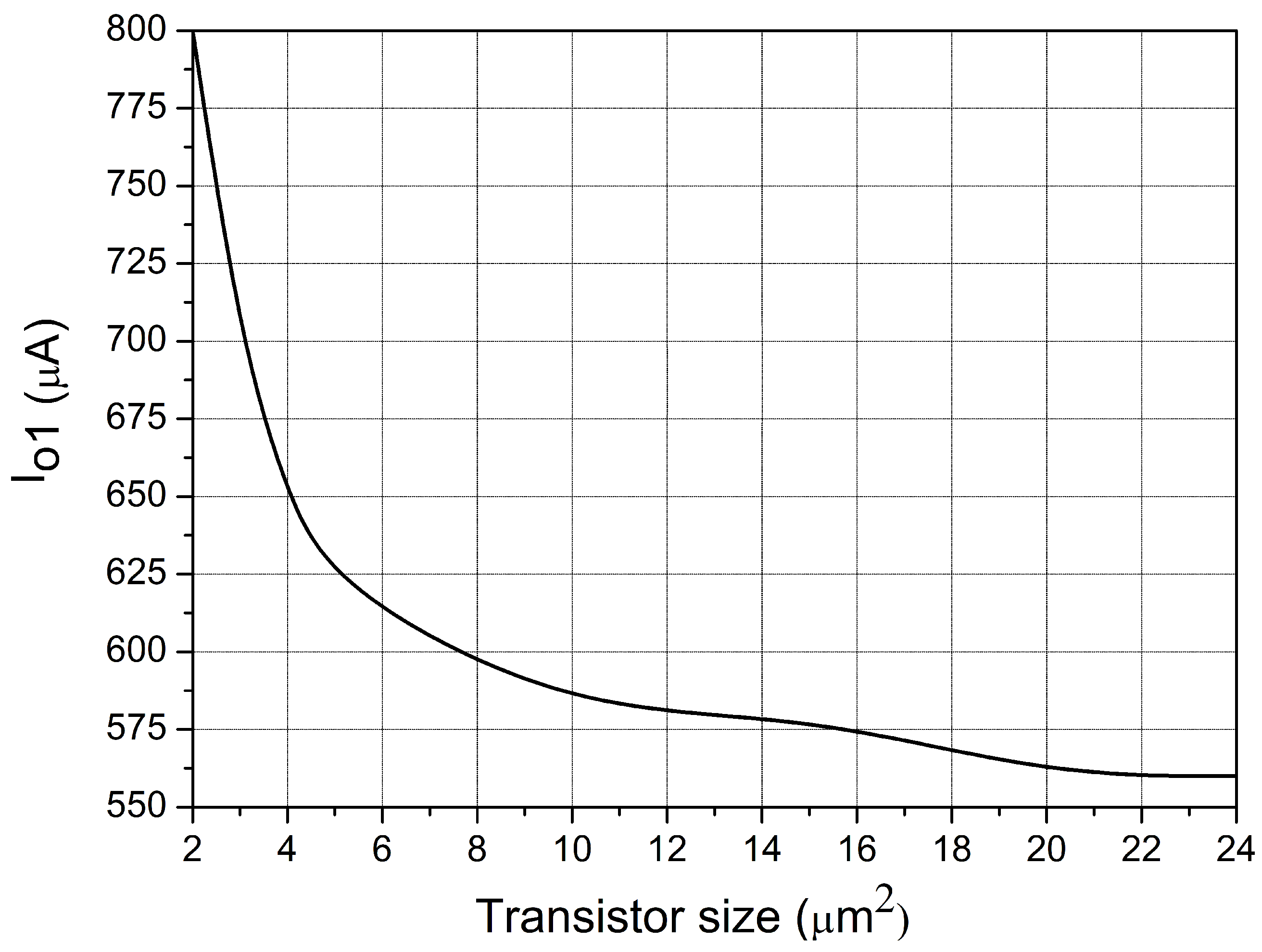

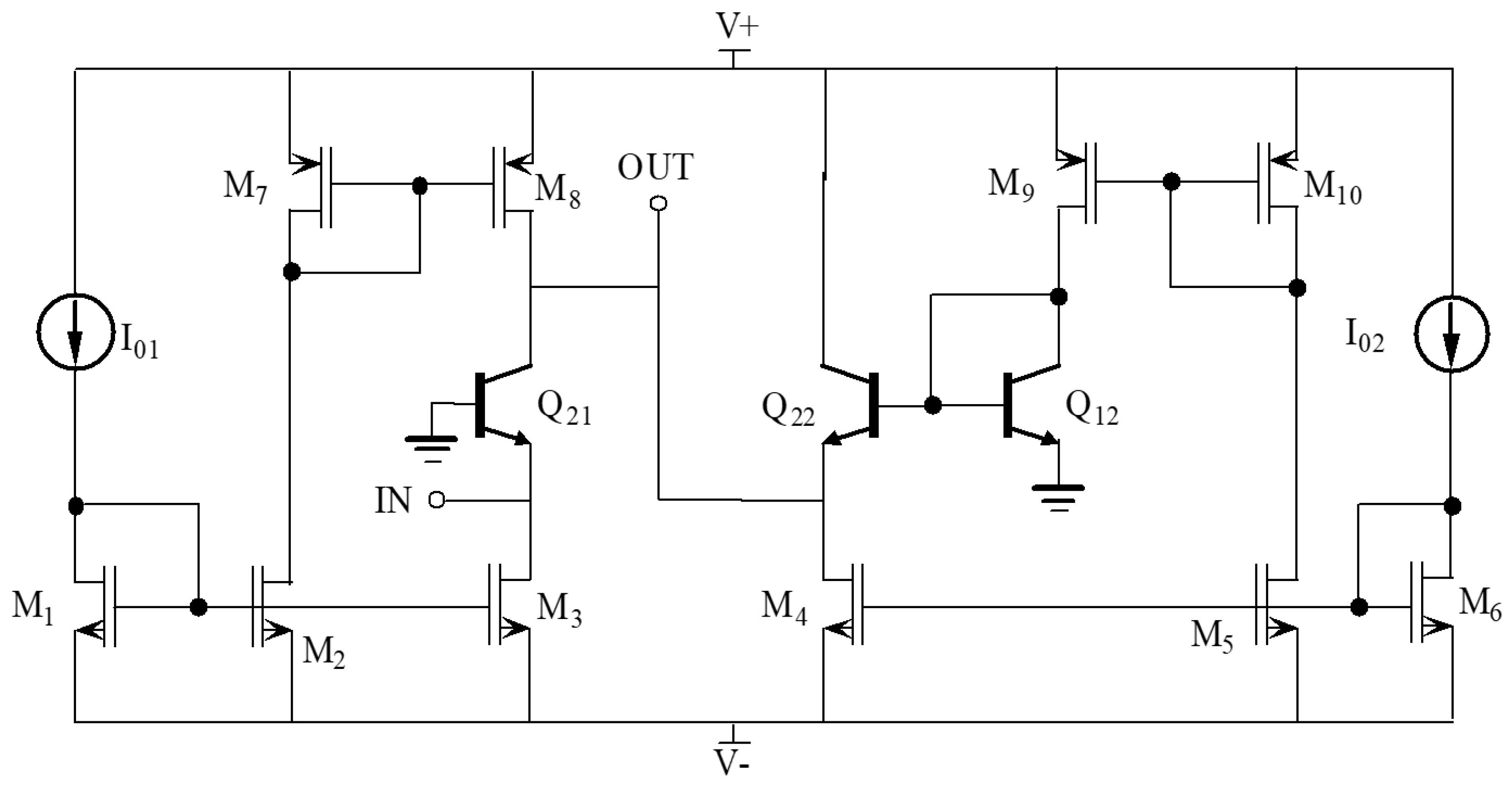

2. RF-VGA Based on the Current Conveyor

- between ports X and Z the device acts as a current follower,

- between ports Y and X it operates as a voltage follower,

- between ports Z and Y it behaves as a transconductor.

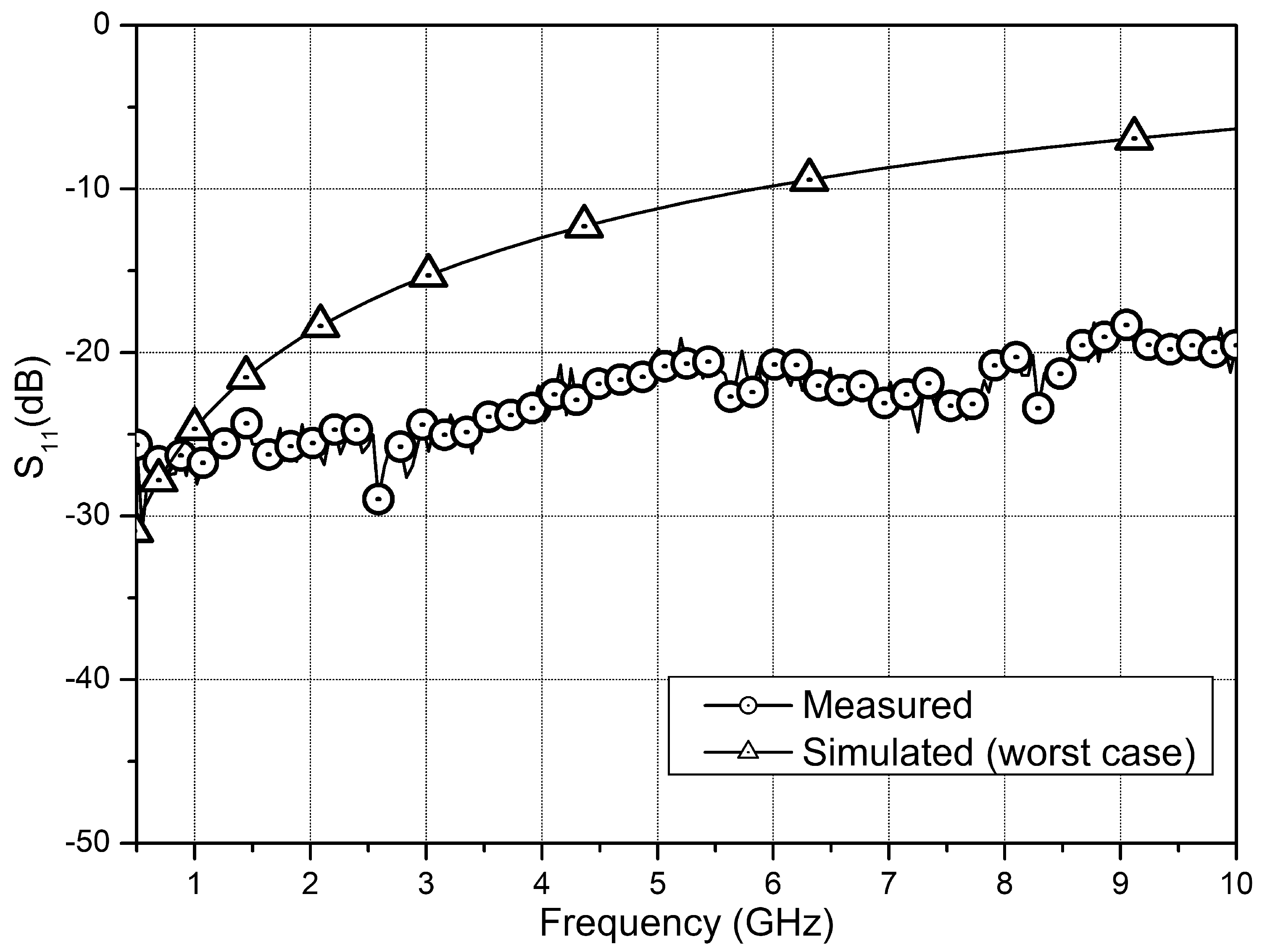

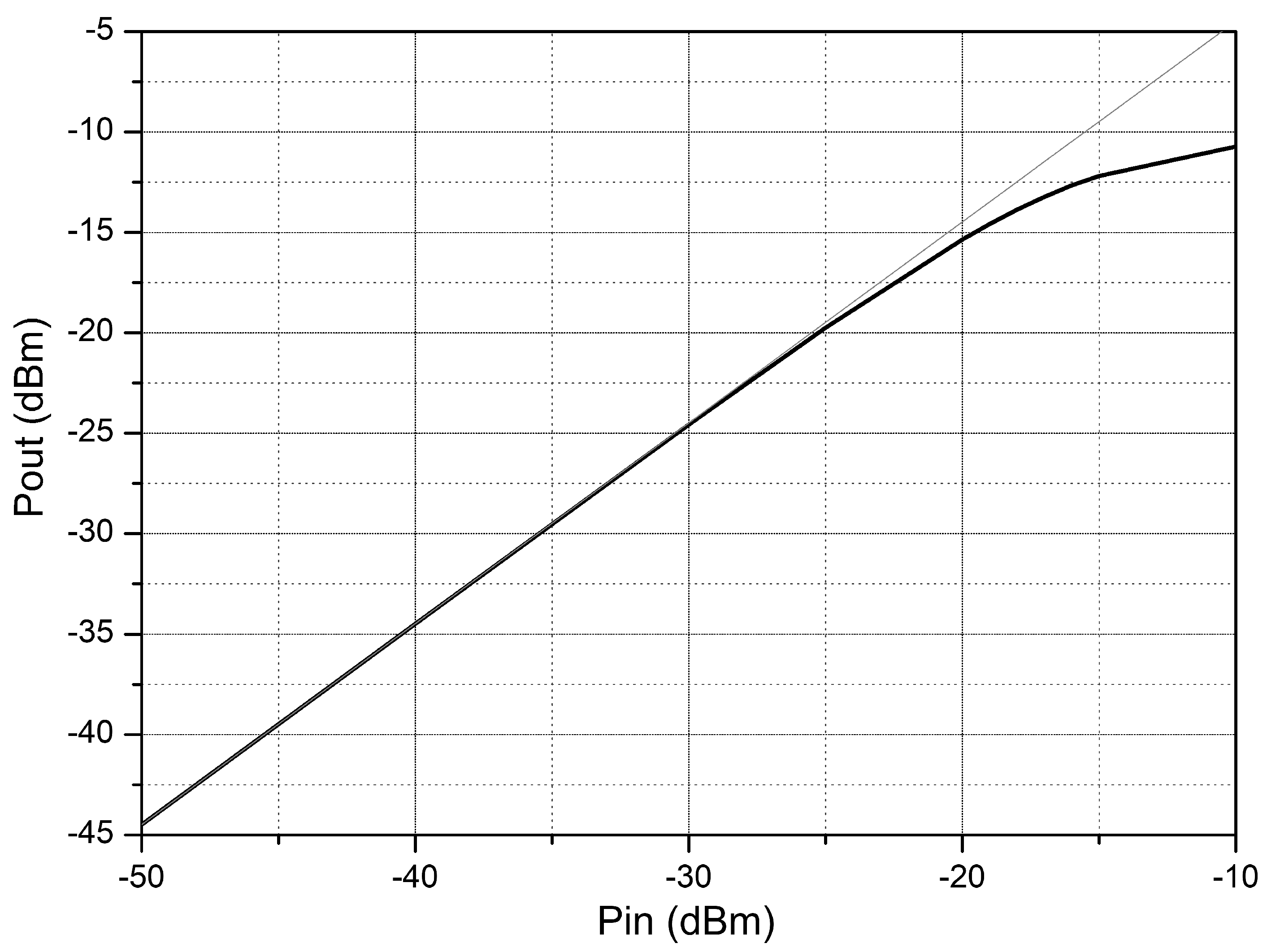

3. Measurements

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| BW | bandwidth |

| CCII | second-generation current conveyor |

| CCCII | second-generation controlled current conveyor |

| ISM | industrial, scientific and medical |

| LNA | low noise amplifier |

| MICS | medical implant communication system |

| RF-VGA | radio frequency variable gain amplifier |

| SDR | software design radio |

| VGA | variable gain amplifier |

References

- Díaz, R.; Khemchandani, S.L.; Vázquez, H.; Suárez, F. Design Of Low-Noise Amplifiers for Ultra-Wideband Communications, 1st ed.; McGraw-Hill Professional: New York, NY, USA, 2014; ISBN 978-007-182-312-8. [Google Scholar]

- Ballweber, B.M.; Gupta, R.; Allstot, D.J. A fully integrated 0.5–5.5 GHz CMOS distributed amplifier. IEEE J. Solid-State Circuits 2000, 35, 231–239. [Google Scholar] [CrossRef]

- Guan, X.; Nguyen, C. Low-power-consumption and high-gain CMOS distributed amplifiers using cascade of inductively coupled common-source gain cells for UWB systems. IEEE Trans. Microw. Theory Tech. 2006, 54, 3278–3283. [Google Scholar] [CrossRef]

- Pino, J.D.; Khemchandani, S.L.; Mateos-Angulo, S.; Mayor-Duarte, D.; San-Miguel-Montesdeoca, M. Area Efficient Dual-Fed CMOS Distributed Power Amplifier. Electronics 2018, 7, 139. [Google Scholar] [CrossRef]

- Feng, C.; Yu, X.P.; Lu, Z.H.; Lim, W.M.; Sui, W.Q. 3–10 GHz self-biased resistive-feedback lna with inductive source degeneration. Electron. Lett. 2013, 49, 387–388. [Google Scholar] [CrossRef]

- Lee, J.; Cressler, J.D. A 3–10 GHz SiGe resistive feedback low noise amplifier for UWB applications. In Proceedings of the 2005 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium-Digest of Papers, Long Beach, CA, USA, 12–14 June 2005; pp. 545–548. [Google Scholar] [CrossRef]

- Kim, C.-W.; Kang, M.-S.; Anh, P.T.; Kim, H.-T.; Lee, S.-G. An ultra-wideband CMOS low noise amplifier for 3–5-GHz UWB system. IEEE J. Solid-State Circuits 2005, 40, 544–547. [Google Scholar] [CrossRef]

- Vázquez, H.G.; Khemchandani, S.L.; Pulido, R.; Goñi-Iturri, A.; del Pino, J. A wideband active feedback LNA with a modified 3D inductor. Microw. Opt. Technol. Lett. 2010, 52, 1561–1567. [Google Scholar] [CrossRef]

- Sahafi, A.; Sobhi, J.; Koozehkanani, Z.D. Linearity improvement of gm-boosted common gate LNA: Analysis to design. Microelectron. J. 2016, 56, 156–162. [Google Scholar] [CrossRef]

- Jafarnejad, R.; Jannesari, A.; Nabavi, A.; Sahafi, A. A low power low noise amplifier employing negative feedback and current reuse techniques. Microelectron. J. 2016, 49, 49–56. [Google Scholar] [CrossRef]

- Ismail, A.; Abidi, A.A. A 3–10-GHz low-noise amplifier with wideband LC-ladder matching network. IEEE J. Solid-State Circuits 2004, 39, 2269–2277. [Google Scholar] [CrossRef]

- Bevilacqua, A.; Niknejad, A.M. An ultrawideband CMOS low-noise amplifier for 3.1–10.6-GHz wireless receivers. IEEE J. Solid-State Circuits 2004, 39, 2259–2268. [Google Scholar] [CrossRef]

- Chen, Z.; Gao, H.; Leenaerts, D.M.W.; Milosevic, D.; Baltus, P.G.M. A 16–43 GHz low-noise amplifer with 2.5–4.0 dB noise figure. In Proceedings of the IEEE Asian Solid-State Circuits Conference (A-SSCC), Toyama, Japan, 7–9 November 2016; pp. 349–352. [Google Scholar] [CrossRef]

- Shekhar, S.; Walling, J.S.; Allstot, D.J. Bandwidth Extension Techniques for CMOS Amplifiers. IEEE J. Solid-State Circuits 2006, 41, 2424–2439. [Google Scholar] [CrossRef]

- Li, Z.; Wang, C.; Li, Q.; Wang, Z. 60 GHz low-power LNA with high gm × Rout transconductor stages in 65 nm CMOS. Electron. Lett. 2017, 53, 279–281. [Google Scholar] [CrossRef]

- Pi, D.; Chun, B.; Heydari, P. A Synthesis-based Bandwidth Enhancing Technique for CML Buffers/Amplifiers. In Proceedings of the 2007 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 16–19 September 2007; pp. 467–470. [Google Scholar] [CrossRef]

- Abidi, A.A. The path to the software-defined radio receiver. IEEE J. Solid-State Circuits 2007, 42, 954–966. [Google Scholar] [CrossRef]

- Sedra, A.; Smith, K. A second-generation current conveyor and its application. IEEE Trans. Circuit Theory 1970, 17, 132–134. [Google Scholar] [CrossRef]

- Fabre, A.; Saaid, O.; Wiest, F.; Boucheron, C. High frequency applications based on a new current controlled conveyor. IEEE Trans. Circuits Syst. I. Fundam. Theory Appl. 1996, 43, 82–91. [Google Scholar] [CrossRef]

- Seguin, F.; Godara, B.; Alicalapa, F.; Fabre, A. A gain-controllable wide-band low-noise amplifier in low-cost 0.8 μm Si BiCMOS yechnology. IEEE Trans. Microw. Theory Tech. 2004, 52, 154–160. [Google Scholar] [CrossRef]

- Seguin, F.; Fabre, A. 2 GHz controlled current conveyor in standard 0.8 μm BiCMOS technology. Electron. Lett. 2001, 37, 329–330. [Google Scholar] [CrossRef]

- Lee, S.; Choi, I.; Kim, H.; Kim, B. A Sub-mW Fully Integrated Wide-Band Receiver for Wireless Sensor Network. IEEE Microw. Wirel. Compon. Lett. 2015, 25, 319–321. [Google Scholar] [CrossRef]

- Wang, Y.; Afshar, B.; Ye, L.; Gaudet, V.C.; Niknejad, A.M. Design of a low power, inductorless wideband variable-gain amplifier for high-speed receiver systems. IEEE Trans Circuits Syst. I Regul. Pap. 2011, 59, 696–707. [Google Scholar] [CrossRef]

- Park, H.; Lee, S.; Lee, J.; Nam, S. A 0.1–1 Ghz CMOS variable gain amplifier using wideband negative capacitance. IEICE Trans. Electron. 2009, 92, 1311–1314. [Google Scholar] [CrossRef]

- Liu, H.; Boon, C.C.; He, X.; Zhu, X.; Yi, X.; Kong, L.; Heimlich, M.C. A wideband analog-controlled variable-gain amplifier with db-linear characteristic for high-frequency applications. IEEE Trans. Microw. Theory Tech. 2019, 64, 533–540. [Google Scholar] [CrossRef]

- Elkholy, M.; Shakib, S.; Dunworth, J.; Aparin, V.; Entesari, K. A wideband variable gain LNA with high OIP3 for 5G using 40-nm bulk CMOS. IEEE Microw. Wirel. Compon. Lett. 2017, 28, 64–66. [Google Scholar] [CrossRef]

- Baumgratz, F.D.; Saavedra, C.; Steyaert, M.; Tavernier, F.; Bampi, S. A wideband low-noise variable-gain amplifier with a 3.4 dB NF and up to 45 dB gain tuning range in 130-nm CMOS. IEEE Trans. Circuits Syst. II Exp. Briefs 2019, 66, 1104–1108. [Google Scholar] [CrossRef]

- Li, Y.; Zhang, C.; Gao, S.; Yue, W. Design of Broadband LNA and RFVGA for DVB Receiver Tuner using CMOS 0.18-μm Process. In Proceedings of the 2019 IEEE Asia-Pacific Microwave Conference (APMC), Singapore, 10–13 December 2019; pp. 1363–1365. [Google Scholar] [CrossRef]

- Asgari, V.; Belostotski, L. Wideband 28-nm CMOS Variable-Gain Amplifier. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 37, 37–47. [Google Scholar] [CrossRef]

- Kong, L.; Liu, H.; Zhu, X.; Boon, C.C.; Li, C.; Liu, Z.; Yeo, K.S. Design of a Wideband Variable-Gain Amplifier With Self-Compensated Transistor for Accurate dB-Linear Characteristic in 65 nm CMOS Technology. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 1–12. [Google Scholar] [CrossRef]

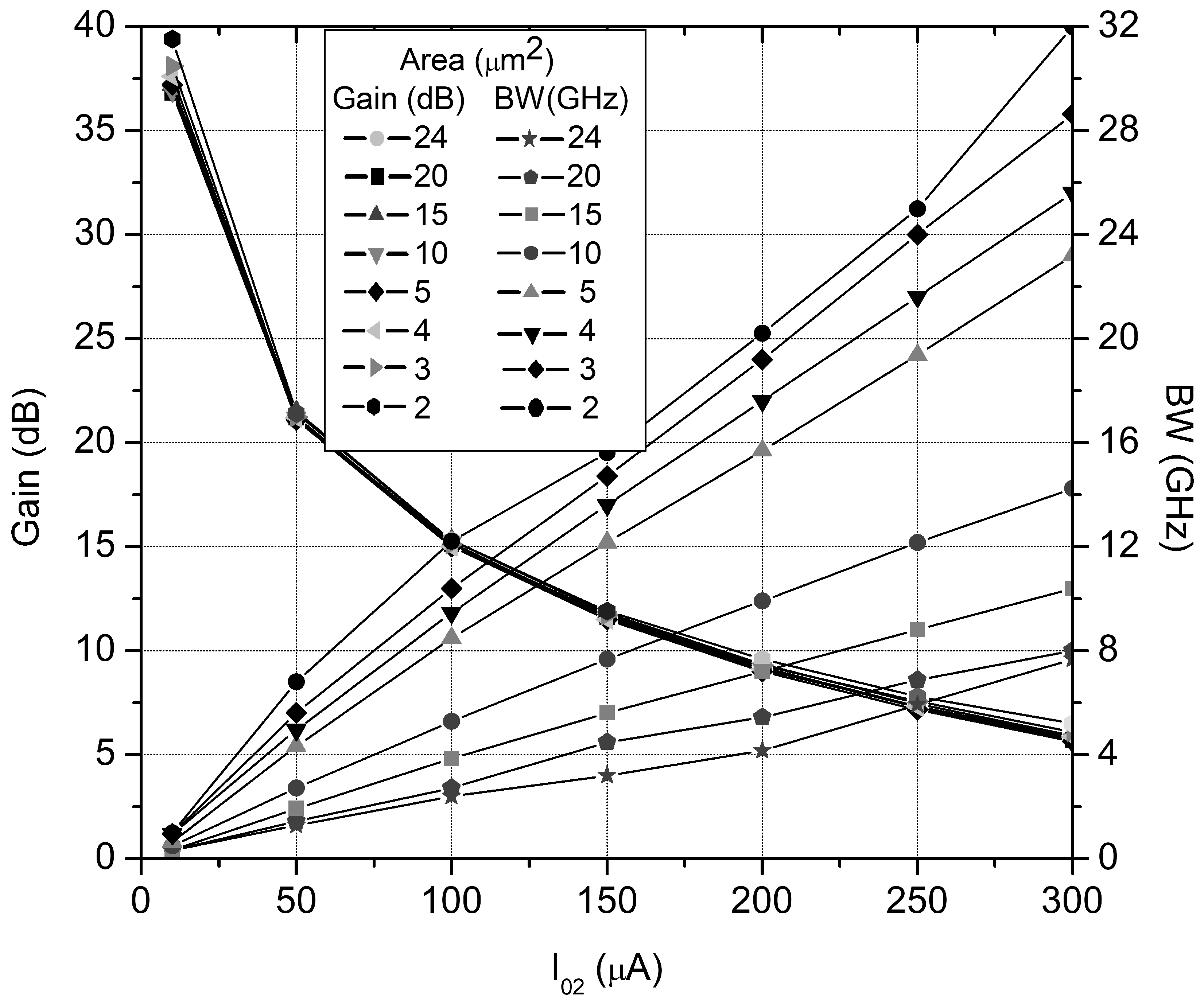

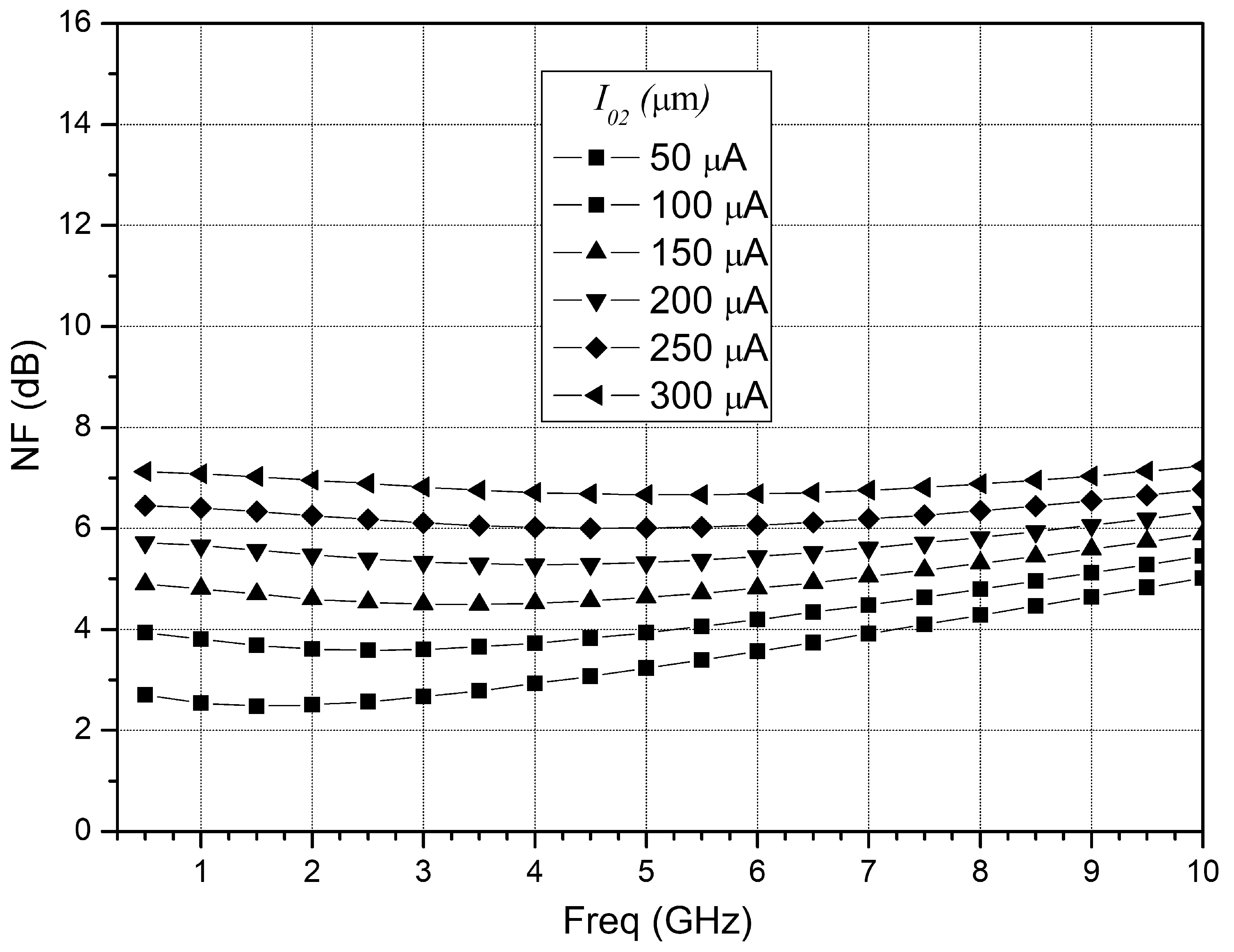

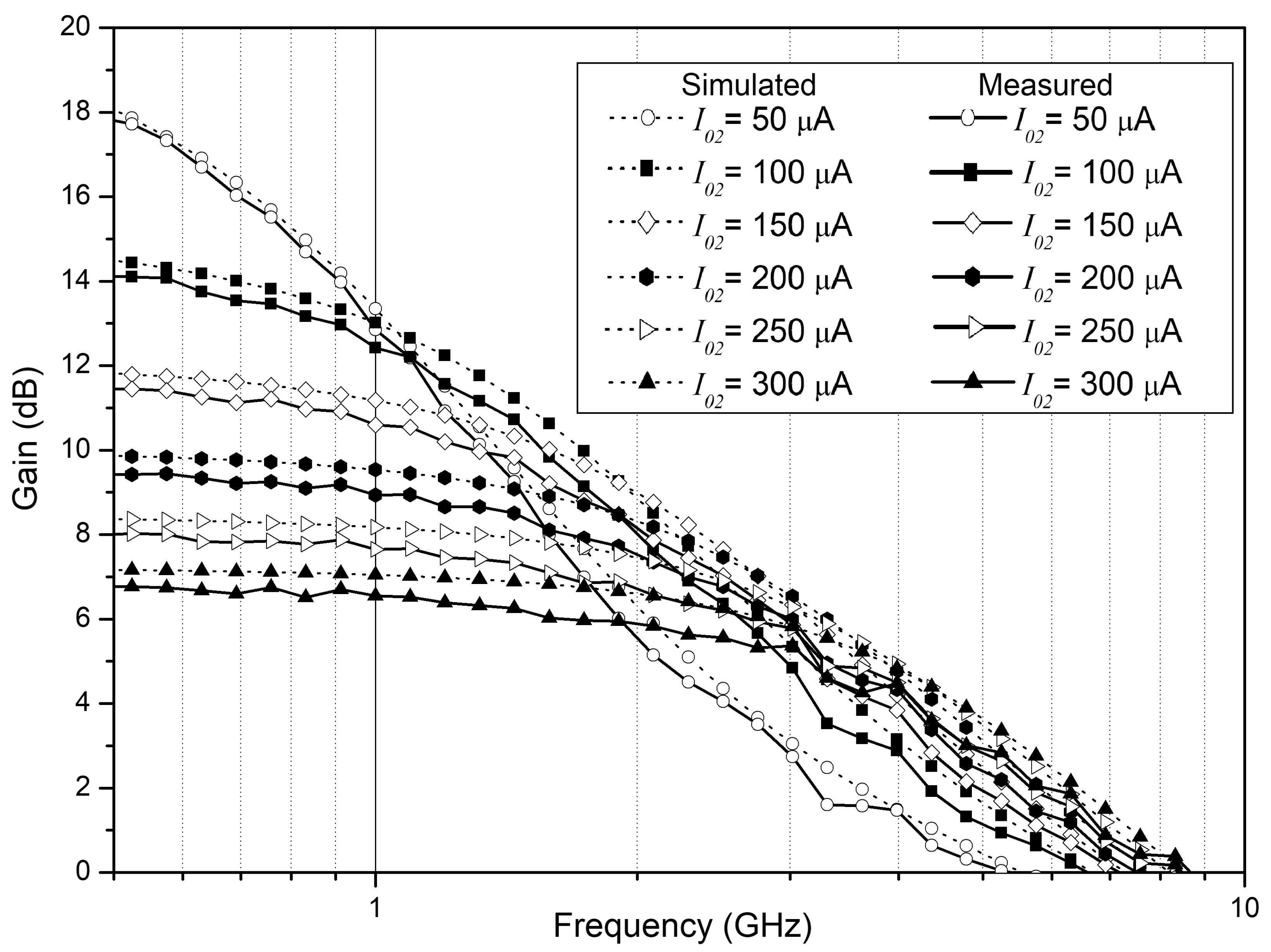

| I02 [A] | 50 | 100 | 150 | 200 | 250 | 300 |

|---|---|---|---|---|---|---|

| Gain [dB] | 18 | 14 | 11.4 | 9.4 | 8 | 6.7 |

| BW [GHz] | 0.85 | 1.3 | 1.9 | 2.7 | 3.26 | 4.3 |

| NF [dB] | 5.5 | 6.5 | 7.2 | 8 | 8.9 | 9.6 |

| 500 | 256 | 175 | 133 | 105 | 90 |

| Reference | Gain [dB] | BW [GHz] | NF [dB] | Vdd [V] | Power [mW] | Area [mm2] | Technology |

|---|---|---|---|---|---|---|---|

| [23] | −10–50 | 2 | 17–30 | 1.0 | 2.5 | 0.013 | 90 nm CMOS |

| [24] | −28–23 | 1 | 3.9–5.2 | 1.5 | 8.2 | 0.051 | 0.18 m CMOS |

| [25] | 2–24 | 2–2.2 | 24–29 | 1.2 | 3.5 | 0.010 | 65 nm CMOS |

| [26] | 18.4–27.1 | 9.3 | 3.3–4.4 | 1.1 | 21.5–31.4 | 0.26 | 40 nm CMOS |

| [27] | −25–20 | 0.2–3.3 | 3.4–20 | 1.2 | 19 | 0.15 | 130 nm CMOS |

| [28] | −54–46 | 0.98–2.15 | 8–15 | – | – | 0.539 | 0.18 m CMOS |

| [29] | 4.6–12 | 0.4–4.5 | 3–9 | 1.5 | 22.5 | 1 | 28 nm FDSOI CMOS |

| [30] | −19–21 | 4 | 17–47 | 1.2 | 3.5 | 0.012 | 65 nm CMOS |

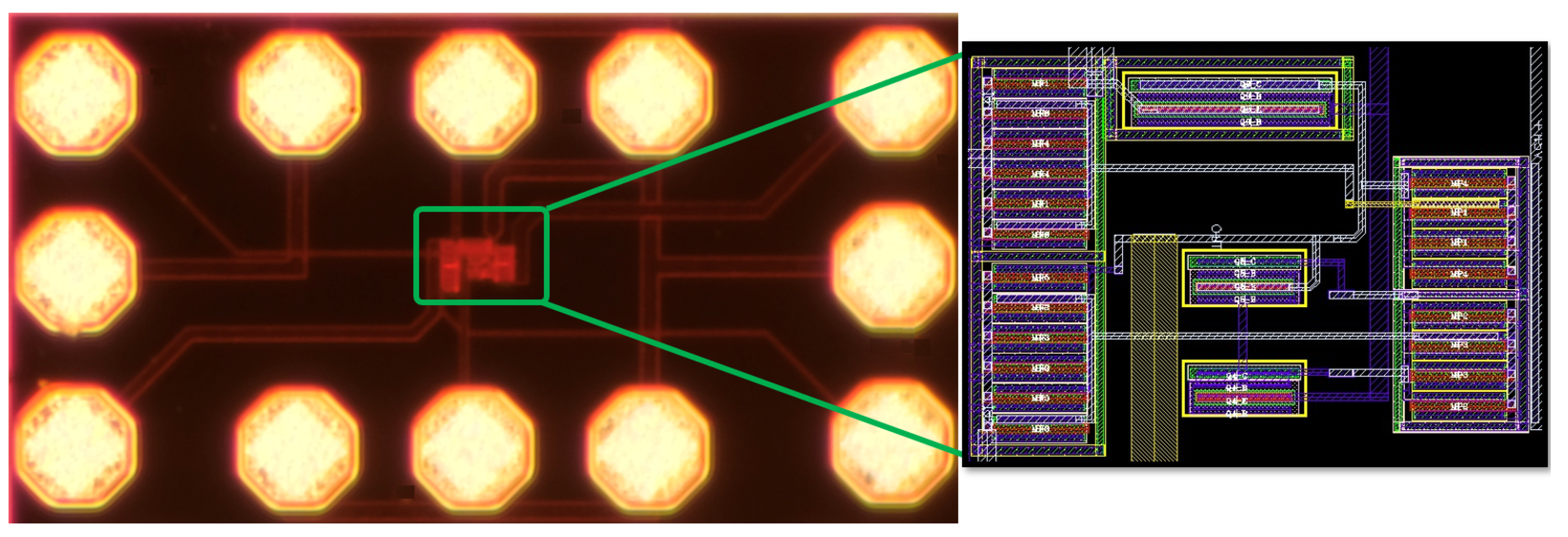

| This work | 6.7–18 | 0.85–4.3 | 5.5–9.6 | ±1.5 | 5.1 | 0.003 | 0.35 m BiCMOS |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

del Pino, J.; L. Khemchandani, S.; Galante-Sempere, D.; Luján-Martínez, C. A Compact Size Wideband RF-VGA Based on Second Generation Controlled Current Conveyors. Electronics 2020, 9, 1600. https://doi.org/10.3390/electronics9101600

del Pino J, L. Khemchandani S, Galante-Sempere D, Luján-Martínez C. A Compact Size Wideband RF-VGA Based on Second Generation Controlled Current Conveyors. Electronics. 2020; 9(10):1600. https://doi.org/10.3390/electronics9101600

Chicago/Turabian Styledel Pino, J., Sunil L. Khemchandani, D. Galante-Sempere, and C. Luján-Martínez. 2020. "A Compact Size Wideband RF-VGA Based on Second Generation Controlled Current Conveyors" Electronics 9, no. 10: 1600. https://doi.org/10.3390/electronics9101600

APA Styledel Pino, J., L. Khemchandani, S., Galante-Sempere, D., & Luján-Martínez, C. (2020). A Compact Size Wideband RF-VGA Based on Second Generation Controlled Current Conveyors. Electronics, 9(10), 1600. https://doi.org/10.3390/electronics9101600