A Semi-Floating Gate Memory with Tensile Stress for Enhanced Performance

Abstract

1. Introduction

2. Simulation and Results

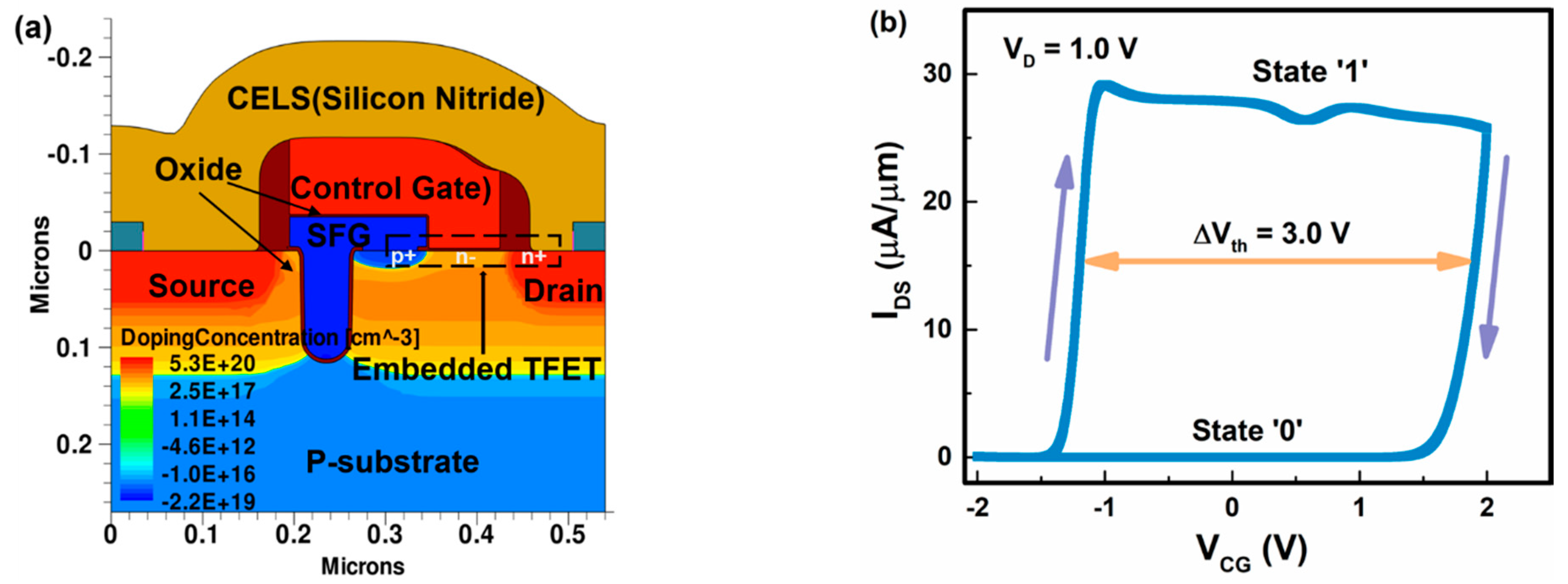

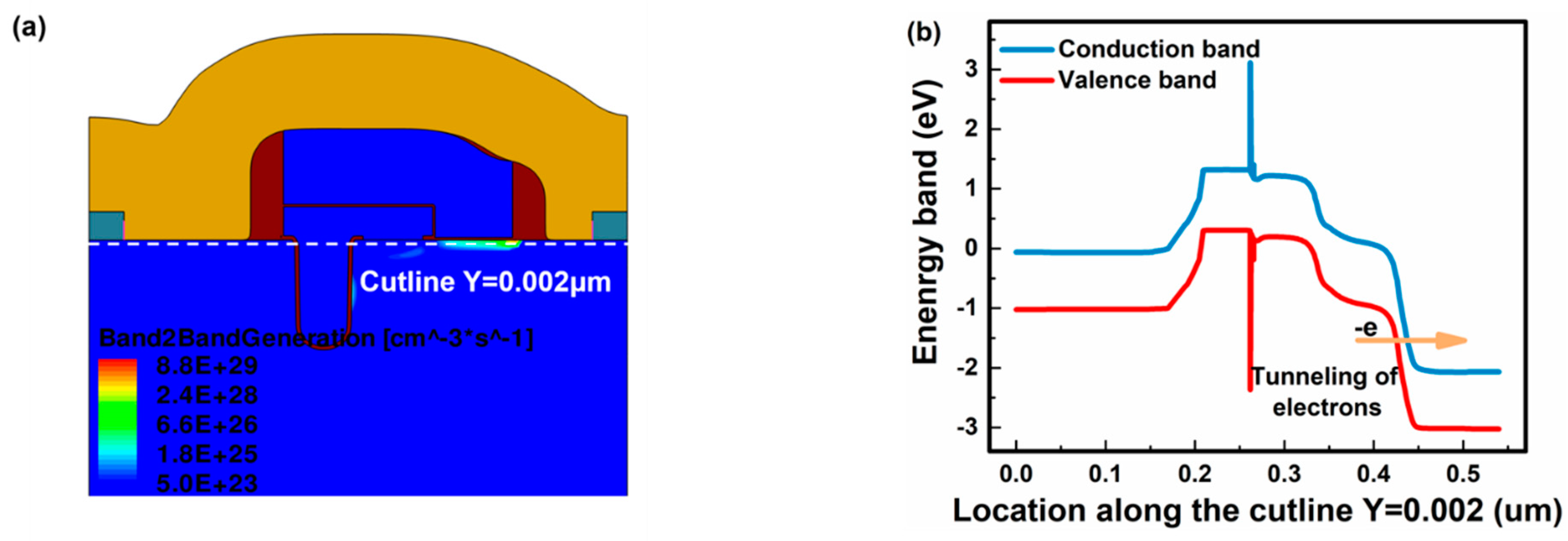

2.1. Device Structure and Operation

2.2. Effect of the Tensile-Stress CESL

2.3. Retention and Disturbance Performance

3. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Mandelman, J.A.; Dennard, R.; Bronner, G.; Divakaruni, J.D.R.; Radens, C. Challenges and future directions for the scaling of dynamic random-access memory (DRAM). IBM J. Res. Dev. 2002, 46, 187–212. [Google Scholar] [CrossRef]

- Hong, S. Memory technology trend and future challenges. In Proceedings of the 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 292–295. [Google Scholar]

- Park, S.-K. Technology scaling challenge and future prospects of DRAM and NAND Flash memory. In Proceedings of the 2015 IEEE International Memory Workshop (IMW), Monterey, CA, USA, 17–20 May 2015; pp. 1–4. [Google Scholar]

- Ranica, R. A capacitor-less DRAM cell on 75 nm gate length 16 nm thin fully depleted SOI device for high density embedded memories. In Proceedings of the 2004 IEEE International Electron Devices Meeting, IEDM Technical Digest, San Francisco, CA, USA, 13–15 December 2004; pp. 277–280. [Google Scholar]

- Choi, S.-J.; Han, J.-W.; Moon, D.-I.; Choi, Y.-K. Analysis and evaluation of a BJT-based 1T-DRAM. IEEE Electron Device Lett. 2010, 31, 393–395. [Google Scholar] [CrossRef]

- Shino, T.; Kusunoki, N.; Higashi, T.; Ohsawa, T.; Fujita, K.; Hatsuda, K.; Ikumi, N.; Matsuoka, F.; Kajitani, Y.; Fukuda, R.; et al. Floating body RAM technology and its scalability to 32 nm node and beyond. In Proceedings of the 2006 International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 2006; pp. 1–4. [Google Scholar]

- Yoshida, E.; Tanaka, T. A capacitorless 1T-DRAM technology using Gate-Induced Drain-Leakage (GIDL) current for low-power and high-speed embedded memory. IEEE Trans. Electron Devices 2006, 53, 692–697. [Google Scholar] [CrossRef]

- Wang, P.-F.; Lin, X.; Liu, L.; Sun, Q.-Q.; Zhou, P.; Liu, X.-Y.; Liu, W.; Gong, Y.; Zhang, D.W. A semi-floating gate transistor for low-voltage ultrafast memory and sensing operation. Science 2013, 341, 640–643. [Google Scholar] [CrossRef] [PubMed]

- Lin, X.; Liu, X.Y.; Zhang, C.M.; Liu, L.; Shi, J.S.; Zhang, S.; Wang, W.B.; Bu, W.H.; Wu, J.; Gong, Y.; et al. Investigation of temperature dependence device scalability and modeling of semifloating-gate transistor memory cell. IEEE Trans. Electron Devices 2015, 62, 1177–1183. [Google Scholar] [CrossRef]

- Horstmann, M. Integration and optimization of embedded-SiGe compressive and tensile stressed liner films and stress memorization in advanced SOI CMOS technologies. In Proceedings of the 2005 IEEE International Electron Devices Meeting, IEDM Technical Digest, Washington, DC, USA, 5 December 2005; pp. 243–246. [Google Scholar]

- Thompson, S.E. A 90-nm logic technology featuring strained-silicon. IEEE Trans. Electron Devices 2004, 51, 1790–1797. [Google Scholar] [CrossRef]

- Ghani, T. A 90-nm high volume manufacturing logic technology featuring novel 45-nm gate length strained silicon CMOS transistors. In Proceedings of the IEEE International Electron Devices Meeting 2003, Washington, DC, USA, 8–10 December 2003; pp. 978–980. [Google Scholar]

- Chui, K.-J.; Ang, K.-W.; Balasubramanian, N.; Li, M.-F.; Samudra, G.; Yeo, Y.-C. N-MOSFET with silicon–carbon source/drain for enhancement of carrier transport. IEEE Trans. Electron Devices 2007, 54, 249–256. [Google Scholar] [CrossRef]

- Pidin, S.; Mori, T.; Nakamura, R.; Saiki, T.; Tanabe, R.; Satoh, S.; Kase, M.; Hashimoto, K.; Sugii, T. MOSFET current drive optimization using silicon nitride capping layer for 65-nm technology node. In Proceedings of the 2004 Symposium on VLSI Technology, Digest of Technical Papers, Honolulu, HI, USA, 15–17 June 2004; pp. 54–55. [Google Scholar]

- Lai, C.M.; Fang, Y.K.; Lin, C.T.; Hsu, C.W.; Yeh, W.K. The impacts of high tensile stress CESL and geometry design on device performance and reliability for 90 nm SOl nMOSFETs. Microelectron. Reliab. 2007, 47, 944–952. [Google Scholar] [CrossRef]

- DeSalvo, B.; Morin, P.; Pala, M.; Ghibaudo, G. A mobility enhancement strategy for sub-14nm power-efficient FDSOI technologies. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014. [Google Scholar]

- Giusi, G.; Crupi, F.; Simoen, E.; Eneman, G.; Jurczak, M. Performance and Reliability of Strained-Silicon nMOSFETs With SiN Cap Layer. IEEE Trans. Electron Devices 2007, 54, 78–82. [Google Scholar] [CrossRef]

- Lee, K.T.; Kang, C.Y.; Yoo, O.S.; Chadwin, D.; Bersuker, G.; Park, H.K.; Lee, J.M.; Hwang, H.S.; Lee, B.H.; Lee, H.D.; et al. A comparative study of reliability and performance of strain engineering using CESL stressor and mechanical strain. In Proceedings of the 2008 IEEE International Reliability Physics Symposium, Phoenix, AZ, USA, 27 April–1 May 2008. [Google Scholar]

- Pang, L.T.; Qian, K.; Spanos, C.J.; Nikolic, B. Measurement and analysis of variability in 45 nm strained-Si CMOS technology. IEEE J. Solid-State Circuits 2009, 44, 2233–2243. [Google Scholar] [CrossRef]

- Sentaurus User’s Manual; ver. C-2013.03; Synopsys, Inc.: Mountain View, CA, USA, 2013.

- Maiti, T.K.; Maiti, C.K. Hybrid orientation technology and strain engineering for ultra-high speed MOSFETs. Bull. Mater. Sci. 2012, 35, 859–865. [Google Scholar] [CrossRef][Green Version]

- Kane, E.O. Theory of Tunneling. J. Appl. Phys. 1961, 32, 83–91. [Google Scholar] [CrossRef]

| Write-1 | Write-0 | Read | Standby | |

|---|---|---|---|---|

| VCG (V) | −2.0 | 1.5 | 0.7 | 0 |

| VD (V) | 1.4 | 0.6 | 1.4 | 1.0 |

| Time (ns) | 5 | 5 | 5 | 8 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yuan, Y.; Jiang, S.; Sun, B.; Chen, L.; Zhu, H.; Sun, Q.; Zhang, D.W. A Semi-Floating Gate Memory with Tensile Stress for Enhanced Performance. Electronics 2019, 8, 414. https://doi.org/10.3390/electronics8040414

Yuan Y, Jiang S, Sun B, Chen L, Zhu H, Sun Q, Zhang DW. A Semi-Floating Gate Memory with Tensile Stress for Enhanced Performance. Electronics. 2019; 8(4):414. https://doi.org/10.3390/electronics8040414

Chicago/Turabian StyleYuan, Ying, Shuye Jiang, Bingqi Sun, Lin Chen, Hao Zhu, Qingqing Sun, and David Wei Zhang. 2019. "A Semi-Floating Gate Memory with Tensile Stress for Enhanced Performance" Electronics 8, no. 4: 414. https://doi.org/10.3390/electronics8040414

APA StyleYuan, Y., Jiang, S., Sun, B., Chen, L., Zhu, H., Sun, Q., & Zhang, D. W. (2019). A Semi-Floating Gate Memory with Tensile Stress for Enhanced Performance. Electronics, 8(4), 414. https://doi.org/10.3390/electronics8040414