A Silicon-Compatible Synaptic Transistor Capable of Multiple Synaptic Weights toward Energy-Efficient Neuromorphic Systems

Abstract

1. Introduction

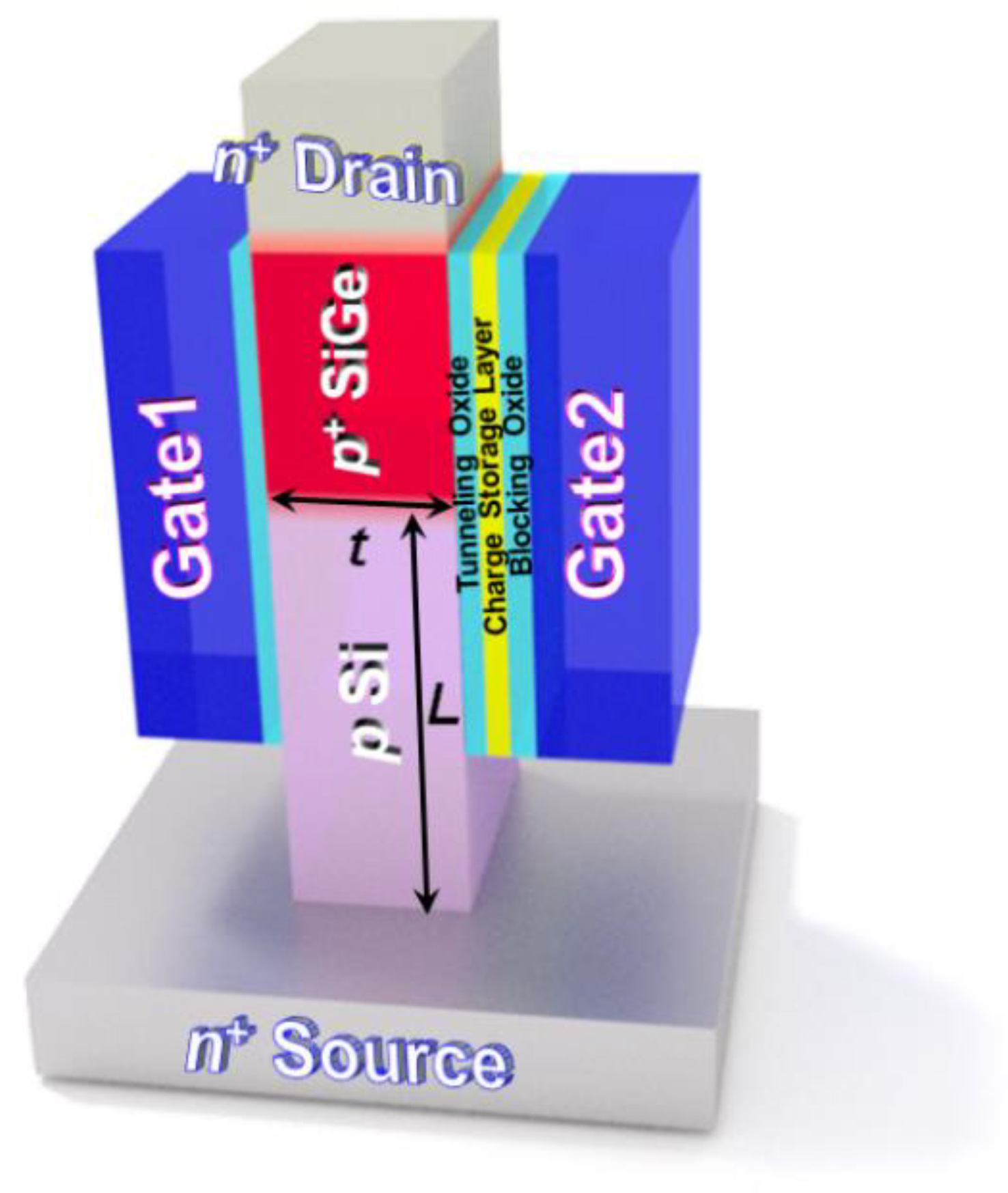

2. Device Structure and Design Strategies

3. Design Results and Discussion

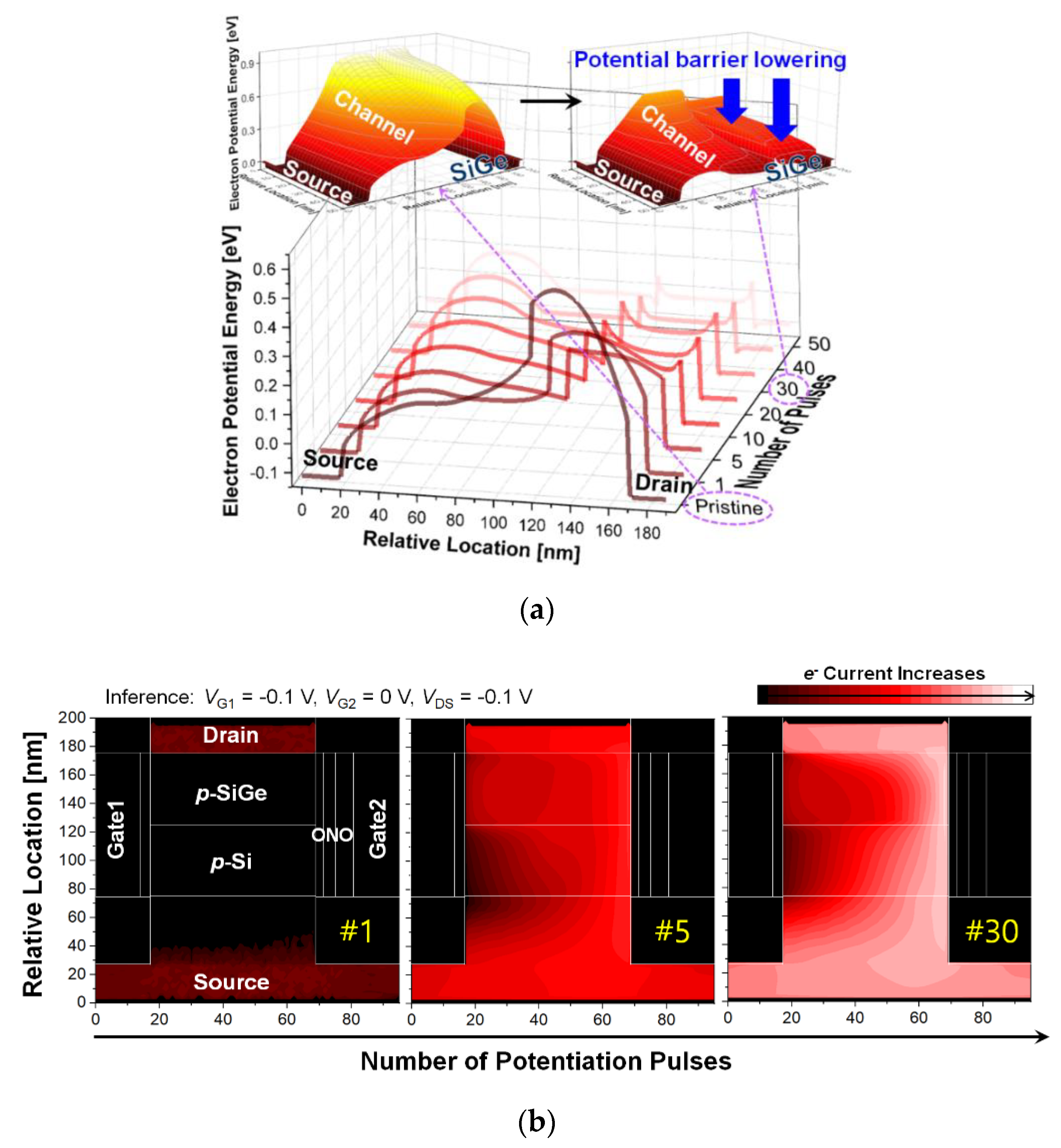

3.1. Design of Synaptic Device

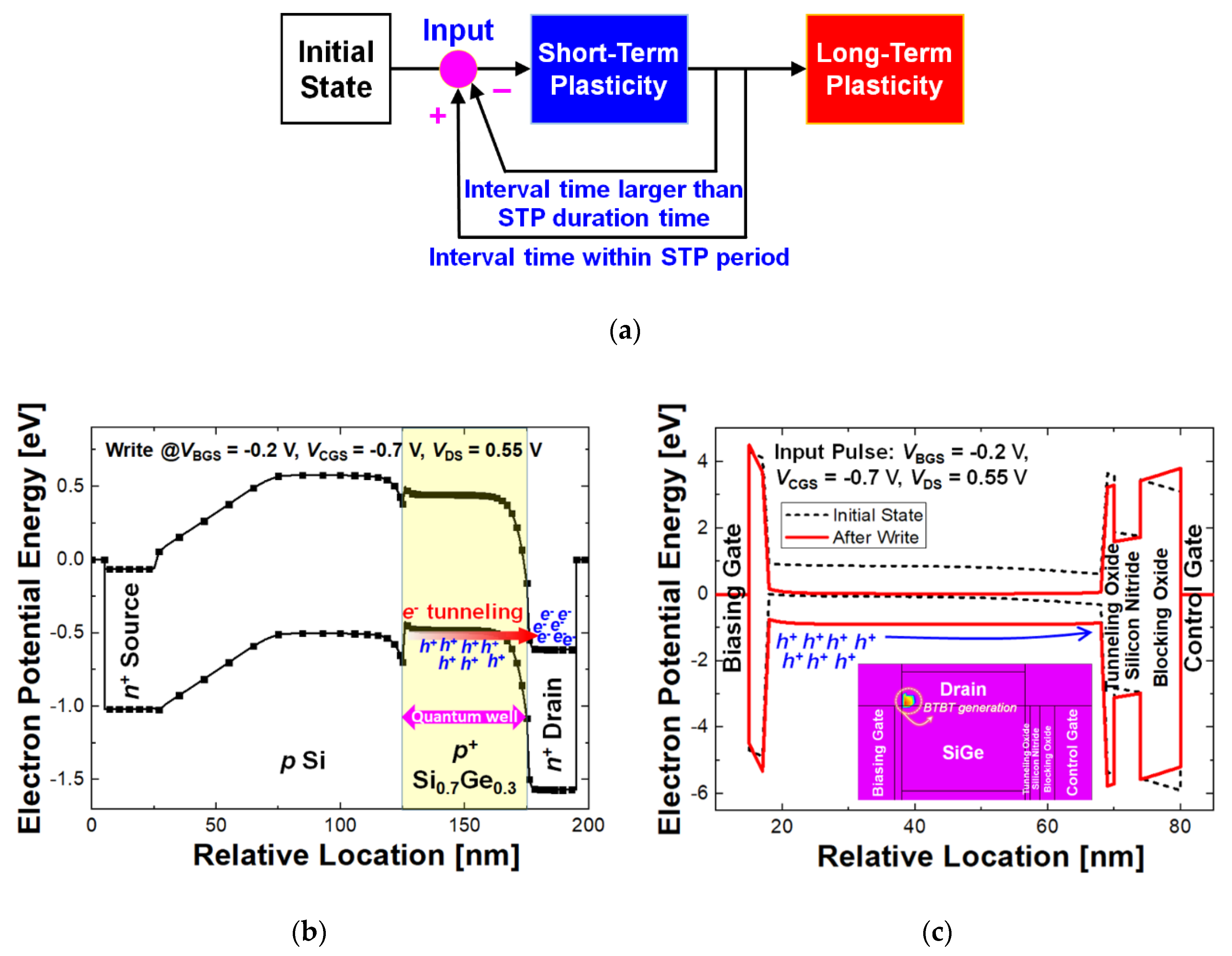

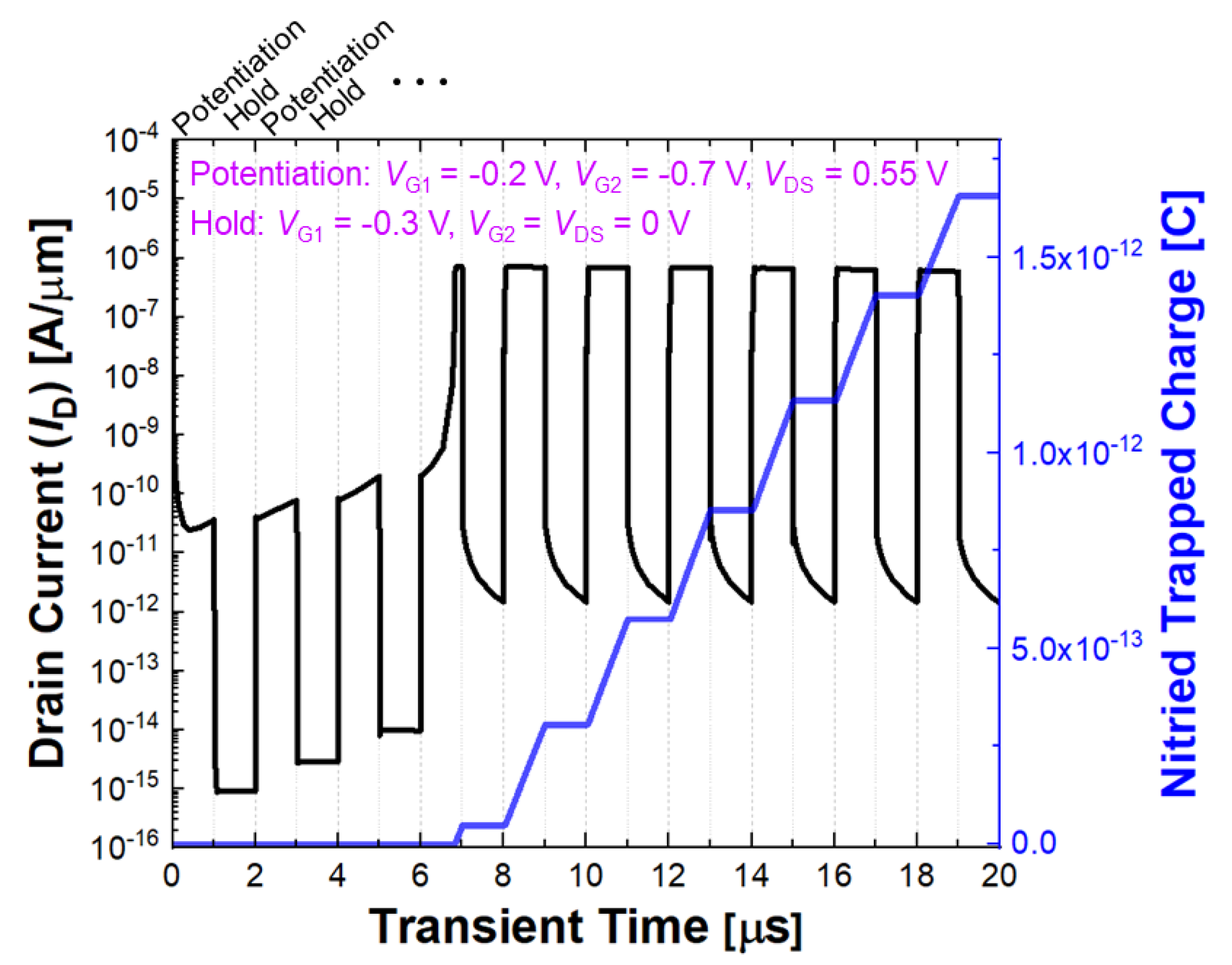

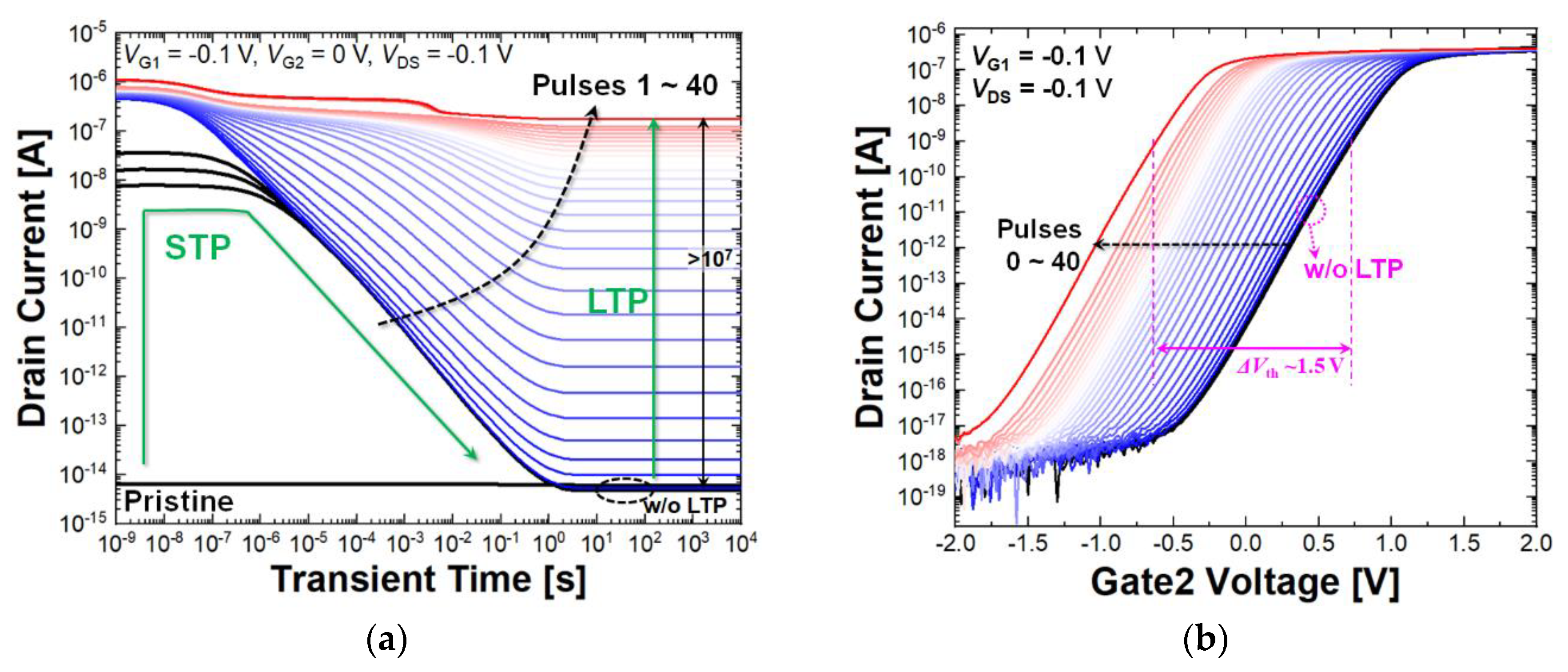

3.2. Validation of Short- and Long-Term Plasticities

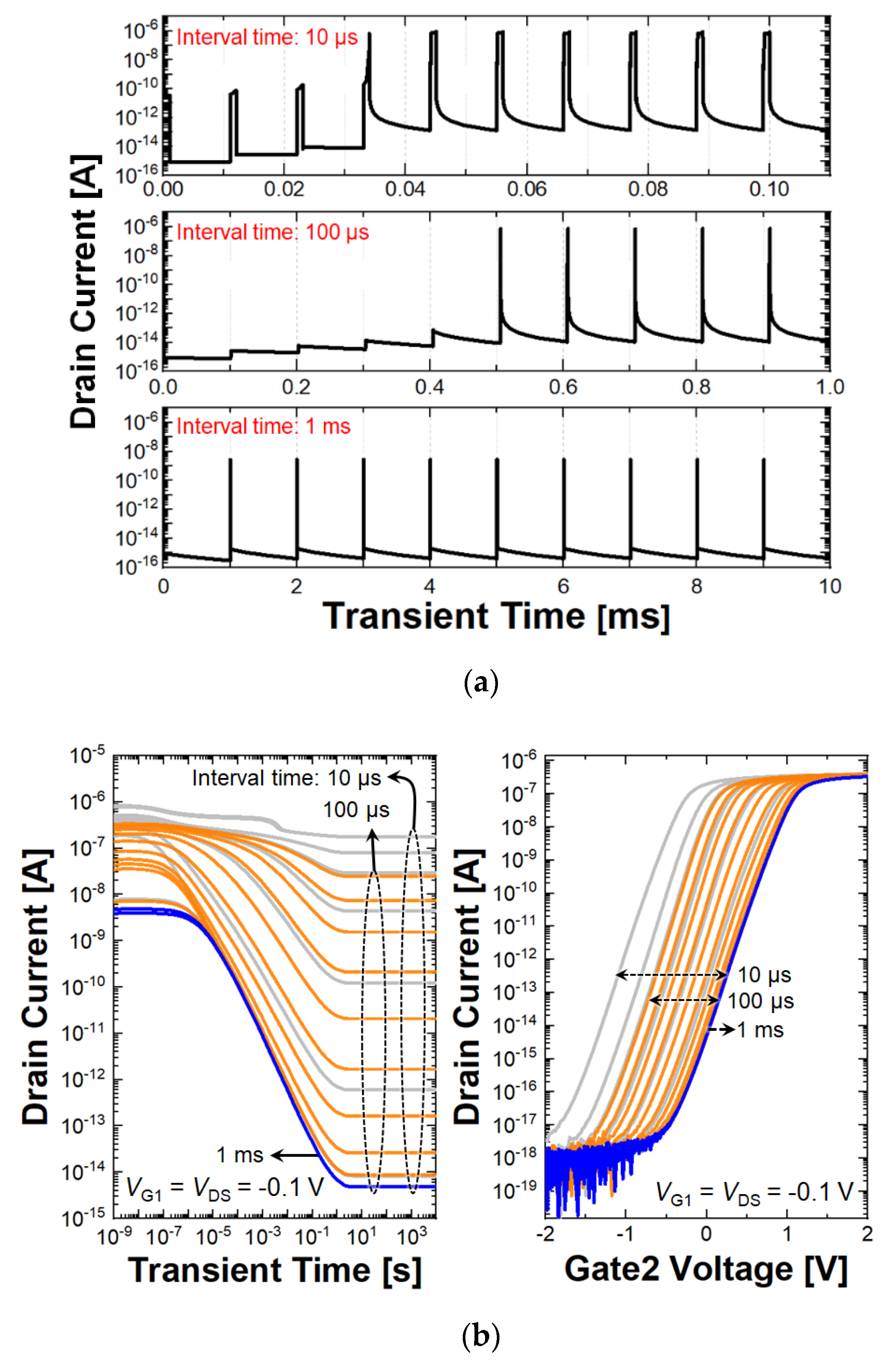

3.3. Interval Time Effects on STP and LTP Characteristics

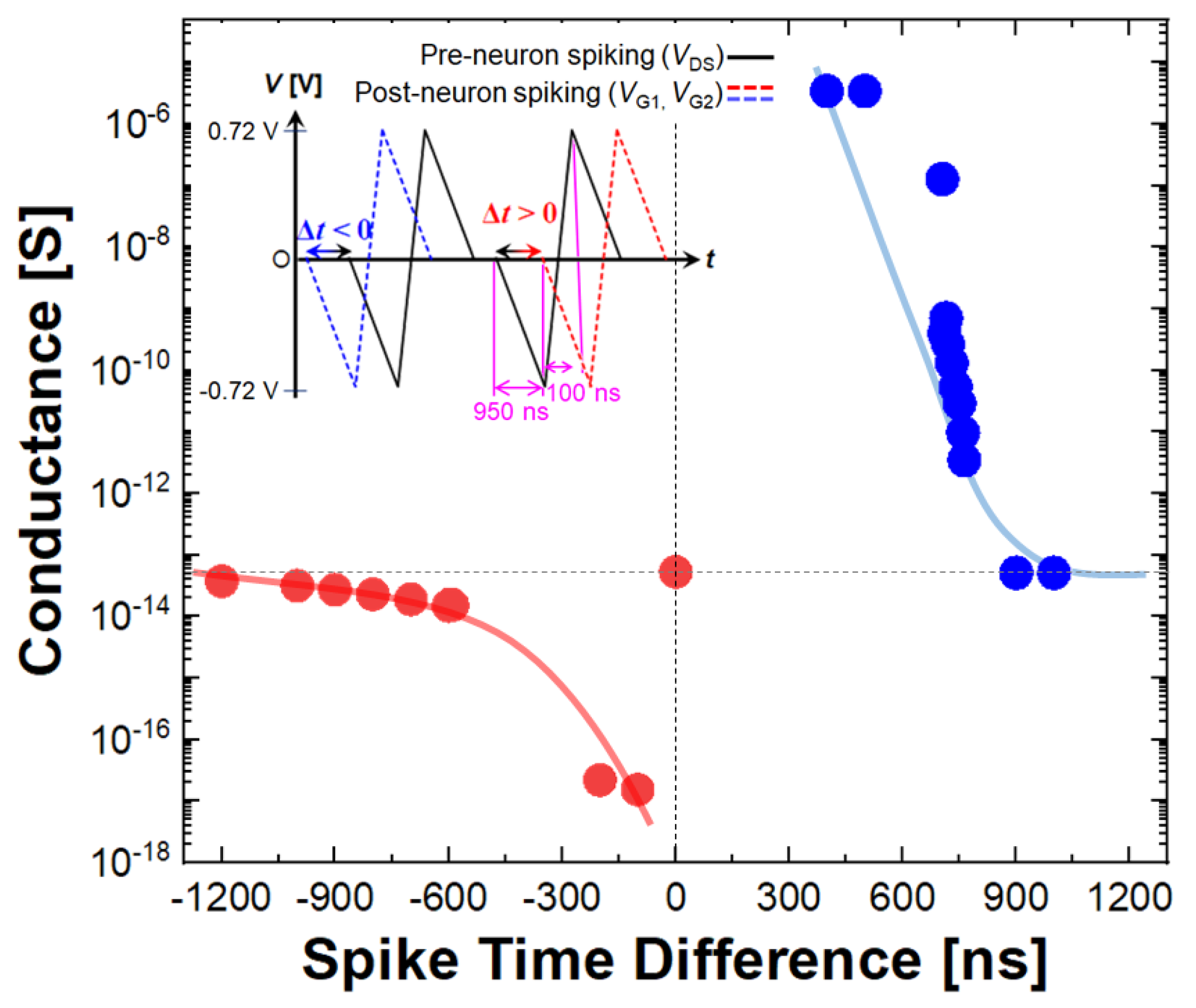

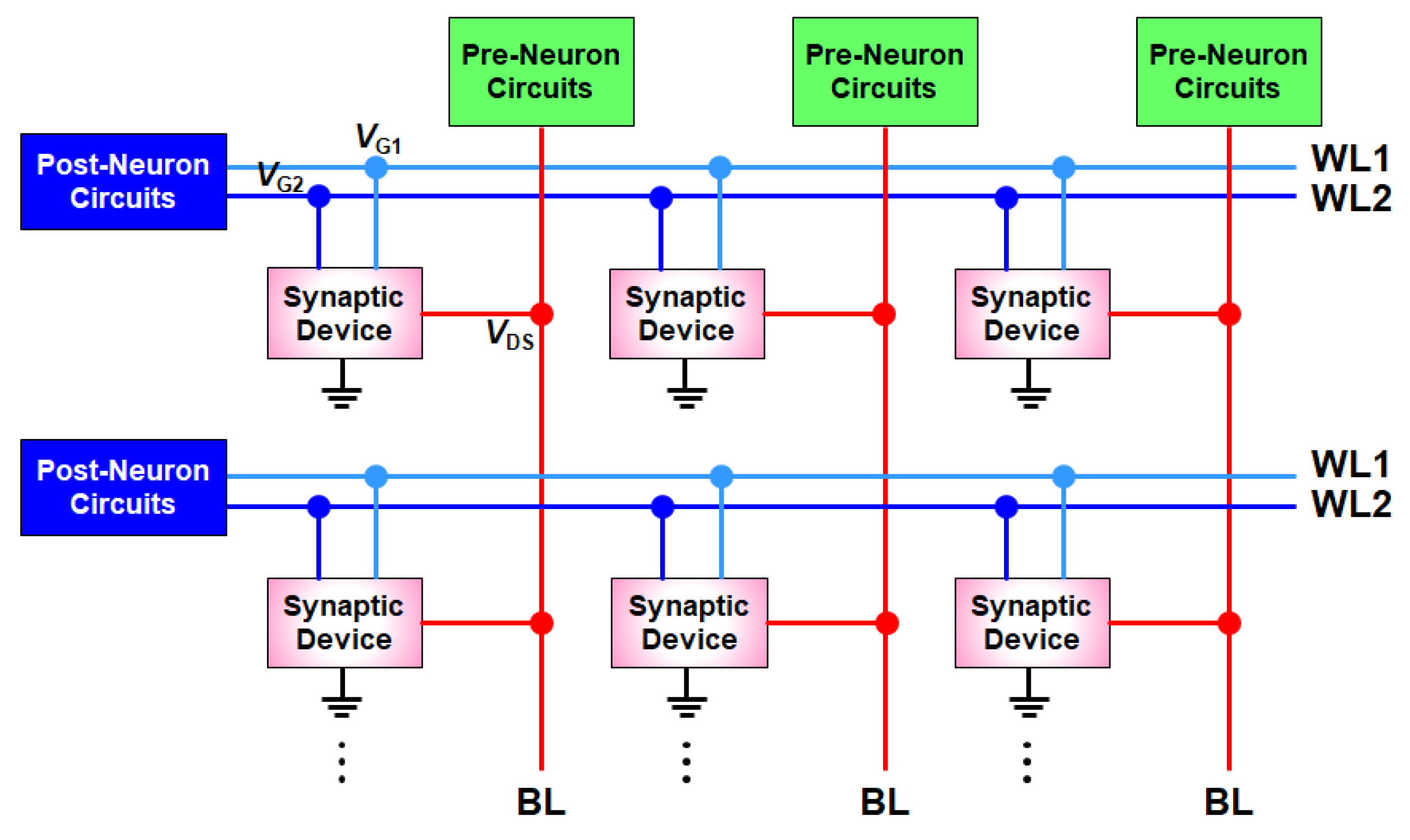

3.4. Spike-Timing-Difference Plasticity and Array Architecture

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Mead, C. Neuromorphic Electronic Systems. Proc. IEEE 1990, 78, 1629–1636. [Google Scholar] [CrossRef]

- Burr, G.W.; Shelby, R.M.; Sebastian, A.; Kim, S.; Kim, S.; Sidler, S.; Virwani, K.; Ishii, M.; Narayana, P.; Fumarola, A.; et al. Neuromorphic computing using non-volatile memory. Adv. Phys. 2017, 2, 89–124. [Google Scholar] [CrossRef]

- Shin, M.; Min, K.; Shim, H.; Kwon, Y. Investigation on Phase-change Synapse Devices for More Gradual Switching. J. Semicond. Technol. Sci. 2019, 19, 8–17. [Google Scholar] [CrossRef]

- Pham, K.V.; Nguyen, T.V.; Tran, S.B.; Nam, H.; Lee, M.J.; Choi, B.J.; Truong, S.N.; Min, K.S. Memristor Binarized Neural Networks. J. Semicond. Technol. Sci. 2018, 18, 568–577. [Google Scholar] [CrossRef]

- Sharad, M.; Fan, D.; Roy, K. Spin-neurons: A possible path to energy-efficient neuromorphic computers. J. Appl. Phys. 2013, 114, 234906. [Google Scholar] [CrossRef]

- Cho, H.; Son, H.; Kim, J.-S.; Kim, B.; Park, H.-J.; Sim, J.-Y. Design of Digital CMOS Neuromorphic IC with Current-starved SRAM Synapse for Unsupervised Stochastic Learning. J. Semicond. Technol. Sci. 2018, 18, 65–77. [Google Scholar] [CrossRef]

- Chu, M.; Kim, B.; Park, S.; Hwang, H.; Jeon, M.; Lee, B.H.; Lee, B.-G. Neuromorphic Hardware System for Visual Pattern Recognition with Memristor Array and CMOS Neuron. IEEE Trans. Ind. Electron. 2015, 62, 2410–2419. [Google Scholar] [CrossRef]

- Kim, K.H.; Gaba, S.; Wheeler, D.; Cruz-Albrecht, J.M.; Hussain, T.; Srinivasa, N.; Lu, W. A Functional Hybrid Memristor Crossbar-Array/CMOS System for Data Storage and Neuromorphic Applications. Nano Lett. 2012, 12, 389–395. [Google Scholar] [CrossRef]

- Park, S.; Noh, J.; Choo, M.; Sheri, A.M.; Chang, M.; Kim, Y.B.; Kim, C.J.; Jeon, M.; Lee, B.G.; Lee, B.H.; et al. Nanoscale RRAM-based synaptic electronics: Toward a neuromorphic computing device. Nanotechnology 2013, 24, 384009. [Google Scholar] [CrossRef]

- SILVACO. Atlas User’s Manual; SILVACO: Santa Clara, CA, USA, 2016. [Google Scholar]

- Xu, W.; Min, S.Y.; Hwang, H.; Lee, T.W. Organic core-sheath nanowire artificial synapses with femtojoule energy consumption. Sci. Adv. 2016, 2, 1–7. [Google Scholar] [CrossRef]

- Busch, G.; Vogt, O. Elektrische Leitfähigkeit und Halleffekt von Ge-Si-Legierungen. Helv. Phys. Acta 1960, 33, 437–458. [Google Scholar] [CrossRef]

- Fischetti, M.V.; Laux, S.E. Band structure, deformation potentials, and carrier mobility in strained Si, Ge, and SiGe alloys. J. Appl. Phys. 1996, 80, 2234–2252. [Google Scholar] [CrossRef]

- Ershov, M.; Ryahii, V. High-Field Electron Transport in SiGe Alloy. Jpn. J. Appl. Phys. 1994, 33, 1365–1372. [Google Scholar] [CrossRef]

- Smith, J. Longitudinal Anisotropy of the High-Field Conductivity of n-Type Germanium at Room Temperature. Phys. Rev. 1969, 178, 1364–1367. [Google Scholar] [CrossRef]

- Canali, C.; Majni, G.; Minder, R.; Ottaviani, G. Electron and Hole Drift Velocity Measurements in Silicon and Their Empirical Relation to Electric Field and Temperature. IEEE Trans. Electron Devices 1975, 22, 1045–1047. [Google Scholar] [CrossRef]

- Ottaviani, G.; Reggiani, L.; Canali, C.; Nava, F.; Alberigi-Quaranta, A. Hole Drift Velocity in Silicon. Phys. Rev. B 1975, 12, 3318–3329. [Google Scholar] [CrossRef]

- Ryder, E.J. Mobility of Holes and Electrons in High Electric Fields. Phys. Rev. 1953, 90, 766–769. [Google Scholar] [CrossRef]

- Liou, T.S.; Wang, T.; Chang, C.Y. Analysis of High-Field Hole Transport Characteristics in Si1-xGex Alloys with a Bond Orbital Band Structure. J. Appl. Phys. 1996, 79, 259–263. [Google Scholar] [CrossRef]

- Braunstein, R.; Moore, A.R.; Herman, F. Intrinsic Optical Absorption in Germanium-Silicon Alloys. Phys. Rev. 1958, 109, 695–710. [Google Scholar] [CrossRef]

- Chretien, O.; Apetz, R.; Souifi, A.; Vescan, L. Si1-xGex/Si valence band offset determination using current-voltage characteristics. Thin Solid Films 1997, 294, 198–200. [Google Scholar] [CrossRef]

- People, R.; Bean, J.C.; Lang, D.V.; Sergent, A.M.; Störmer, H.L.; Wecht, K.W. Modulation doping in GexSi1-x/Si strained layer heterostructures. Appl. Phys. Letts. 1984, 45, 1231–1233. [Google Scholar] [CrossRef]

- Takagi, S.; Hoyt, J.L.; Rim, K.; Welser, J.J.; Gibbons, J.F. Evaluation of the Valence Band Discontinuity of Si/Si1-xGex/Si Heterostructures by Application of Admittance Spectroscopy to MOS Capacitors. Electron Devices IEEE Trans. 1998, 45, 494–501. [Google Scholar] [CrossRef]

- Nauka, K.; Kamins, T.I.; Turner, J.E.; King, C.A.; Hoyt, J.L.; Gibbons, J.F. Admittance spectroscopy measurements of band offsets in Si/Si1-xGex/Si heterostructures. Appl. Phys. Letts. 1992, 60, 195–197. [Google Scholar] [CrossRef]

- Sant, S.; Lodha, S.; Ganguly, U.; Mahapatra, S.; Heinz, F.O.; Smith, L.; Moroz, V.; Ganguly, S. Band gap bowing and band offsets in relaxed and strained Si1-xGex alloys by employing a new nonlinear interpolation scheme. J. Appl. Phys. 2013, 113, 033708. [Google Scholar] [CrossRef]

- Walle, C.G.V.; Martin, R.M. Theoretical calculations of heterojunction discontinuities in the Si/Ge system. Phys. Rev. B 1986, 34, 5621–5634. [Google Scholar] [CrossRef]

- Kurdi, M.; Sauvage, S.; Fishman, G.; Boucaud, P. Band-edge alignment of SiGe/Si quantum wells and SiGe/Si self-assembled islands. Phys. Rev. B 2006, 73, 195327. [Google Scholar] [CrossRef]

- Yu, E.; Lee, W.J.; Jung, J.; Cho, S. Ultrathin SiGe Shell Channel p-Type FinFET on Bulk Si for Sub-10-nm Technology Nodes. IEEE Trans. Electron Devices 2018, 65, 1290–1297. [Google Scholar] [CrossRef]

- Hebb, D.O. The Organization of Behavior; Wiley: New York, NY, USA, 1949. [Google Scholar]

- Yu, E.; Cho, S.; Shin, H.; Park, B.G. A Band-Engineered One-Transistor DRAM with Improved Data Retention and Power Efficiency. IEEE Electron Device Lett. 2019, 40, 562–565. [Google Scholar] [CrossRef]

- Kuzum, D.; Yu, S.; Wong, P. Synaptic electronics: Materials, devices and applications. Nanotechnology 2013, 24, 1–22. [Google Scholar] [CrossRef]

- Huttenlocher, P. Synaptic density in human frontal cortex—Develop-metal changes and effects on aging. Brain Res. 1979, 163, 195–205. [Google Scholar] [CrossRef]

- Lennie, P. The cost of cortical computation. Curr. Biol. 2003, 13, 493–497. [Google Scholar] [CrossRef]

- Harris, J.; Jolivet, R.; Attwell, D. Synaptic Energy Use and Supply. Neuron 2012, 75, 762–777. [Google Scholar] [CrossRef] [PubMed]

- Wang, Y.; Wang, R.; Xu, X. Neural Energy Supply-Consumption Properties Based on Hodgkin-Huxley Model. Neural Plast. 2017, 2017, 6207141. [Google Scholar] [CrossRef] [PubMed]

- Attwell, D.; Laughlin, S. An Energy Budget for Signaling in the Gray Matter of the Brain. J. Cereb. Blood Flow Metab. 2001, 21, 1133–1145. [Google Scholar] [CrossRef]

- Howarth, C.; Peppiatt-Wildman, C.; Attwell, D. The energy use associated with neural computation in the cerebellum. J. Cereb. Blood Flow Metab. 2010, 30, 403–414. [Google Scholar] [CrossRef]

- Tech Insights. Samsung 18 nm DRAM Cell Integration: QPT and Higher Uniformed Capacitor High-k Dielectrics. Available online: https://www.techinsights.com/blog/samsung-18-nm-dram-cell-integration-qpt-and-higher-uniformed-capacitor-high-k-dielectrics (accessed on 14 June 2017).

| μn [cm/V·s] | μp [cm/V·s] | vsat,n [cm/s] | vsat,p [cm/s] | χ [eV] | Eg [eV] | |

|---|---|---|---|---|---|---|

| Si | 1590.0 | 570.00 | 1.02 × 107 | 7.33 × 106 | 4.050 | 1.10 |

| Si0.7Ge0.3 | 170.02 | 178.81 | 6.08 × 106 | 5.17 × 106 | 3.975 | 0.965 |

| VG1 | VG2 | VDS | Time | Energy | ||

|---|---|---|---|---|---|---|

| Potentiation | −0.2 V | −0.7 V | 0.55 V | 1 μs | 0.52 fJ | |

| Depression | 0 V | 6 V | 0 V | 1 μs | 1.51 fJ | |

| Inference | −0.1 V | 0 V | −0.1 V | 10 ns | Initial | 6.42 × 10−24 J |

| 20 pulsed | 1.87 × 10−16 J | |||||

| 40 pulsed | 5.24 × 10−16 J | |||||

| Synapse density | 9.09 × 109/cm2 (∵Unit cell size: 95 nm × 117 nm) | |||||

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yu, E.; Cho, S.; Park, B.-G. A Silicon-Compatible Synaptic Transistor Capable of Multiple Synaptic Weights toward Energy-Efficient Neuromorphic Systems. Electronics 2019, 8, 1102. https://doi.org/10.3390/electronics8101102

Yu E, Cho S, Park B-G. A Silicon-Compatible Synaptic Transistor Capable of Multiple Synaptic Weights toward Energy-Efficient Neuromorphic Systems. Electronics. 2019; 8(10):1102. https://doi.org/10.3390/electronics8101102

Chicago/Turabian StyleYu, Eunseon, Seongjae Cho, and Byung-Gook Park. 2019. "A Silicon-Compatible Synaptic Transistor Capable of Multiple Synaptic Weights toward Energy-Efficient Neuromorphic Systems" Electronics 8, no. 10: 1102. https://doi.org/10.3390/electronics8101102

APA StyleYu, E., Cho, S., & Park, B.-G. (2019). A Silicon-Compatible Synaptic Transistor Capable of Multiple Synaptic Weights toward Energy-Efficient Neuromorphic Systems. Electronics, 8(10), 1102. https://doi.org/10.3390/electronics8101102