1. Introduction

The continuous demand for high-performance millimeter and sub-millimeter receivers for radio astronomy has driven the development of increasingly compact, integrated, and low-noise front-end technologies. In this framework, the Advanced European THz Receiver Array (AETHRA) [

1,

2] project was launched to design and demonstrate a new generation of cryogenic front-end modules based on fully integrated Monolithic Microwave Integrated Circuits (MMICs) [

3]. AETHRA aimed to cover frequencies up to the terahertz range, with Work Package 1 (WP1) focused on the development of a W-band (75–116 GHz) downconverter module that integrated all the main Radio Frequency (RF), Local Oscillator (LO), and Intermediate Frequency (IF) functionalities on a single MMIC platform. The WP1 downconverter, developed at the Fraunhofer Institute for Applied Solid State Physics (IAF) and tested at the Institut de Radioastronomie Millimétrique (IRAM) in Grenoble, included Low-Noise Amplifiers (LNAs), sub-harmonic mixers, LO frequency multipliers, and power amplifiers.

The characterization of the AETHRA WP1 module revealed that its MMIC power amplifiers require significantly higher currents than typical cryogenic LNA stages. The schematic diagrams of the AETHRA WP1 downconverter shown in

Figure 1 and

Figure 2 provide the estimated current requirements of the two power amplifiers (PA1 and PA2):

Such requirements exceed the capability of the GAIA digital bias board [

4]. Originally developed by the Italian National Institute for Astrophysics (INAF)–Astronomical Observatory of Cagliari, GAIA is a programmable, rack-mountable power supply unit specifically designed for the remote biasing, monitoring, and control of LNAs in large radio telescope receivers, featuring high stability and RFI mitigation techniques. Although its maximum current drain of 50 mA per channel is optimal for most current applications, this limits its scope to excluding the direct driving of high-power MMICs (monolithic microwave integrated circuits).

To extend GAIA’s functionality for high-current devices, a dedicated Power Stage GAIA (PSG) board was developed at INAF. The PSG is a four-layer analog extension capable of supplying up to 500 mA at 5 V on each of ten channels, resulting in a total deliverable power of 25 W, while maintaining full digital monitoring and control through the standard GAIA interface. It is worth noting that, although the target application involves cryogenic receivers, the PSG board itself is designed as warm support electronics to operate at room temperature. Although the specific application presented in this work requires drain voltages below 2 V, the PSG was designed as a general-purpose platform for future astronomical instrumentation, supporting up to 5 V to ensure compatibility with other MMIC technologies (e.g., commercial GaN or GaAs devices) requiring standard 3 V or 5 V drain supplies. The system employs linear voltage buffers for power delivery and high-precision current-sense amplifiers for current monitoring, integrated into closed-loop feedback acquisition. The latest firmware revision ensures full compatibility and supports real-time supervision of all voltages and currents provided by the PSG.

A key design driver of the PSG was the need to preserve the extremely low electromagnetic footprint required by sensitive cryogenic receivers. Unlike switching or digitally intensive power systems, the PSG architecture is fully based on linear analog components operating in continuous mode. This approach aims to avoid generating the fast transitions or harmonics typically associated with digital circuitry. Consequently, the design goal was to ensure that the PSG does not produce the spectral lines characteristic of digital systems or the broadband emissions arising from electronic switching, making it intrinsically a very low RFI emitter.

The GAIA + PSG system was therefore designed for minimal electromagnetic interference, high bias stability, and modular scalability. Each GAIA board can manage one PSG board, together controlling up to ten high-current channels suitable for biasing the MMIC [

5] amplifiers within the AETHRA WP1 downconverter. The resulting architecture provides an efficient, low-noise, and digitally controlled solution for cryogenic front-ends requiring precise high-current biasing.

This paper describes the design methodology, electronic architecture, and validation of the GAIA + PSG system, highlighting the performance improvements achieved compared with standard biasing approaches. The results demonstrate the effectiveness of a modular, microcontroller-based linear bias architecture for next-generation multi-channel cryogenic receivers in radio astronomy and related applications. This work introduces a novel biasing solution that specifically addresses the stringent requirements of next-generation radio astronomical receivers. Unlike standard commercial off-the-shelf units or efficient switching power supplies, which often compromise on spectral purity or remote manageability, the proposed system uniquely combines three critical factors: (i) the high-current capability necessary to drive modern power-hungry MMICs, (ii) a fully linear architecture that eliminates switching noise to ensure a pristine electromagnetic environment (RFI-free), and (iii) native integration into the established GAIA digital monitoring and control framework. This synergistic approach provides a robust, low-noise, and remotely programmable platform essential for the reliable operation of advanced cryogenic front-ends. The paper is organized as follows:

Section 2 describes the materials and methods, detailing the architecture of the GAIA control board and the design of the new Power Stage GAIA (PSG) extension, including the firmware implementation.

Section 3 presents the experimental results, covering static characterization, dynamic stability analysis, and noise performance.

Section 4 discusses the implications of these results for next-generation cryogenic receivers. Finally,

Section 5 summarizes the conclusions and outlines future work.

2. Materials and Methods

The GAIA + PSG system has been conceived as a modular digital bias platform capable of supplying, monitoring, and controlling up to ten independent bias channels for MMIC devices. The system consists of two stacked printed-circuit boards (PCBs): the GAIA board, which provides digital control, monitoring, and communication functions; and the Power Stage GAIA (PSG) board, which supplies the required high-current. The two boards are connected through a dedicated parallel connector carrying power, I2C, and digital control lines.

2.1. GAIA Control Board

The GAIA board acts as the main controller and user interface. It is based on an ATMega2560 microcontroller running custom firmware that manages up to ten bias channels. Each channel includes programmable independent voltages generated through AD5231 [

6] digital potentiometers and monitored by 16-bit LTC2495 [

7] ADCs. Communication with an external control unit (e.g., PC or telescope monitor system) is achieved via USB or serial interfaces using a simple ASCII protocol. The firmware provides continuous real-time readout of bias voltages and currents, automatic fault detection, and data logging.

The board includes low-noise voltage references, EMI filters on all analog lines, and a carefully designed ground plane layout to minimize RFI. In particular, the last revision of the board improves noise immunity, ADC accuracy, and compatibility with the PSG extension. The main specifications of the GAIA board are summarized in

Table 1 and the 3D rendering is illustrated in

Figure 3.

2.2. Power Stage GAIA (PSG) Board

The PSG board extends the current capability of GAIA to meet the requirements of the AETHRA WP1 downconverter. Each of the ten channels on the PSG provides a regulated drain voltage up to 5 V and a maximum current of 500 mA. A key design requirement was the preservation of the extremely low electromagnetic footprint essential for observation sites. Therefore, the architecture avoids switching converters or high-frequency clocked blocks entirely. Instead, it is based on LT1970 [

8] power operational amplifiers configured as linear voltage followers operating in continuous mode. This ensures high output current and low noise without generating the fast transitions or harmonics typical of digital power supplies. Current measurement is performed through precision shunt resistors and INA225 [

9] instrumentation amplifiers, whose analog outputs are digitized by the GAIA ADCs. The INA225 was specifically selected for its high precision, low offset drift, and hardware-selectable gain capabilities.

A TCA9555 I/O expander handles channel enabling, fault detection, and overcurrent protection logic. The PSG board features a four-layer PCB design with separated analog and digital ground planes to minimize crosstalk and ensure thermal stability. To address the challenges of combining high-current delivery with low-noise performance, the PCB layout was meticulously organized into four functional layers (see

Figure 4 for the stack-up details):

Top Layer (Figure 5): This layer hosts the main power components, including the ten LT1970 amplification stages and the conditioning cells. The placement is optimized to facilitate heat dissipation from the power amplifiers.

Inner Layers (Figure 6 and Figure 7): The second and third layers are characterized by a thicker copper profile (35

m) compared to the outer layers (18

m). This design choice minimizes the impedance of the high-current power distribution paths and provides robust ground planes.

Bottom Layer (Figure 8): This layer is primarily used for routing the interconnection signals and the digital control bus.

Figure 5.

Layout of the top layer.

Figure 5.

Layout of the top layer.

Figure 6.

Layout of the second layer.

Figure 6.

Layout of the second layer.

Figure 7.

Layout of the third layer.

Figure 7.

Layout of the third layer.

Figure 8.

Layout of the bottom layer.

Figure 8.

Layout of the bottom layer.

A critical aspect of the layout is the grounding strategy. The inner layers are utilized to create extensive ground planes that effectively shield the sensitive analog traces from Electromagnetic Interference (EMI) and RFI. Furthermore, the layout enforces a strict separation between the analog and digital ground domains, which join only at a single star point to prevent ground loops and digital noise coupling. The trace routing was also optimized to minimize crosstalk between adjacent channels, avoiding sharp

angles to mitigate signal reflections. The board complies with the 3U standard Eurocard form factor (

mm), as shown in the 3D rendering (

Figure 9) and the realized prototype (

Figure 10), ensuring seamless mechanical integration into the GAIA rack system. The entire board was designed using Autodesk Eagle software, version 9.6.2.

All components were selected for low offset, high linearity, and operation over a wide temperature range (−40 °C to +85 °C). The main specifications of the PSG board are reported in

Table 2.

2.3. System Description, Firmware Implementation, and Operation

For the monitoring and control of the PSG board, the GAIA board was selected. This version includes a dedicated digital GPIO pin for verifying the presence of the PSG board, connected through a compatible backplane and used for hardware presence detection. The firmware used in this work is an upgraded version of the original GAIA firmware, extending its functionality to control the ADCs for interrogation and to manage the enable/disable logic of the PSG amplifiers.

The firmware also implements monitoring and calibration capabilities. In this mode, the system reads the voltage and current values. To ensure the accuracy of the reported measurements, the GAIA and PSG boards undergo joint laboratory calibration prior to deployment; the resulting calibration constants are stored in the GAIA’s internal memory. To maintain transparency during operation, the external commands for reading

V and

I, as well as for enabling channels, remain unchanged with respect to the original GAIA firmware. Internally, however, the system dynamically adapts its behavior depending on whether the PSG board is detected, either activating or bypassing the PSG electronics. Specifically, the firmware utilizes the TCA9555 [

10] I/O expander via the I

2C bus to physically enable the PSG channels only when required, minimizing power consumption and potential digital noise when the extension is not in use.

During normal operation, the GAIA microcontroller sets the desired drain and gate voltages for each channel through digital commands. The PSG converts these control voltages into high-current outputs, while the INA225 amplifiers continuously measure the corresponding currents. The feedback signals are digitized and returned to the GAIA ADCs for monitoring and regulation. This closed-loop configuration ensures stable bias conditions and precise control of the high power operating points.

The modular architecture allows cascading multiple GAIA+PSG units to serve multi-channel or multi-polarization receivers. Specifically, scalability beyond ten channels is achieved by installing additional GAIA+PSG units in the rack, interconnected via a wired or PCB backplane and managed through the Ethernet interface. The communication protocol is designed to support this expansion seamlessly.

Figure 11 illustrates the functional block diagram of a single bias channel. All bias parameters are logged and can be remotely adjusted through the control interface, ensuring full flexibility and traceability for both laboratory and telescope environments.

The resulting GAIA+PSG system offers a scalable, low-noise, and digitally controlled bias solution capable of sustaining the high-current requirements of the AETHRA WP1 downconverter as well as future cryogenic multibeam receivers.

3. Results

The Power Stage GAIA (PSG) prototype was validated through a series of electrical bench tests performed at the INAF–Astronomical Observatory of Cagliari laboratories. The primary objective of these tests was to verify the capability of the PSG board to deliver high currents with low noise and high voltage stability, while maintaining full digital control via the GAIA interface. All tests were carried out at room temperature and under nominal power supply conditions of V and +5 V.

3.1. Static Characterization

Each of the ten PSG channels was characterized by measuring the output voltage and current response under resistive loads ranging from 50

to 10

, corresponding to drain currents designed for up to 500 mA at 5 V. Under the test conditions reported here, the system was tested up to a maximum output current of 460 mA.

Figure 12 illustrates the measured output power (

) and current (

) as a function of the output voltage (

), highlighting the linear current increase up to the tested upper limit of 460 mA. Measurements were taken on all ten channels. As the results were identical, only the measurement for Channel 1 is shown for clarity. The LT1970-based output stages exhibited a linear transfer function across the entire operating range, with an average voltage accuracy better than 1 mV and output noise below 0.5 mV

RMS. Current sensing via the INA225 amplifiers provided a resolution of 0.5 mA, consistent with the 16-bit conversion accuracy of the LTC2495 ADC. The measured performance confirmed full compliance with the design goals, providing an order of magnitude higher current capability compared with the original GAIA bias board.

3.2. Dynamic Response and Stability

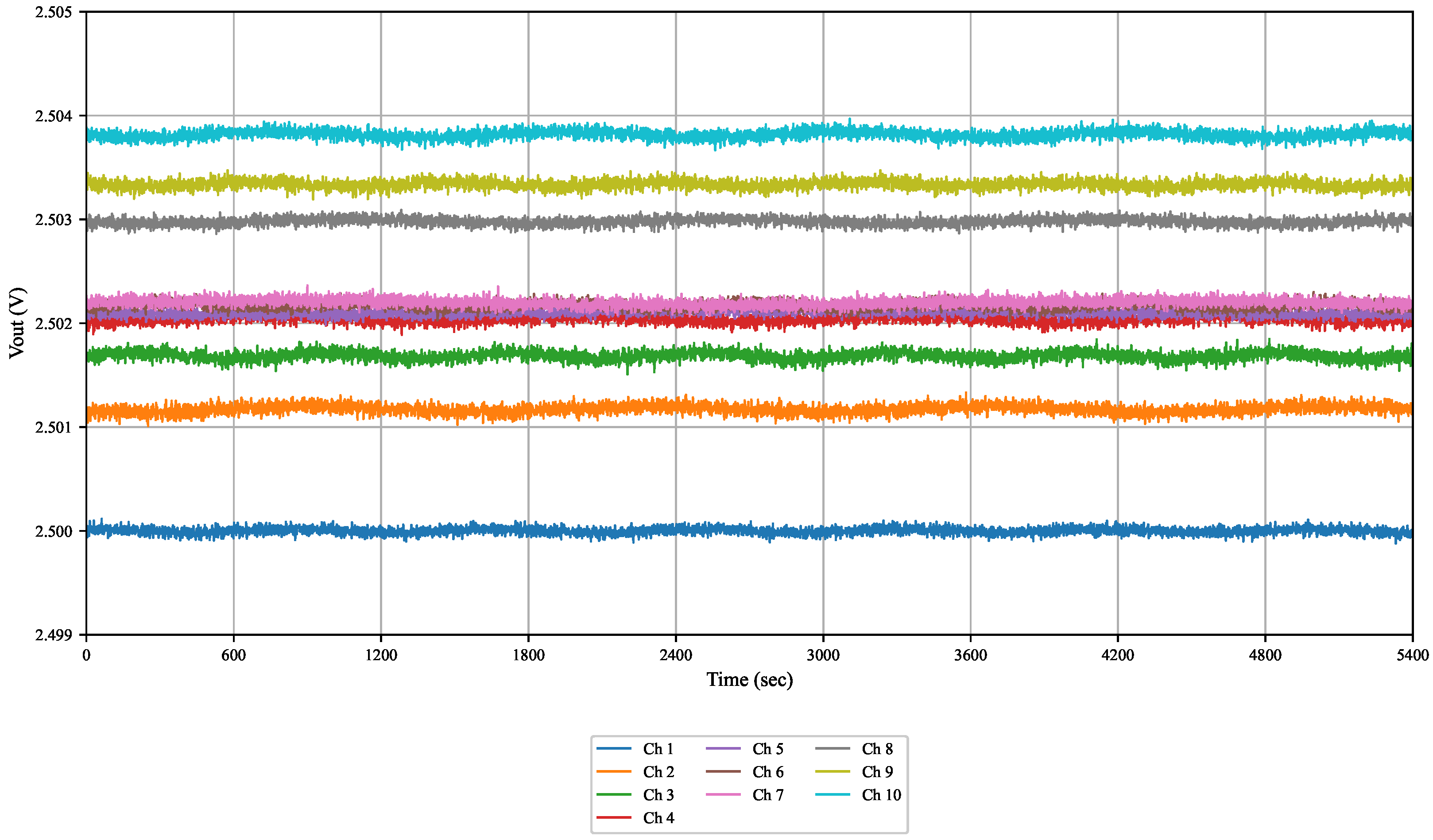

Dynamic tests were conducted by applying step changes to the programmed voltage in the 0–5 V range and monitoring the response through the GAIA–PSG control interface. The system exhibited a settling time below 10 ms for a full-scale voltage step, with negligible overshoot and no oscillatory behavior, confirming the intrinsic stability of the feedback network implemented around each LT1970 amplifier. Long-term stability measurements were also performed by monitoring the voltage over 90-min intervals, as illustrated in

Figure 13. This observation window was specifically chosen because it vastly exceeds the typical integration times of the target astronomical signals, which are generally below 1 s (<1 s). The RMS deviation shown in

Table 3 remained below 47

across all channels, demonstrating excellent stability of the PSG circuitry and of the onboard voltage references. The system utilizes components rated for an extended operational range (

°C to

°C). Stability is further ensured by the active feedback loop, which effectively compensates for any thermal drift in the transistor parameters, maintaining a constant output voltage. Indeed, the reported long-term measurements naturally include thermal settling effects and show minimal variations (<50

V), confirming the thermal robustness of the design.

In addition to the unloaded stability test, an identical long-term measurement was repeated by applying a resistive load that draws 300 mA from the supply while maintaining the programmed voltage at 2.5 V (mid-scale). Even under high-power conditions, the PSG voltage regulation loop confirmed its stability, preserving the same performance during nominal operation (specifically at 0.75 W per single channel). Crucially, the system remained stable under load, with no measurable increase in drift or noise. The corresponding results are shown in

Figure 14. The RMS deviation shown in

Table 4 remained below 149

across all channels.

3.3. Noise and Electromagnetic Compatibility

Noise characterization was performed using a low-frequency spectrum analyzer connected to the output of each PSG channel under a 100 load. The spectral density was found to be flat down to a few hertz, with no significant spurious tones within the 0–1 kHz band. In addition, qualitative electromagnetic compatibility tests were conducted by operating the GAIA + PSG system in proximity to an RF receiver front-end mock-up. No measurable increase in background noise or RFI was detected. Specifically, the PSG did not introduce measurable interference in the P, L, S, or C bands, confirming that the linear design successfully eliminates the spectral lines characteristic of digital systems and the broadband emissions typical of switching converters. Any residual impact on the observed radio spectrum was found to be dominated by thermal noise.

3.4. System Integration Tests

Functional validation of the combined GAIA + PSG system was carried out using the updated GAIA firmware, which provides full support for PSG communication and monitoring. The test setup consisted of ten independent high-current channels driven through the standard GAIA interface and controlled via a LAN connection from a laboratory PC as depicted in

Figure 15. All channels operated nominally, with real-time current and voltage telemetry matching the corresponding external measurements. These results confirm the effectiveness of the PSG as a modular, low-noise, high-current extension of the GAIA architecture, suitable for biasing MMIC devices in advanced cryogenic receiver systems such as the AETHRA WP1 downconverter.

4. Discussion

The experimental results confirm that the Power Stage GAIA (PSG) board successfully meets the demanding electrical and stability requirements of next-generation cryogenic receivers envisioned by the AETHRA project. The capability to deliver up to 25 W with low noise and high voltage stability represents a significant improvement over the baseline GAIA bias system, which was originally designed for low-current LNA stages. This enhancement enables the biasing of power-hungry MMIC amplifiers integrated in W-band downconverter modules, such as those developed within AETHRA Work Package 1. Moreover, the system offers immediate software adaptability for different biasing requirements. Since the output voltage is fully programmable (0–5 V) and the current is continuously monitored, the PSG can bias any LNA or PA that falls within these electrical specifications, regardless of the device’s operating frequency band.

From an architectural standpoint, the PSG demonstrates that a modular and microcontroller-based approach can be effectively extended to higher current levels without compromising noise or electromagnetic performance. The integration of precision analog components—LT1970 power stages, INA225 current sensors, and 16-bit ADCs—within a digitally controlled framework allows for both fine-grained control and robust system supervision. The use of an I2C-based communication interface ensures full compatibility with existing GAIA hardware and firmware, minimizing development overhead and facilitating system scalability.

Although the validation reported here was performed at room temperature, the observed voltage stability and low output noise suggest that the PSG will maintain excellent performance under cryogenic conditions. The design margin in current and voltage delivery, combined with its low RFI emission, makes the GAIA + PSG system a strong candidate for integration into future multi-channel cryogenic front-ends for millimeter and sub-millimeter astronomy. Future work will include the characterization of the PSG under cryogenic load conditions and its full integration within the AETHRA WP1 receiver chain, to verify long-term stability, noise coupling, and system reliability in operational environments.

5. Conclusions

This work presented the design, implementation, and validation of the Power Stage GAIA (PSG), a high-current digital bias extension of the GAIA system developed at INAF for the AETHRA project. The PSG provides up to 500 mA per channel with precise digital control, low output noise, and excellent long-term stability, thereby extending the applicability of the GAIA architecture to the biasing of high-power MMIC amplifiers used in advanced cryogenic front-ends.

Experimental validation performed at the laboratory level demonstrated linear operation, high voltage accuracy, and negligible electromagnetic interference, confirming the robustness and scalability of the proposed design. The modular GAIA + PSG system offers a compact, low-noise, and digitally supervised solution suitable for integration in multi-channel receiver arrays operating in the millimeter and sub-millimeter bands.

Future developments will focus on cryogenic validation and full integration within the AETHRA WP1 downconverter chain, with the aim of assessing performance under realistic operating conditions and paving the way toward next-generation, fully integrated bias systems for radio astronomical instrumentation.

This activity was carried out within the framework of the AETHRA–Advanced European THz Receiver Array project, supported by the European Union and coordinated by INAF in collaboration with Fraunhofer IAF and IRAM Grenoble.

Author Contributions

Conceptualization, P.O., A.S., G.V. and A.N.; methodology, P.O., A.S. and G.V.; software, A.S. and A.C.; validation, P.O., G.V., A.S., A.C. and R.C.; formal analysis, P.O., G.V. and A.S.; investigation, A.S., A.C., G.V. and P.O.; resources, A.N., P.O., A.S., R.C. and G.V.; data curation, A.S., A.C., P.O. and G.V.; writing—original draft preparation, P.O., A.C., G.V. and A.S.; writing—review and editing, A.N. and G.M.; visualization, A.C. and P.O.; supervision, P.O.; project administration, P.O.; funding acquisition, A.N. All authors have read and agreed to the published version of the manuscript.

Funding

This research was supported by the European Union’s Horizon 2020 research and innovation programme under grant number 730562 (RadioNet), via the AETHRA WP1 project.

Data Availability Statement

The original contributions presented in this study are included in the article. Further inquiries can be directed to the corresponding authors.

Conflicts of Interest

The authors declare no conflicts of interest.

Abbreviations

The following abbreviations are used in this manuscript:

| PSG | Power Stage Gaia |

| MMIC | Monolithic Microwave Integrated Circuits |

| AETHRA | Advanced European THz Receiver Array |

| LO | Local Oscillator |

| RF | Radio Frequency |

| LNA | Low-Noise Amplifier |

| RFI | Radio Frequency Interference |

| ADC | Analog-to-Digital Converter |

| I2C | Inter-Integrated Circuit |

| PCB | Printed Circuit Board |

| USB | Universal Serial Bus |

| ASCII | American Standard Code for Information Interchange |

| EMI | Electromagnetic Interference |

| IAF | Fraunhofer Institute for Applied Solid State Physics |

| INAF | Istituto Nazionale di Astrofisica |

| IRAM | Institut de radioastronomie millimétrique |

| RMS | Root Mean Square |

| LAN | Local Area Network |

| WP | Work Package |

References

- AETHRA (Advanced European THz Receiver Array). European Research Project, WP1: W-Band Downconverter, 2020. A Collaboration Between MPIfR (Max Planck Institute for Radio Astronomy), Bonn, Germany, IRAM (Institut de RadioAstronomie Millimetrique), Grenoble, France, INAF (National Institute for Astrophysics)-Astronomical Observatory of Cagliari, Selargius, Italy, and IAF (Fraunhofer Institute for Applied Solid State Physics), Freiburg, Germany. Available online: https://radiowiki.mpifr-bonn.mpg.de/lib/exe/fetch.php?media=jra%3A730562_radionet_wp5.pdf (accessed on 2 December 2025).

- Serres, P.; Navarrini, A.; Garnier, O.; Schaefer, F.; Türk, S.; Thome, F.; Ortu, P.; Valente, G.; Saba, A.; Fontana, A.L.; et al. Demonstrator of Cryogenic Multibeam Receiver with MMIC LNAs for 75–116 GHz. In Proceedings of the 32nd IEEE International Symposium on Space THz Technology (ISSTT 2022), Baeza, Spain, 16–20 October 2022; Available online: https://www.proceedings.com/content/073/073155webtoc.pdf (accessed on 2 December 2025).

- Wang, H.; Chen, M. Cryogenic MMIC Low-Noise Amplifiers for Radio Telescope Applications. Electronics 2025, 14, 1572. [Google Scholar] [CrossRef]

- Ortu, P.; Saba, A.; Valente, G.; Muntoni, G.; Navarrini, A.; Pisanu, T.; Ghiani, R.; Urru, E.; Montisci, G. A New Monitor and Control Power Supply PCB for Biasing LNAs of Large Radio Telescopes Receivers. IEEE Access 2023, 11, 53134–53143. [Google Scholar] [CrossRef]

- Lamb, J.W. Evaluation of biasing and protection circuitry components for cryogenic MMIC low-noise amplifiers. Cryogenics 2014, 61, 43–52. [Google Scholar] [CrossRef]

- Analog Devices. AD5231: 1024-Position Digital Potentiometer Datasheet, 2015. Datasheet. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/ad5231.pdf (accessed on 2 December 2025).

- Analog Devices. LTC2495: 16-Channel, 16-Bit ADC Datasheet, 2014. Datasheet. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/2495fe.pdf (accessed on 2 December 2025).

- Analog Devices/Linear Technology. LT1970: Precision, High Output Drive Op Amp Datasheet, 2020. Datasheet. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/1970fe.pdf (accessed on 2 December 2025).

- Texas Instruments. INA225: Precision Current-Sense Instrumentation Amplifier Datasheet, 2018. Datasheet. Available online: https://www.ti.com/lit/ds/symlink/ina225.pdf (accessed on 2 December 2025).

- Texas Instruments. TCA9555: I2C I/O Expander Datasheet, 2016. Datasheet. Available online: https://www.ti.com/lit/ds/symlink/tca9555.pdf (accessed on 2 December 2025).

Figure 1.

Schematic diagram of the fully integrated MMIC downconverter for AETHRA WP1 (75–116 GHz) designed at IAF, showing the main subcircuits: RF hybrid, sub-harmonic mixers, IF LNAs, LO chain with power amplifiers, and frequency multiplier.

Figure 1.

Schematic diagram of the fully integrated MMIC downconverter for AETHRA WP1 (75–116 GHz) designed at IAF, showing the main subcircuits: RF hybrid, sub-harmonic mixers, IF LNAs, LO chain with power amplifiers, and frequency multiplier.

Figure 2.

DC−bias scheme for AETHRA downconverter module.

Figure 2.

DC−bias scheme for AETHRA downconverter module.

Figure 3.

A 3D rendering of the front side of the GAIA board.

Figure 3.

A 3D rendering of the front side of the GAIA board.

Figure 4.

Cross-sectional layer stack-up of the PSG board.

Figure 4.

Cross-sectional layer stack-up of the PSG board.

Figure 9.

A 3D rendering of the front side of the PSG board, showing the main power-supply circuitry.

Figure 9.

A 3D rendering of the front side of the PSG board, showing the main power-supply circuitry.

Figure 10.

Photograph of the front side of the PSG board.

Figure 10.

Photograph of the front side of the PSG board.

Figure 11.

Block diagram of the PSG (right) and connection to the GAIA board (left) through a backplane or cable (for rack mounting on a 19-inch chassis) using I2C bus.

Figure 11.

Block diagram of the PSG (right) and connection to the GAIA board (left) through a backplane or cable (for rack mounting on a 19-inch chassis) using I2C bus.

Figure 12.

Measured output characteristics for Channel 1. The plot displays the output power (, left axis) and current (, right axis) as a function of the output voltage (). The red dashed line indicates the upper current limit of .

Figure 12.

Measured output characteristics for Channel 1. The plot displays the output power (, left axis) and current (, right axis) as a function of the output voltage (). The red dashed line indicates the upper current limit of .

Figure 13.

Long-term stability measurements of the voltage across channels CH1–CH10. The monitoring was performed over a 90-min interval (), showing steady output voltages around with minimal thermal drift.

Figure 13.

Long-term stability measurements of the voltage across channels CH1–CH10. The monitoring was performed over a 90-min interval (), showing steady output voltages around with minimal thermal drift.

Figure 14.

Summary of the long-term stability performance under unloaded and 300 mA loaded conditions. The table reports, for each channel, the mean output voltage and the RMS deviation (standard deviation) computed over the 90-min acquisition interval, highlighting the consistent stability of the voltage regulation loop across operating scenarios.

Figure 14.

Summary of the long-term stability performance under unloaded and 300 mA loaded conditions. The table reports, for each channel, the mean output voltage and the RMS deviation (standard deviation) computed over the 90-min acquisition interval, highlighting the consistent stability of the voltage regulation loop across operating scenarios.

Figure 15.

Experimental setup used for powering, controlling, and monitoring the GAIA and PSG boards. The power supply (Rohde & Schwarz HMP4040) provides the +5 V, +12 V, and −12 V rails to both boards, while a PC communicates with the GAIA unit via Ethernet and with the PSG unit through the parallel and I2C interfaces. The output voltage and current delivered to the external load are measured using a voltmeter and an ammeter (Rohde & Schwarz HMC8012).

Figure 15.

Experimental setup used for powering, controlling, and monitoring the GAIA and PSG boards. The power supply (Rohde & Schwarz HMP4040) provides the +5 V, +12 V, and −12 V rails to both boards, while a PC communicates with the GAIA unit via Ethernet and with the PSG unit through the parallel and I2C interfaces. The output voltage and current delivered to the external load are measured using a voltmeter and an ammeter (Rohde & Schwarz HMC8012).

Table 1.

Main specifications of the GAIA control board (without PSG extension).

Table 1.

Main specifications of the GAIA control board (without PSG extension).

| Parameter | Value/Description |

|---|

| Number of channels | 10 (independent gate/drain) |

| Gate voltage range | −6.5–5 V (programmable) |

| Drain voltage range | 0–5 V (programmable) |

| Drain current capability | up to 50 mA per channel |

| ADC resolution | 16 bit (LTC2495) |

| Digital potentiometer | AD5231 (1024 steps) |

| Communication interface | USB/UART (ASCII protocol) |

| Control bus to PSG | I2C, 100 kHz |

| Typical RFI emission | <−100 dBm Hz−1 at 1 GHz |

Table 2.

Main specifications of the PSG board.

Table 2.

Main specifications of the PSG board.

| Parameter | Value/Description |

|---|

| Number of independent channels | 10 |

| Maximum output current | 500 mA per channel |

| Voltage range | 0–5 V (programmable) |

| Current sensing | INA225 + precision shunt |

| Control and protection | TCA9555 digital driver |

| ADC feedback resolution | 16 bit (from GAIA) |

| PCB structure | 4 layers, mixed-signal layout (see Figure 10) |

| Power supply input | +6 V DC/5 A max |

| Communication | I2C bus from GAIA board |

Table 3.

Summary of the long-term stability performance. The table lists the mean output voltage and the RMS deviation (standard deviation) calculated for each channel over the 90-min test interval.

Table 3.

Summary of the long-term stability performance. The table lists the mean output voltage and the RMS deviation (standard deviation) calculated for each channel over the 90-min test interval.

| Channel | Mean Voltage (V) | Standard Deviation (μV) |

|---|

| 1 | 2.503404 | 33.47 |

| 2 | 2.501104 | 34.75 |

| 3 | 2.500355 | 35.11 |

| 4 | 2.500601 | 36.83 |

| 5 | 2.502563 | 35.87 |

| 6 | 2.502690 | 46.27 |

| 7 | 2.500586 | 41.16 |

| 8 | 2.503802 | 36.94 |

| 9 | 2.502393 | 36.07 |

| 10 | 2.504047 | 35.95 |

Table 4.

Summary of the long-term stability performance under unloaded and 300 mA loaded conditions. The table reports, for each channel, the mean output voltage and the RMS deviation (standard deviation) computed over the 90-min acquisition interval, highlighting the consistent stability of the drain-voltage regulation loop across operating scenarios.

Table 4.

Summary of the long-term stability performance under unloaded and 300 mA loaded conditions. The table reports, for each channel, the mean output voltage and the RMS deviation (standard deviation) computed over the 90-min acquisition interval, highlighting the consistent stability of the drain-voltage regulation loop across operating scenarios.

| Channel | Mean Voltage (V) | Standard Deviation (μV) |

|---|

| 1 | 2.500310 | 101.67 |

| 2 | 2.501172 | 117.45 |

| 3 | 2.501685 | 106.76 |

| 4 | 2.502041 | 121.46 |

| 5 | 2.502107 | 119.32 |

| 6 | 2.502173 | 125.28 |

| 7 | 2.502196 | 149.65 |

| 8 | 2.502980 | 134.92 |

| 9 | 2.503338 | 118.92 |

| 10 | 2.503817 | 124.23 |

| Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |