Design of a Sub-6 GHz CMOS Power Amplifier with a High-Q Glass Transformer for Off-Chip Output-Matching Networks

Abstract

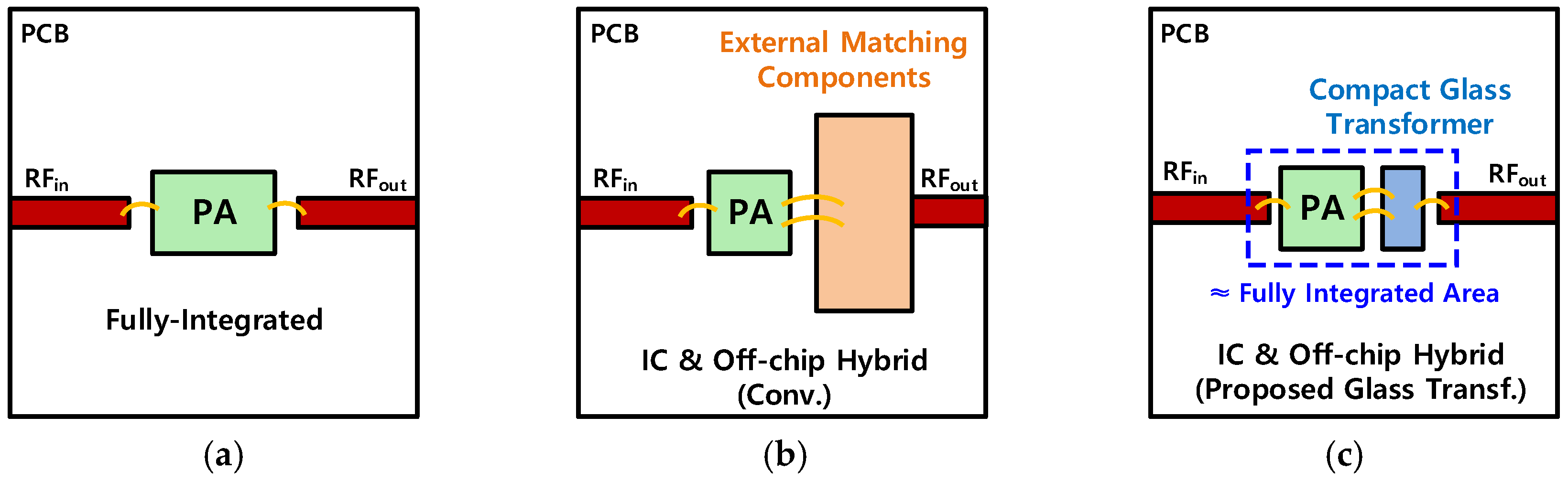

1. Introduction

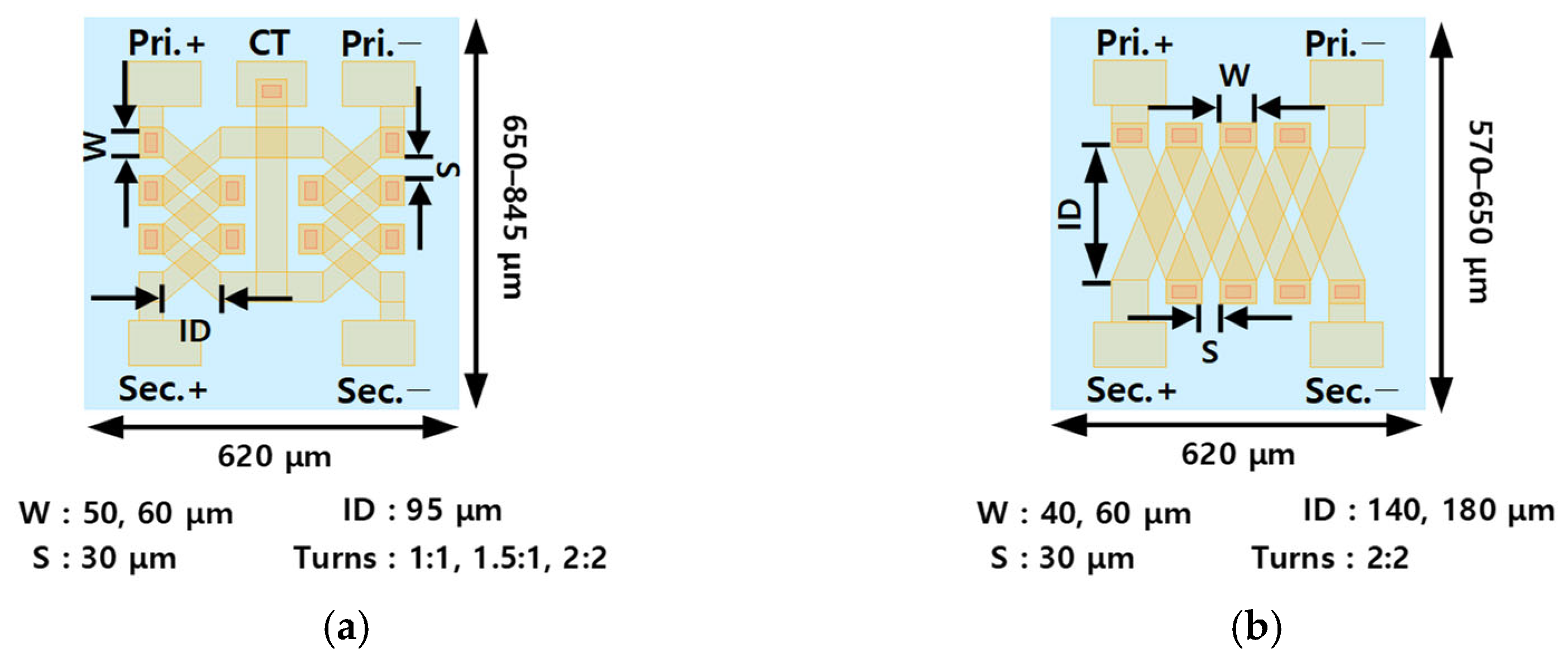

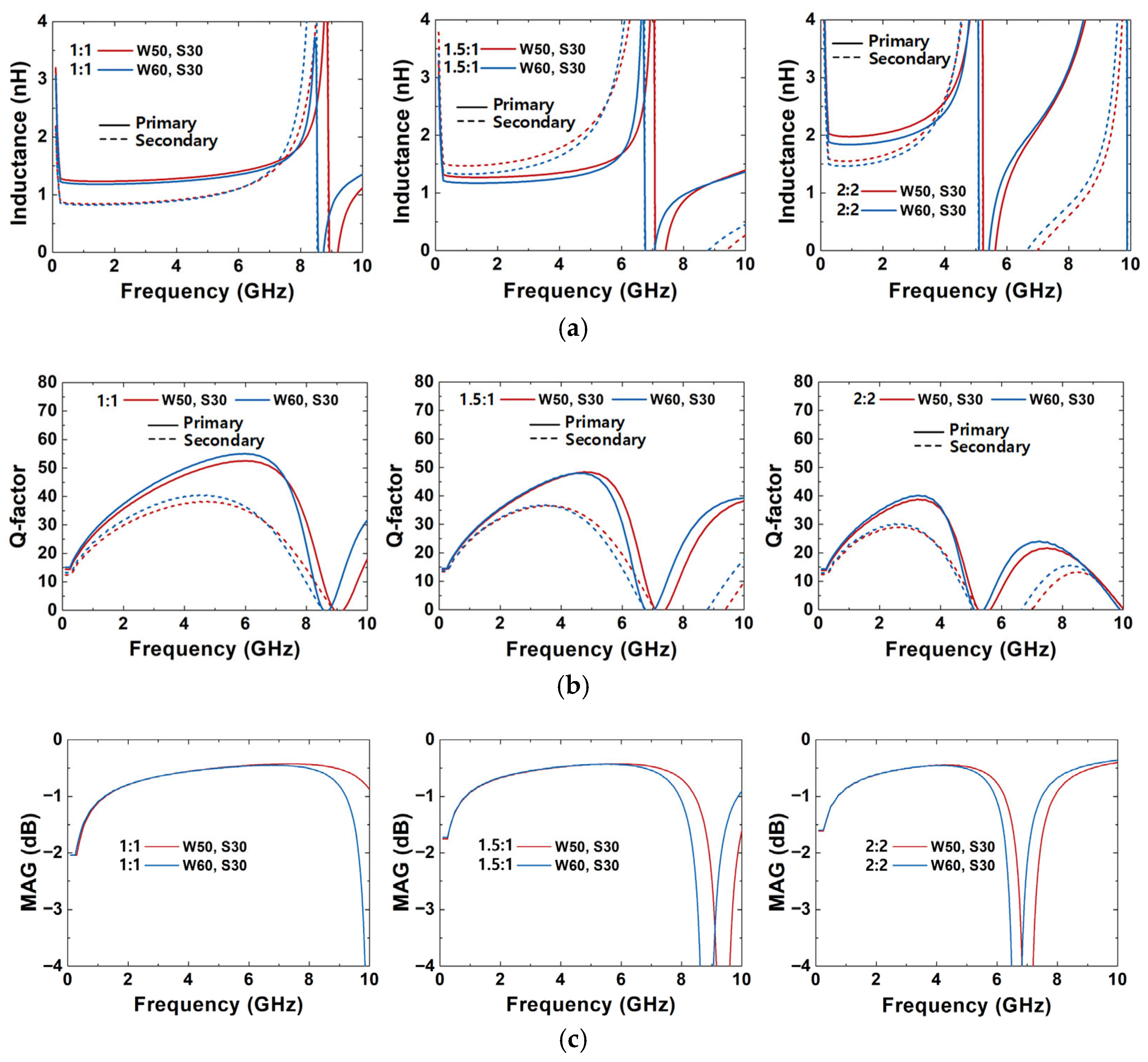

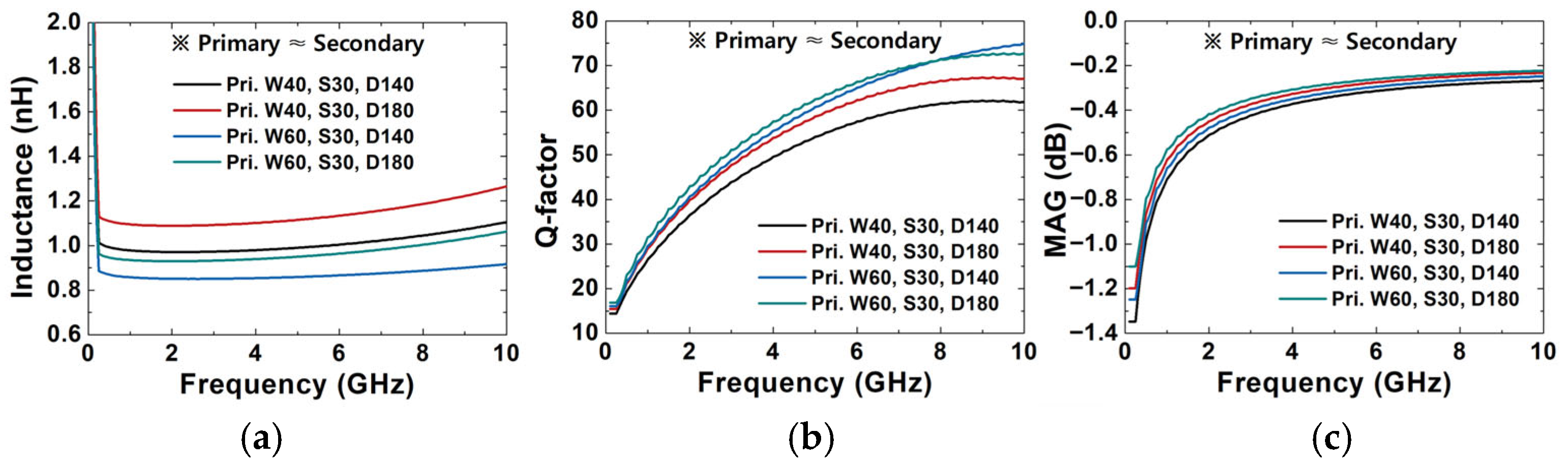

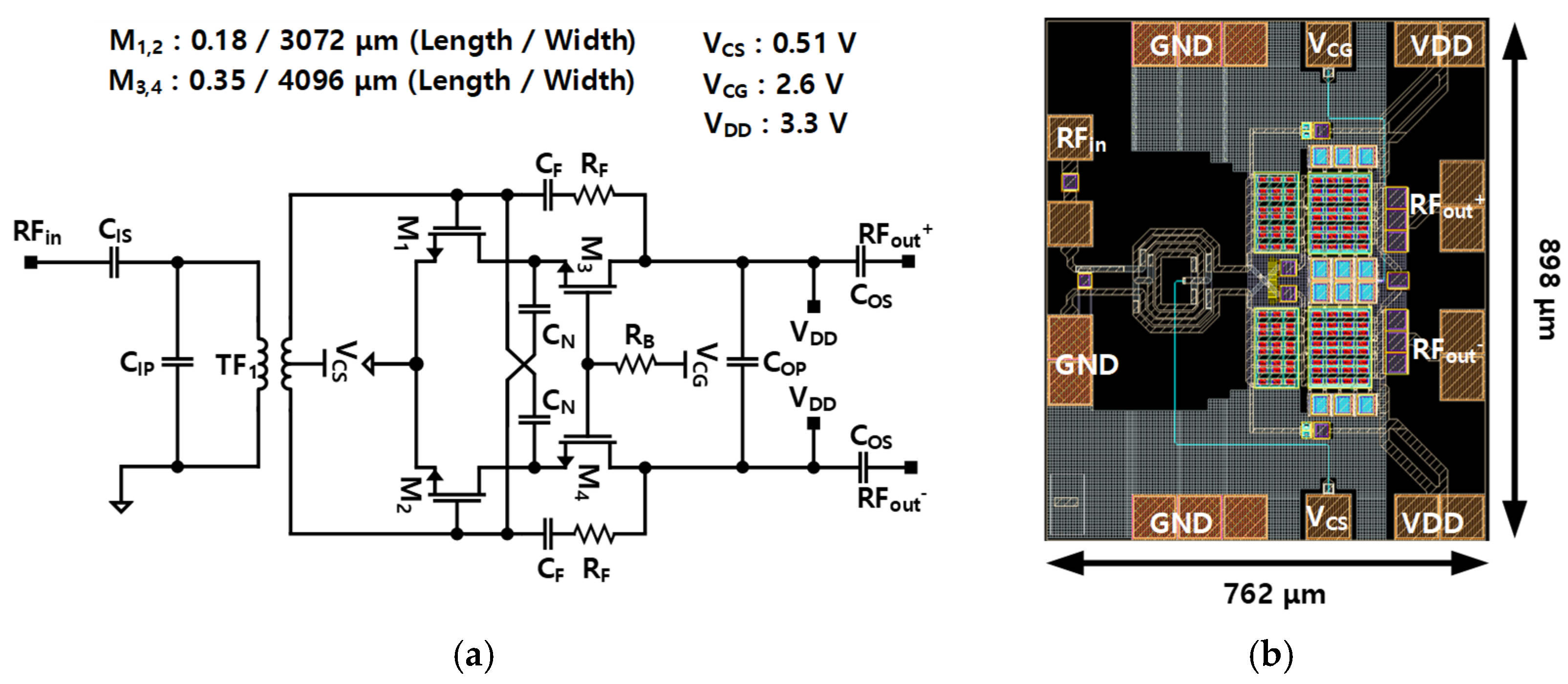

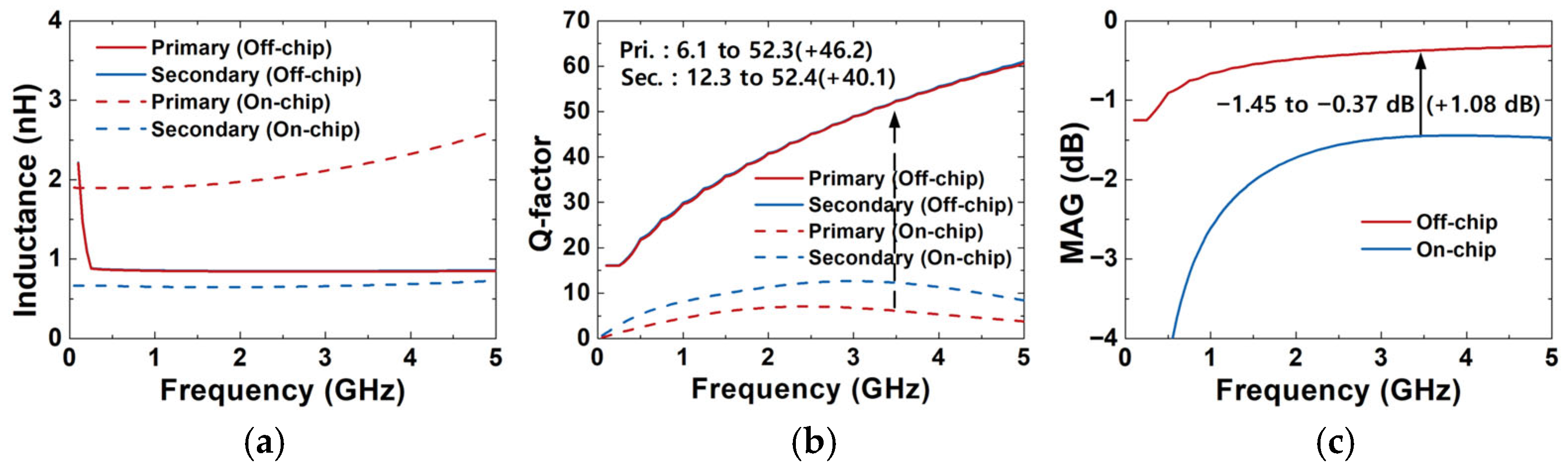

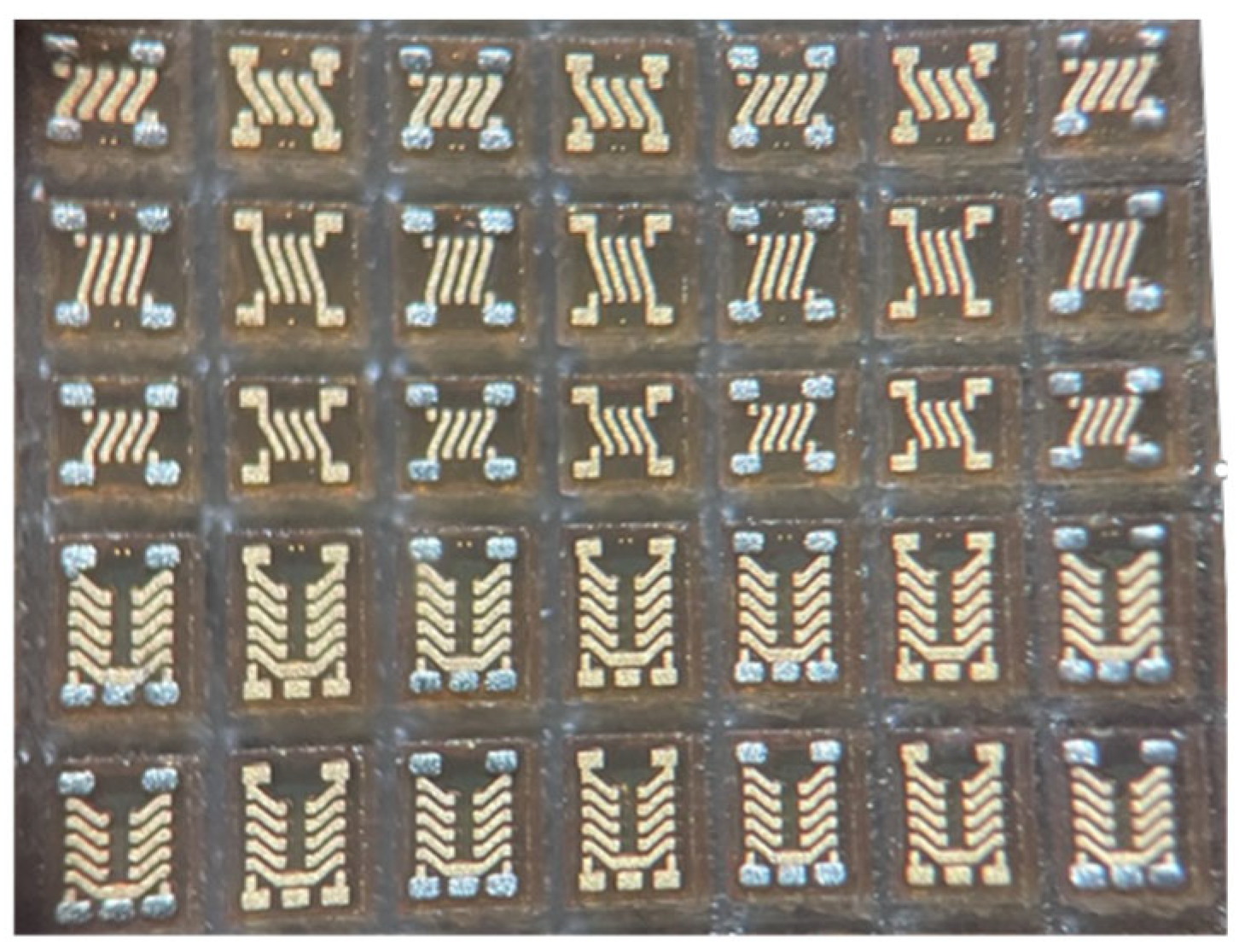

2. Design of High-Q Glass Transformer

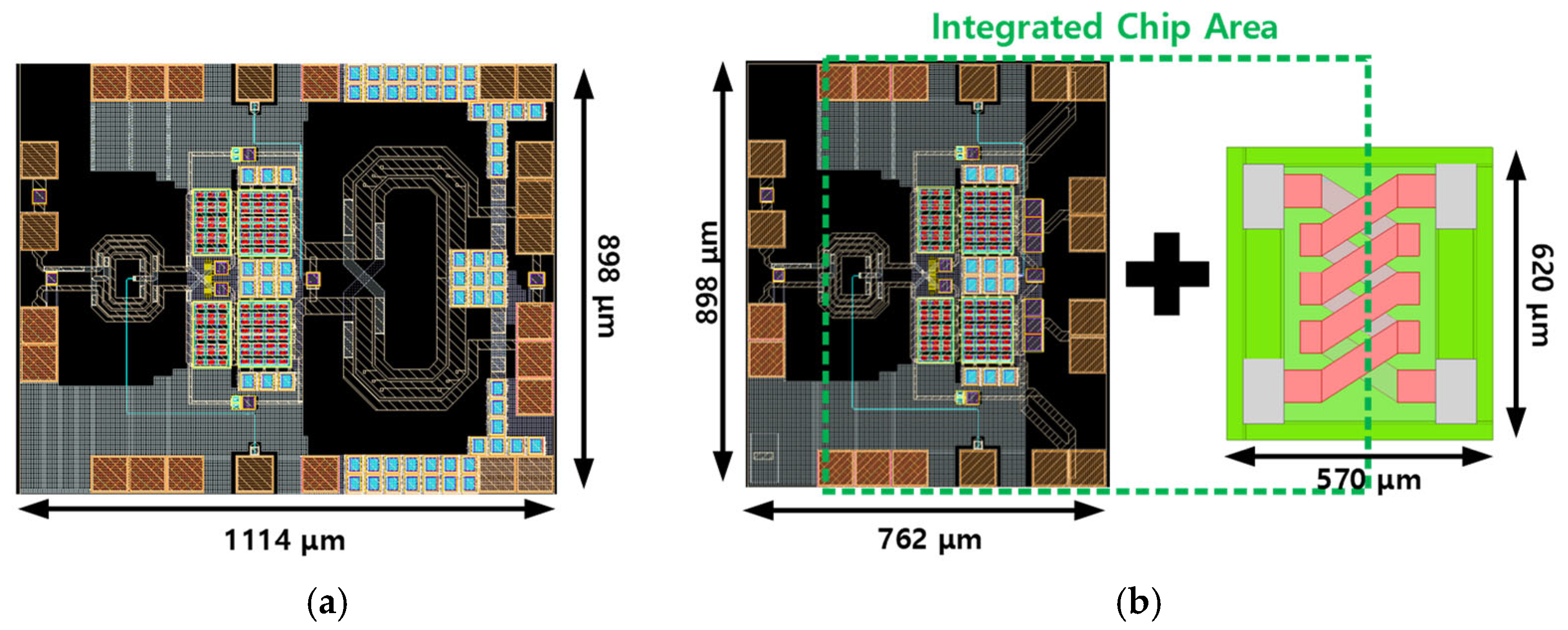

3. Design of Power Amplifier with High-Q Glass Transformer

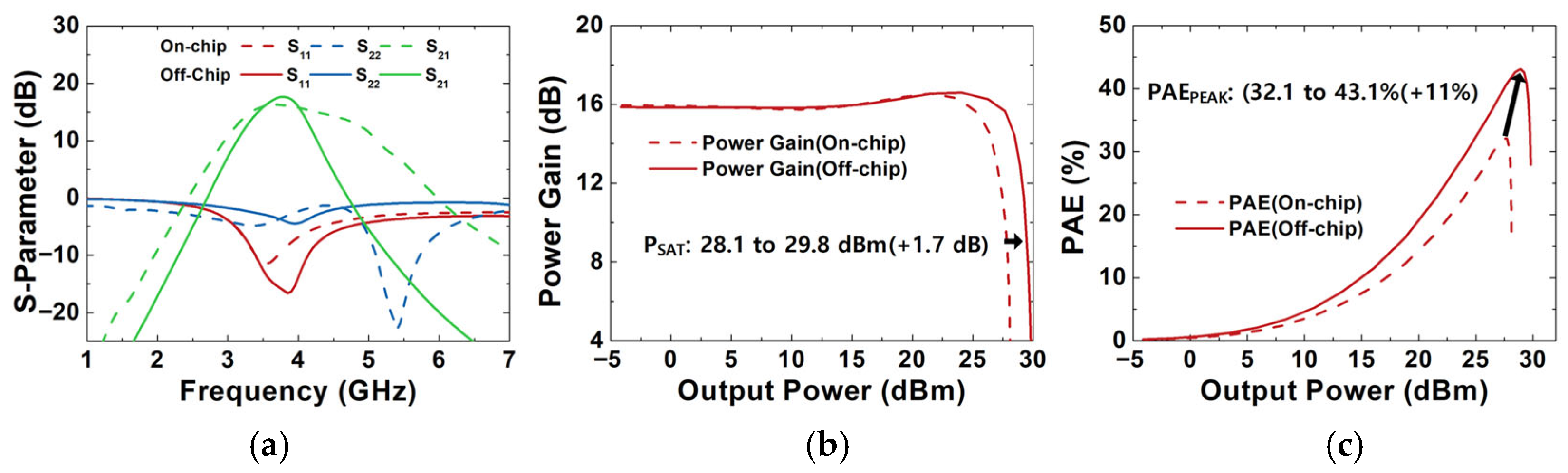

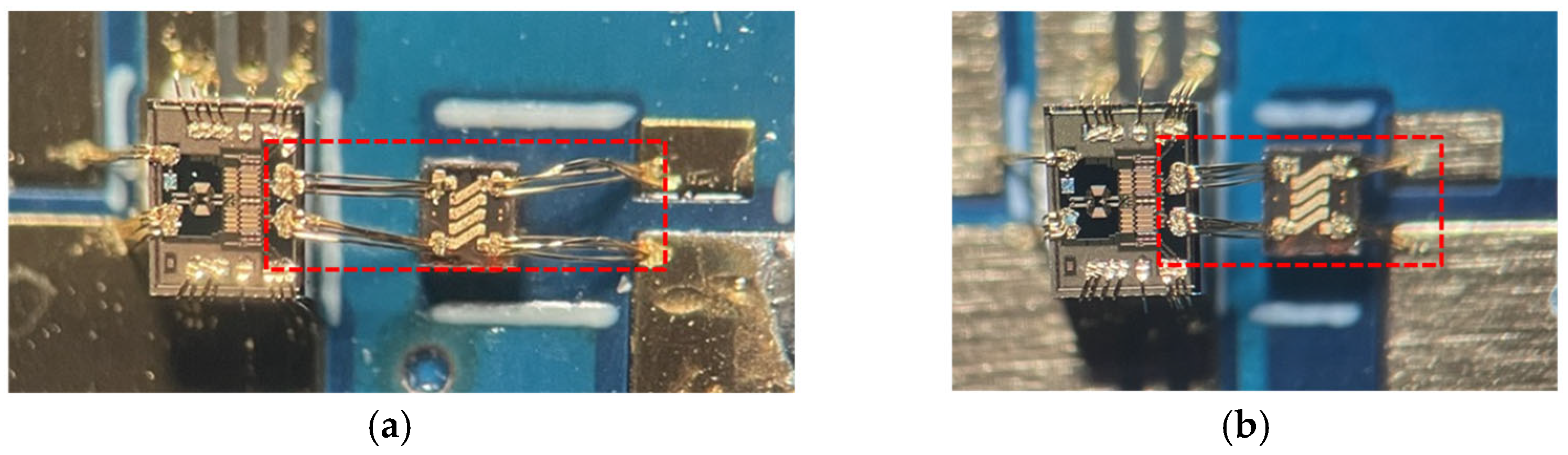

4. Assembly and Measurement of Power Amplifier with High-Q Glass Transformer

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Yue, C.P.; Wong, S.S. On-Chip Spiral Inductors with Patterned Ground Shields for Si-Based RF ICs. IEEE J. Solid-State Circuits 1998, 33, 743–752. [Google Scholar] [CrossRef]

- Mohan, S.S.; del Mar Hershenson, M.; Boyd, S.P.; Lee, T.H. Simple Accurate Expressions for Planar Spiral Inductances. IEEE J. Solid-State Circuits 1999, 34, 1419–1424. [Google Scholar] [CrossRef]

- Chen, H.-H.; Hsu, Y.-W. Analytic Design of on-Chip Spiral Inductor with Variable Line Width. Electronics 2022, 11, 2029. [Google Scholar] [CrossRef]

- Jang, J.; Park, C.; Kim, H.; Hong, S. A CMOS RF Power Amplifier Using an Off-Chip Transmission Line Transformer With 62% PAE. IEEE Microw. Wireless Compon. Lett. 2007, 17, 385–387. [Google Scholar] [CrossRef]

- Lim, W.; Kang, H.; Lee, W.; Bae, J.; Oh, S.; Oh, H.; Chae, S.; Hwang, K.-C.; Lee, K.-Y.; Yang, Y. Dual-Mode CMOS Power Amplifier Based on Load-Impedance Modulation. IEEE Microw. Wireless Compon. Lett. 2018, 28, 1041–1043. [Google Scholar] [CrossRef]

- Chiou, H.-K.; Lin, H.-C.; Chang, D.-C. High-Efficiency and Cost-Effective 10 W Broadband Continuous Class-J Mode Quasi-MMIC Power Amplifier Design Utilizing 0.25 μm GaN/SiC and GaAs IPD Technology for 5G NR n77 and n78 Bands. Electronics 2023, 12, 3494. [Google Scholar] [CrossRef]

- Eid, M.A.E.; Abouelnaga, T.G.; Ibrahim, H.A.; Hamad, E.K.I.; Al-Gburi, A.J.A.; Alghamdi, T.A.H.; Alathbah, M. Highly Efficient GaN Doherty Power Amplifier for N78 Sub-6 GHz Band 5G Applications. Electronics 2023, 12, 4001. [Google Scholar] [CrossRef]

- Que, X.; Li, J.; Wang, Y. A Broadband Three-Way Series Doherty Power Amplifier with Deep Power Back-Off Efficiency Enhancement for 5G Application. Electronics 2024, 13, 1882. [Google Scholar] [CrossRef]

- Angarita Malaver, E.F.; Barrera Lombana, N.; Moreno Rubio, J.J. Smith Chart-Based Design of High-Frequency Broadband Power Amplifiers. Electronics 2024, 13, 4096. [Google Scholar] [CrossRef]

- Vasjanov, A.; Barzdenas, V. A Review of Advanced CMOS RF Power Amplifier Architecture Trends for Low Power 5G Wireless Networks. Electronics 2018, 7, 271. [Google Scholar] [CrossRef]

- Lee, M.; Yoo, J.; Lee, J.; Park, C. Design Techniques for Wideband CMOS Power Amplifiers for Wireless Communications. Electronics 2024, 13, 1695. [Google Scholar] [CrossRef]

- Wang, Z.; Wang, X.; Liu, Y. A Wideband Power Amplifier in 65 nm CMOS Covering 25.8–36.9 GHz by Staggering Tuned MCRs. Electronics 2023, 12, 3566. [Google Scholar] [CrossRef]

- Wu, C.-H.; Tang, C.-C.; Liu, S.-I. Analysis of On-Chip Spiral Inductors Using the Distributed Capacitance Model. IEEE J. Solid-State Circuits 2003, 38, 1040–1044. [Google Scholar] [CrossRef]

- Jiang, H.; Yeh, J.L.A.; Tien, N.C. On-Chip Spiral Inductors Suspended over Deep Copper-Lined Cavities. IEEE Trans. Microw. Theory Tech. 2000, 48, 2415–2423. [Google Scholar] [CrossRef]

- Goñi, A.; del Pino, J.; González, B.; Hernández, A. An Analytical Model of Electric Substrate Losses for Planar Spiral Inductors on Silicon. IEEE Trans. Electron Devices 2007, 54, 546–553. [Google Scholar] [CrossRef]

- Ye, W.; Ma, K.; Yeo, K.S.; Zou, Q. A 65 nm CMOS Power Amplifier with Peak PAE above 18.9% from 57 to 66 GHz Using Synthesized Transformer-Based Matching Network. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 2533–2543. [Google Scholar] [CrossRef]

- Estrada, J.A.; Montejo-Garai, J.R.; de Paco, P.; Psychogiou, D.; Popović, Z. Power Amplifiers with Frequency-Selective Matching Networks. IEEE Trans. Microw. Theory Tech. 2021, 69, 697–708. [Google Scholar] [CrossRef]

- Wei, Z.; Huang, F.; Zhang, Y.; Tang, X.; Jiang, N. A Compact Transformer-Based E-Band CMOS Power Amplifier with Enhanced Efficiencies of 15.6% PAE1dB and 6.5% PAE at 6 dB Power Back-Off. Electronics 2022, 11, 1679. [Google Scholar] [CrossRef]

- Kim, M.S.; Pulugurtha, M.R.; Sundaram, V.; Tummala, R.R.; Yun, H. Ultrathin High-Q 2-D and 3-D RF Inductors in Glass Packages. IEEE Trans. Compon. Packag. Manuf. Technol. 2018, 8, 643–652. [Google Scholar] [CrossRef]

- Wu, X.; Wen, L.; Cao, L.; Cao, G.; Li, G.; Fu, Y.; Yu, Z.; Fang, Z.; Wang, Q. A Fully Integrated Solid-State Charge Detector with Through Fused Silica Glass Via Process. Electronics 2023, 12, 1045. [Google Scholar] [CrossRef]

- Huang, T.-J.; Kiebala, T.; Suflita, P.; Moore, C.; Housser, G.; McMahon, S.; Puchades, I. Comparative Analysis of Thermal Properties in Molybdenum Substrate to Silicon and Glass for a System-on-Foil Integration. Electronics 2024, 13, 1818. [Google Scholar] [CrossRef]

- Galler, T.; Chaloun, T.; Mayer, W.; Kröhnert, K.; Ambrosius, N.; Schulz-Ruhtenberg, M.; Waldschmidt, C. MMIC-to-Dielectric Waveguide Transitions for Glass Packages above 150 GHz. IEEE Trans. Microw. Theory Tech. 2023, 71, 2807–2817. [Google Scholar] [CrossRef]

- Park, J.; Lee, C.; Yoo, J.; Park, C. A CMOS Antiphase Power Amplifier with an MGTR Technique for Mobile Applications. IEEE Trans. Microw. Theory Tech. 2017, 65, 4645–4656. [Google Scholar] [CrossRef]

- Kim, T.; Park, C. Ka-Band Three-Stacked CMOS Power Amplifier with LC Shunt-Feedback to Enhance Gain and Stability. IEEE Trans. Circuits Syst. II Express Briefs 2024, 71, 1969–1973. [Google Scholar] [CrossRef]

- Asada, H.; Matsushita, K.; Bunsen, K.; Okada, K.; Matsuzawa, A. A 60 GHz CMOS Power Amplifier Using Capacitive Cross-Coupling Neutralization with 16% PAE. In Proceedings of the 41st European Microwave Conference (EuMC), Manchester, UK, 10–13 October 2011; pp. 1115–1118. [Google Scholar]

- Wu, H.; You, B.; Gao, K.-K.; Li, X.-G. A 4th-Order LTCC Bandpass Filter with Both Tunable Center Frequency and Bandwidth. Electronics 2022, 11, 4119. [Google Scholar] [CrossRef]

- Espinosa-Adams, D.; Llorente-Romano, S.; González-Posadas, V.; Jiménez-Martín, J.L.; Segovia-Vargas, D. Novel Dielectric Resonator-Based Microstrip Filters with Adjustable Transmission and Equalization Zeros. Electronics 2025, 14, 2557. [Google Scholar] [CrossRef]

- Tsai, J.-H. A 5.3-GHz 30.1-dBm Fully Integrated CMOS Power Amplifier with High-Power Built-In Linearizer. IEEE Microw. Wirel. Technol. Lett. 2023, 33, 431–434. [Google Scholar] [CrossRef]

- Ginzberg, N.; Cohen, E. A Wideband CMOS Power Amplifier With 52% Peak PAE Employing Resistive Shunt Feedback for Sub-6 GHz 5G Applications. IEEE Microw. Wirel. Technol. Lett. 2023, 33, 192–195. [Google Scholar] [CrossRef]

- Lin, H.-C.; Liao, H.-Z.; Chang, D.-C.; Chiou, H.-K. A Highly Linear Stacked CMOS Power Amplifier with Cold-FET Linearizer for Sub-6 GHz Applications. In Proceedings of the 2024 IEEE Asia-Pacific Microwave Conference (APMC), Bali, Indonesia, 17–20 November 2024; pp. 952–954. [Google Scholar] [CrossRef]

- Cancelli, R.; Avitabile, G.; Florio, A. Designing and Optimizing a 2.4 GHz Complementary Metal–Oxide–Semiconductor Class-E Power Amplifier Combining Standard and High-Voltage Metal–Oxide–Semiconductor Field-Effect Transistors. Electronics 2025, 14, 1135. [Google Scholar] [CrossRef]

| Turns | Width | Inductance (Primary) | Inductance (Secondary) | Q Factor (Primary) | Q Factor (Secondary) | MAG |

|---|---|---|---|---|---|---|

| 1:1 | 50 μm | 1.26 nH | 886.0 pH | 45.2 | 36.5 | −0.60 dB |

| 60 μm | 1.21 nH | 869.7 pH | 47.3 | 38.9 | −0.47 dB | |

| 1.5:1 | 50 μm | 1.32 nH | 1.67 nH | 44.6 | 38.9 | −0.51 dB |

| 60 μm | 1.22 nH | 1.53 nH | 45.0 | 36.8 | −0.51 dB | |

| 2:2 | 50 μm | 2.33 nH | 2.17 nH | 38.7 | 26.5 | −0.47 dB |

| 60 μm | 2.16 nH | 2.06 nH | 40.0 | 26.8 | −0.47 dB |

| Width | Diam. | Inductance (Primary) | Inductance (Secondary) | Q Factor (Primary) | Q Factor (Secondary) | MAG |

|---|---|---|---|---|---|---|

| 40 μm | 140 μm | 975.7 pH | 969.8 pH | 46.9 | 46.9 | −0.39 dB |

| 180 μm | 1.10 nH | 1.09 nH | 50.9 | 50.6 | −0.35 dB | |

| 60 μm | 140 μm | 852.3 pH | 846.0 pH | 52.3 | 52.4 | −0.37 dB |

| 180 μm | 935.4 pH | 931.2 pH | 54.5 | 55.2 | −0.32 dB |

| Component | Value | Component | Value |

|---|---|---|---|

| CIS | 884.8 fF | CN | 803.6 fF |

| CIP | 517.8 fF | CF | 1.90 pF |

| COP | 1.20 pF | RF | 607.1 Ω |

| COS | 2.85 pF | RB | 2 kΩ |

| Parameter | Long Bond Wire | Short Bond Wire | Simulation |

|---|---|---|---|

| S21,PEAK (dB) | 12.3 @3.04 GHz | 13.9 @3.43 GHz | 17.7 @3.8 GHz |

| PSAT (dBm) | 24.0 @2.9 GHz | 25.3 @2.9 GHz | 29.8 @3.5 GHz |

| PAEPEAK (%) | 10.2 @2.9 GHz | 16.1 @2.9 GHz | 43.1 @3.5 GHz |

| Ref. | Tech. | Freq. (GHz) | PSAT (dBm) | PAE (%) | Size (mm2) | FoM 2 |

|---|---|---|---|---|---|---|

| [28] | 0.18 μm | 5.3 | 30.1 | 18 | 2.96 | 0.062 |

| [29] | 65 nm | 0.33–2.5 | 19.5–21.5 | 35–52.4 | 0.49 | 0.151 |

| [30] | 0.18 μm | 2.9–5 | 25.7–27.2 | ≈15–25 | 3.70 | 0.035 |

| [31] 1 | 0.13 μm | 2.4 | 20.5 | 40.9 | 0.657 | 0.070 |

| This work 1 | 0.18 μm | 3.5 | 29.8 | 43.1 | 1.20 3 | 0.343 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, J.; Yook, J.-M.; Yoo, J.; Park, C. Design of a Sub-6 GHz CMOS Power Amplifier with a High-Q Glass Transformer for Off-Chip Output-Matching Networks. Electronics 2025, 14, 4261. https://doi.org/10.3390/electronics14214261

Lee J, Yook J-M, Yoo J, Park C. Design of a Sub-6 GHz CMOS Power Amplifier with a High-Q Glass Transformer for Off-Chip Output-Matching Networks. Electronics. 2025; 14(21):4261. https://doi.org/10.3390/electronics14214261

Chicago/Turabian StyleLee, Jaeyong, Jong-Min Yook, Jinho Yoo, and Changkun Park. 2025. "Design of a Sub-6 GHz CMOS Power Amplifier with a High-Q Glass Transformer for Off-Chip Output-Matching Networks" Electronics 14, no. 21: 4261. https://doi.org/10.3390/electronics14214261

APA StyleLee, J., Yook, J.-M., Yoo, J., & Park, C. (2025). Design of a Sub-6 GHz CMOS Power Amplifier with a High-Q Glass Transformer for Off-Chip Output-Matching Networks. Electronics, 14(21), 4261. https://doi.org/10.3390/electronics14214261