Thermal Management of Wide-Bandgap Power Semiconductors: Strategies and Challenges in SiC and GaN Power Devices

Abstract

1. Introduction

2. Thermal Generation in SiC and GaN Power Devices

2.1. Fundamental Thermal Properties and Loss Mechanisms

2.1.1. Conduction Losses

2.1.2. Switching Losses

2.1.3. Other Switching-Related Phenomena

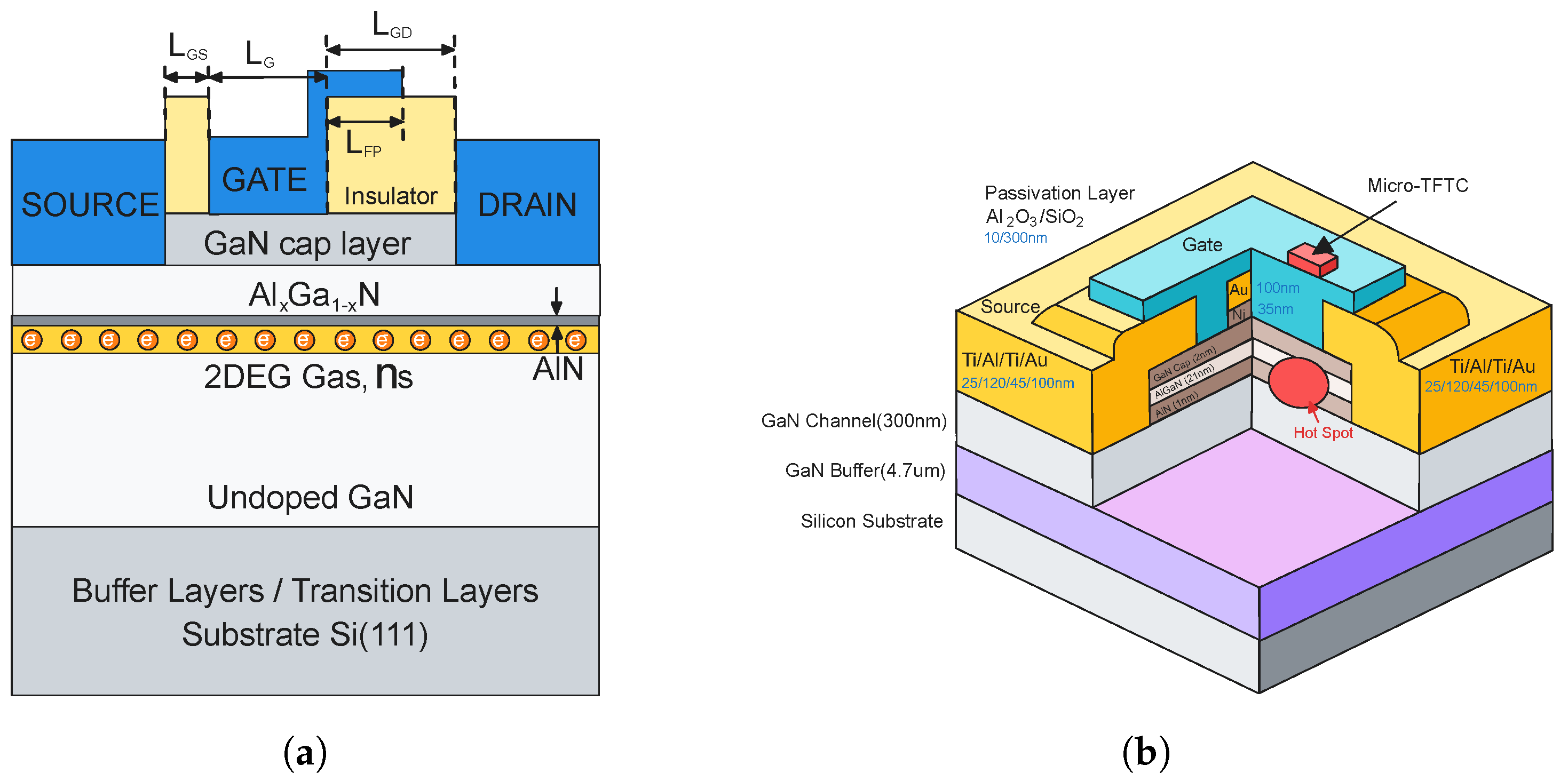

2.2. Device Structure and Localized Heating

3. Thermal Management Solutions for WBG Power Devices: Advanced Packaging and Cooling Techniques

3.1. Thermal Pathways and Packaging Materials

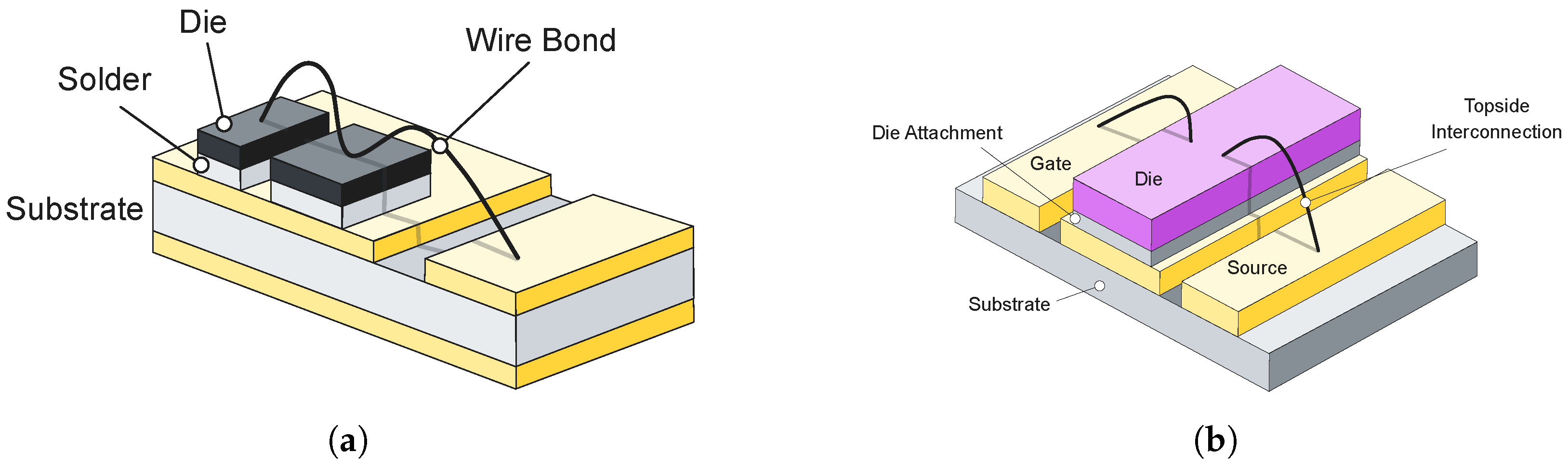

3.2. Advanced Package Architectures

3.2.1. Double-Sided Cooling (DSC)

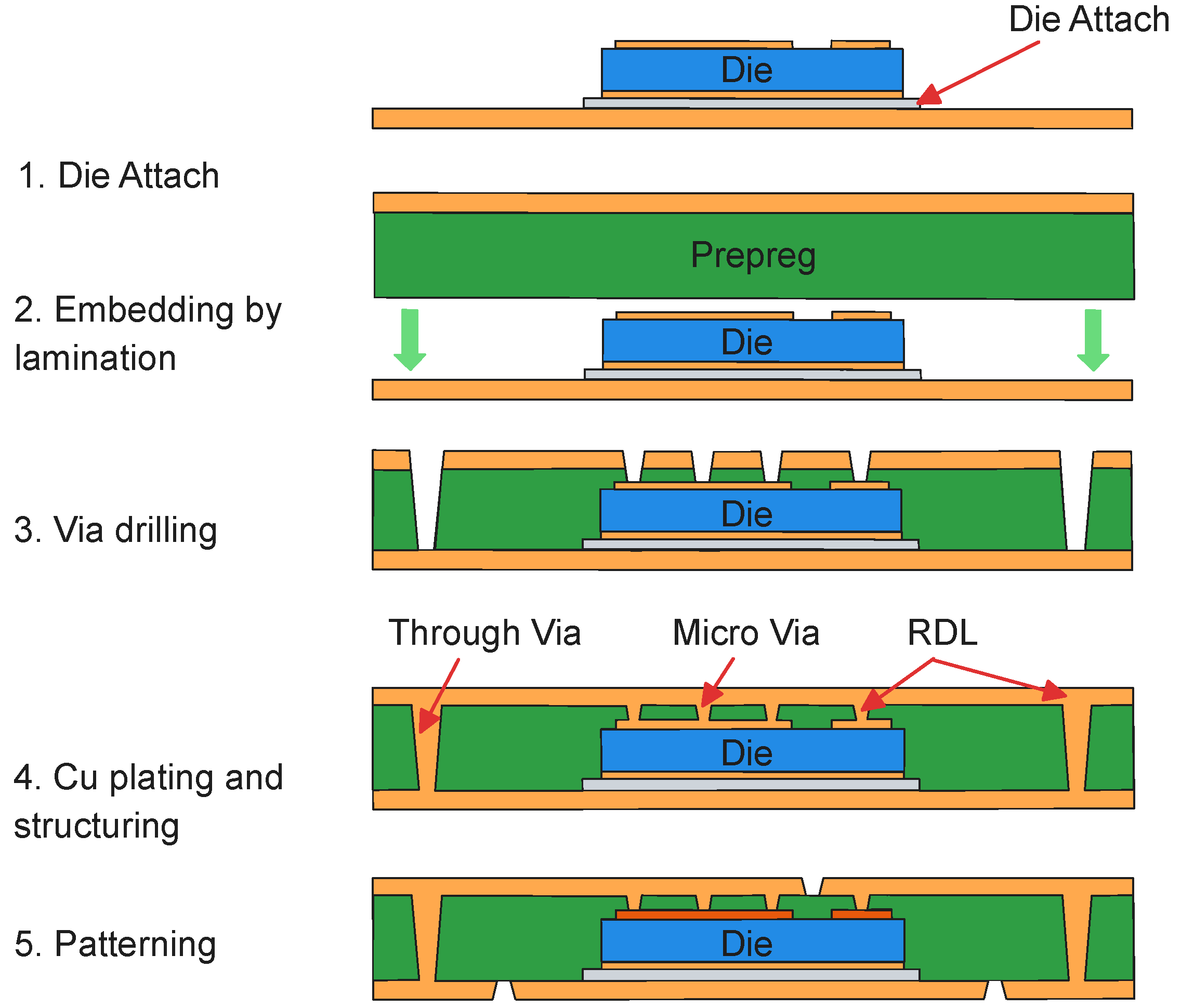

3.2.2. Embedded Packaging

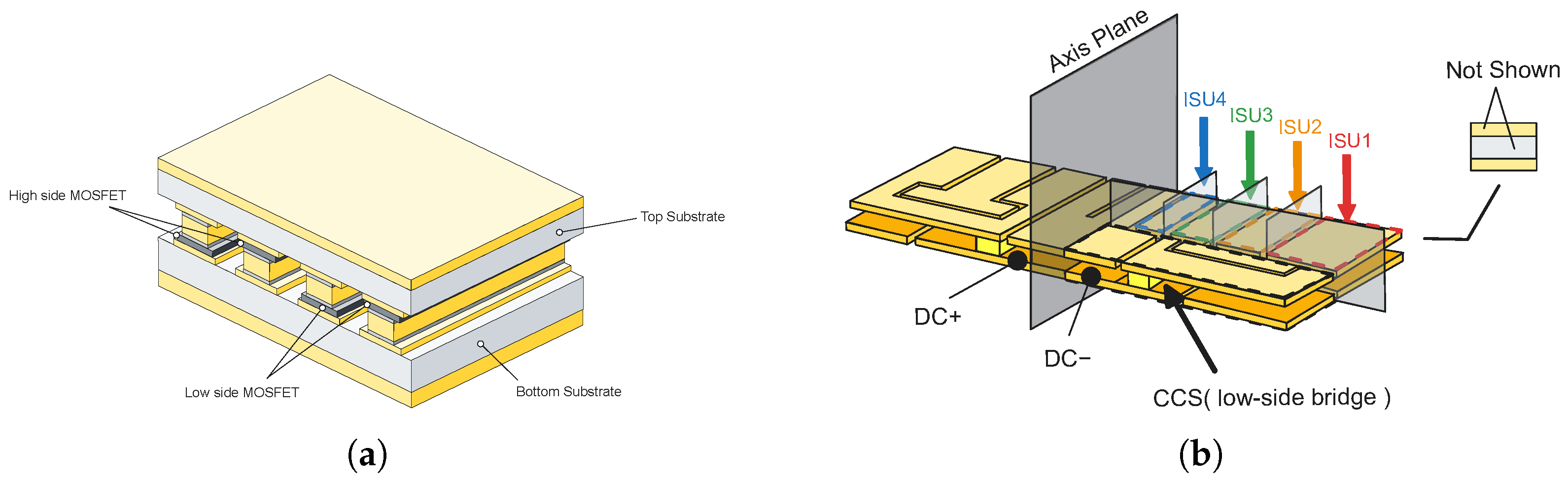

3.2.3. Interleaved Planar Packaging

3.3. System-Level Cooling Techniques

4. Reliability Issues and Thermal Modeling

4.1. Overview of Reliability Issues and Assessment Methodologies

4.2. Health Monitoring and Lifetime Prediction Techniques

4.3. Thermal-Aware Design for Extended Lifetime

5. Technology Integration and Patent Trends

5.1. Co-Design and Integration Strategies

5.2. Patent-Based Analysis of Integration Trends in WBG Power Semiconductors

- Methodology. We queried WIPS ON (accessed on 4 September 2025, KST) for patent families filed in 2010–2025, focusing on Wide-Bandgap (SiC and GaN) power devices with relevance to packaging and thermal integration. To avoid pulling Si-only results, we applied the following Boolean query (English keywords; Korean synonyms were also checked in the same portal): (Listing 1)

| Listing 1. Boolean query used for patent search in WIPS ON database. |

| (SiC OR GaN OR “Wide-Bandgap” OR WBG OR “power semiconductor”) AND (“thermal management” OR cooling OR “heat dissipation” OR “heat sink” OR “thermal interface material” OR TIM OR packaging OR “thermal resistance” OR “thermal conductivity”) |

- Representative Families. SiC—US 8,329,252 B2 [85] exemplifies epitaxial/process innovations that suppress defect formation and improve substrate/epi quality, directly supporting the reliability targets in Section 4.1 and the thermal strategies in Section 3. GaN—US 2011/0297914 A1 [86] describes a wire-bond-free flip-chip stack that shortens the vertical heat path and reduces parasitics. Although originally framed for LEDs, this packaging architecture is platform-neutral and is cited here as an early integration precedent, consistent with Section 2.2 and Section 3.2.

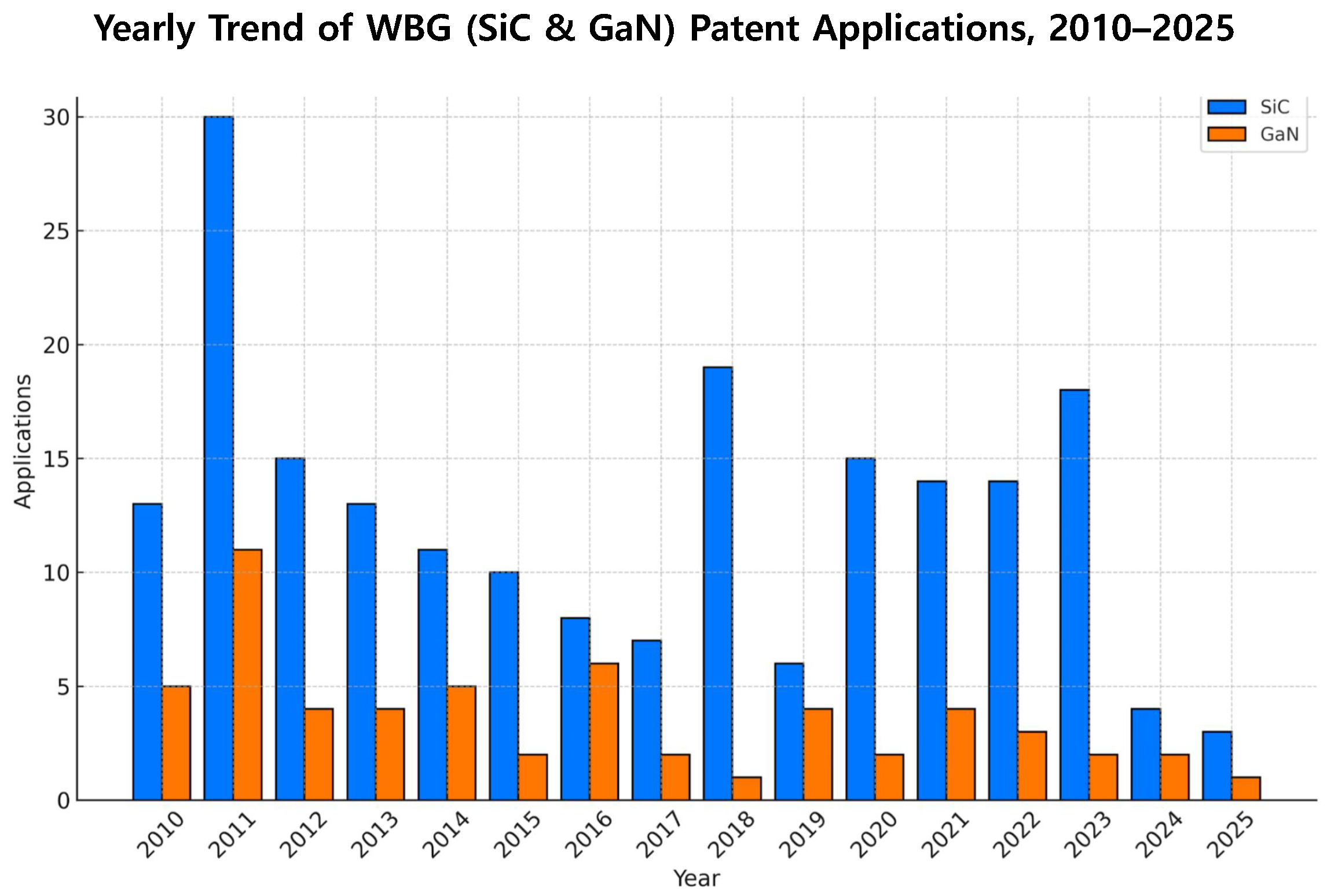

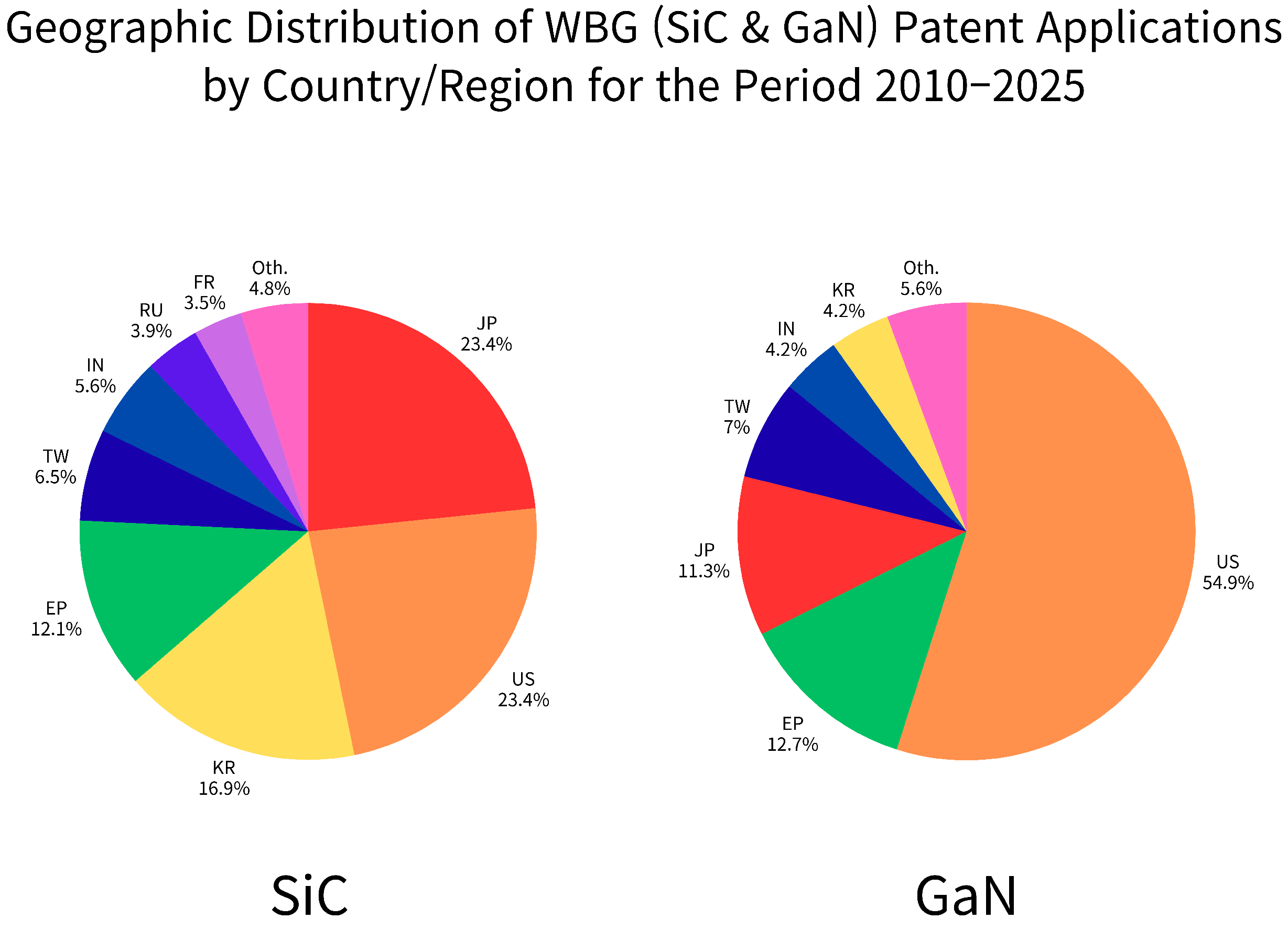

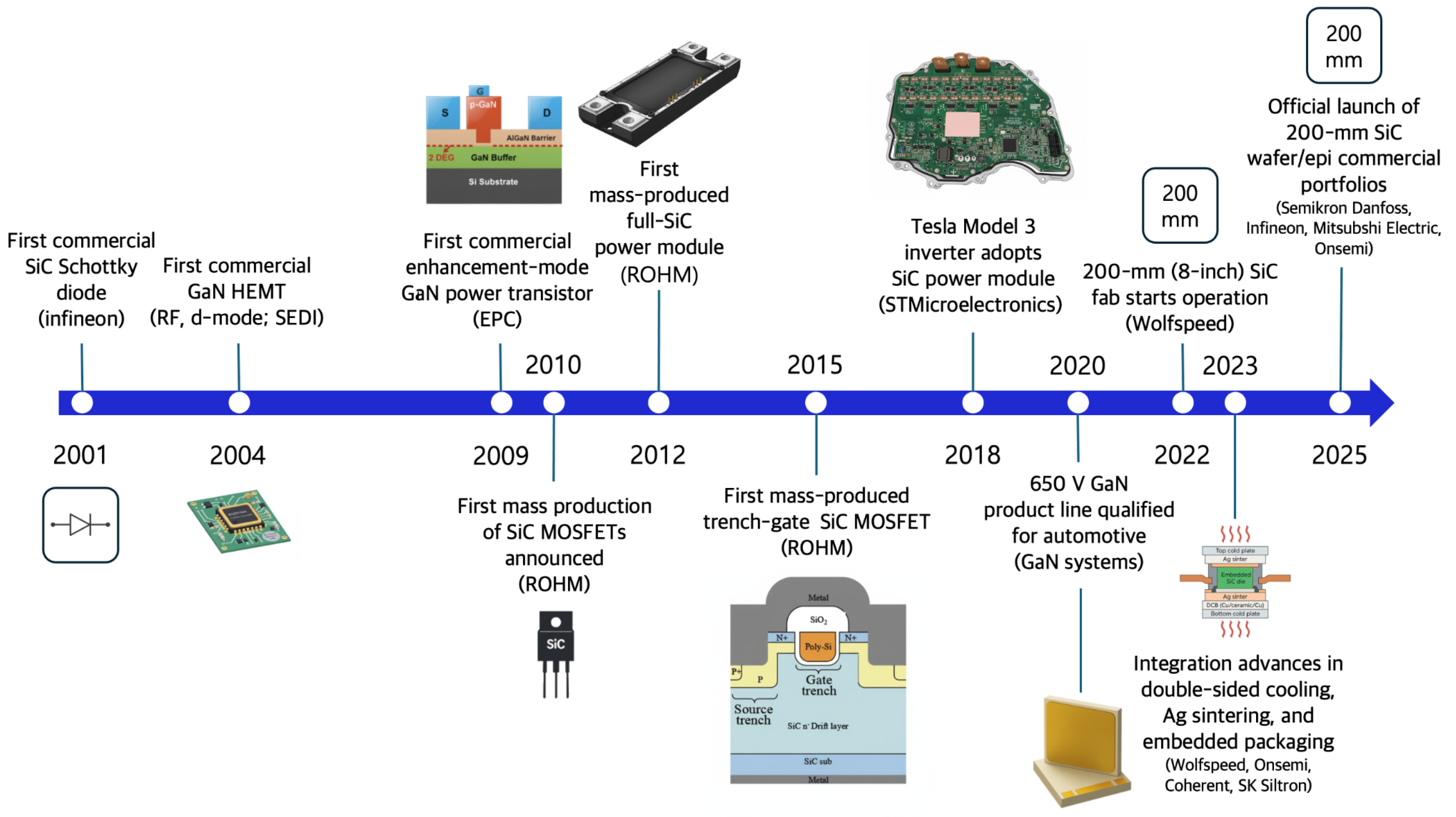

- Trends and Implications. These examples reflect a broader evolution from quantitative expansion to qualitative, integration-centric innovation (Figure 5). Geographically, the United States and Japan lead in SiC, while the U.S. holds a commanding share in GaN (Figure 6). Overall, securing intellectual property (IP) on high-quality substrates, advanced interconnects, and electro-thermal co-design has become decisive for delivering reliable, high-density WBG systems at scale.

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| Abbreviations | |

| 2DEG | Two-Dimensional Electron Gas |

| 3D | Three-Dimensional |

| AEC | Automotive Electronics Council |

| AEC-Q100 | AEC Qualification Standard for Integrated Circuits |

| AEC-Q101 | AEC Qualification Standard for Discrete Semiconductors |

| ALT | Accelerated Life Testing |

| AlN | Aluminum Nitride |

| BPD | Basal Plane Dislocation |

| CAVET | Current-Aperture Vertical Electron Transistor |

| CCS | Current Commutator Structure |

| DBN | Dynamic Bayesian Network |

| DFT | Density Functional Theory |

| DRBD | Dynamic Reliability Block Diagram |

| DSC | Double-Sided Cooling |

| EL | Electroluminescence |

| EM | Electromigration |

| EMI | Electromagnetic Interference |

| FEM | Finite Element Method |

| GaN | Gallium Nitride |

| HEMT | High Electron Mobility Transistor |

| HTC | Heat Transfer Coefficient |

| HTGB | High-Temperature Gate Bias |

| HTRB | High-Temperature Reverse Bias |

| IMC | Intermetallic Compound |

| IP | Intellectual Property |

| ISU | Interleaved Switch Unit |

| JEDEC | Joint Electron Device Engineering Council |

| JESD22 | JEDEC Standard JESD22: Stress-Test Procedures |

| JESD47 | JEDEC Standard JESD47: Reliability Qualification of Integrated Circuits |

| JFET | Junction Field-Effect Transistor |

| LTM | Lumped Thermal Model |

| MMIC | Monolithic Microwave Integrated Circuit |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor |

| PC | Power Cycling |

| PCB | Printed Circuit Board |

| PoF | Physics-of-Failure |

| RC | Resistance–Capacitance (network) |

| RUL | Remaining Useful Life |

| SAB | Surface-Activated Bonding |

| Si | Silicon |

| SiC | Silicon Carbide |

| TC | Thermal Cycling |

| TBC | Thermal Boundary Conductance |

| TBR | Thermal Boundary Resistance |

| TCAF | Thermally Conductive Adhesive Film |

| TDB | Time-Dependent Breakdown |

| TED | Threading Edge Dislocation |

| THB | Temperature–Humidity Bias |

| TLP | Transient Liquid Phase |

| TSEP | Temperature-Sensitive Electrical Parameter |

| WBG | Wide-Bandgap |

| Parameters and Symbols | |

| Output Capacitance | |

| Current Slew Rate | |

| Drain Leakage Current | |

| Gate Current | |

| On-State Resistance | |

| Junction Temperature | |

| Junction Temperature Variation | |

| Drain–Source Voltage | |

| Gate–Source Voltage | |

| Threshold Voltage | |

| On-State Drain–Source Voltage | |

| Thermal Resistance (Compact Network Parameter) | |

| Thermal Capacitance (Compact Network Parameter) | |

| Transient Thermal Impedance | |

| Junction-to-Case Thermal Impedance | |

References

- Millan, J.; Godignon, P.; Perpina, X.; Perez-Tomas, A.; Rebollo, J. A Survey of Wide Bandgap Power Semiconductor Devices. IEEE Trans. Power Electron. 2014, 29, 2155–2163. [Google Scholar] [CrossRef]

- Kimoto, T. Material Science and Device Physics in SiC Technology for High-Voltage Power Devices. Jpn. J. Appl. Phys. 2015, 54, 040103. [Google Scholar] [CrossRef]

- Mishra, U.K.; Parikh, P.; Wu, Y.F. AlGaN/GaN HEMTs—An Overview of Device Operation and Applications. Proc. IEEE 2002, 90, 1022–1031. [Google Scholar] [CrossRef]

- Priyadarshini, S.; Sridutt, L.; Prakash, S.; Gunasekaran, K.; Samikannu, R. Thermal Modelling and Efficiency Analysis of On-Board Charger Using Wide-Gap Semiconductor Devices for EV Application. In Proceedings of the 2024 3rd Odisha International Conference on Electrical Power Engineering, Communication and Computing Technology (ODICON), Bhubaneswar, India, 8–9 November 2024; pp. 1–6. [Google Scholar]

- Buffolo, M.; Favero, D.; Marcuzzi, A.; De Santi, C.; Meneghesso, G.; Zanoni, E.; Meneghini, M. Review and Outlook on GaN and SiC Power Devices: Industrial State-of-the-Art, Applications, and Perspectives. IEEE Trans. Electron Devices 2024, 71, 1344–1355. [Google Scholar] [CrossRef]

- Zheng, Q.; Li, C.; Rai, A.; Leach, J.H.; Broido, D.A.; Cahill, D.G. Thermal Conductivity of GaN, AlN, and SiC from 150 K to 850 K. Phys. Rev. Mater. 2019, 3, 014601. [Google Scholar] [CrossRef]

- Mitterhuber, L.; Kosednar-Legenstein, B.; Vohra, A.; Borga, M.; Posthuma, N.; Kraker, E. Correlation of Heat Transport Mechanism and Structural Properties of GaN High Electron Mobility Transistors. J. Appl. Phys. 2024, 136, 245102. [Google Scholar] [CrossRef]

- Wang, K.; Hu, W.; Wu, S.; Wang, H.; Padhiar, M.A.; Ji, Y. Simulation Investigation of Effects of Substrate and Thermal Boundary Resistance on Performances of AlGaN/GaN HEMTs. Phys. Scr. 2024, 99, 065554. [Google Scholar] [CrossRef]

- Abd El-Azeem, S.M.; El-Ghanam, S.M. Comparative Study of Gallium Nitride and Silicon Carbide MOSFETs as Power Switching Applications under Cryogenic Conditions. Cryogenics 2020, 107, 103071. [Google Scholar] [CrossRef]

- Emon, A.I.; Carlton, H.; Harris, J.; Krone, A.; Mirza, A.; Hassan, M.; Yuan, Z.; Huitink, D.; Luo, F. Design and Optimization of 650 V/60 A Double-Sided Cooled Multichip GaN Module. In Proceedings of the 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), Phoenix, AZ, USA, 14–17 June 2021; pp. 2313–2317. [Google Scholar]

- Agrawal, B. Loss Minimization Using Linear Soft-Switching with Wide Bandgap Devices in Efficient High-Frequency DC-DC Converters. Master’s Thesis, McMaster University, Hamilton, ON, Canada, 2017. [Google Scholar]

- Jafari, A.; Nikoo, M.S.; Perera, N.; Yildirim, H.K.; Karakaya, F.; Soleimanzadeh, R.; Matioli, E. Comparison of Wide-Band-Gap Technologies for Soft-Switching Losses at High Frequencies. IEEE Trans. Power Electron. 2020, 35, 12595–12600. [Google Scholar] [CrossRef]

- Emon, A.I.; Mustafeez-ul-Hassan; Mirza, A.B.; Kaplun, J.; Vala, S.S.; Luo, F. A Review of High-Speed GaN Power Modules: State of the Art, Challenges, and Solutions. IEEE J. Emerg. Sel. Top. Power Electron. 2023, 11, 2707–2729. [Google Scholar] [CrossRef]

- Matioli, E.; Zhu, H.; Perera, N.; Nikoo, M.S.; Jafari, A.; van Erp, R. Switching Losses in Power Devices: From Dynamic on Resistance to Output Capacitance Hysteresis. In Proceedings of the 2023 25th European Conference on Power Electronics and Applications (EPE’23 ECCE Europe), Aalborg, Denmark, 4–8 September 2023; pp. 1–7. [Google Scholar]

- Gill, L.; DasGupta, S.; Neely, J.C.; Kaplar, R.J.; Michaels, A.J. A Review of GaN HEMT Dynamic On-Resistance and Dynamic Stress Effects on Field Distribution. IEEE Trans. Power Electron. 2024, 39, 517–537. [Google Scholar] [CrossRef]

- Ramyar, A.; Lou, Y.; Avestruz, A.T. Accurate Temperature Measurement of Active Area for Wide-Bandgap Power Semiconductors. In Proceedings of the 2023 IEEE 24th Workshop on Control and Modeling for Power Electronics (COMPEL), Ann Arbor, MI, USA, 25–28 June 2023; pp. 1–8. [Google Scholar]

- Gaska, R.; Osinsky, A.; Yang, J.W.; Shur, M.S. Self-Heating in High-Power AlGaN-GaN HFETs. IEEE Electron Device Lett. 1998, 19, 89–91. [Google Scholar] [CrossRef]

- Bhatti, H.I.; Yuvaraja, S.; Wang, C.; Tang, X.; Li, X. Monolithic Integrated Micro-Thin-Film Thermocouples for On-Chip Temperature Measurement of GaN HEMTs. IEEE Trans. Electron Devices 2024, 71, 7734–7739. [Google Scholar] [CrossRef]

- Meneghesso, G.; Verzellesi, G.; Danesin, F.; Rampazzo, F.; Zanon, F.; Tazzoli, A.; Meneghini, M.; Zanoni, E. Reliability of GaN High-Electron-Mobility Transistors: State of the Art and Perspectives. IEEE Trans. Device Mater. Reliab. 2008, 8, 332–343. [Google Scholar] [CrossRef]

- Wang, X.D.; Hu, W.D.; Chen, X.S.; Lu, W. The Study of Self-Heating and Hot-Electron Effects for AlGaN/GaN Double-Channel HEMTs. IEEE Trans. Electron Devices. 2012, 59, 1393–1401. [Google Scholar] [CrossRef]

- Sarua, A.; Ji, H.; Kuball, M.; Uren, M.J.; Martin, T.; Hilton, K.P.; Balmer, R.S. Integrated Micro-Raman/Infrared Thermography Probe for Monitoring of Self-Heating in AlGaN/GaN Transistor Structures. IEEE Trans. Electron Devices 2006, 53, 2438–2447. [Google Scholar] [CrossRef]

- Rahman, M.; Hasan, A.S.M.K.; Mantooth, H.A.; Song, X. High Temperature Characterization and Degradation Test of a Cascode Gallium Nitride Field Effect Transistor. In Proceedings of the 2024 IEEE 11th Workshop on Wide Bandgap Power Devices & Applications (WiPDA), Dayton, OH, USA, 4–6 November 2024; pp. 1–6. [Google Scholar] [CrossRef]

- Wu, L.; Deng, E.; Wang, Y.; Xu, S.; Hua, W.; Yang, S.; Ding, L. A Multi-Currents Method for Junction Temperature Separation of Cascode GaN. IEEE Trans. Power Electron. 2024, 39, 15567–15575. [Google Scholar] [CrossRef]

- Won, Y.; Cho, J.; Agonafer, D.; Asheghi, M.; Goodson, K.E. Cooling Limits for GaN HEMT Technology. In Proceedings of the 2013 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Monterey, CA, USA, 13–16 October 2013; pp. 1–5. [Google Scholar]

- Ain, K.N.; Zhang, G.Q.; Rodrigues, A.; Hasan, M.N.; Holzmann, D.; Geens, K.; Chatterjee, U.; Roshanghias, A. An Introduction to Wire-Bondless Discrete GaN Power Packages with Top-Side Cu Sinterconnects. In Proceedings of the 2024 IEEE 10th Electronics System-Integration Technology Conference (ESTC), Berlin, Germany, 11–13 September 2024; pp. 1–5. [Google Scholar]

- Lee, H.; Smet, V.; Tummala, R. A Review of SiC Power Module Packaging Technologies: Challenges, Advances, and Emerging Issues. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 239–255. [Google Scholar] [CrossRef]

- Wang, L.; Wang, W.; Hueting, R.J.E.; Rietveld, G.; Ferreira, J.A. Review of Topside Interconnections for Wide Bandgap Power Semiconductor Packaging. IEEE Trans. Power Electron. 2023, 38, 472–490. [Google Scholar] [CrossRef]

- Faqir, M.; Manoi, A.; Mrotzek, T.; Knippscheer, S.; Massiot, M.; Buchta, M.; Blanck, H.; Rochette, S.; Vendier, O.; Kuball, M. New GaN Power-Electronics Packaging Solutions: A Thermal Analysis Using Raman Thermography. J. Microelectron. Electron. Packag. 2011, 8, 110–113. [Google Scholar] [CrossRef]

- Lu, D.; Ye, Y.; Liu, R.; Wu, M.; Du, X.; Yu, L.; Qiao, J.; Liu, Z.; Kong, Y.; Jiao, B. Near-Junction Thermal Management of GaN-on-SiC MMIC Power Amplifier Through Substrate Embedded Microchannel. IEEE Trans. Electron Devices 2024, 71, 502–509. [Google Scholar] [CrossRef]

- Hou, F.; Sun, Z.; Su, M.; Fan, J.; You, X.; Li, J.; Wang, Q.; Cao, L.; Zhang, G. Review of Die-Attach Materials for SiC High-Temperature Packaging. IEEE Trans. Power Electron. 2024, 39, 13471–13486. [Google Scholar] [CrossRef]

- Kim, D.; Nagao, S.; Chen, C.; Wakasugi, N.; Yamamoto, Y.; Suetake, A.; Takemasa, T.; Sugahara, T.; Suganuma, K. Online Thermal Resistance and Reliability Characteristic Monitoring of Power Modules with Ag Sinter Joining and Pb, Pb-Free Solders During Power Cycling Test by SiC TEG Chip. IEEE Trans. Power Electron. 2021, 36, 4977–4990. [Google Scholar] [CrossRef]

- Chen, G.; Han, D.; Mei, Y.H.; Cao, X.; Wang, T.; Chen, X.; Lu, G.Q. Transient Thermal Performance of IGBT Power Modules Attached by Low-Temperature Sintered Nanosilver. IEEE Trans. Device Mater. Reliab. 2012, 12, 124–132. [Google Scholar] [CrossRef]

- Bai, J.G.; Yin, J.; Zhang, Z.; Lu, G.Q.; van Wyk, J.D. High-Temperature Operation of SiC Power Devices by Low-Temperature Sintered Silver Die-Attachment. IEEE Trans. Adv. Packag. 2007, 30, 506–510. [Google Scholar] [CrossRef]

- Wang, M.; Mei, Y.H.; Jin, J.; Chen, S.; Li, X.; Lu, G.Q. Pressureless Sintered-Silver Die-Attach at 180 °C for Power Electronics Packaging. IEEE Trans. Power Electron. 2021, 36, 12141–12145. [Google Scholar] [CrossRef]

- Knoerr, M.; Kraft, S.; Schletz, A. Reliability Assessment of Sintered Nano-Silver Die Attachment for Power Semiconductors. In Proceedings of the 2010 12th Electronics Packaging Technology Conference, Singapore, 8–10 December 2010; pp. 56–61. [Google Scholar]

- Saccon, R.; Bhogaraju, S.K.; Elger, G. Cu Sintering for High Power Electronics Packaging—Challenges and Solutions. In Proceedings of the GMM-Fachbericht 105: Mikro-Nano-Integration, Aachen, Germany, 21 November 2022; pp. 26–31. [Google Scholar]

- Liu, X.; Zhou, Q.; Zhao, X.; Koh, S.W.; Ye, H.; Zhang, G. Study and Application of Nano Cu Sintering Technology in Power Electronics Packaging. In Proceedings of the 2021 IEEE 71st Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 1 June–4 July 2021; pp. 1928–1932. [Google Scholar]

- Duch, S.; Gunst, S.; Reh, S. The Attractions, Challenges, and Potential of Copper Sinter Paste for Power Electronics Applications. In Proceedings of the 13th International Conference on Integrated Power Electronics Systems (CIPS 2024), Düsseldorf, Germany, 12–14 March 2024; p. 6. [Google Scholar]

- Mu, F.; Cheng, Z.; Shi, J.; Shin, S.; Xu, B.; Shiomi, J.; Graham, S.; Suga, T. High Thermal Boundary Conductance across Bonded Heterogeneous GaN—SiC Interfaces. ACS Appl. Mater. Interfaces 2019, 11, 33428–33434. [Google Scholar] [CrossRef]

- Yang, F.; Lixin, J.; Wang, L.; Zhang, F.; Wang, B.; Zhao, C.; Wang, J.; Bayer, C.; Ferreira, J. Interleaved Planar Packaging Method of Multichip SiC Power Module for Thermal and Electrical Performance Improvement. IEEE Trans. Power Electron. 2022, 37, 1615–1629. [Google Scholar] [CrossRef]

- Tang, G.; Wai, L.C.; Lim, S.B.; Ye, Y.L.; Lau, B.L.; Yamamoto, K.; Zhang, X. Development of a Novel Lead Frame Based Double Side Liquid Cooling High Performance SiC Power Module. In Proceedings of the 2021 IEEE 71st Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 1 June–4 July 2021; pp. 118–124. [Google Scholar]

- Li, B.; Yang, X.; Wang, K.; Zhu, H.; Wang, L.; Chen, W. A Compact Double-Sided Cooling 650 V/30 A GaN Power Module with Low Parasitic Parameters. IEEE Trans. Power Electron. 2022, 37, 426–439. [Google Scholar] [CrossRef]

- Zhu, M.; Wang, L.; Pei, Y.; Yang, F.; Cheng, Z.; Gao, K. Compact Spatially Symmetric Double-Sided Embedded Packaging Method for Parallel SiC MOSFETs. In Proceedings of the 2024 25th International Conference on Electronic Packaging Technology (ICEPT), Tianjin, China, 7–9 August 2024; pp. 1–4. [Google Scholar]

- Tian, X.; Jia, N.; DeVoto, D.; Paret, P.; Bai, H.; Tolbert, L.M.; Cui, H. PCB-on-DBC GaN Power Module Design with High-Density Integration and Double-Sided Cooling. IEEE Trans. Power Electron. 2024, 39, 507–516. [Google Scholar] [CrossRef]

- Nakamura, K.; Shigematsu, K.; Imaoka, J.; Yamamoto, M. Prototyping and Evaluation of SiC Half Bridge Circuit Using Power Device Embedded Module Process Towards Future Three Dimensional Packaging. In Proceedings of the 2023 IEEE CPMT Symposium Japan (ICSJ), Kyoto, Japan, 15–17 November 2023; pp. 196–199. [Google Scholar]

- Risch, R.; Biela, D.J. PCB-Embedded Packaging for Ultra-Fast Switching of SiC MOSFETs. In Proceedings of the 12th International Conference on Integrated Power Electronics Systems (CIPS 2022), Berlin, Germany, 15–17 March 2022; pp. 269–275. [Google Scholar]

- Wang, J.; Liu, Z.; Peng, H.; Ren, X. A Novel Intelligent Power Module in Embedded Packaging with Low Parasitic Inductance and Low Thermal Resistance. In Proceedings of the 2024 25th International Conference on Electronic Packaging Technology (ICEPT), Tianjin, China, 7–9 August 2024; pp. 1–4. [Google Scholar]

- Tian, X.; Jia, N.; Chertkovsky, D.B.; Sun, J.; Bai, H.; Tolbert, L.M.; Cui, H. An Embedded GaN Power Module with Double-Sided Cooling and High-Density Integration. In Proceedings of the 2022 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 9–13 October 2022; pp. 1–7. [Google Scholar]

- Zhang, C.; Liu, X.; Li, J.; Song, G.; Ye, H. Simulation Study on Thermal Mechanical Properties of Different Embedded Packaging Structures and Materials of GaN Devices. In Proceedings of the 2020 21st International Conference on Electronic Packaging Technology (ICEPT), Guangzhou, China, 1–5 August 2020; pp. 1–5. [Google Scholar]

- McPherson, B.; McGee, B.; Simco, D.; Olejniczak, K.; Passmore, B. Direct Liquid Cooling of High Performance SiC Power Modules. In Proceedings of the 2017 IEEE International Workshop on Integrated Power Packaging (IWIPP), Delft, The Netherlands, 5–7 April 2017. [Google Scholar]

- Morozumi, A.; Hokazono, H.; Nishimura, Y.; Ikeda, Y.; Nabetani, Y.; Takahashi, Y. Direct Liquid Cooling Module with High Reliability Solder Joining Technology for Automotive Applications. In Proceedings of the 2013 25th International Symposium on Power Semiconductor Devices & ICs (ISPSD), Kanazawa, Japan, 26–30 May 2013; pp. 435–438. [Google Scholar]

- Gould, K.; Cai, S.Q.; Neft, C.; Bhunia, A. Liquid Jet Impingement Cooling of a SiC Power Conversion Module for Vehicle Applications. IEEE Trans. Power Electron. 2015, 30, 2975–2984. [Google Scholar] [CrossRef]

- Barua, H.; Chowdhury, S.; Wilkins, J.; Ozpineci, B. Single and Double-Sided Jet Impingement Cooling for SiC-Based Power Modules. In Proceedings of the 2023 IEEE 10th Workshop on Wide Bandgap Power Devices & Applications (WiPDA), Charlotte, NC, USA, 4–6 December 2023; pp. 74–79. [Google Scholar]

- Mouawad, B.; Skuriat, R.; Li, J.; Johnson, C.M.; DiMarino, C. Development of a Highly Integrated 10 kV SiC MOSFET Power Module with a Direct Jet Impingement Cooling System. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 256–259. [Google Scholar]

- Jung, K.W.; Kharangate, C.R.; Lee, H.; Palko, J.; Zhou, F.; Asheghi, M.; Dede, E.M.; Goodson, K.E. Microchannel Cooling Strategies for High Heat Flux (1 kW/cm2) Power Electronic Applications. In Proceedings of the 2017 16th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), Orlando, FL, USA, 30 May–2 June 2017; pp. 98–104. [Google Scholar]

- van Erp, R.; Kampitsis, G.; Nela, L.; Ardebili, R.S.; Matioli, E. Embedded Microchannel Cooling for High Power-Density GaN-on-Si Power Integrated Circuits. In Proceedings of the 2020 19th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), Orlando, FL, USA, 21–23 July 2020; pp. 53–59. [Google Scholar]

- Chen, X.; Donmezer, F.N.; Kumar, S.; Graham, S. A Numerical Study on Comparing the Active and Passive Cooling of AlGaN/GaN HEMTs. IEEE Trans. Electron Devices 2014, 61, 4056–4061. [Google Scholar] [CrossRef]

- van Erp, R.; Kampitsis, G.; Matioli, E. Efficient Microchannel Cooling of Multiple Power Devices with Compact Flow Distribution for High Power-Density Converters. IEEE Trans. Power Electron. 2020, 35, 7235–7245. [Google Scholar] [CrossRef]

- Ni, Z.; Lyu, X.; Yadav, O.P.; Cao, D. Review of SiC MOSFET-Based Three-Phase Inverter Lifetime Prediction. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 1007–1014. [Google Scholar]

- Li, X.; Deng, X.; Liao, Z.; Li, X.; Jia, R.; Zhang, B. Failure Mechanism of 1200-V SiC MOSFET with Embedded Schottky Barrier Diode Under Short-Circuit Condition. IEEE Trans. Electron. Devices 2025, 72, 1259–1263. [Google Scholar] [CrossRef]

- Schrock, J.A.; Ray II, W.B.; Lawson, K.; Bilbao, A.; Bayne, S.B.; Holt, S.L.; Cheng, L.; Palmour, J.W.; Scozzie, C. High-Mobility Stable 1200-V, 150-A 4H-SiC DMOSFET Long-Term Reliability Analysis Under High Current Density Transient Conditions. IEEE Trans. Power Electron. 2015, 30, 2891–2895. [Google Scholar] [CrossRef]

- Yang, X.; Liu, J.; Wang, B.; Zhang, G. Pulsed Overcurrent Capability of Power Semiconductor Devices in Solid-State Circuit Breakers: SiC MOSFET vs. Si IGBT. In Proceedings of the 2022 IEEE Applied Power Electronics Conference and Exposition (APEC), Houston, TX, USA, 20–24 March 2022; pp. 966–973. [Google Scholar]

- Pela, R.R.; Hsiao, C.L.; Hultman, L.; Birch, J.; Gueorguiev, G.K. Electronic and optical properties of core–shell InAlN nanorods: A comparative study via LDA, LDA-1/2, mBJ, HSE06, G0W0 and BSE methods. Phys. Chem. Chem. Phys. 2024, 26, 7504–7514. [Google Scholar] [CrossRef] [PubMed]

- Ni, Z.; Lyu, X.; Yadav, O.P.; Singh, B.N.; Zheng, S.; Cao, D. Overview of Real-Time Lifetime Prediction and Extension for SiC Power Converters. IEEE Trans. Power Electron. 2020, 35, 7765–7794. [Google Scholar] [CrossRef]

- Ma, K.; Liserre, M.; Blaabjerg, F.; Kerekes, T. Thermal Loading and Lifetime Estimation for Power Device Considering Mission Profiles in Wind Power Converter. IEEE Trans. Power Electron. 2015, 30, 590–602. [Google Scholar] [CrossRef]

- McPherson, J.W. Brief history of JEDEC qualification standards for silicon technology and their applicability(?) to WBG semiconductors. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018; pp. 3B.1-1–3B.1-8. [Google Scholar] [CrossRef]

- Tang, Y.; Zhan, C.; Zhu, L.; Wang, W.; Gou, Y.; Ji, S. Efficient Junction Temperature Estimation of SiC Power Modules Based on Temperature-Dependent Lumped Thermal Model. IEEE J. Emerg. Sel. Top. Power Electron. 2025, 13, 2799–2810. [Google Scholar] [CrossRef]

- Xu, Y.; Ho, C.N.M.; Ghosh, A.; Muthumuni, D. Design, Implementation, and Validation of Electro-Thermal Simulation for SiC MOSFETs in Power Electronic Systems. IEEE Trans. Ind. Appl. 2021, 57, 2714–2725. [Google Scholar] [CrossRef]

- Li, J.; Castellazzi, A.; Eleffendi, M.A.; Gurpinar, E.; Johnson, C.M.; Mills, L. A Physical RC Network Model for Electrothermal Analysis of a Multichip SiC Power Module. IEEE Trans. Power Electron. 2018, 33, 2494–2508. [Google Scholar] [CrossRef]

- Zheng, X.; Pomeroy, J.W.; Jindal, G.; Kuball, M. Temperature-Dependent Thermal Impedance Measurement of GaN-Based HEMTs Using Transient Thermoreflectance. IEEE Trans. Electron Devices 2024, 71, 2367–2372. [Google Scholar] [CrossRef]

- Hanif, A.; Yu, Y.; DeVoto, D.; Khan, F. A Comprehensive Review Toward the State-of-the-Art in Failure and Lifetime Predictions of Power Electronic Devices. IEEE Trans. Power Electron. 2019, 34, 4729–4746. [Google Scholar] [CrossRef]

- Lu, X.; Wang, L. A Novel Method for Real-Time Junction Temperature Monitoring of SiC MOSFET Through Sensitivity Amplification of Turn-Off Delay Time. IEEE Trans. Power Electron. 2025, 40, 11326–11338. [Google Scholar] [CrossRef]

- Yu, H.; Jiang, X.; Chen, J.; Wang, J.; Shen, Z.J. A Novel Real-Time Junction Temperature Monitoring Circuit for SiC MOSFET. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 15–19 March 2020; pp. 1297–1301. [Google Scholar]

- Barón, K.M.; Nitzsche, M.; Sharma, K.; Kallfass, I. Characterization of Electrical Parameters for Health Monitoring in SiC MOSFETs during AC Power Cycling. In Proceedings of the 2021 IEEE 8th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Redondo Beach, CA, USA, 7–11 November 2021. [Google Scholar] [CrossRef]

- Sezer, M.M.; Akici, F.; Afshar, M.; Vankayalapati, B.T.; Akin, B. Gate Leakage Current Characterization and Remaining Useful Lifetime Prediction in SiC MOSFETs. IEEE Trans. Transp. Electrif. 2025, 11, 8948–8958. [Google Scholar] [CrossRef]

- Wu, X.; Yang, X.; Ye, J.; Liu, G. Novel Prognostics for IGBTs Using Wire-Bond Contact Degradation Model Considering On-Chip Temperature Distribution. IEEE Trans. Power Electron. 2025, 40, 4411–4424. [Google Scholar] [CrossRef]

- Li, B.; Li, D.; Li, D.; Yang, B.; Gong, B.; Han, S.; Su, B.; Deng, Y.; Yang, D. Vertical Thermal Design and Modeling for Integrated Power Amplifier WBLGA SiP Packaging. In Proceedings of the 2024 25th International Conference on Electronic Packaging Technology (ICEPT), Tianjin, China, 7–9 August 2024; pp. 1–6. [Google Scholar]

- Sueker, K.H. Transient Thermal Impedance Modeling of Semiconductor Heat Sinking. In Proceedings of the Conference Record of the 1993 IEEE Industry Applications Conference Twenty-Eighth IAS Annual Meeting, Toronto, ON, Canada, 2–8 October 1993; pp. 1238–1241. [Google Scholar]

- Islam, M.M.; Rahman, M.A.; Islam, M.R. Power Loss and Thermal Impedance Modeling of Multilevel Power Converter with Discontinuous Modulation. IEEE Trans. Energy Convers. 2021, 36, 36–47. [Google Scholar] [CrossRef]

- Chen, W.; Yan, X.; Ibrahim, M.S.; Meda, A.H.; Fan, X.; Zhang, G.; Fan, J. Thermal-Mechanical-Electrical Co-Design of Fan-Out Panel-Level SiC MOSFET Packaging with a Multi-Objective Optimization Algorithm. In Proceedings of the 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2023; pp. 2007–2011. [Google Scholar]

- Blanchette, H.; Al-Haddad, K. Switching Power MOSFET Performance: A Compromise Between EMI Generation and Thermal Consideration. In Proceedings of the 2006 IEEE International Symposium on Industrial Electronics, Montreal, QC, Canada, 9–13 July 2006; pp. 1293–1298. [Google Scholar]

- Cui, H.; Li, B.; Kong, H.; Yang, F.; Wang, F.; Wang, L.; Gao, K. Understanding the Thermal Characteristics of SiC Power MOSFET Device for Power Modules Design. In Proceedings of the 2023 IEEE 14th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Shanghai, China, 9–12 June 2023; pp. 1088–1095. [Google Scholar]

- Cho, J.; Li, Y.; Altman, D.H.; Hoke, W.E.; Asheghi, M.; Goodson, K.E. Temperature Dependent Thermal Resistances at GaN-Substrate Interfaces in GaN Composite Substrates. In Proceedings of the 2012 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), La Jolla, CA, USA, 14–17 October 2012; pp. 1–4. [Google Scholar]

- Zhu, G.; Zhang, L.; Hou, Z.; Wang, Y.; Liang, L.; Mei, Y. Interconnection-Varied Warpage Modeling of Sintered-Nanosilver-Connected Power Modules with a Heatsink Considering Time Sequence Efforts. In Proceedings of the 2024 25th International Conference on Electronic Packaging Technology (ICEPT), Tianjin, China, 7–9 August 2024; pp. 1–5. [Google Scholar]

- Makarov, Y.; Spencer, M. Method for the Growth of SiC, by Chemical Vapor Deposition, Using Precursors in Modified Cold-Wall Reactor. U.S. Patent 8,329,252 B2, 11 December 2012. [Google Scholar]

- Zheng, J.; Lin, S.; He, A.; Lin, K. GaN-Based Flip-Chip Light-Emitting Diode with Double Reflective Layers on its Side and Fabrication Method Thereof. U.S. Patent 2011/0297914 A1, 8 December 2011. [Google Scholar]

| Technology | Key Performance Improvements | Advantages | Disadvantages/Trade-Offs | Primary Applications |

|---|---|---|---|---|

| Double-Sided Cooling |

|

|

|

|

| Embedded Packaging |

|

|

| |

| Interleaved Planar |

|

|

|

|

| Jet Impingement |

|

|

|

|

| Microchannel |

|

|

|

|

| Direct Liquid |

|

|

|

|

| Indirect Liquid |

|

|

|

|

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Han, G.; Kim, J.; Park, S.; Bae, W. Thermal Management of Wide-Bandgap Power Semiconductors: Strategies and Challenges in SiC and GaN Power Devices. Electronics 2025, 14, 4193. https://doi.org/10.3390/electronics14214193

Han G, Kim J, Park S, Bae W. Thermal Management of Wide-Bandgap Power Semiconductors: Strategies and Challenges in SiC and GaN Power Devices. Electronics. 2025; 14(21):4193. https://doi.org/10.3390/electronics14214193

Chicago/Turabian StyleHan, Gyuyeon, Junseok Kim, Sanghyun Park, and Wongyu Bae. 2025. "Thermal Management of Wide-Bandgap Power Semiconductors: Strategies and Challenges in SiC and GaN Power Devices" Electronics 14, no. 21: 4193. https://doi.org/10.3390/electronics14214193

APA StyleHan, G., Kim, J., Park, S., & Bae, W. (2025). Thermal Management of Wide-Bandgap Power Semiconductors: Strategies and Challenges in SiC and GaN Power Devices. Electronics, 14(21), 4193. https://doi.org/10.3390/electronics14214193