Abstract

In advanced Complementary Metal-Oxide-Semiconductor (CMOS) technologies, where diminished feature sizes amplify radiation-induced soft errors, the optimization of fault-tolerant circuit designs requires detailed transistor-level analysis of reliability–performance trade-offs. As a fundamental building block in digital systems and critical data paths, the 2:1 multiplexer, widely used in data-path routing, clock networks, and reconfigurable systems, provides a critical benchmark for assessing radiation-hardened design methodologies. In this context, this work aims to analyze the power consumption, area overhead, and delay of 2:1 multiplexer designs under transient fault conditions, employing the CMOS and Differential Cascode Voltage Switch Logic (DCVSL) logic styles and mitigation strategies. Electrical simulations were conducted using 32 nm high-performance predictive technology, evaluating both the original circuit versions and modified variants incorporating three mitigation strategies: transistor sizing, D-Cells, and C-Elements. Key metrics, including power consumption, delay, area, and radiation robustness, were analyzed. The C-Element and transistor sizing techniques ensure satisfactory robustness for all the circuits analyzed, with a significant impact on delay, power consumption, and area. Although the D-Cell technique alone provides significant improvements, it is not enough to achieve adequate levels of robustness.

1. Introduction

The continuous advancement of CMOS electronic devices has been made possible through transistor scaling, which has enabled remarkable improvements in computational density [1]. As technology nodes continue scaling down, the reliability of integrated circuits (ICs) in the radiation environment becomes more important [2]. Of particular concern is the necessary reduction in supply voltage that accompanies device scaling. While lower operating voltages successfully address power dissipation requirements, they inadvertently increase the circuit’s vulnerability to radiation-induced effects [3]. This occurs because the reduced voltage levels correspondingly decrease the energy required to maintain logic states, thereby making the circuits more susceptible to corruption caused by particle strikes, resulting in single-event effect (SEE) faults [4].

Single-event effects represent a critical reliability challenge in modern electronic systems, often manifesting as soft errors that can corrupt data or disrupt circuit operation without causing permanent damage. These effects occur when ionizing radiation generates charge carriers that interfere with normal device operation, with common manifestations including single-event upsets (SEUs) or single-event transients (SETs) [5]. Among these phenomena, SETs pose particularly significant threats to combinational logic circuits, as they induce transient variations in current or voltage that can be propagated, leading to errors. The growing vulnerability to SETs in advanced technology nodes primarily stems from the fact that rising clock frequencies and tighter timing constraints create greater opportunities for SET propagation through logic paths.

Single-event transients induced by ionizing radiation pose a critical threat to the reliability of nanoscale integrated circuits, particularly in harsh environments such as space, avionics, and high-altitude applications. While extensive research has focused on SET mitigation in memory elements (e.g., flip-flops and SRAM) [6,7], full adders [8], voters [9], and basic logic gates [10], circuits such as multiplexers (MUXs) remain understudied.

The 2:1 multiplexer serves as a fundamental building block in processors and communication systems, yet its inherent structure makes it particularly vulnerable to radiation effects. This vulnerability arises from the fact that a single-event transient occurring on the select line can corrupt the output, depending on the input logic state, potentially leading to silent data errors or system failures. While prior research has extensively evaluated multiplexer designs for power and delay characteristics, to the best of our knowledge, comprehensive assessments of radiation susceptibility remain limited. Although recent work has begun examining SET vulnerability across different 2:1 MUX topologies, including transmission gates, static CMOSs, pass transistors, and others [11], the literature still lacks systematic studies exploring radiation-tolerant designs that combine logic styles with hardening-by-design techniques.

This paper presents a comprehensive analysis of 2:1 multiplexer designs under single-event transient faults, evaluating the impact on power, delay, and area (PPA) characteristics, alongside susceptibility to radiation-induced faults. Based on the previously evaluation provided in [11], we selected the most promising multiplexer topologies, considering two logic styles, static CMOS and differential cascode voltage-switch logic (DCVSL). These multiplexers are then discussed in terms of three circuit-level mitigation strategies: transistor sizing (TS), Decoupling Cells (D-Cells), and C-Elements (CEs). The main contribution of this work is to quantify the trade-offs between performance metrics and SET robustness, providing guidelines for the design of radiation-hardened multiplexers in critical applications. Furthermore, the comparison with related work highlights the growing need for radiation impact analysis in multiplexer designs, particularly as technology nodes scale down, increasing susceptibility to radiation-induced faults. To the best of our knowledge, this is the first work to systematically apply radiation-hardening techniques—such as transistor sizing, Decoupling Cells, and C-Elements—to 2:1 multiplexers while rigorously analyzing their performance trade-offs. Our findings demonstrate that hardening the output node not only improves radiation resilience but also ensures robustness across internal nodes, offering a balanced solution for reliability-critical applications. By integrating radiation tolerance metrics with traditional PPA evaluation, this work bridges a critical gap in the field, providing designers with a comprehensive discussion for designing and optimizing multiplexers for harsh environments. The methodologies and results presented herein serve as a foundational step for future work in designing fault-tolerant combinational circuits for applications ranging from space electronics to medical devices.

The remainder of this paper is organized as follows: Section 2 provides background on multiplexer design techniques, single-event transient mechanisms in nanoscale technologies, and mitigation approaches, including transistor sizing, Decoupling Cells, and C-Elements. Section 3 describes the simulation methodology, covering SPICE models, SET injection techniques, and power–area–delay extraction. Section 4 presents the results, comparing the performance and SET resilience of each design variant. Section 5 discusses key trade-offs and practical implications for circuit designers. Finally, Section 6 concludes the work and outlines future research directions.

2. Background

The choice of logic style directly influences the characteristics of an integrated circuit, such as power, performance, and area. Considering design for reliable systems, robustness is also a relevant point to be characterized for the logic functions under evaluation to help designers to choose the most appropriated transistor arrangement for the application requirement [12,13]. This work considers the robustness to radiation effects, more specifically the single-event effects on combinational circuits that result into single-event transient faults. In this context, we present an overview about SET faults and also about the circuit-level fault mitigation techniques explored in this work. Among different approaches proposed in the literature, we focus on the impact of C-Elements [14], Decoupling Cells [15], and transistor sizing [16] applied to different logic styles of multiplexers.

2.1. Single-Event Effects

The study of radiation effects on microelectronics began in earnest after the 1962 failure of a U.S. telecommunications satellite during high-altitude nuclear testing [17]. Radiation interacts with integrated circuits through two fundamental mechanisms: (1) direct ionization by the incident particle and (2) indirect ionization through secondary particles generated when primary particles react with material [18].

The ongoing scaling of CMOS technology has increased radiation vulnerability despite performance improvements. Reduced operating voltages and critical charge levels have heightened SEE sensitivity, while higher clock frequencies diminish natural timing masking effects against soft errors. Single-event effects occur when energetic particles strike sensitive regions, generating charge pulses [19]. These are classified as destructive or non-destructive [20]. Destructive SEEs cause permanent damage on the circuits, while non-destructive cause temporary errors. In the case of non-destructive SEEs, there are single-event upsets, which are bit-flips in memory elements, and single-event transients, which are particle collisions in combinational logic. However, the effects caused by these non-destructive failures are considered temporary; i.e., they can be restored by re-performing the operation [2].

A sensitive node is typically a reversed-biased PN junction with a conductive path to the output [21]. As the particle passes through this sensitive node, it liberates electron–hole pairs, losing energy in the process. This generates a transient current, leading to the accumulation of charges at the affected node [22]. The particle’s trajectory is referred to as the particle range, and the energy lost along this path is known as Linear Energy Transfer (LET) [23].

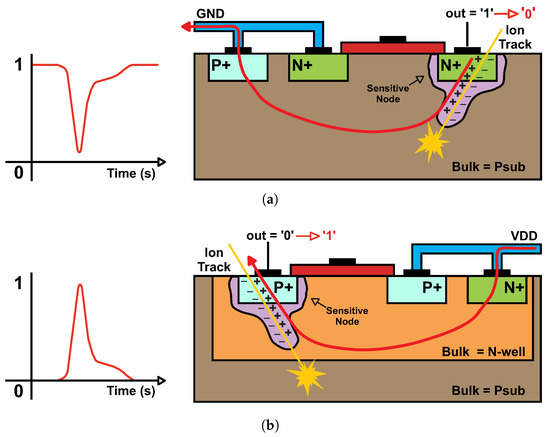

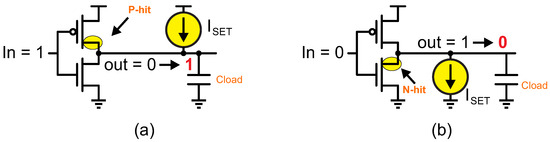

In the context of combinational circuits, such particle interactions can result in a single-event transient (SET) fault. The transient pulse generated by the particle can vary in magnitude and polarity depending on the transistor affected. Figure 1 shows in a simplified way that a particle collision in a circuit can have different magnitudes. If the particle collides an NMOS transistor, the terminal will be discharged to GND, generating a “101” transient pulse, as illustrated in Figure 1a. Conversely, if the particle affects a PMOS transistor, the node will be charged by the charges present in the well, generating a “010” transient current, called a P-hit, as illustrated in Figure 1b.

Figure 1.

Particle collision in a sensitive node generates different pulse patterns depending on the affected region: (a) N-hit effect and (b) P-hit effect.

2.2. Circuit-Level Fault Mitigation Techniques

The growing deployment of electronic systems in radiation-prone environments has significantly increased the demand for effective mitigation techniques against radiation faults. Radiation-hardening strategies vary from fabrication process modifications to circuit-level design implementations, typically named technological hardening or hardening-by-design approaches [24]. While technological hardening involves specialized manufacturing processes, hardening by design offers greater flexibility by implementing radiation tolerance during the circuit design phase. This design-centric approach can be applied across multiple abstraction levels, from individual transistor optimization to complete system architecture, enabling tailored solutions for different radiation environments. However, these hardening techniques invariably introduce trade-offs among area, power consumption, and delay overhead, which must be carefully balanced. At the transistor level, many techniques can be applied [24]; however, this paper focus on three gate hardening strategies, (1) transistor sizing, (2) D-Cell implementation, and (3) C-Element utilization, each offering distinct advantages and compromises in terms of radiation tolerance and circuit performance metrics.

2.2.1. C-Element

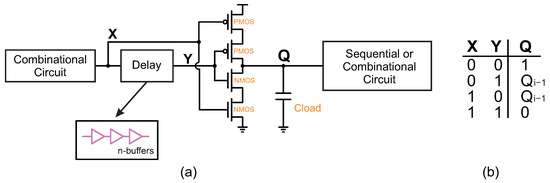

The C-Element strategy is a fault mitigation technique that compares the logic state of its inputs [14]. The idea of temporal filtering is to mitigate SET pulses that are faster than the delay. Thus, when the inputs are identical, the C-Element works as an inverter, changing the logic state of its output. Additionally, when its inputs differ, it retains the logic state, functioning as a memory element. The time it remains in this state is defined by the number of delay buffers. The logic behavior is shown in Figure 2.

Figure 2.

(a) C-Element configuration and (b) truth table.

However, this technique has two vulnerabilities: The first occurs when the C-Element is in the memory state, because if a particle hits the C-Element block, the energy necessary to cause an error is reduced and the SET pulse will propagate. The second is the scaling of the delay, because if the charge collection period at the node is very long, the delay needs to be longer.

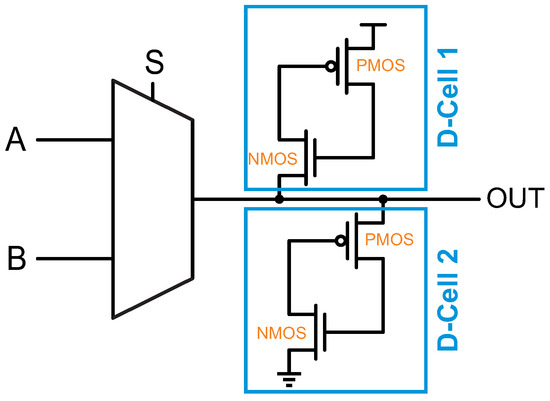

2.2.2. Decoupling Cell

Decoupling Cells, also known as D-Cells, represent a promising approach to mitigate the effects of single-event transients in combinational logic gates. Originally used to filter noise in power supply and signals, these cells consist of transistors connected in cross-coupling mode, which increases the total capacitance at the output node of the logic gate [15]. This increase in capacitance increases the critical charge () required to induce a SET pulse, making the output node less sensitive to the impact of energetic particles. It is recommended to use two Decoupling Cells to ensure protection against P-hit and N-hit effects, connecting one between the output and the power supply and the other between the output and ground, as shown in Figure 3.

Figure 3.

Application of two D-Cells.

2.2.3. Transistor Sizing

Transistor resizing aims to increase the capacitance of the sensitive nodes, increasing the critical charge () needed to induce a SET [16]. However, this can increase the transistor’s drain area, which in turn increases the charge collected () during the particle’s impact. For low-LET particles, symmetrical resizing tends to reduce the transient pulse [25]. However, for higher LETs, the technique may not be effective and may even increase the amplitude and duration of the SET. The effectiveness of resizing is a compromise between the collected load and the critical load of the node. However, increasing the size of the transistors too much presents significant disadvantages in terms of area cost and power.

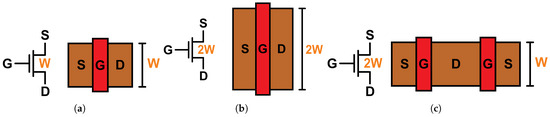

In this context, to manage the large elements in the design layout, it is common to apply the transistor folding technique [16,26]. Transistor folding divides a large transistor into multiple parallel segments in the layout, as shown in Figure 4. This makes it possible to reduce the area of the transistor drain affected by radiation without decreasing the node’s total capacitance or current capacity (since the transistors are added in parallel). This approach proves effective in reducing SETs induced by low- and high-energy particles [16]. Figure 4 shows the difference between these techniques at the circuit level and at the layout level.

Figure 4.

Transistor sizing. (a) NMOS Minimal, (b) NMOS with X2, and (c) NMOS X2 with folding layout technique.

2.3. Related Work

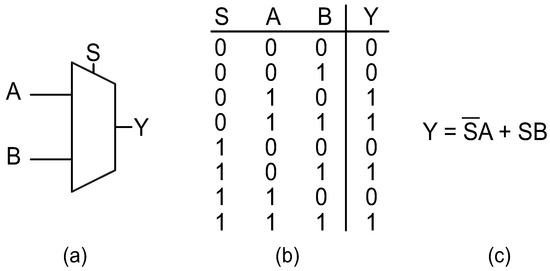

Multiplexers, also called MUXs, are essential components in digital electronics, particularly in communication systems and microprocessors, acting as data selectors that route multiple input signals to a single output line [27]. Their importance lies in their ability to increase data transmission efficiency, optimize memory space usage in computers, and convert data from parallel to serial formats in data communication. Multiplexers of the 2:1 type function as data selection switches, choosing between two input lines (A or B) based on the state of a selection line (S) and directing the selected signal to the output (Y). Figure 5 presents the logic gate block, truth table, and the logic function of a 2:1 multiplexer.

Figure 5.

(a) Multiplexer logic gate block, (b) MUX 2:1 truth table, and (c) MUX logic function.

The literature features numerous works exploring different multiplexer designs while analyzing aspects such as power, performance, and area cost [11,27,28,29,30]. Since the 1990s, studies focused on multiplexer analysis have been produced in the literature, such as the work by [28], which presents an analysis of different logic styles examining power, area, and performance aspects for combinational circuits and full adders, using a 600 nm technology node.

In the 2000s, the topic was revisited, with the work in [27] presenting a power analysis for three different technology nodes: 45 nm, 32 nm, and 16 nm. The work in [31] presents an analysis of 2:1 multiplexers in various logic styles, using 180 nm technology. Currently, new demands for ultra-low-power circuits are emerging, and the work in [30] introduces new multiplexer proposals for (28 nm) technology nodes. Studies discussing radiation effects robustness analysis remain limited. More recently, the work in [11] addresses the most common logic styles in low-power and high-performance circuits, analyzing them only from a robustness perspective.

In this context, the main contribution of this work is to perform an analysis that encompasses the main metrics discussed in the literature—power consumption, performance, and area cost—and provide a robustness analysis against transient faults, employing circuit-level fault tolerance techniques. Several works use fault mitigation techniques to increase the robustness of combinational circuits and review the main techniques used [20,24,32,33,34,35].

Table 1 provides a comparative synthesis of the key characteristics addressed in the literature and the contributions proposed by this work. The evaluated aspects include the targeted technology node, the impact on power–performance–area parameters, a radiation-hardened design analysis, extracted LET threshold (LETth) values, and an assessment of different design approaches. The table reveals that while some related works evaluate 2:1 multiplexers, most focus primarily on PPA analysis without considering radiation effects. This comprehensive analysis addresses a research gap in the existing literature concerning 2:1 multiplexers’ robustness. Many works have been dedicated to optimizing these fundamental building blocks for traditional power, performance, and area metrics. However, the concurrent evaluation of radiation-induced transient faults has remained limited. Our work advances this field by integrating radiation-hardening techniques into the design flow and quantifying their impact on PPA parameters. This approach yields a more holistic understanding of the design trade-offs required for reliability-critical applications. By employing circuit-level fault tolerance methods such as transistor sizing, Decoupling Cells, and C-Elements, we demonstrate that a balanced PPA solution can be achieved without compromising robustness. The findings indicate that hardening the output node is a particularly effective strategy, as it not only improves radiation resilience at the final stage but also offers an inherent level of robustness across internal circuit nodes. This integration of radiation tolerance metrics with traditional PPA evaluation provides a robust and comprehensive panorama for circuit designers, enabling the optimization of multiplexers for operation in harsh environments where transient faults are a significant concern.

Table 1.

Comparative synthesis of the characteristics evaluated in this work and in the literature.

3. Methodology

This work systematically evaluates the robustness of 2:1 multiplexer designs against single-event transient faults while analyzing trade-offs between radiation-hardening effectiveness and power–performance–area characteristics. In order to analyze the robustness of each circuit, electrical simulations were carried out using the NGSPICE simulator, version 44 [36]. The simulation methodology is presented in the next paragraphs.

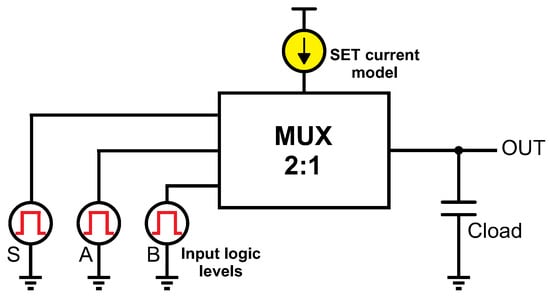

The experiments use the 32 nm high-performance predictive model from [37], with a nominal voltage of 0.9 V and minimal transistor sizing (i.e., L = 32 nm, Wn_ = 70 nm, and Wp_ = 105 nm), and a Cload capacitor of 1 is connected to the output node. In addition to minimum sizing, the logic effort rule is applied. The simulated scenario used is demonstrated in Figure 6. These characteristics are used to simulate and define the typical behavior of each circuit.

Figure 6.

Electrical simulation scenario.

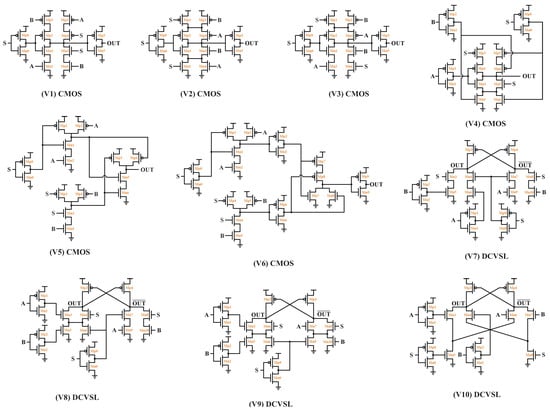

The first step involves selecting the best design candidates. For this, we rely on a prior evaluation of various multiplexer designs [11], where the top ten designs were chosen based on radiation robustness. Figure 7 illustrates the ten analyzed designs, all featuring data inputs A and B and a selector switch S. A detailed analysis of the different 2:1 multiplexer designs reveals poor distinctions in their implementations.

Figure 7.

Designs of 2:1 multiplexers.

Circuits V1 to V4 are developed in single-stage CMOS, while circuits V5 and V6 are developed in multi-stage. All these circuits are designed in the static CMOS logic style. Circuit V1 has no parallel loop in any plane. V2 has parallel loops in both planes, and V3 has them only in the upper plane. V4 represents the equivalent circuit of the multiplexer equation when the Morgan’s equation is applied, resulting in the inverter being removed from the output and added to all inputs. MUX V5 is developed using NAND logic gates, and V6 uses both NAND and NOR logic gates.

The designs of V7 to V10 are developed in the DCVSL logic style. For designs V7 to V10, the differences lie in the NMOS transistor network. Design V7 has no parallel loops, V8 only in the left network, and V9 in both, and V10 has cross-coupling between the planes.

The second step of this work is to define a Linear Energy Transfer threshold (LETth) value within which the designs should be able to tolerate a SET. The value of 5 MeV was chosen considering the intensity of some of the most common radiation-causing elements reported in the literature [34]. It is important to note that this work consists exclusively of electrical simulations, without encompassing physical experimentation. We consider that different particle interactions may result in an energy deposition of approximately 5 MeV within the circuit and opted to adopt a moderate but significant intensity in the evaluation. Based on this representative energy value, we perform electrical simulations following established methodologies in the literature that employ TCAD tools to model radiation effects and evaluate circuit response [21,38,39]. By abstracting the analysis to a generic scenario in which any particle may cause this energy deposition, we define our protection parameters without the need to detail every possible particle type and interaction mechanism. This methodological choice effectively avoids the complexity and high computational cost associated with extensive simulations, such as Monte Carlo analyses, while maintaining a focus on the circuit’s electrical response under representative radiation conditions. This value is configurable and can be changed without modifying the methodological sequence of this work.

The third step is to evaluate the radiation robustness of each design, as the traditional form, i.e., without mitigation technique, and as radiation-hardened forms by applying three transient fault mitigation techniques, C-Elements, D-Cells, and transistor sizing, observing the impact of each on power consumption, delay, and area cost parameters. After evaluating the typical behavior and identifying that no design reached the desired LET threshold (i.e., 5 MeV), the three mitigation techniques were implemented separately.

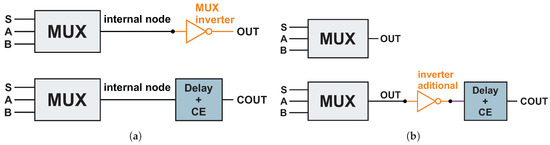

The first technique implemented is the C-Element technique, whose transistors and buffers are dimensioned with the same specifications as the 2:1 multiplexers. The implementation in the designs illustrated in Figure 7 requires specific adaptations due to its inverting characteristic. When the original circuit has an inverter connected to the output, it must be removed to allow the correct connection of the delay block and the comparator; otherwise, if there is no inverter in the initial configuration, it is necessary to insert a new inverter stage before the delay. These modifications, represented schematically in Figure 8, ensure the proper integration of the C-Element into the system, preserving the operating logic and timing conditions of the design.

Figure 8.

Circuit modifications made in order to implement the C-Element. (a) The MUX has an inverter on the output, and (b) the MUX does not have an inverter on the output.

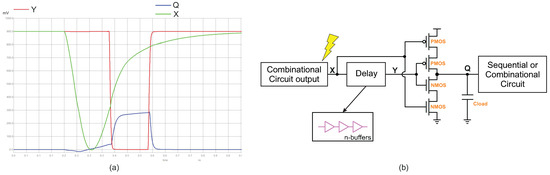

To determine the minimum number of buffers required to completely mitigate a SET fault, pairs of buffers are added sequentially, starting with one pair, until the charge collection period is shorter than the delay time [40]. Figure 9 presents the fault masking process graphed by the C-Element. In X, a fault is injected at the output of the combinational circuit; Y indicates the output of the delay block, and Q shows the output of the C-Element, representing the result after mitigation. It is noteworthy that even when the particle-induced disturbance reaches its maximum amplitude (0 V in this example), the C-Element output exhibits only a minimal perturbation. This demonstrates the effectiveness of the mitigation technique in suppressing transient faults at the circuit output.

Figure 9.

(a) Graph of C-Element steps and (b) C-Element points highlighted on the graph.

Figure 9 illustrates the importance of properly dimensioning the delay block. The delay introduced by it ensures that only a minimum amount of energy is propagated to the comparator input. This energy is insufficient to sustain the error condition at the comparator output. In the context of this study, the delay was obtained by configuring 16 buffers.

The second technique implemented is the D-Cell. In this work, two D-Cells are implemented in the output node, as shown in Figure 3. Since the main idea of this technique is to be capacitive [15], the size of the PMOS and NMOS transistors is set to 800 nm; that is, each D-Cell has a total size of 1600 nm.

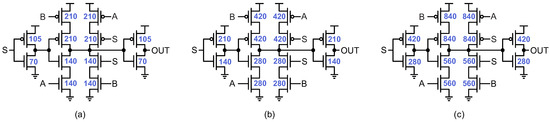

The last technique employed is transistor sizing. This work begins with minimum-sized transistors, optimized using logic effort. Subsequently, each transistor’s dimensions are scaled up by a factor of two while maintaining proportional relationships, as detailed in Figure 10.

Figure 10.

Transistor sizing in MUX. (a) Traditional sizing, (b) X2, and (c) X4.

To simulate the electrical effect of the SET fault, the macro-modeling method is used [41], which consists of inserting an independent current source of opposite magnitude to the state of the sensitive node [4], as shown in Figure 11 and mathematically modeled as described in Equation (1). A fault is considered when the pulse maximum exceeds 50% of , i.e., 0.45 V, at the circuit output. The pulse is modeled according to Equation (1). The is defined to s and is defined to s [42]. These values represent the time constants for charge collection and the time constant for the initial establishment of the ion track, respectively.

Figure 11.

Electrical simulation of SET fault. (a) P-hit effect and (b) N-hit effect.

From the current value obtained from the simulation, it is possible to calculate the value of the collected charge () using Equation (2). As this work considers the minimum current value necessary to cause a fault, the collected charge is equivalent to the critical charge. To calculate the value of , Equation (3) is used. The parameter L refers to the depth of the charge collection channel and has a value of 1 m. The constant 10.8 fC corresponds to the charge deposited by the particle for each 1 m [43].

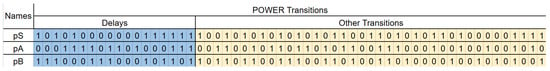

To perform the power consumption simulations, a specific test pattern was developed for each input, as illustrated in Figure 12. The sources “pa”, “pb”, and “ps” correspond to the waveforms applied to inputs A, B, and S, respectively. The pattern includes all 57 possible transitions, with the first 18 designed to represent the delays associated with each input individually, while the others correspond to the other transition combinations. After defining the test pattern, the power consumption was measured by the simulator using Equation (4).

Figure 12.

Input test pattern to calculate maximum power consumption.

4. Results

This section presents the results of the impact of each technique on robustness. These results are presented in graphs organized by input vector and tables, summarizing the information of critical LETth, mean, and standard deviation, in addition to an overview of which techniques achieved the objective. The results for the nominal operation, without any mitigation technique applied, are labeled MUX. These results for nominal operation provide a relative comparison baseline for the impact of the mitigation approaches. Finally, the drawbacks of the mitigation techniques on the electrical characteristics of power consumption and delay are discussed for each 2:1 multiplexer design illustrated in Figure 7.

4.1. LET Impact

The evaluation of the mitigation techniques’ impact on the LET threshold reveals several critical findings. Notably, the C-Element technique demonstrated complete radiation robustness, proving to be fully effective against single-event transients in the multiplexer design. It is important to clarify that the C-Element technique was omitted from the LETth tables because its mitigation strategy relies on introducing a delay to filter out transient faults. This approach was specifically dimensioned to mitigate faults of up to 5 MeV, consistently ensuring 100% robustness across all designs where it was applied.

The electrical simulation results are organized in Table 2. The first column indicates the multiplexer design, the second is the fault mitigation technique (MT) used, and the third is divided into the eight input vectors, with their respective LETth values. The last column is the percentage of vectors that presented a LETth value higher than our 5 MeV threshold. To calculate the percentage, the total number of vectors that reached 5 MeV is considered and divided by the total number of vectors, which, in the case of the 2:1 MUX, is eight. Values that meet the 5 MeV target in Table 2 are highlighted in green. It is important to note that designs V1, V2, V3, and V6 exhibit identical radiation response characteristics due to the presence of an inverter connected to the output of each circuit. As a result of their equivalent behavior under radiation, these designs were grouped into a single row in the table to simplify visualization and comparison.

Table 2.

LETth analysis in each mitigation technique (values in MeV). The average values that reach 5 MeV are highlighted in green.

The results demonstrate that the mitigation techniques consistently improve LETth values across all designs. The most significant enhancements come from transistor sizing approaches, as the X2 and X4 variants. While the standalone D-Cell technique provides modest improvements, with a LETth increase of approximately 10%, its combination with transistor sizing yields substantially better coverage, particularly in designs V4 and V8, which show the most pronounced benefits. When analyzing the input vectors in Table 2, it is clear that for input vectors 010, 011, 101, and 111, no mitigation technique was able to make a circuit robust to 5 MeV; that is, since these input vectors lead to an output logic “1”, these circuits are more sensitive to N-hit faults.

The techniques that stood out were X4 and X4 + DC, as they achieved the target in almost all designs. Design V4 was the only CMOS design that presented a LETth greater than 7 MeV in both mitigation techniques. In the circuits developed in DCVSL (V7 to V10), all designs achieved the target for four input vector combinations: 000, 001, 100, and 110. Circuits V8 and V9 stand out, as they presented a LETth greater than 7 MeV in two vectors, considering the X4 and X4 + DC mitigation techniques.

After organization, the lowest LETth value was identified, called critical LETth, and the arithmetic mean, standard deviation, and percentage of difference between the critical LETth and the circuit mean, called % Diff in Table 3, were calculated. The average values that reach 5 MeV are highlighted in green.

Table 3.

LET statistics for each mitigation technique.The average values that reach 5 MeV are highlighted in green.

To complement the presented data in Table 2, the statistics in Table 3 confirm that the mitigation techniques as effective as the C-Element are X4 and X4 + DC. This conclusion is drawn not only from an analysis of their average values but also from the critical LETth values of these techniques, which closely approach the objective.

The output inverter designs (V1, V2, V3, and V6) demonstrated consistent performance. This performance was accompanied by low standard deviation and percentage difference between the critical value and the overall average. When analyzing the X4 technique alone, a difference of only 4.69% was observed between the critical LETth and the average, a particularly positive result, since this configuration achieved the target in 50% of the input vectors.

In contrast, the designs implemented in DCVSL (V8 and V9), although exceeding the established threshold, presented a significant discrepancy between the critical LETth and the overall circuit average, over 20%, as evidenced by the high standard deviation values.

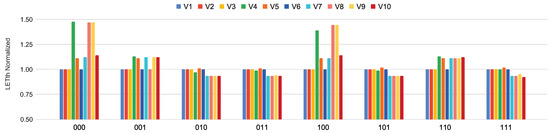

Figure 13 presents the normalization ratio in the traditional scenario for the LETth of each input vector. The LETth values are normalized relative to those of the designs with an inverter at the output (V1, V2, V3, and V6), as these designs exhibited the lowest standard deviation. The normalization was performed by dividing the LETth value of each design operating under normal conditions by the corresponding LETth value from design V1, V2, V3, or V6 with the same mitigation technique and input vector. For example, as shown in Table 2, the LETth value for the MUX configuration in V4, input vector 000, is 1.79 MeV, while for V1–V3 and V6, it is 1.11 MeV, resulting in a normalization ratio of 1.48. This approach highlights the relative robustness among designs, allowing for the identification and analysis of critical behavior in specific input vectors under standard operation. It is important to highlight that this pattern of robustness observed under the standard condition persists even when mitigation techniques are applied.

Figure 13.

Normalized LETth in each input vector.

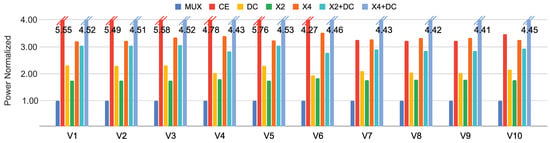

4.2. Power Consumption Impact

The energy consumption data for each project in each scenario are presented in Table 4. The “MUX” column represents the traditional consumption of the respective project without the application of techniques, while the others present the results for each mitigation approach individually. In Figure 14 the power consumption results normalized by the traditional power consumption are presented. A value of 1.00 indicates that the technique has the same consumption as the traditional configuration, and higher values indicate a proportional increase in consumption. It compares the impact of each technique relative to the traditional behavior of each multiplexer design in Figure 7.

Table 4.

Power consumption for nominal (MUX) circuits and with the evaluated mitigation approaches.

Figure 14.

Normalized power consumption by traditional behavior (MUX design).

As demonstrated in Table 4, the technique that least influenced power consumption for all designs is X2 sizing, followed by D-Cells, especially in designs V4 and V6. These results are confirmed by the graph in Figure 14. In contrast, the combined X4 + DC technique had a more significant impact on power consumption in all designs, especially those developed in CMOS, presenting an increase approximately 4.5x greater than traditional consumption, as shown in Figure 14. The C-Element also had a significant impact, but only the CMOS logic style was more affected, reaching 5.76x greater power consumption in design V5.

The designs projected in DCVSL (V7 to V10) presented high consumption in their traditional configurations and were also strongly impacted by the X4 + DC technique, with values close to 450 in designs V8 and V9. Design V7 presented similar consumption between the C-Element and X4 sizing techniques. Designs V8 and V9 presented virtually identical behavior across all techniques. Finally, design V10 was the only DCVSL design in which consumption with the C-Element technique was higher than that with X4.

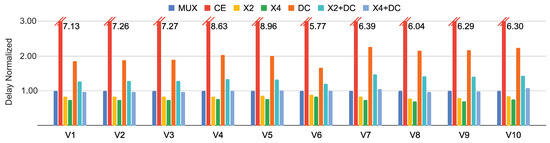

4.3. Delay Impact

Table 5 presents the average propagation delay values for each design for all fault mitigation techniques. Figure 15 presents a comparative bar chart illustrating the average propagation delay for each circuit under different techniques, normalized to the propagation delays of each traditional multiplexer design. The first column corresponds to the baseline implementation without any mitigation, serving as a reference point. The subsequent columns display the delay introduced by each individual hardening technique.

Table 5.

Delay results for each design.

Figure 15.

Normalized delay impact on each radiation-hardening technique.

The C-Element is the technique that most negatively impacts performance, due to the intrinsic need for a delay block in its structure. However, its impact is even greater in static CMOS circuits, especially in designs V4 and V5, where the impact was over 850%. In contrast, design V6 suffered the least in terms of its traditional performance of all the circuits. One reason for design V6’s behavior is that it is a multi-stage multiplexer and has an inverter at the output. In other words, it gains performance by removing the inverter, and the delays relative to each input are less affected.

The techniques that use only transistor scaling, X2 and X4, were the most beneficial, improving the performance of all the multiplexers. This is an expected result considering their structure. The D-Cells had a significant impact on all the projects, especially those developed in DCVSL, increasing the propagation delay by more than 220%. Furthermore, it is relevant to note that the X4 + DC technique, combining techniques with complementary characteristics, had practically zero impact on performance.

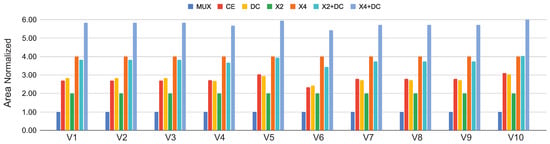

4.4. Area Impact

Table 6 presents the estimated area values for each design and mitigation technique. Figure 16 complements this information by providing a bar chart normalized by the initial area of each design, highlighting the area impact of each mitigation technique. As described in the methodology, the area values are estimates, obtained by summing the W parameters of the transistors present in each design. It is possible to observe that the C-Element and D-Cell presented a very similar area cost; that is, the area cost of the buffers was practically equivalent to the area cost of adding the D-Cell transistors. The technique that had the least impact on the circuits was X2 sizing, only doubling the cost, as expected. The X4 and X4 + DC transistor sizing techniques had the greatest impact on the area of all the circuits; increasing the size of all the transistors combined with a capacitive technique will have a very high area cost.

Table 6.

Area impact for nominal (MUX) circuits and with the evaluated mitigation approaches.

Figure 16.

Normalized area impact on each radiation technique.

Design V6, despite being the largest because it had the most transistors, was the one with the smallest impact in terms of area. In contrast, design V10 had the smallest area and was the one most impacted by the X4 + DC technique.

In contrast, the X2 sizing technique had the smallest impact on area for all designs. However, when this approach was combined with the DC technique, X2 + DC, it was observed that it presented an area cost comparable to X4 sizing alone. This correspondence is particularly evident in design V10, where both techniques showed almost identical values of area.

The insertion of the C-Element had a fixed cost in area, as the same number of buffers and the same comparator block were used, varying only with the insertion or removal of an inverter. The circuits developed in DCVSL presented a similar area impact for the C-Element and D-Cell techniques compared with the static CMOS circuits.

5. Overall Trade-Off Discussion

The tolerance of certain design features depends on the objectives of each application. This section discusses the optimal combination of designs and fault mitigation strategies, considering scenarios in which power, delay, and area can be tolerated. The comprehensive evaluation of these fault mitigation techniques for 2:1 multiplexers reveals a complex design challenge to observe the trade-offs among radiation robustness, power consumption, propagation delay, and area overhead. The selection of a design strategy is inherently a trade-off, dictated by the specific requirements of the target application.

The C-Element technique demonstrates the highest level of radiation robustness across all evaluated designs. This resilience to the adopted intensity of simulated transient faults (5 MeV) comes at a significant cost. Its implementation degrades the propagation delay by over 850% and power consumption by up to 5.76 times compared with the nominal circuits. Area overhead is also notable, though less critical than the performance and power penalties. Therefore, the C-Element is ideally suited for ultra-critical applications where uninterrupted operation in harsh radiation environments is paramount and the system architecture can inherently tolerate considerable power and performance degradation. Examples include deep-space exploration systems or life-support critical medical devices, where reliability supersedes all other metrics.

Conversely, the standalone Decoupling Cell (D-Cell) technique offers only marginal improvements in LETth, approximately 10%. While it exhibits a low impact on propagation delay, its limited effectiveness in fault mitigation makes it an unsuitable primary hardening solution for radiation-sensitive applications.

Transistor sizing presents a more nuanced set of trade-offs. The X2 sizing variant provides beneficial effects on performance, making circuits faster, and has the least impact on power consumption and area among the evaluated techniques. However, its robustness enhancement is insufficient to meet the 5 MeV threshold, rendering it inadequate for applications demanding high radiation tolerance. This approach might be considered for performance-driven application where only a minor, non-critical improvement in inherent robustness is enough.

The X4 sizing technique offers a more substantial increase in LETth, achieving the 5 MeV target for a significant portion of input vectors in several designs. While it also contributes to improved propagation delay, this enhancement is accompanied by an increase in both power consumption and area overhead. This technique is a viable option for applications requiring a moderate level of radiation hardening with a focus on performance, provided that the power and area budgets are flexible enough to accommodate the increased resource utilization.

The combined mitigation strategies reveal compelling solutions. The X2 + DC combination, despite integrating two techniques, fails to achieve the robustness target. Furthermore, it introduces significant penalties, nearly doubling the power consumption of the X2-only approach and increasing the area while also making circuits slower. Consequently, this combination is generally not recommended due to its unfavorable trade-off balance.

In contrast, the X4 + DC technique emerges as the most balanced and effective solution for a wide range of radiation-sensitive applications. This combination consistently achieves the LETth target across designs. The synergistic interaction between X4 sizing and the D-Cell ensures that high performance can be maintained alongside robust radiation tolerance. The primary trade-offs for X4 + DC are its increased power consumption and area. Therefore, this approach is recommended for high-performance, radiation-hardened applications where a strong emphasis is placed on maintaining speed and functionality in harsh environments and the system can accommodate the increased power and area footprints. Examples include high-speed data processing units in aerospace systems or critical control logic in nuclear facilities.

6. Conclusions

This article presents a discussion about approaches to increasing the robustness of the 2:1 multiplexer designs up to a threshold of 5 MeV. During the analysis, we consider the application of three faults mitigation techniques at the circuit level, C-Element, D-Cell, and transistor sizing, observing the robustness to SET and also the drawbacks, i.e., the impacts on power consumption, delay, and area cost parameters. For this purpose, ten 2:1 multiplexer designs were chosen from [11,30], covering the static CMOS and DCVSL logic styles, which are recognized for their low power consumption characteristics.

Regarding robustness, the C-Element stands out as the most effective technique for mitigating transient faults, as long as these faults are restricted to the temporal pre-filtering block. However, its implementation has a considerable negative impact on propagation delay and power consumption. Although the impact on the area is not critical, it is still strongly related to the delay block.

The D-Cell technique shows a low impact on propagation delay. However, it is not effective in mitigating transient faults, presenting only an improvement of 10% compared with the traditional circuit robustness, at a moderate area cost.

The transistor sizing technique presents more interesting results. For X2 sizing, the impacts on power and delay are 1.77x and 0.8x respectively, making the circuits faster. However, like the D-Cell, it is not efficient in mitigating failures, either in the average behavior or in the input vector analysis. By combining X2 + DC, the behavior changes. The addition of the D-Cell almost doubles the power consumption, makes the circuits slower, and increases the area, without any circuit reaching the 5 MeV target.

Our analysis demonstrates that X4 and X4 + DC transistor sizing impact power and area characteristics across all multiplexer designs while emerging as the only viable solutions, besides the C-Element, capable of meeting the stringent 5 MeV threshold. However, it is important to highlight that for the X4 + DC technique, the impact on the delay is nullified, due to the characteristics of each technique. These findings confirm X4 + DC as the most balanced hardening approach for radiation-sensitive applications where performance cannot be compromised.

Notably, while the LETth response is uniform among inverter-based designs (V1, V2, V3, V6), their area, power, and delay vary substantially, emphasizing the importance of considering all design parameters in optimization. The standout performer is design V5, which consistently achieves superior robustness, setting it apart as the reference implementation for robust multiplexer design under radiation constraints. These findings suggest that particularly when using X4 + DC, designers can reach the required tolerance levels while balancing power and area costs. Designs V4, V8, and V9 exhibit a considerably higher standard deviation in LETth values across the different input vectors, as highlighted in Table 3. This large variability indicates that the radiation robustness of these circuits is highly dependent on the specific input vector being applied. As a result, these designs are not suitable alternatives in scenarios where the input vector probability distribution deviates from the typical assumption of uniform (50%) probability. In practical applications where certain input vectors may occur more frequently or are more critical, choosing designs with more consistent LETth behavior—such as V5—ensures more reliable and predictable radiation tolerance.

While designs V1–V3 and V6 failed to meet radiation targets, they revealed crucial insights about inverter vulnerability that will guide future work. Our ongoing research focuses on two key advancements: (1) developing asymmetric sizing approaches specifically for output inverter structures and (2) evaluating layout-level optimization including Enclosed Layout Transistors (ELTs) for enhanced radiation tolerance. These developments will address the current limitations while advancing toward radiation-hardened multiplexers capable of meeting the extreme demands of next-generation space electronics. The foundational results presented here establish critical benchmarks for these forthcoming innovations in radiation-hardened IC design.

Author Contributions

Conceptualization, A.F.D.R., B.B.S., C.M. and R.B.S.; methodology, A.F.D.R., B.B.S., C.M. and R.B.S.; validation, A.F.D.R. and R.B.S.; formal analysis, A.F.D.R., C.M. and R.B.S.; investigation, A.F.D.R. and R.B.S.; data curation, A.F.D.R. and R.B.S.; writing—original draft preparation, A.F.D.R. and B.B.S.; writing—review and editing, C.M. and R.B.S.; visualization, A.F.D.R.; supervision, C.M. and R.B.S. All authors have read and agreed to the published version of the manuscript.

Funding

This research study has not receive any funding support.

Data Availability Statement

The original contributions presented in this study are included in the article. Further inquiries can be directed to the corresponding author.

Acknowledgments

The authors are grateful for the financial support from the following Brazilian institutes: Coordenação de Aperfeiçoamento de Pessoal de Nível Superior—Brasil (CAPES), Fundação de Amparo à Pesquisa do Estado do Rio Grande do Sul (FAPERGS), and Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPq).

Conflicts of Interest

The authors declare no conflicts of interest. The funders had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript; or in the decision to publish the results.

References

- Benedetto, J.; Eaton, P.; Mavis, D.; Gadlage, M.; Turflinger, T. Digital single event transient trends with technology node scaling. IEEE Trans. Nucl. Sci. 2006, 53, 3462–3465. [Google Scholar] [CrossRef]

- Dodd, P.; Shaneyfelt, M.; Schwank, J.; Felix, J. Current and future challenges in radiation effects on CMOS electronics. IEEE Trans. Nucl. Sci. 2010, 57, 1747–1763. [Google Scholar] [CrossRef]

- Hughes, H.; Benedetto, J. Radiation effects and hardening of MOS technology: Devices and circuits. IEEE Trans. Nucl. Sci. 2003, 50, 500–521. [Google Scholar] [CrossRef]

- Messenger, G. Collection of charge on junction nodes from ion tracks. IEEE Trans. Nucl. Sci. 1982, 29, 2024–2031. [Google Scholar] [CrossRef]

- Dodd, P.E.; Massengill, L.W. Basic mechanisms and modeling of single-event upset in digital microelectronics. IEEE Trans. Nucl. Sci. 2003, 50, 583–602. [Google Scholar] [CrossRef]

- Pannu, N.; Prakash, N.R. Modeling and simulation of low power single event upset-resilient SRAM cell. Analog. Integr. Circuits Signal Process. 2025, 122, 19. [Google Scholar] [CrossRef]

- Schwank, J.R.; Rodbell, K.P.; Heidel, D.F.; Pellish, J.A.; Marshall, P.W.; Tang, H.H.; Murray, C.E.; LaBel, K.A.; Gordon, M.S.; Stawiasz, K.G.; et al. 32 and 45 nm Radiation-Hardened-By-Design (RHBD) SOI Latches; Technical Report; Sandia National Lab. (SNL-NM): Albuquerque, NM, USA, 2011. [Google Scholar]

- Oliveira, R.N.M.; da Silva, F.G.R.G.; Reis, R.; Schvittz, R.B.; Meinhardt, C. Improving Soft Error Robustness of Full Adder Circuits with Decoupling Cell and Transistor Sizing. In Proceedings of the 2022 35th SBC/SBMicro/IEEE/ACM Symposium on Integrated Circuits and Systems Design (SBCCI), Porto Alegre, Brazil, 22–26 August 2022; pp. 1–6. [Google Scholar] [CrossRef]

- Oliveira, I.F.V.; Pontes, M.F.; Schvittz, R.B.; Rosa, L.S.; Butzen, P.F.; Soares, R.I. Fault Tolerance Evaluation of Different Majority Voter Designs. In Proceedings of the 2022 IEEE International Symposium on Circuits and Systems (ISCAS), Austin, TX, USA, 27 May–1 June 2022; pp. 185–189. [Google Scholar] [CrossRef]

- Pontes, M.F.; Oliveira, I.F.V.; Schvittz, R.B.; Rosa, L.S.; Butzen, P.F. The Impact of Logic Gates Susceptibility in Overall Circuit Reliability Analysis. In Proceedings of the 2022 IEEE International Symposium on Circuits and Systems (ISCAS), Austin, TX, USA, 27 May–1 June 2022; pp. 1610–1614. [Google Scholar] [CrossRef]

- Ana Flávia D., R.; Bernardo B., S.; Cristina, M.; Adriano V., W.; Rafael B., S. Evaluation of Transient Fault Tolerance in Different Logic Styles of 2: 1 Multiplexers. In Proceedings of the 2025 IEEE 16th Latin America Symposium on Circuits and Systems (LASCAS), Bento Gonçalves, Brazil, 25–28 February 2025; Volume 1, pp. 1–5. [Google Scholar] [CrossRef]

- Ramesh, S.; Sundararajan, T.; Prasad, M.J.C.; Senthilkumar, P. Performance Comparison of Static CMOS and Domino Logic Style in VLSI Design: A Review. Int. J. Future Revolut. Comput. Sci. Commun. Eng. 2019, 5, 47–53. [Google Scholar]

- Oklobdzija, V.G. Differential and pass-transistor CMOS logic for high performance systems. Microelectron. J. 1998, 29, 679–688. [Google Scholar] [CrossRef]

- Toro, D.G.; Arzel, M.; Seguin, F.; Jézéquel, M. Soft error detection and correction technique for radiation hardening based on C-element and BICS. IEEE Trans. Circuits Syst. II Express Briefs 2014, 61, 952–956. [Google Scholar]

- Andjelkovic, M.; Babic, M.; Li, Y.; Schrape, O.; Krstic, M.; Kraemer, R. Use of decoupling cells for mitigation of SET effects in CMOS combinational gates. In Proceedings of the 2018 25th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Bordeaux, France, 9–12 December 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 361–364. [Google Scholar]

- Kastensmidt, F.L.; Assis, T.; Ribeiro, I.; Wirth, G.; Brusamarello, L.; Reis, R. Transistor sizing and folding techniques for radiation hardening. In Proceedings of the 2009 European Conference on Radiation and Its Effects on Components and Systems, Brugge, Belgium, 14–18 September 2009; pp. 512–519. [Google Scholar] [CrossRef]

- Velazco, R.; Fouillat, P.; Reis, R. Radiation Effects on Embedded Systems; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2007. [Google Scholar]

- Gomes, I.A.C. Use of Approximate Triple Modular Redundancy for Fault Tolerance in Digital Circuits. Ph.D. Thesis, University of Alicante, San Vicente del Raspeig, Spain, 2018. [Google Scholar]

- Friedberg, W.; Copeland, K. Ionizing Radiation in Earth’s Atmosphere and in Space Near Earth; Technical Report; Office of Aerospace Medicine: Oklahoma City, OK, USA, 2011. [Google Scholar]

- Huang, Q.; Jiang, J. An overview of radiation effects on electronic devices under severe accident conditions in NPPs, rad-hardened design techniques and simulation tools. Prog. Nucl. Energy 2019, 114, 105–120. [Google Scholar] [CrossRef]

- Schvittz, R.B.; Butzen, P.F.; da Rosa, L.S. Methods for susceptibility analysis of logic gates in the presence of single event transients. In Proceedings of the 2020 IEEE International Test Conference (ITC), Washington, DC, USA, 1–6 November 2020; IEEE: Piscataway, NJ, USA, 2020; pp. 1–9. [Google Scholar]

- Ferlet-Cavrois, V.; Massengill, L.W.; Gouker, P. Single Event Transients in Digital CMOS-A Review. IEEE Trans. Nucl. Sci. 2013, 60, 1767–1790. [Google Scholar] [CrossRef]

- Dodd, P.E. Physics-based simulation of single-event effects. IEEE Trans. Device Mater. Reliab. 2005, 5, 343–357. [Google Scholar] [CrossRef]

- Kannaujiya, A.; Shah, A.P. Radiation effects in vlsi circuits-part ii: Hardening techniques. IETE Tech. Rev. 2025, 42, 3–29. [Google Scholar] [CrossRef]

- Zhou, Q.; Mohanram, K. Transistor sizing for radiation hardening. In Proceedings of the 2004 IEEE International Reliability Physics Symposium, Phoenix, AZ, USA, 25–29 April 2004; IEEE: Piscataway, NJ, USA, 2004; pp. 310–315. [Google Scholar] [CrossRef]

- Her, T.; Wong, D. Cell area minimization by transistor folding. In Proceedings of the EURO-DAC 93 and EURO-VHDL 93- European Design Automation Conference, Hamburg, Germany, 20–24 September 1993; pp. 172–177. [Google Scholar] [CrossRef]

- Dua, T.; Rajput, A. 2: 1 multiplexer using different design styles: Comparative analysis. STM J. Adv. Robot. 2020, 7, 5–13. [Google Scholar]

- Zimmermann, R.; Fichtner, W. Low-power logic styles: CMOS versus pass-transistor logic. IEEE J. Solid-State Circuits 2002, 32, 1079–1090. [Google Scholar] [CrossRef]

- Anugraha, R.V.; Durga, D.S.; Avudaiammam, R. Design and performance analysis of 2: 1 multiplexer using multiple logic families at 180 nm technology. In Proceedings of the 2017 2nd IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT), Bengaluru, India, 19–20 May 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 1849–1853. [Google Scholar]

- Cui, Y.; Shan, W.; Cao, P. Ultra-low-power one-hot transmission-gate multiplexer (OTG-MUX) scalable into large fan-in circuits in 28 nm CMOS. Integration 2024, 94, 102094. [Google Scholar] [CrossRef]

- Kumar, N.; Mittal, P.; Rawat, B.; Mittal, M. Dynamic power consumption and delay analysis for ultra-low power 2 to 1 multiplexer designs. Adv. Electr. Electron. Eng. 2021, 19, 145. [Google Scholar] [CrossRef]

- Ray, A. Radiation effects and hardening of electronic components and systems: An overview. Indian J. Phys. 2023, 97, 3011–3031. [Google Scholar] [CrossRef]

- Rajakumar, P.; Kumar, S.S. A comprehensive review of Single Event Transients on various MOS devices. IEEE Access 2024, 12, 154760–154777. [Google Scholar] [CrossRef]

- Kannaujiya, A.; Shah, A.P. Radiation Effects in VLSI Circuits–Part I: Historical Perspective. IETE Tech. Rev. 2024, 41, 716–735. [Google Scholar] [CrossRef]

- Andjelkovic, M.; Calligaro, C.; Schrape, O.; Gatti, U.; Kuentzer, F.; Krstic, M. Standard delay cells with improved tolerance to single event transients. In Proceedings of the 2021 IEEE 32nd International Conference on Microelectronics (MIEL), Nis, Serbia, 12–14 September 2021; IEEE: Piscataway, NJ, USA, 2021; pp. 329–332. [Google Scholar]

- Vogt, H.; Atkinson, G.; Nenzi, P. Ngspice Users Manual Version 44 (Describes Ngspice-44 Release Version). Technical Report, Ngspice Project. 2024. Available online: https://ngspice.sourceforge.io/docs/ngspice-44-manual.pdf (accessed on 24 July 2025).

- Zhao, W.; Cao, Y. New generation of predictive technology model for sub-45 nm early design exploration. IEEE Trans. Electron Devices 2006, 53, 2816–2823. [Google Scholar] [CrossRef]

- Wrobel, F.; Saigné, F. MC-ORACLE: A tool for predicting Soft Error Rate. Comput. Phys. Commun. 2011, 182, 317–321. [Google Scholar] [CrossRef]

- Aguiar, Y.Q.; Wrobel, F.; Autran, J.L.; Leroux, P.; Saigné, F.; Pouget, V.; Touboul, A.D. Mitigation and Predictive Assessment of SET Immunity of Digital Logic Circuits for Space Missions. Aerospace 2020, 7, 12. [Google Scholar] [CrossRef]

- Reddy, T.V.; Nakhate, S. Radiation hardened by design technique to mitigate single event transients in combinational logic circuits. In Proceedings of the 2017 International Conference on Recent Innovations in Signal processing and Embedded Systems (RISE), Bhopal, India, 27–29 October 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 342–347. [Google Scholar]

- Andjelkovic, M.; Ilic, A.; Stamenkovic, Z.; Krstic, M.; Kraemer, R. An overview of the modeling and simulation of the single event transients at the circuit level. In Proceedings of the 2017 IEEE 30th International Conference on Microelectronics (MIEL), Nis, Serbia, 9–11 October 2017; pp. 35–44. [Google Scholar] [CrossRef]

- Carreno, V.A.; Choi, G.; Iyer, R. Analog-Digital Simulation of Transient-Induced Logic Errors and Upset Susceptibility of an Advanced Control System; Technical Report; NASA: Washington, DC, USA, 1990. [Google Scholar]

- Wang, F.; Agrawal, V.D. Single event upset: An embedded tutorial. In Proceedings of the 21st International Conference on VLSI Design (VLSID 2008), Hyderabad, India, 4–8 January 2008; IEEE: Piscataway, NJ, USA, 2008; pp. 429–434. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).