3.1. Irradiation and Annealing Test Results

The transfer characteristic curves (

ID-

VG curves) before and after total dose irradiation and annealing tests are shown in

Figure 1.

Experimental results demonstrated distinct radiation effects and recovery behaviors in NMOS devices: Under a total ionizing dose of 500 krad (Si), the threshold voltage exhibited exceptional stability with a drift of <5 mV, confirming minimal oxide charge trapping influence on gate control. However, off-state leakage current surged from 10−9 A to 10−7 A due to radiation-induced interface traps creating parasitic conduction paths. Subsequent annealing at 100 °C for 168 h fully restored leakage to 10−9 A and recovered the ID-VG curve to its pre-irradiation profile, attributed to hydrogen-mediated passivation of interface defects during thermal treatment. These findings establish that while ionizing radiation primarily degrades off-state leakage through trap-assisted tunneling, standard annealing protocols can completely reverse such damage without compromising threshold voltage integrity, highlighting the robustness of NMOS devices in radiation-aware applications.

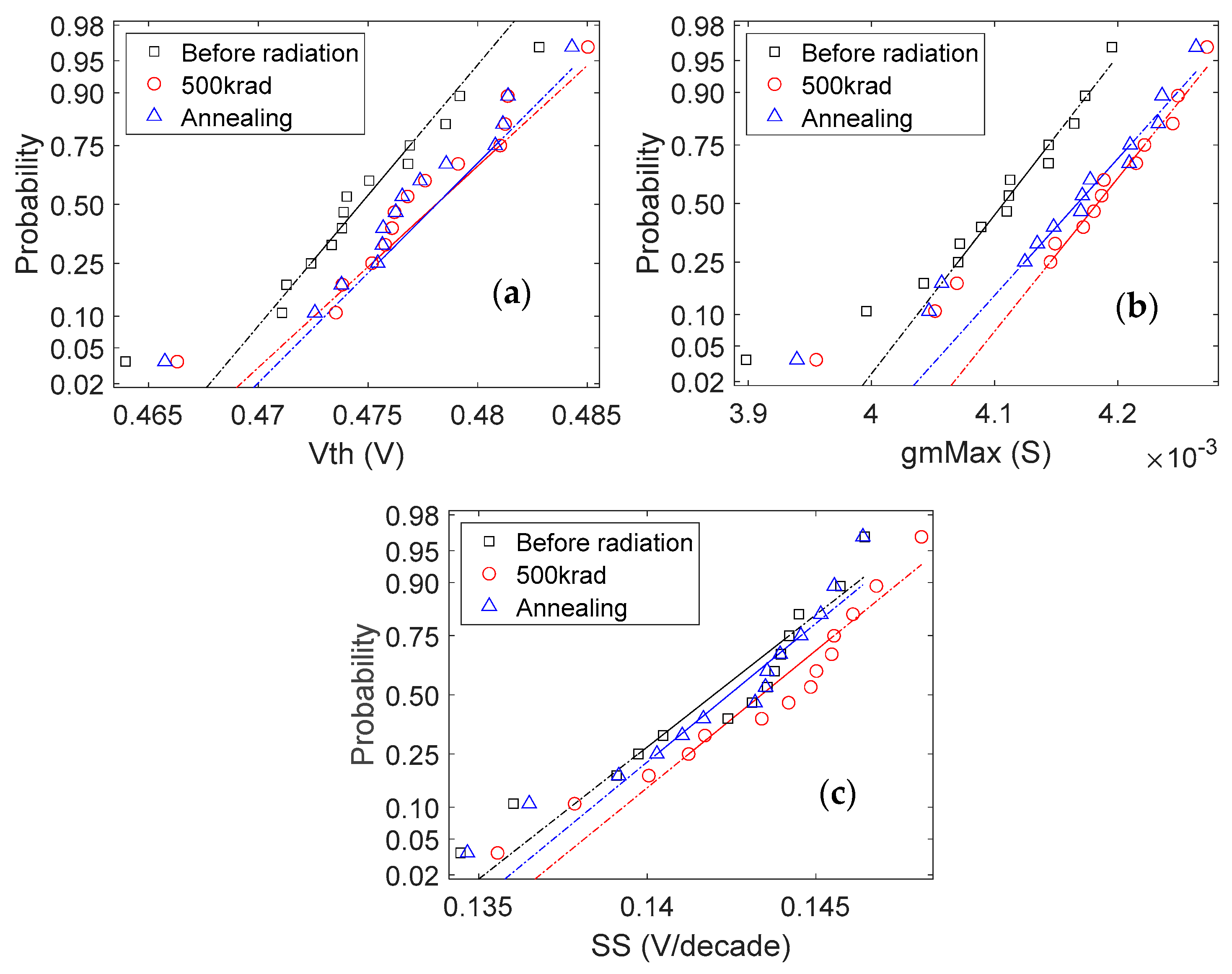

To spread device-to-device variation effects on irradiation and annealing responses, threshold voltage, maximum transconductance (

Gm-max), and subthreshold swing (

SS) distributions are statistically analyzed across multiple devices, as shown in

Figure 2. Notably, the

ID range of 10

−5 A to 10

−4 A is selectively used for

SS extraction to eliminate miscalculations caused by radiation-elevated off-state leakage currents. The threshold voltage shifted from 0.4745 V (pre-irradiation) to 0.4771 V after 500 krad irradiation, only resulting in a Δ

Vth of +2.6 mV. This positive drift dominance indicates that interface trap charges (contributing to

Vth increase) outweighed oxide-trapped charges (inducing

Vth decrease). Post-annealing

Vth remained at 0.4768 V, showing no significant recovery trend. Further analysis of

SS demonstrated irradiation-induced degradation from 0.1420 V/decade to 0.1433 V/decade, consistent with interface trap generation, followed by near-complete restoration to 0.1421 V/decade after annealing. The change in the maximum transconductance value is also very small during the total dose irradiation process, and the change in the maximum transconductance value after irradiation is less than 1 mS.

The persistent Vth stability during annealing suggests a balanced recovery mechanism: both oxide-trapped charges and interface traps recovered at comparable rates, with their opposing contributions (negative vs. positive Vth drift) resulting in a net-zero drift. These observations confirm that while interface traps dominate SS degradation and partial Vth shifts, the counteracting recovery dynamics between oxide and interface charges maintain Vth homeostasis during thermal treatment.

3.2. Hot-Carrier Test Results

After conducting irradiation and annealing tests, hot-carrier tests are performed. The

ID-VG curves under different time conditions are shown in

Figure 3. The results reveal that during the hot-carrier test, the threshold voltage exhibited a positive shift, and the slope of the subthreshold region decreased, indicating an increase in the subthreshold swing.

The

Vth variations during irradiation, annealing, and hot-carrier tests are illustrated in

Figure 4. The results show that the

Vth of the NMOS device is insensitive to TID irradiation, with minimal changes induced by irradiation (Δ

Vth ≈ 2.6 mV, as shown in

Figure 2a). However, during the hot-carrier test, the threshold voltage increased rapidly. At HCI condition 1, the

Vth rose from 0.4771 V to 0.6598 V after 10,000 s of hot-carrier stress, resulting in a Δ

Vth = 182.7 mV. This shift is significantly higher than the average Δ

Vth caused by TID irradiation (2.6 mV), highlighting the severe degradation under hot-carrier stress compared to irradiation effects.

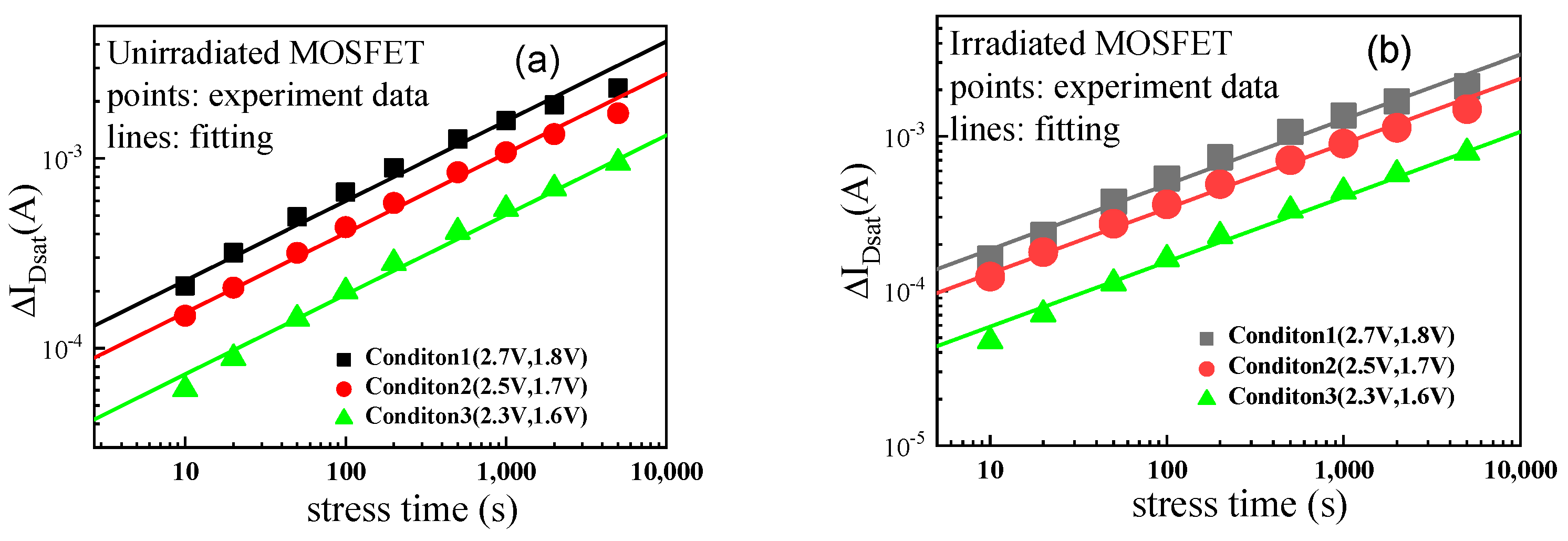

Hot-carrier injection tests are performed on both non-irradiated and irradiated devices under identical conditions.

Figure 5 illustrates the average values and variances of threshold voltage shift (Δ

Vth) and saturation drain current shift (Δ

IDsat) for five devices under three stress conditions as functions of testing time under hot-carrier stress. Δ

Vth represents the change in threshold voltage between before and after HCI testing, while Δ

IDsat denotes the change in saturation drain current between before and after HCI testing. Observations from

Figure 5 reveal that the degradation rate of Δ

Vth in total-dose-irradiated NMOS devices under HCI stress is slightly faster than that of non-irradiated devices, whereas the degradation rates of Δ

IDsat under HCI stress are slower in irradiated devices compared to non-irradiated ones, exhibiting trends opposite to Δ

Vth. As shown in

Figure 5a, under HCI Stress Condition 1 (

VD = 2.7 V,

VG = 1.8 V), the Δ

Vth of irradiated devices increases by 185 mV after 5000 s of HCI stress, while non-irradiated devices show a Δ

Vth of 173 mV, with a minimal difference of 12 mV. Under HCI Stress Condition 3 (

VD = 2.3 V,

VG = 1.6 V), the Δ

Vth values after 5000 s of stress are 71 mV (irradiated) and 68 mV (non-irradiated), differing by only 3 mV. This indicates that the Δ

Vth difference between irradiated and non-irradiated devices is negligible under low HCI stress but becomes more pronounced as stress intensity increases. In contrast, Δ

IDsat exhibits an opposing trend to Δ

Vth. From

Figure 5b, under HCI Stress Condition 1, Δ

IDsat reaches −2.11 mA (irradiated) and −2.34 mA (non-irradiated) after 5000 s of stress, with a difference of +0.23 mA. Under HCI Stress Condition 3, Δ

IDsat values are −0.79 mA (irradiated) and −0.95 mA (non-irradiated), differing by +0.16 mA. It is evident from

Figure 5b that the saturation leakage current decreases with increasing HCI stress time. However, the reduction in saturation leakage current for the unirradiated device is less pronounced compared to the irradiated device, which is contrary to the variation trend of Δ

Vth. Furthermore, the difference in Δ

IDsat between the irradiated and unirradiated devices increases slightly as the hot-carrier stress voltage rises.

3.3. Comparative Analysis of Hot-Carrier Lifetime

To quantitatively evaluate the impact of irradiation on hot-carrier degradation, degradation model parameters extracted before and after irradiation are compared.

According to IEC 62416-2010, the relationship between the degradation amount of MOS device parameters and the degradation time, as well as the stress voltage value, during hot-carrier injection effect testing can be expressed by the following formula:

where ∆

D represents the degradation amount of the MOS device parameter caused by hot-carrier injection stress,

A and

B are coefficients determined through the same global fitting procedure,

C is the degradation time exponent, and

t is time. Based on Formula (1), the threshold voltage shift caused by hot carriers can be expressed by the following equation:

Using the least squares method, a global fitting is performed based on Equation (1) for the degradation data for unirradiated devices under three stress voltages (

VD,stress = 2.7 V, 2.5 V, 2.3 V), yielding the degradation time exponent

C = 0.42 in Equation (2), as shown in

Figure 6a.

By setting the stress time

t = 100 s, the threshold voltage shift Δ

Vth at 1 s corresponds to the value of A × exp (B/

VD,stress). Based on the linear relationship Δ

Vth @100 s~1/

VD,stress, the coefficients are determined as

A = 8.003 and

B = −19.21. The hot-carrier degradation model for non-irradiated devices is expressed as follows:

Using the same model parameter extraction methodology, the hot-carrier degradation model for irradiated devices is derived as follows, with the parameter extraction process illustrated in

Figure 6b:

According to the IEC 62416-2010 standard [

16], based on the model Equations (3) and (4), using Δ

Vth = 50 mV (approximately 10% degradation of the initial

Vth) as the failure criterion, the calculated hot-carrier lifetimes for non-irradiated and irradiated devices operating at

VD = 1.2 V are 2.018 × 10

11 s and 1.330 × 10

11 s, respectively. This indicates that the hot-carrier lifetime for 10% threshold voltage degradation in irradiated devices is approximately 65% of that in non-irradiated devices, demonstrating that total ionizing dose radiation effects accelerate the degradation of threshold voltage under hot-carrier stress.

The saturation drain current variation Δ

IDsat can be expressed by the following equation:

By fitting the average Δ

IDsat values of irradiated and non-irradiated devices (as shown in

Figure 7), the hot-carrier degradation model for Δ

IDsat in non-irradiated devices is derived as follows:

Using the same parameter extraction method, the hot-carrier degradation model for Δ

IDsat in irradiated devices is obtained as follows:

Based on Equations (5) and (6), with ΔIDsat = 0.6 mA (approximately 10% degradation of the initial IDsat as the failure criterion), the calculated hot-carrier lifetimes for 10% saturation drain current degradation in non-irradiated and irradiated devices operating at VD = 1.2 V are 2.917 × 1010 s and 5.835 × 1010 s, respectively. This reveals that the hot-carrier lifetime for 10%, IDsat degradation in irradiated devices is approximately twice that of non-irradiated devices, which is completely contrary to the degradation trend observed for the 50 mV threshold voltage criterion. It can be observed that, despite the minimal threshold voltage shift in the device caused by total dose irradiation, the lifetime corresponding to a 10% saturation leakage current degradation is significantly extended due to the total dose effect.

3.4. Analysis of Hot-Carrier Lifetime Differences

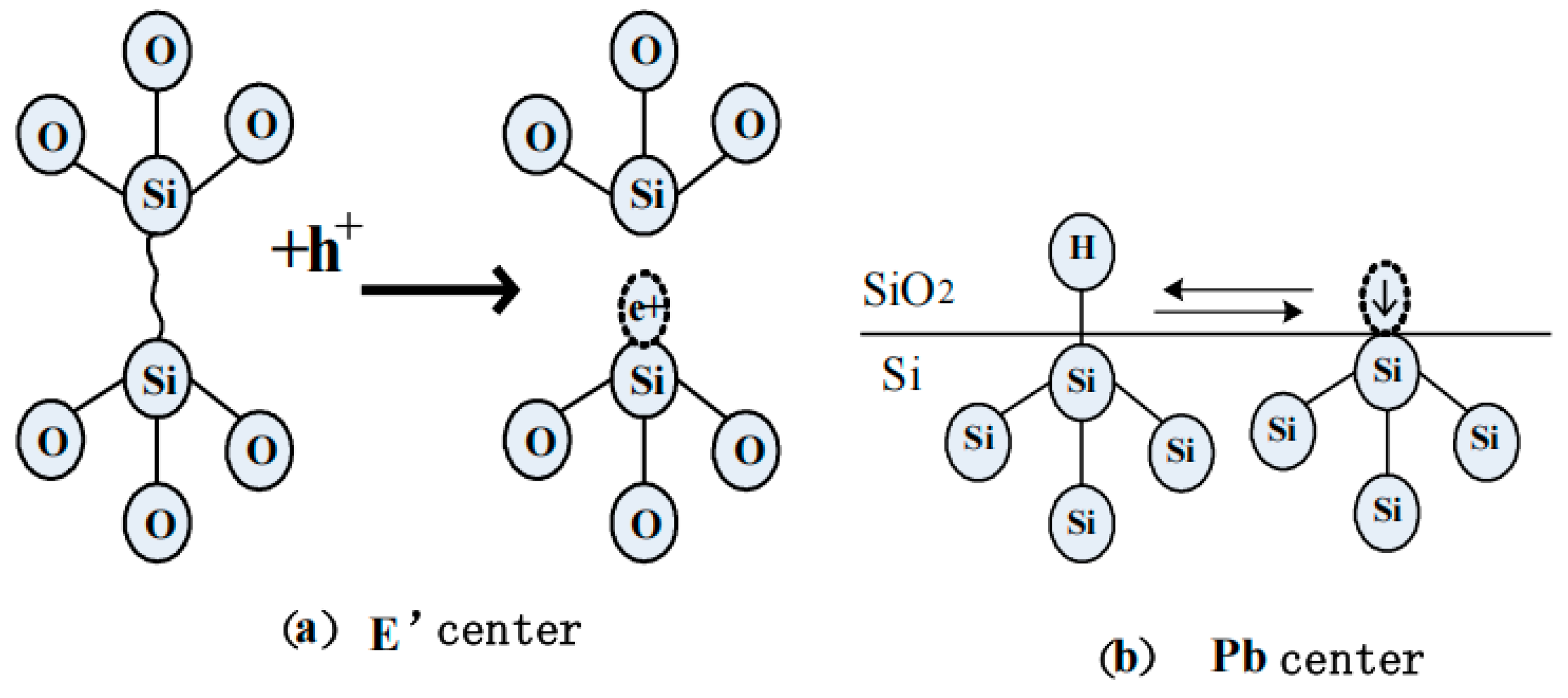

During TID irradiation of NMOS devices, the structural degradation of the gate oxide layer near the Si-SiO

2 interface initiated with the dissociation of Si-Si bonds, creating dangling bonds that preferentially trapped holes to form E’ centers (

Figure 8a). These E’ centers functioned as stable positive oxide trap charges due to their unpaired electrons localized at oxygen vacancy sites. Subsequent hot-carrier injection testing revealed a dynamic interplay between these trapped holes and injected hot electrons: the energetic electrons neutralized the trapped holes in dangling bonds, leading to a net reduction in positive charge within the oxide layer. This charge imbalance directly contributed to a measurable positive shift in threshold voltage, reflecting the cumulative impact of oxide trap charge modulation on device electrostatics.

Concurrently, TID irradiation triggered the transformation of silicon dangling bonds at the Si-SiO

2 interface into Pb centers (

Figure 8b), which exhibited amphoteric trapping behavior. These centers preferentially captured electrons under operational bias, generating negative interface trap charges. Intriguingly, the radiation-induced oxide trap charges displayed non-monotonic evolution during HCI testing, characterized by partial annihilation of trapped holes followed by charge inversion to negative polarity. Similarly, the interface trap charge density exhibited a bimodal trajectory: initial reduction due to recombination of electron–hole pairs with oxide traps near the interface during early HCI stages, succeeded by progressive accumulation as source-injected electrons became trapped by interface defects. The synergistic effect induced by TID and HCI stresses led to dual-phase evolution of oxide traps and interface traps, where the negative oxide trap charges and negative interface trap charges collectively amplified the positive threshold voltage shift through electrostatic coupling across the gate dielectric.

To elucidate the distinct contributions of oxide trap charges (Q

ot) and interface trap charges (D

it), comparative analysis of subthreshold swing (

SS) degradation kinetics under hot-carrier stress is conducted on irradiated and non-irradiated devices (

Figure 9). The subthreshold current can be expressed by the following [

17]:

where

VG is the gate–source voltage,

VD is the drain–source voltage, I

D0 is the channel current when

VG is equal to

Vth,

ψs is the surface potential, and n is the body factor which can be expressed by the following:

where

Cox is the gate oxide capacitance per unit area,

Cd is the depletion capacitance per unit area, and

Cit is the interface trap capacitance per unit area.

So, the subthreshold swing can be expressed by the following:

By substituting Equations (7) and (8) into Equation (9) for calculation, the subthreshold swing (

SS) can be expressed as follows:

Since Cit = q2 × Dit, where Dit is interface trap density, it can be considered that the SS is a function of the interface trap density according to Equation (11).

However,

Figure 9 demonstrates negligible differences in

SS degradation patterns between irradiated and pristine devices, accompanied by minimal variations in D

it evolution during HCI testing. This critical observation conclusively demonstrates that the pronounced hot-carrier lifetime reduction caused by TID radiation predominantly stems from oxide trap charge dynamics (Q

ot) rather than interface trap charge accumulation. The mechanistic dominance of Q

ot is further corroborated by the charge inversion phenomena and sustained negative charge buildup in the oxide layer, which directly modulates carrier transport and enhances local electric fields, thereby accelerating device degradation under hot-carrier stress conditions.

The calculation formula for the saturation drain current is as follows [

17]:

where

μn is electron mobility; W/L is the width-to-length ratio.

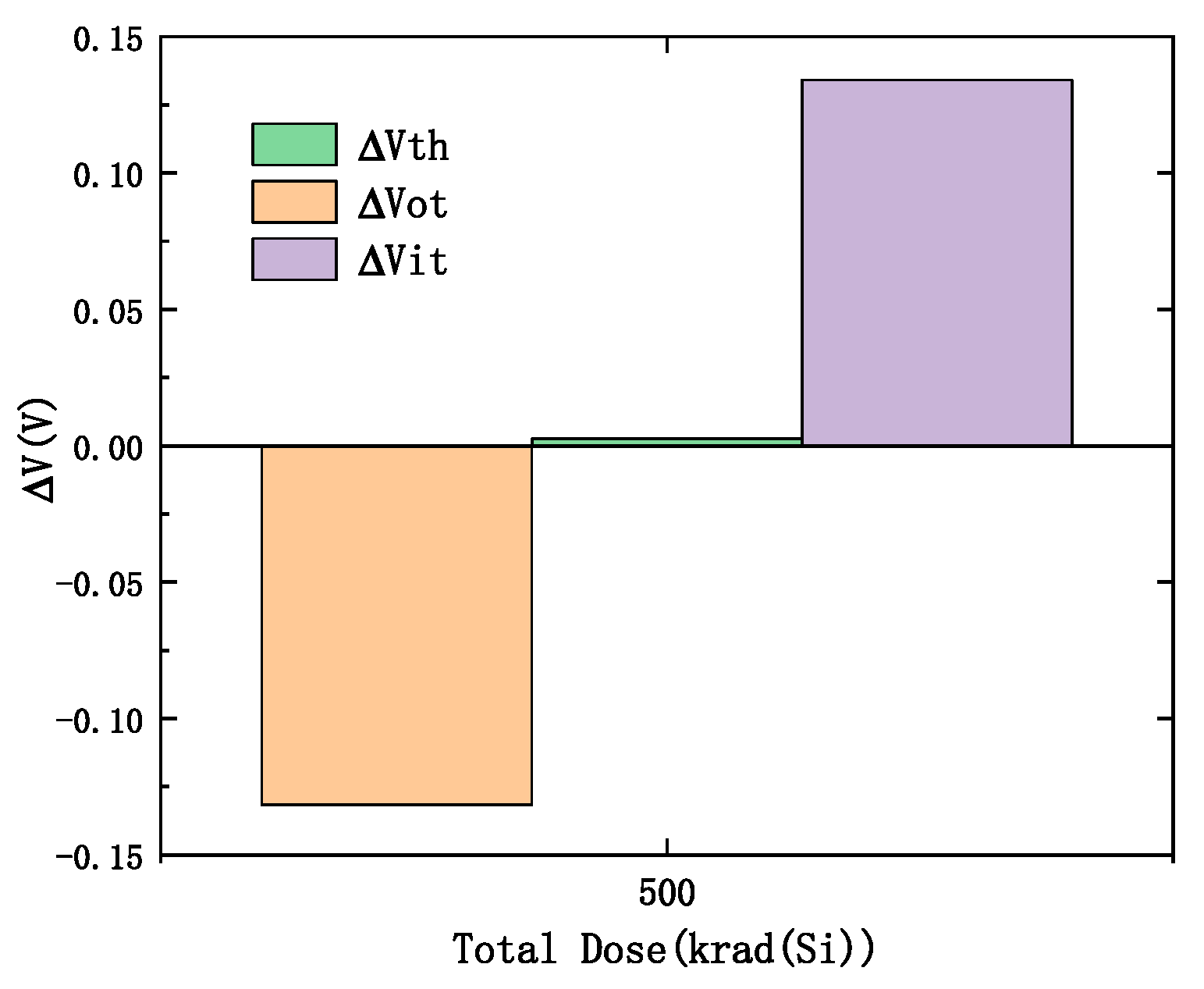

Although the total dose irradiation causes only a minor threshold voltage shift, radiation induces positive oxide trap charge and negative interface trap charge. To separate these two effects, the flat band voltage method [

18] was employed. The threshold voltage shift (Δ

Vot) caused by the oxide trap charge and the threshold voltage shift (Δ

Vit) caused by the interface trap charge are presented in

Figure 10. As can be observed from the figure, despite the total dose irradiation resulting in a small threshold voltage shift of 2.6 mV, Δ

Vot is −0.131 V and Δ

Vit is 0.134 V. This indicates that the induced oxide trap charge and interface trap charge counteract each other in terms of voltage.

The formation of oxide trap charges within the gate dielectric layer under total ionizing dose irradiation enhances Coulomb scattering events between charge carriers and lattice defects, significantly increasing the collision probability and degrading electron mobility through two mechanisms: (1) direct momentum transfer via charged defect scattering and (2) modification of the inversion layer charge density. However, during prolonged HCI testing, the injected high-energy electrons penetrate the oxide layer and undergo recombination with trapped holes in radiation-induced defects, partially neutralizing the positive oxide trap charges and even inducing charge inversion at certain defect sites where trapped holes are replaced by electrons. This dynamic charge compensation process reduces the net positive oxide trap charge density in irradiated devices to levels marginally below those observed in pristine devices under identical stress conditions, paradoxically resulting in less severe electron mobility degradation within the irradiated oxide layer.

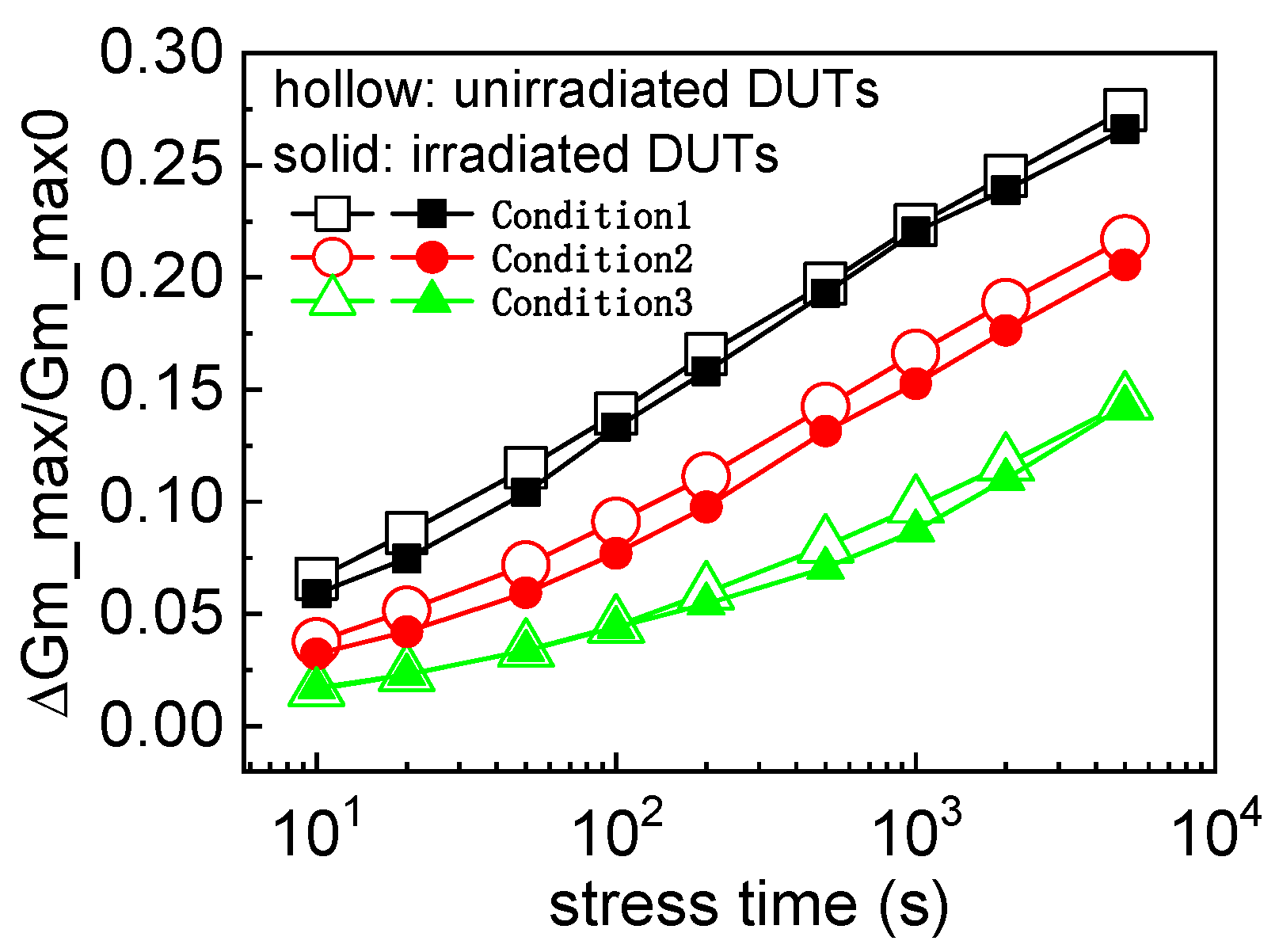

Since electron mobility varies less in irradiated devices compared to unirradiated devices, this also results in a similar pattern for the maximum transconductance (

Gm-max).

Figure 11 shows the variation in the ratio between the change in subthreshold maximum transconductance (Δ

Gm-max) and the pre-stress maximum transconductance (

Gm-max0) with stress time under three hot-carrier injection stress conditions. It can be seen from the figure that all three HCI stress conditions exhibit a consistent trend: the Δ

Gm-max/

Gm-max0 value for irradiated devices is smaller than that for unirradiated devices.

The maximum transconductance in the subthreshold region is expressed as follows [

17]:

As shown in Equation (13), when VD is fixed, Gm-max depends linearly on electron mobility. Due to mobility degradation in irradiated devices, unirradiated devices exhibit lower ΔIDsat values compared to irradiated ones. This behavior contrasts with the ΔVth trend, ultimately leading to a significantly extended lifetime of irradiated devices in hot-carrier stress tests compared to unirradiated counterparts.

Consequently, irradiated NMOS devices exhibit smaller electron mobility variations (Δμn) in the gate oxide region compared to non-irradiated devices during HCI stress, as the radiation-modified defect population provides both trap sites for charge neutralization and recombination centers that mitigate scattering effects. This counterintuitive behavior directly correlates with the observed degradation patterns in ΔIDsat, confirming that IDsat degradation kinetics are predominantly governed by electron mobility changes rather than threshold voltage shifts under these coupled radiation–HCI stress conditions. The experimental validation of this mechanism through parameter extraction and defect spectroscopy aligns with theoretical models describing defect–charge interaction dynamics in irradiated MOS systems, establishing a comprehensive framework for understanding reliability degradation in radiation-hardened devices subjected to combined environmental stresses.