Ion-Induced Charge and Single-Event Burnout in Silicon Power UMOSFETs

Abstract

1. Introduction

2. Materials and Methods

2.1. Devices Under Test

2.2. Alpha Particle Irradiation

2.3. Heavy Ion Irradiation

3. Results

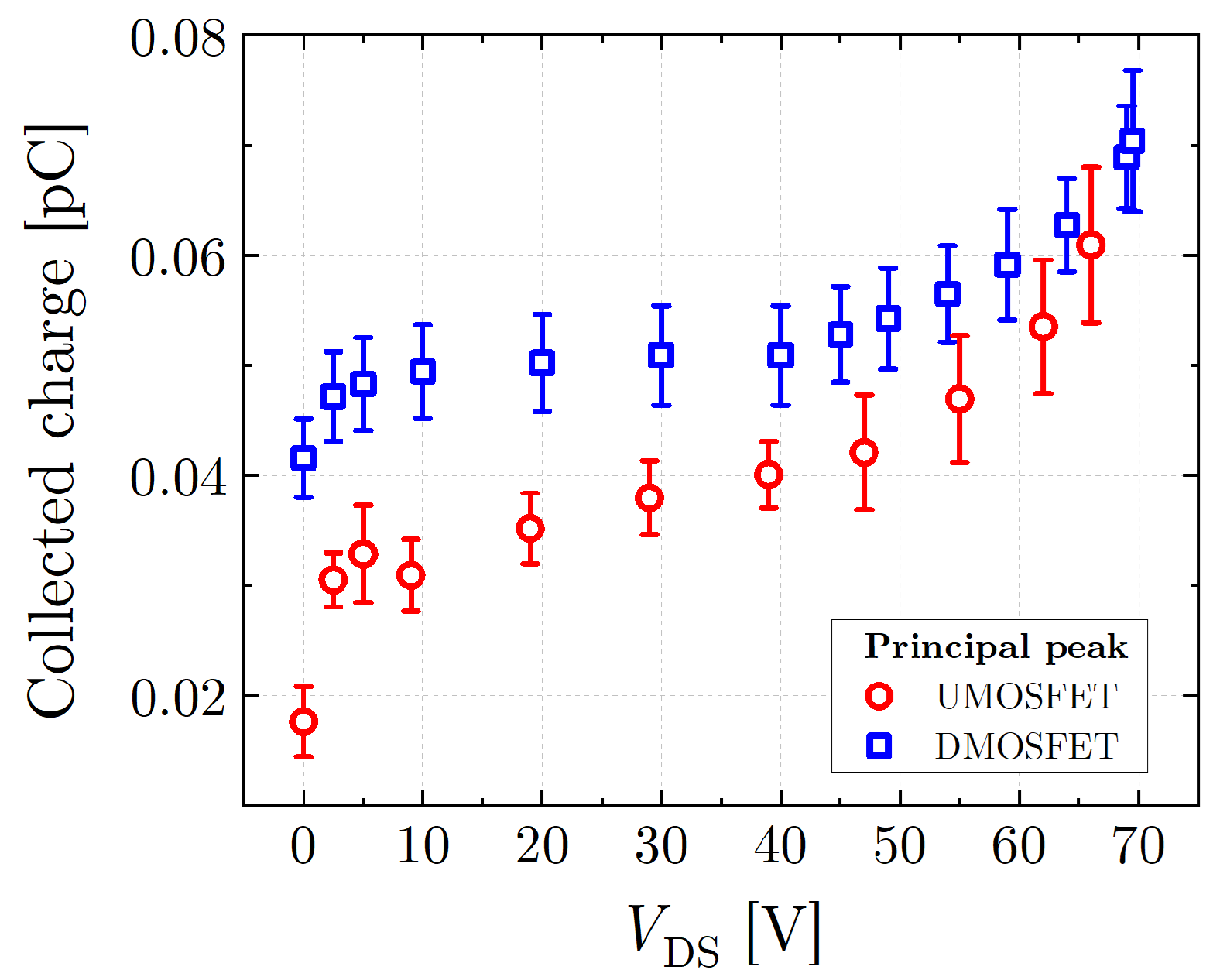

3.1. Alpha Particle Irradiation

3.2. Heavy Ion Irradiation

4. Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Baliga, B.J. Fundamentals of Power Semiconductor Devices, 2nd ed.; Springer International Publishing AG: Cham, Switzerland, 2018. [Google Scholar]

- Aguiar, V.A.; Alberton, S.G.; Pereira, M.S. Radiation-Induced Effects on Semiconductor Devices: A Brief Review on Single-Event Effects, Their Dynamics, and Reliability Impacts. Chips 2025, 4, 12. [Google Scholar] [CrossRef]

- Sexton, F.W. Destructive single-event effects in semiconductor devices and ICs. IEEE Trans. Nucl. Sci. 2003, 50, 603–621. [Google Scholar] [CrossRef]

- Alberton, S.G.; Aguiar, V.A.P.; Medina, N.H.; Added, N.; Macchione, E.L.A.; Menegasso, R.; Cesário, G.J.; Santos, H.C.; Scarduelli, V.B.; Alcántara-Núñez, J.A.; et al. Charge deposition analysis of heavy-ion-induced single-event burnout in low-voltage power VDMOSFET. Microelectron. Reliab. 2022, 137, 114784. [Google Scholar] [CrossRef]

- Alberton, S.G.; Bôas, A.C.V.; Wyss, J.; Aguiar, V.A.P.; Pereira, M.S.; Silvestrin, L.; Mattiazzo, S.; Paccagnella, A.; Cazzaniga, C.; Kastriotou, M.; et al. On the Vulnerability of UMOSFETs in Terrestrial Radiation Environments. IEEE Access 2025, 13, 53885–53894. [Google Scholar] [CrossRef]

- Baliga, B.J. Advanced Power MOSFET Concepts; Springer Science & Business Media: New York, NY, USA, 2010. [Google Scholar]

- Williams, R.K.; Darwish, M.N.; Blanchard, R.A.; Siemieniec, R.; Rutter, P.; Kawaguchi, Y. The trench power MOSFET: Part I—History, technology, and prospects. IEEE Trans. Electron Devices 2017, 64, 674–691. [Google Scholar] [CrossRef]

- Galloway, K.F. A Brief Review of Heavy-Ion Radiation Degradation and Failure of Silicon UMOS Power Transistors. Electronics 2014, 3, 582–593. [Google Scholar] [CrossRef]

- Wang, Y.; Zhang, Y.; Yu, C. Research of Single-Event Burnout in Power UMOSFETs. IEEE Trans. Electron Devices 2013, 60, 887–892. [Google Scholar] [CrossRef]

- Martinella, C.; Alia, R.G.; Stark, R.; Coronetti, A.; Cazzaniga, C.; Kastriotou, M.; Kadi, Y.; Gaillard, R.; Grossner, U.; Javanainen, A. Impact of Terrestrial Neutrons on the Reliability of SiC VD-MOSFET Technologies. IEEE Trans. Nucl. Sci. 2021, 68, 634–641. [Google Scholar] [CrossRef]

- Martinella, C.; Race, S.; Stark, R.; Alia, R.G.; Javanainen, A.; Grossner, U. High-Energy Proton and Atmospheric-Neutron Irradiations of SiC Power MOSFETs: SEB Study and Impact on Channel and Drift Resistances. IEEE Trans. Nucl. Sci. 2023, 70, 1844–1851. [Google Scholar] [CrossRef]

- Aguiar, V.; Medina, N.H.; Added, N.; Macchione, E.L.A.; Alberton, S.; Leite, A.; Aguirre, F.; Ribas, R.; Perego, C.; Fagundes, L.; et al. SAFIIRA: A heavy-ion multi-purpose irradiation facility in Brazil. Rev. Sci. Instruments 2020, 91, 053301. [Google Scholar] [CrossRef]

- Wyss, J.; Bisello, D.; Pantano, D. SIRAD: An irradiation facility at the LNL Tandem accelerator for radiation damage studies on semiconductor detectors and electronic devices and systems. Nucl. Instruments Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2001, 462, 426–434. [Google Scholar] [CrossRef]

- Liu, S.; Marec, R.; Sherman, P.; Titus, J.L.; Bezerra, F.; Ferlet-Cavois, V.; Marin, M.; Sukhaseum, N.; Widmer, F.; Muschitiello, M.; et al. Evaluation on protective single event burnout test method for power DMOSFETs. IEEE Trans. Nucl. Sci. 2012, 59, 1125–1129. [Google Scholar] [CrossRef]

- MIL-STD-750E; Test Method Standard: Test Methods for Semiconductor Devices. Technical Report; Department of Defense (USA): Arlington County, VA, USA, 2006.

- European Space Agency. Single Event Effects Test Method and Guidelines, ESCC Basic Specification No. 25100; Technical Report; European Space Agency: Paris, France, 2014. [Google Scholar]

- JEDEC-JESD57A; Test Procedures for the Measurement of Single-Event Effects in Semiconductor Devices from Heavy-Ion Irradiation. Technical Report; JEDEC Solid State Technology Association: Arlington, VA, USA, 2017.

- Aguiar, V.A.P.; Medina, N.H.; Added, N.; Alberton, S.G.; Macchione, E.L.A.; Guazzelli, M.A.; Melo, M.A.A.; Oliveira, J.A.; Giacomini, R.C.; Aguirre, F.R.; et al. Evaluation of Funnel Models on Calculation of Ion-Induced Collected Charge. IEEE Trans. Electron Devices 2025, 72, 31–36. [Google Scholar] [CrossRef]

- Hohl, J.H.; Galloway, K.F. Analytical model for single event burnout of power MOSFETs. IEEE Trans. Nucl. Sci. 1987, 34, 1275–1280. [Google Scholar] [CrossRef]

- Hohl, J.H.; Johnnson, G. Features of the triggering mechanism for single event burnout of power MOSFETs. IEEE Trans. Nucl. Sci. 1989, 36, 2260–2266. [Google Scholar] [CrossRef]

- Chynoweth, A.G. Ionization rates for electrons and holes in silicon. Phys. Rev. 1958, 109, 1537. [Google Scholar] [CrossRef]

- Felix, J.A.; Shaneyfelt, M.R.; Schwank, J.R.; Dalton, S.M.; Dodd, P.E.; Witcher, J.B. Enhanced Degradation in Power MOSFET Devices Due to Heavy Ion Irradiation. IEEE Trans. Nucl. Sci. 2007, 54, 2181–2189. [Google Scholar] [CrossRef]

- IXYS Corporation. TrenchT3® HiperFET® Power MOSFET. In IXF220N06T3 Datasheet; IXYS Corporation: Milpitas, CA, USA, 2016. [Google Scholar]

- Petersen, E. Single Event Effects in Aerospace; John Wiley & Sons: Hoboken, NJ, USA, 2011. [Google Scholar]

- Titus, J.L.; Wheatley, C.F. SEE Characterization of Vertical DMOSFETs: An Updated Test Protocol. IEEE Trans. Nucl. Sci. 2003, 50, 2341–2351. [Google Scholar] [CrossRef]

- Ziegler, J.F.; Ziegler, M.D.; Biersack, J.P. SRIM—The Stopping and Range of Ions in Matter (2010). Nucl. Instruments Methods Phys. Res. Sect. B Beam Interact. Mater. Atoms 2010, 268, 1818–1823. [Google Scholar] [CrossRef]

- Michez, A.; Dhombres, S.; Boch, J. ECORCE: A TCAD Tool for Total Ionizing Dose and Single Event Effect Modeling. IEEE Trans. Nucl. Sci. 2015, 62, 1516–1527. [Google Scholar] [CrossRef]

- Egawa, H. Avalanche characteristics and failure mechanism of high voltage diodes. IEEE Trans. Electron Devices 1966, ED-13, 754–758. [Google Scholar] [CrossRef]

- Wrobel, T.F.; Coppage, F.N.; Hash, G.L.; Smith, A.J. Current Induced Avalanche in Epitaxial Structures. IEEE Trans. Nucl. Sci. 1985, 32, 3991–3995. [Google Scholar] [CrossRef]

- Sze, S.M. Physics of Semiconductor Devices, 2nd ed.; John Wiley & Sons: Hoboken, NJ, USA, 1981. [Google Scholar]

- Titus, J.L. An updated perspective of single event gate rupture and single event burnout in power MOSFETs. IEEE Trans. Nucl. Sci. 2013, 60, 1912–1928. [Google Scholar] [CrossRef]

- Liu, S.; Titus, J.L.; Boden, M. Effect of buffer layer on single-event burnout of power DMOSFETs. IEEE Trans. Nucl. Sci. 2007, 54, 2554–2560. [Google Scholar] [CrossRef]

- Yu, C.H.; Wang, Y.; Bao, M.T.; Li, X.J.; Yang, J.Q.; Cao, F. Impact of Heavy-Ion Irradiation in an 80-V Radiation-Hardened Split-Gate Trench Power UMOSFET. IEEE Trans. Electron Devices 2022, 69, 664–668. [Google Scholar] [CrossRef]

- Alberton, S.G.; Vilas-Bôas, A.C.; Guazzelli, M.A.; Aguiar, V.A.P.; Pereira, M.S.; Added, N.; Federico, C.A.; Cavalcante, T.C.; Júnior, E.C.F.P.; Vaz, R.G.; et al. Single-Event Effects Induced by Monoenergetic Fast Neutrons in Silicon Power UMOSFETs. IEEE Trans. Device Mater. Reliab. 2025. early access. [Google Scholar] [CrossRef]

- Kosier, S.L.; Sengupta, A.; Ball, D.R.; Hutson, J.M.; Sternberg, A.L.; Islam, S.; Witulski, A.F.; Schrimpf, R.D.; Galloway, K.F.; Alles, M.L.; et al. Physical Model for SiC Power Device Heavy-Ion Burnout Based on Pre-Strike Depletion Capacitance Energy Storage. IEEE Trans. Nucl. Sci. 2025, 72, 1418–1424. [Google Scholar] [CrossRef]

| Ion | Energy [MeV] | Range [µm] | [MeV.cm2.mg−1] |

|---|---|---|---|

| 4He | 5.486 | 28.0 | 0.6 |

| 28Si | 50.2 | 17.4 | 13.3 |

| 72.0 | 24.8 | 12.1 | |

| 96.0 | 33.8 | 10.9 | |

| 120.0 | 43.9 | 9.9 | |

| 58Ni | 100.0 | 20.1 | 30.9 |

| 140.0 | 25.7 | 31.3 | |

| 196.0 | 33.5 | 30.1 |

| Technology | [cm2] | Normalized per Die Area a |

|---|---|---|

| UMOSFET | ||

| DMOSFET |

| Technology | a | b |

|---|---|---|

| UMOSFET | ||

| DMOSFET |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Alberton, S.G.; Aguiar, V.A.P.; Added, N.; Vilas-Bôas, A.C.; Guazzelli, M.A.; Wyss, J.; Silvestrin, L.; Mattiazzo, S.; Pereira, M.S.; Finco, S.; et al. Ion-Induced Charge and Single-Event Burnout in Silicon Power UMOSFETs. Electronics 2025, 14, 2288. https://doi.org/10.3390/electronics14112288

Alberton SG, Aguiar VAP, Added N, Vilas-Bôas AC, Guazzelli MA, Wyss J, Silvestrin L, Mattiazzo S, Pereira MS, Finco S, et al. Ion-Induced Charge and Single-Event Burnout in Silicon Power UMOSFETs. Electronics. 2025; 14(11):2288. https://doi.org/10.3390/electronics14112288

Chicago/Turabian StyleAlberton, Saulo G., Vitor A. P. Aguiar, Nemitala Added, Alexis C. Vilas-Bôas, Marcilei A. Guazzelli, Jeffery Wyss, Luca Silvestrin, Serena Mattiazzo, Matheus S. Pereira, Saulo Finco, and et al. 2025. "Ion-Induced Charge and Single-Event Burnout in Silicon Power UMOSFETs" Electronics 14, no. 11: 2288. https://doi.org/10.3390/electronics14112288

APA StyleAlberton, S. G., Aguiar, V. A. P., Added, N., Vilas-Bôas, A. C., Guazzelli, M. A., Wyss, J., Silvestrin, L., Mattiazzo, S., Pereira, M. S., Finco, S., Paccagnella, A., & Medina, N. H. (2025). Ion-Induced Charge and Single-Event Burnout in Silicon Power UMOSFETs. Electronics, 14(11), 2288. https://doi.org/10.3390/electronics14112288