High-Efficiency and Cost-Effective 10 W Broadband Continuous Class-J Mode Quasi-MMIC Power Amplifier Design Utilizing 0.25 μm GaN/SiC and GaAs IPD Technology for 5G NR n77 and n78 Bands

Abstract

:1. Introduction

2. Circuit Design

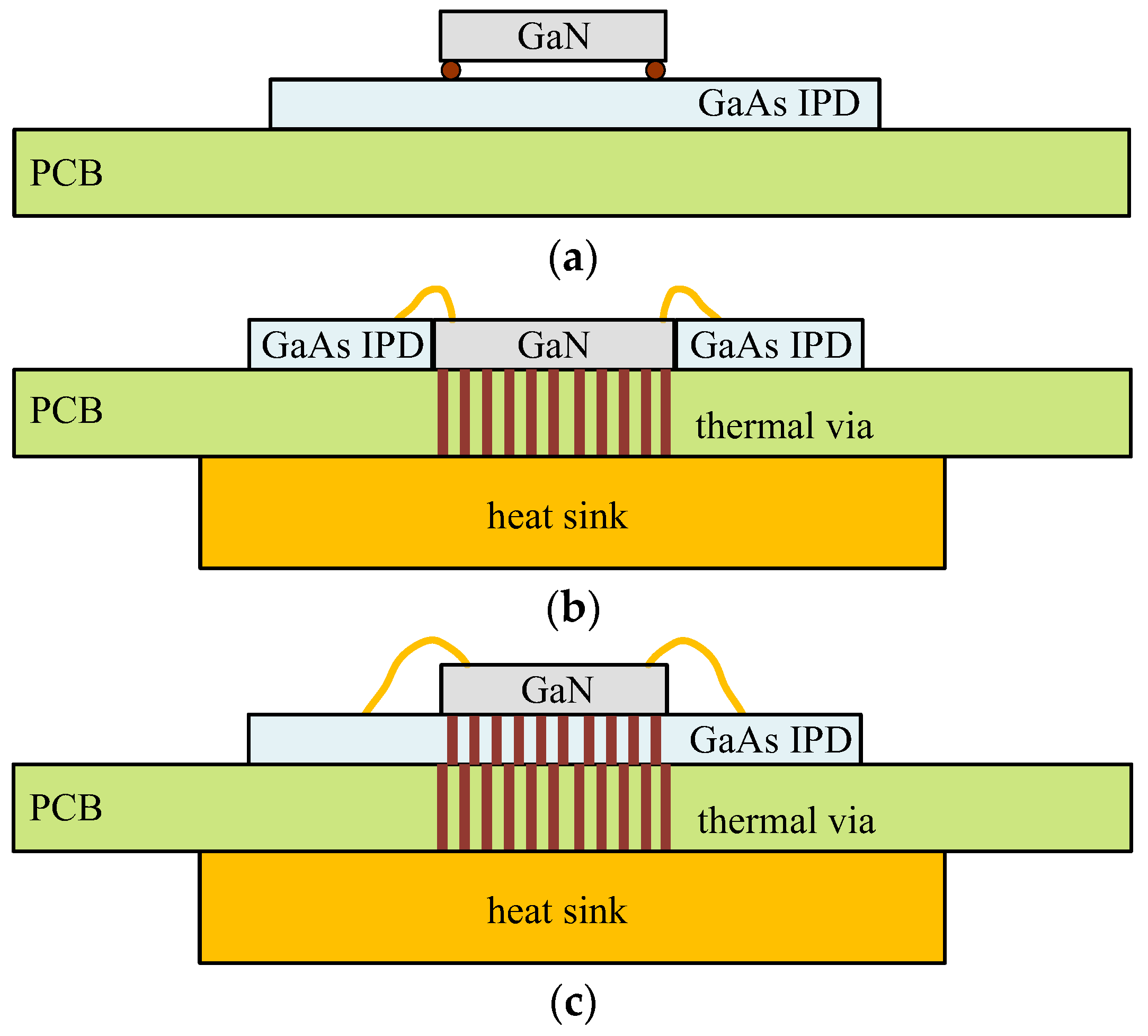

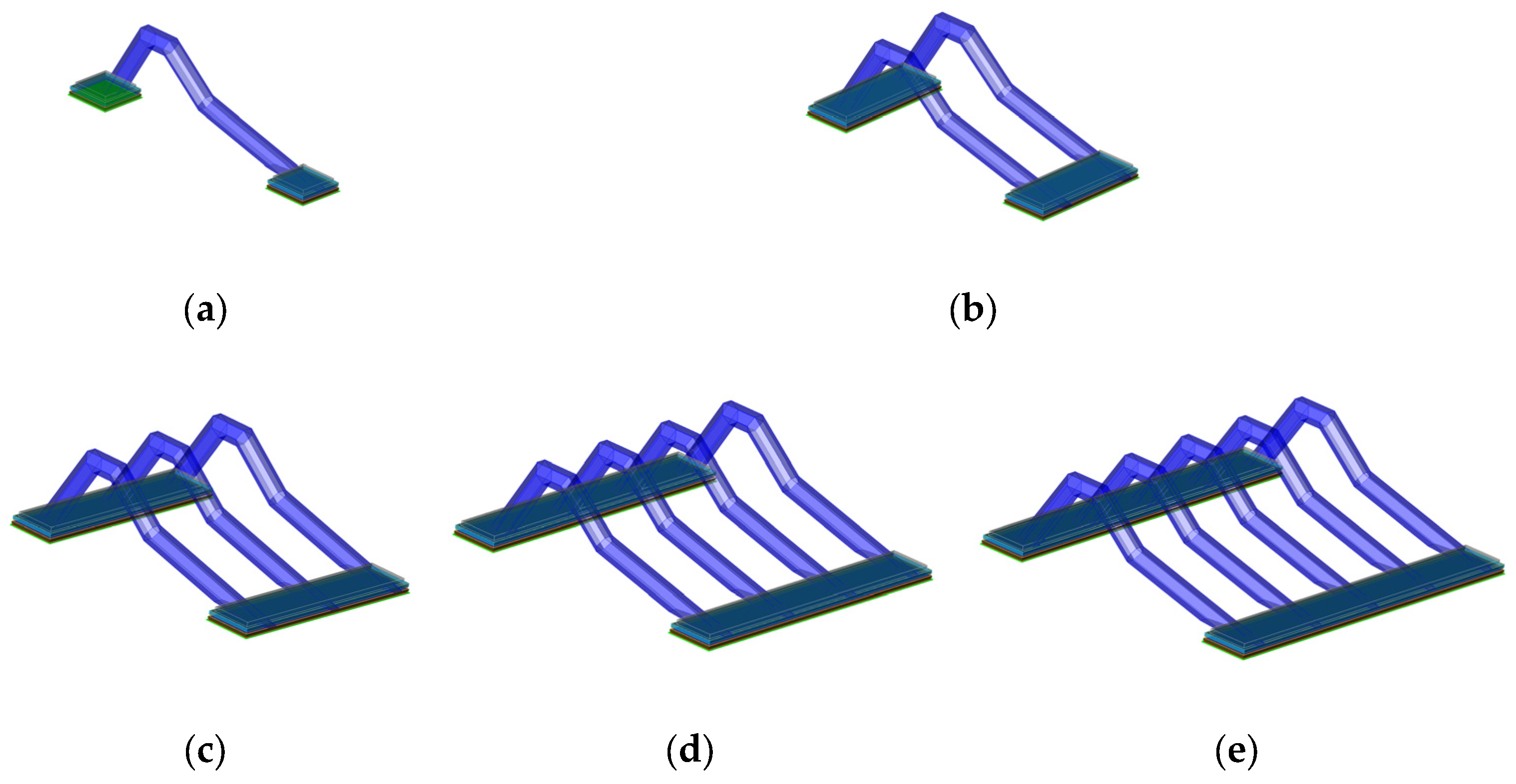

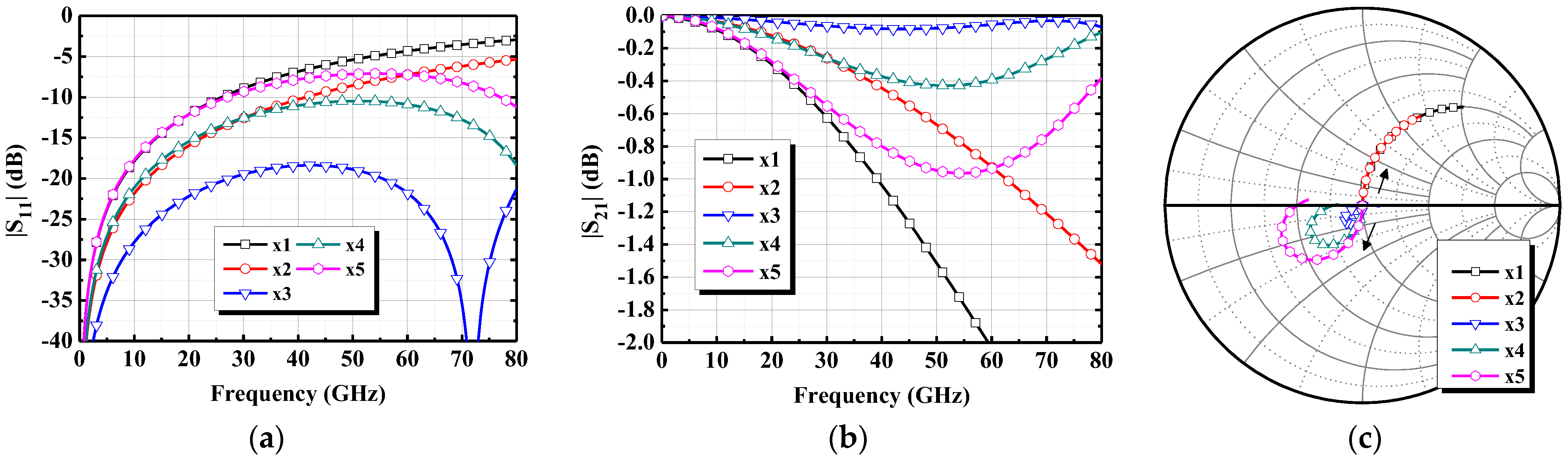

2.1. Assembly and Interconnect Design

2.2. Transistor and Bias Selection

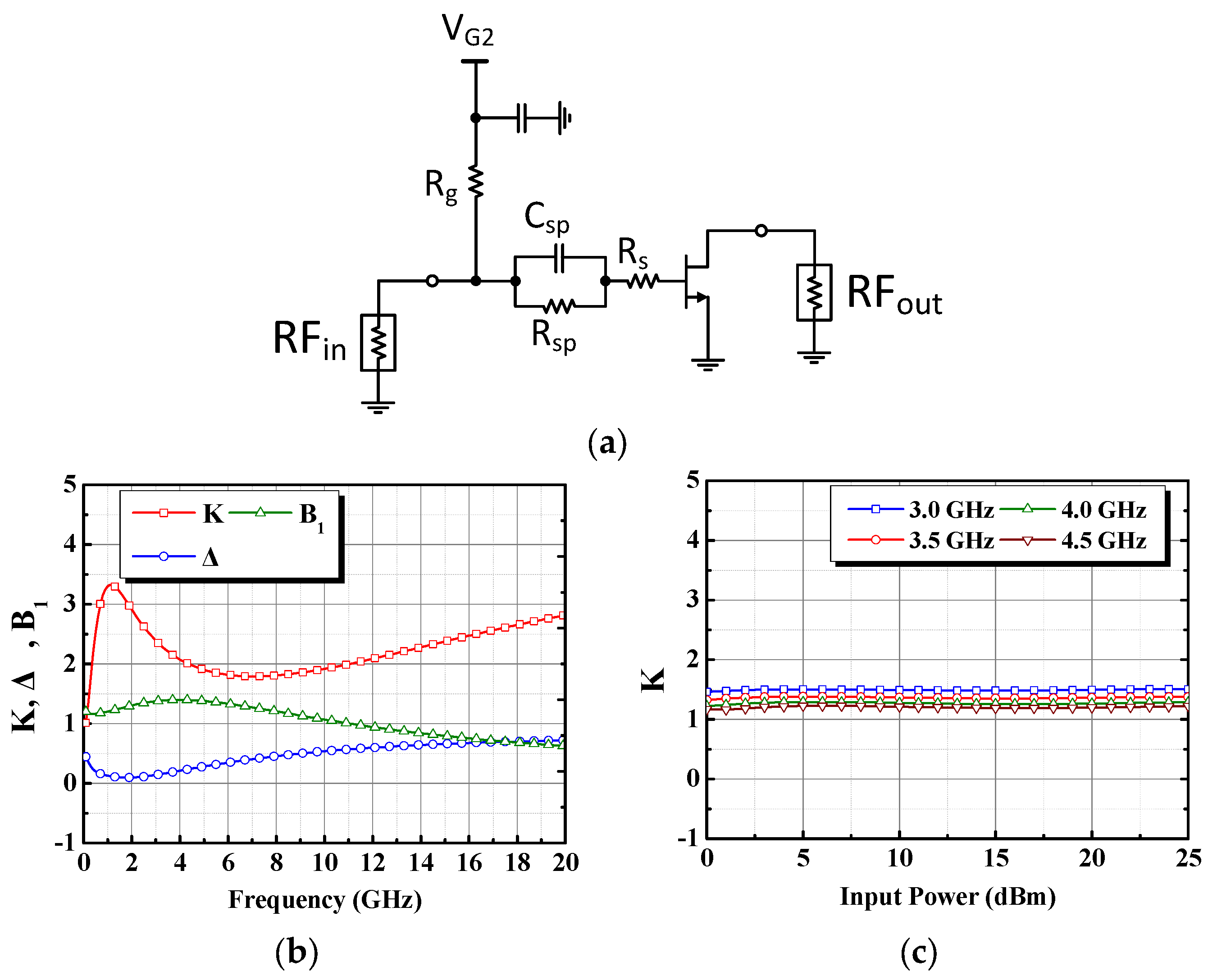

2.3. Bias and Stability Network Design

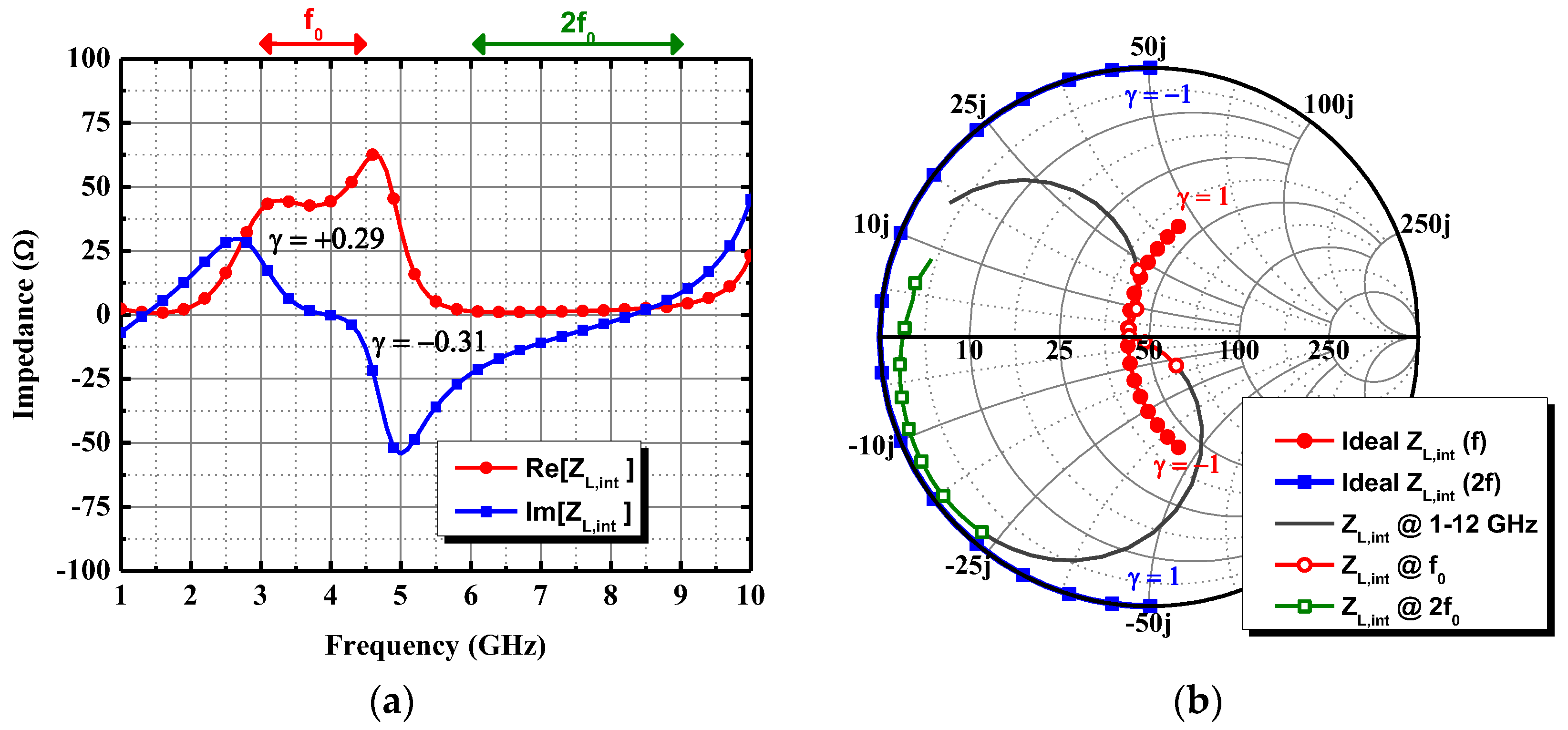

2.4. Class-J Output Matching Network

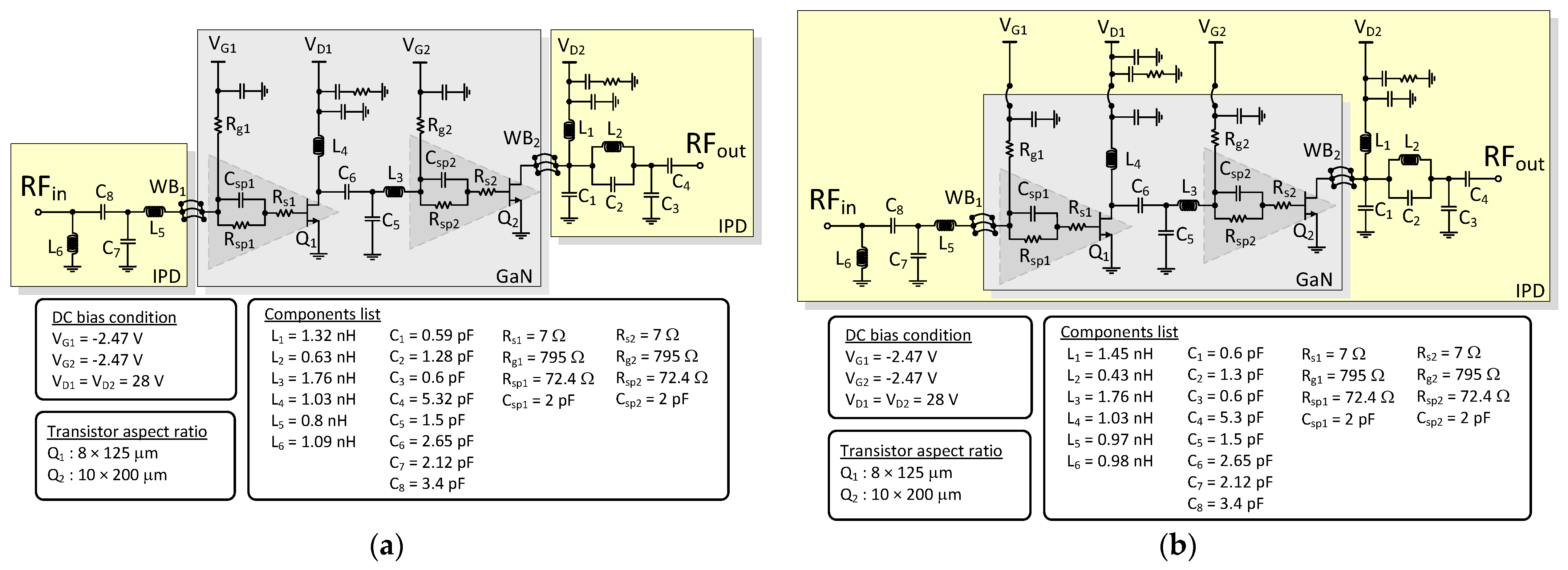

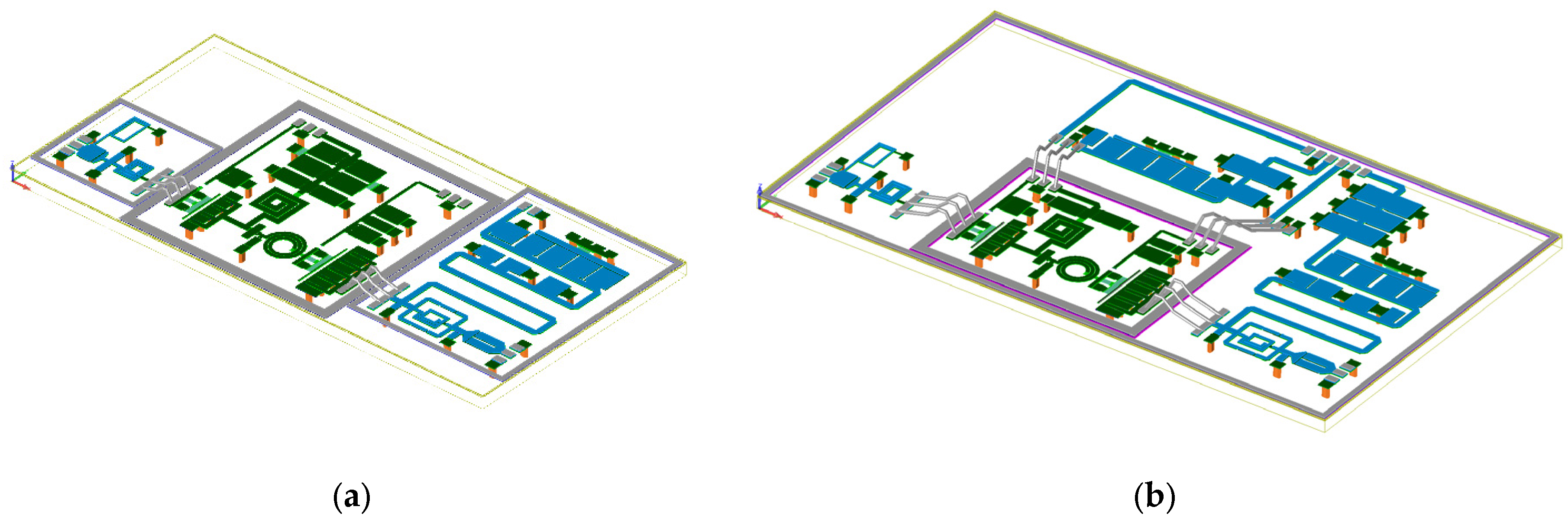

2.5. Schematics, Assemblies, and 3D Views

3. Experimental Results and Discussion

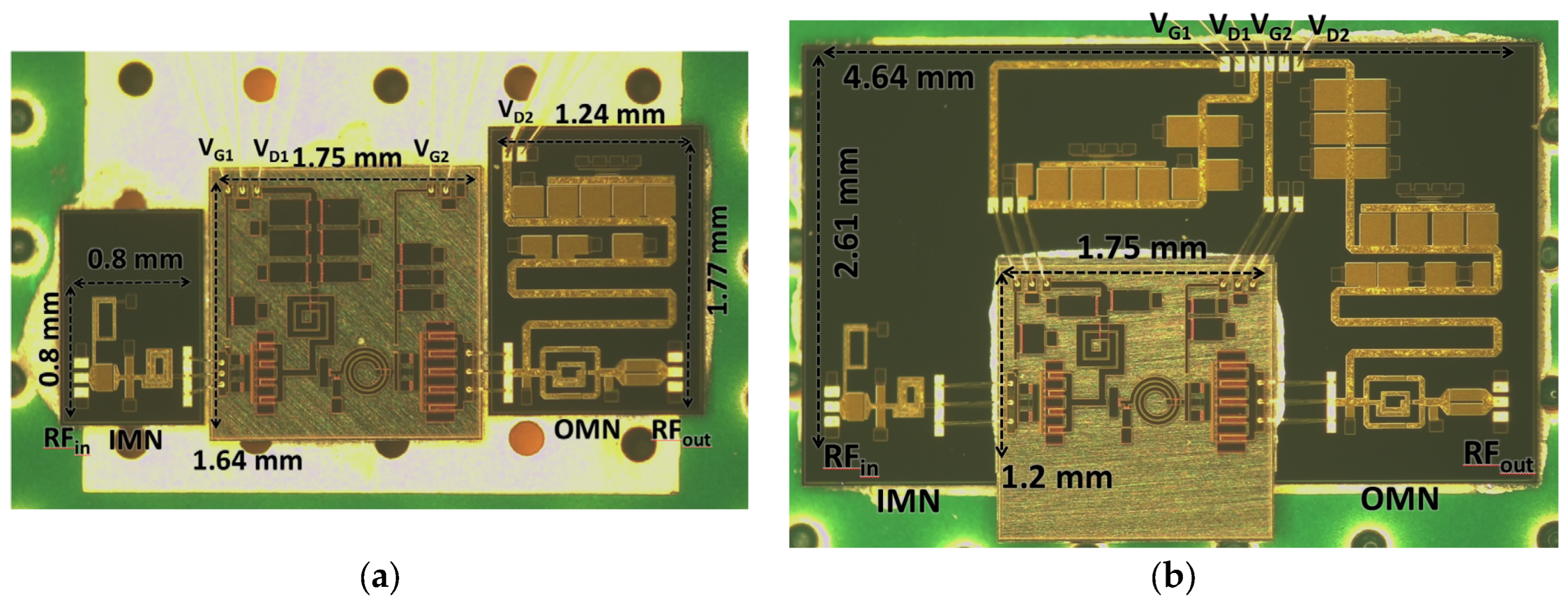

3.1. Chip Photographs and Assemblies

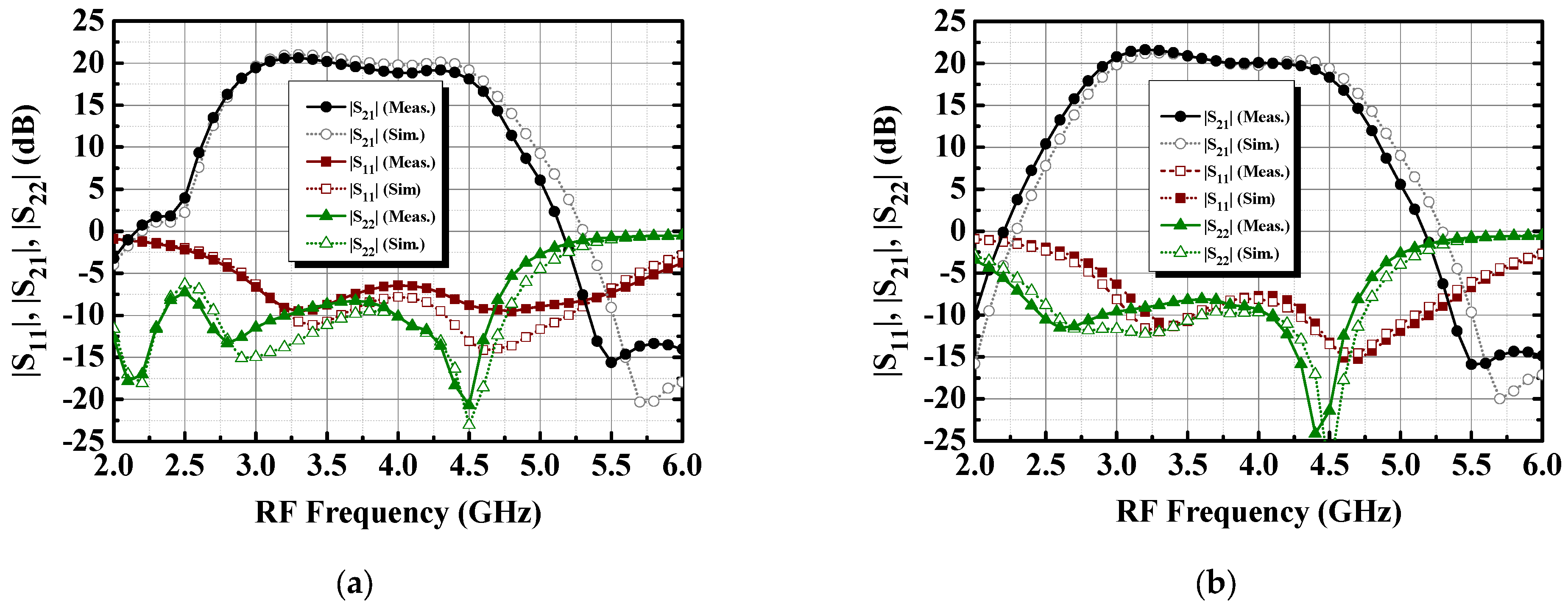

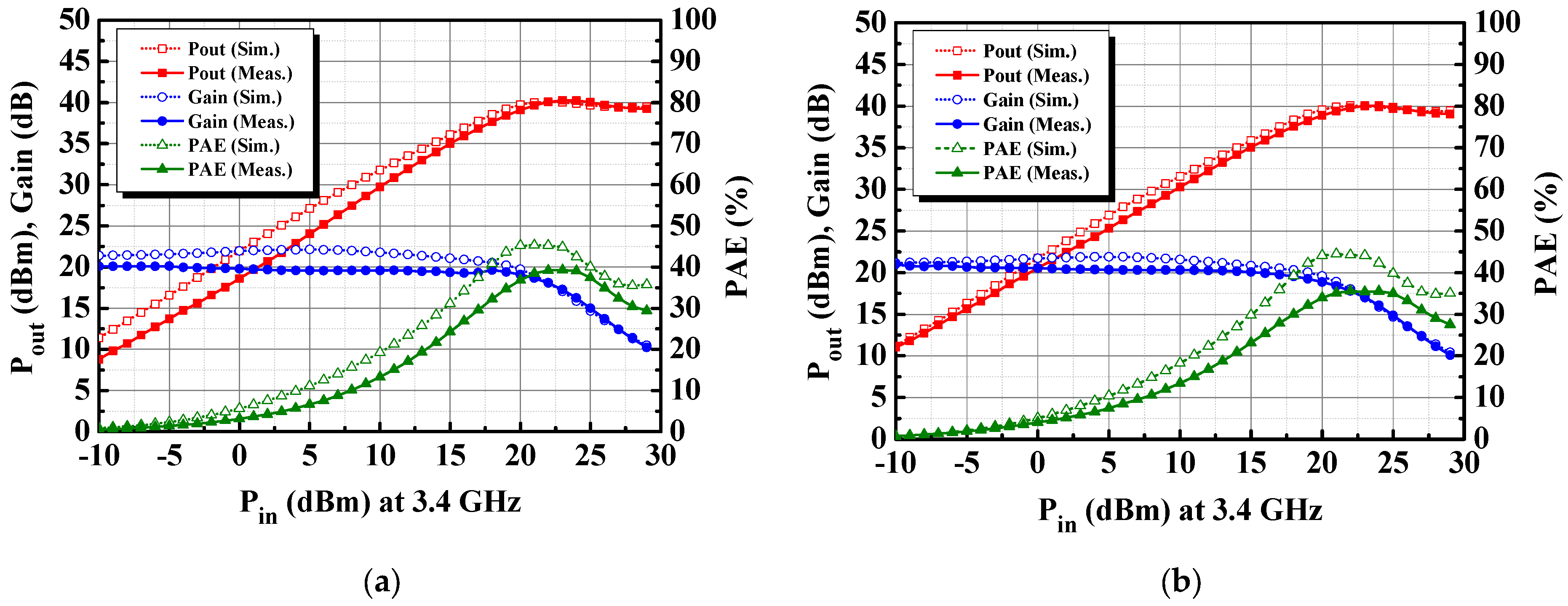

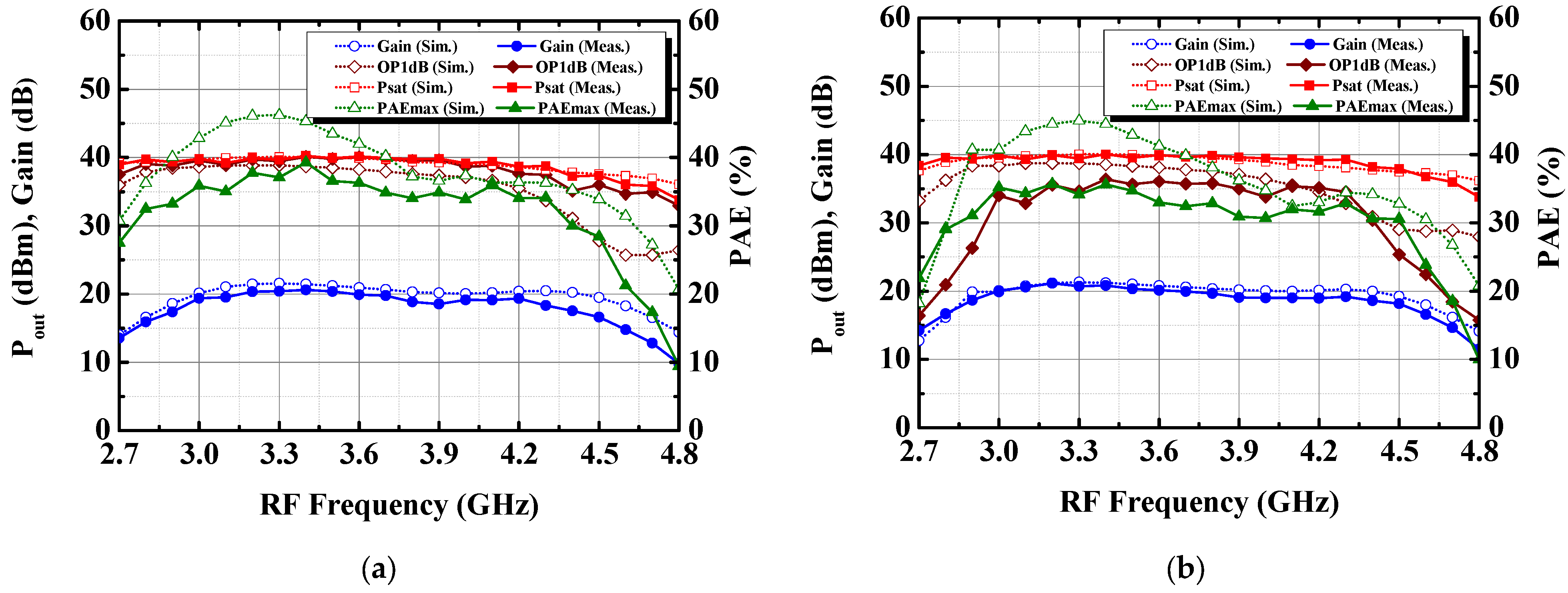

3.2. Small-Signal and Large-Signal Characterizations

3.3. Modulation Signal Characterizations

4. Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Mayeda, J.C.; Lie, D.Y.C.; Lopez, J. A high efficiency fully-monolithic 2-stage C-band GaN power amplifier for 5G microcell applications. In Proceedings of the Texas Symposium on Wireless and Microwave Circuits and Systems (WMCS), Waco, TX, USA, 5–6 April 2018. [Google Scholar]

- Qi, T.; He, S. Power Up Potential Power Amplifier Technologies for 5G Applications. IEEE Microw. Mag. 2019, 20, 89–101. [Google Scholar] [CrossRef]

- Ahn, H.; Back, S.; Nam, I.; An, D.; Lee, J.; Jeong, M.; Kim, B.E.; Lee, Y.T.; Kim, H.T.; Ho, Y.C.; et al. A Fully Integrated −32-dB EVM Broadband 802.11abgn/ac PA With an External PA Driver in WLP 40-nm CMOS. IEEE Trans. Microw. Theory Tech. 2019, 67, 1870–1882. [Google Scholar] [CrossRef]

- Wang, Z.; Hu, S.; Gu, L.; Lin, L. Review of Ka-Band Power Amplifier. Electronics 2022, 11, 942. [Google Scholar] [CrossRef]

- Pengelly, R.S.; Wood, S.M.; Milligan, J.W.; Sheppard, S.T.; Pribble, W.L. A Review of GaN on SiC High Electron-Mobility Power Transistors and MMICs. IEEE Trans. Microw. Theory Tech. 2012, 60, 1764–1783. [Google Scholar] [CrossRef]

- Quaglia, R.; Camarchia, V.; Pirola, M.; Rubio, J.J.M.; Ghione, G. Linear GaN MMIC Combined Power Amplifiers for 7-GHz Microwave Backhaul. IEEE Trans. Microw. Theory Tech. 2014, 62, 2700–2710. [Google Scholar] [CrossRef]

- Cao, T.; Liu, Y.; Chen, W.; Yang, C.; Zhou, J. Analytical Design Solution for Optimal Matching of Hybrid Continuous Mode Power Amplifiers Suitable for a High-Efficiency Envelope Tracking Operation. Electronics 2019, 8, 621. [Google Scholar] [CrossRef]

- Ghisotti, S.; Pisa, S.; Colantonio, P. S Band Hybrid Power Amplifier in GaN Technology with Input/Output Multi Harmonic Tuned Terminations. Electronics 2021, 10, 2318. [Google Scholar] [CrossRef]

- Chen, X.; Wu, Y.; Wang, W. Dual-Band, Dual-Output Power Amplifier Using Simplified Three-Port, Frequency-Dividing Matching Network. Electronics 2022, 11, 144. [Google Scholar] [CrossRef]

- Gustafsson, D.; Andersson, K.; Leidenhed, A.; Malmstrom, M.; Rhodin, A.; Wegeland, T. A packaged hybrid doherty PA for microwave links. In Proceedings of the European Microwave Conference (EuMC), London, UK, 4–6 October 2016. [Google Scholar]

- Ayad, M.; Byk, E.; Neveux, G.; Camiade, M.; Barataud, D. Single and dual input packaged 5.5–6.5GHz, 20W, Quasi-MMIC GaN-HEMT Doherty Power Amplifier. In Proceedings of the IEEE MTT-S International Microwave Symposium (IMS), Honololu, HI, USA, 4–9 June 2017. [Google Scholar]

- Quaglia, R.; Greene, M.D.; Poulton, M.J.; Cripps, S.C. Design and characterization of a 1.7–2.7 GHz quasi-MMIC Doherty power amplifier. In Proceedings of the IEEE MTT-S International Microwave Symposium (IMS), Honololu, HI, USA, 4–9 June 2017. [Google Scholar]

- Quaglia, R.; Greene, M.D.; Poulton, M.J.; Cripps, S.C. A 1.8–3.2-GHz Doherty Power Amplifier in Quasi-MMIC Technology. IEEE Microw. Wirel. Compon. Lett. 2019, 29, 345–347. [Google Scholar] [CrossRef]

- Liu, R.-J.; Zhu, X.-W.; Xia, J.; Chen, P.; Yu, C.; Zhang, L.; Chen, Z.-Y. A 30-W GaN Quasi-MMIC Doherty Power Amplifier Based on All-Distributed Inductors Load Network. In Proceedings of the 2021 51st European Microwave Conference (EuMC), London, UK, 4–6 April 2022. [Google Scholar]

- Cao, Y.; Zhu, X.-W.; Liu, R.-J.; Dong, Q. Design of an S-band quasi-MMIC Power Amplifier. In Proceedings of the 2021 International Conference on Microwave and Millimeter Wave Technology (ICMMT), Nanjing, China, 23–26 May 2021. [Google Scholar]

- Doherty, W.H. A New High Efficiency Power Amplifier for Modulated Waves. Proc. Inst. Radio Eng. 1936, 24, 1163–1182. [Google Scholar]

- Raab, F.H. Class-F power amplifiers with maximally flat waveforms. IEEE Trans. Microw. Theory Tech. 1997, 45, 2007–2012. [Google Scholar] [CrossRef]

- Cripps, S.C.; Tasker, P.J.; Clarke, A.L.; Lees, J.; Benedikt, J. On the Continuity of High Efficiency Modes in Linear RF Power Amplifiers. IEEE Microw. Wirel. Compon. Lett. 2009, 19, 665–667. [Google Scholar] [CrossRef]

- Carrubba, V.; Clarke, A.L.; Akmal, M.; Lees, J.; Benedikt, J.; Tasker, P.J.; Cripps, S.C. The Continuous Class-F Mode Power Amplifier. In Proceedings of the 40th European Microwave Conference, Paris, France, 28–30 September 2010. [Google Scholar]

- Tasker, P.J.; Carrubba, V.; Wright, P.; Lees, J.; Benedikt, J.; Cripps, S. Wideband PA Design: The “Continuous” Mode of Operation. In Proceedings of the 2012 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), La Jolla, CA, USA, 14–17 October 2012. [Google Scholar]

- Li, C.-H.; Ko, C.-L.; Kuo, C.-N.; Kuo, M.-C.; Chang, D.-C. A Low-Cost DC-to-84-GHz Broadband Bondwire Interconnect for SoP Heterogeneous System Integration. IEEE Trans. Microw. Theory Tech. 2013, 61, 4345–4352. [Google Scholar] [CrossRef]

- Chan, C.-H.; Chou, C.-C.; Chuang, H.-R. Integrated Packaging Design of Low-Cost Bondwire Interconnection for 60-GHz CMOS Vital-Signs Radar Sensor Chip with Millimeter-Wave Planar Antenna. IEEE Trans. Compon. Packag. Manuf. Technol. 2018, 8, 177–185. [Google Scholar] [CrossRef]

- Umar, M.; Laabs, M.; Neumann, N.; Plettemeier, D. Bondwire Model and Compensation Network for 60 GHz Chip-to-PCB Interconnects. IEEE Antennas Wirel. Propag. Lett. 2021, 20, 2196–2200. [Google Scholar] [CrossRef]

- Nunes, L.C.; Cabral, P.M.; Pedro, J.C. AM/AM and AM/PM Distortion Generation Mechanisms in Si LDMOS and GaN HEMT Based RF Power Amplifiers. IEEE Trans. Microw. Theory Tech. 2014, 62, 799–809. [Google Scholar] [CrossRef]

- Gonzalez, G. Microwave Transistor Amplifiers: Analysis and Design, 2nd ed.; Pearson: London, UK, 1996; pp. 240–243. [Google Scholar]

- Saxena, S.; Rawat, K.; Roblin, P. Continuous Class-B/J Power Amplifier Using a Nonlinear Embedding Technique. IEEE Trans. Circuits Syst. II Exp. Briefs 2017, 64, 837–841. [Google Scholar] [CrossRef]

- Alizadeh, A.; Hassanzadehyamchi, S.; Medi, A. Integrated Output Matching Networks for Class–J/J−1 Power Amplifiers. IEEE Trans. Circuits Syst. I Reg. Pap. 2019, 66, 2921–2934. [Google Scholar] [CrossRef]

- Nikandish, G.; Staszewski, R.B.; Zhu, A. Design of Highly Linear Broadband Continuous Mode GaN MMIC Power Amplifiers for 5G. IEEE Access 2019, 7, 57138–57150. [Google Scholar] [CrossRef]

- Florian, C.; Cignani, R.; Niessen, D.; Santarelli, A. A C-BAND AlGaN-GaN MMIC HPA for SAR. IEEE Microw. Wirel. Compon. Lett. 2012, 22, 471–473. [Google Scholar] [CrossRef]

- May, S.; Maassen, D.; Rautschke, F.; Boeck, G. Two stage 4–8 GHz, 5 W GaN-HEMT amplifier. In Proceedings of the 2017 47th European Microwave Conference (EuMC), Nuremberg, Germany, 10–12 October 2017. [Google Scholar]

- Zhao, B.; Sanabria, C.; Hon, T. A 2-Stage S-Band 2W CW GaN MMIC Power Amplifier in an Overmold QFN Package. In Proceedings of the 2022 IEEE Texas Symposium on Wireless and Microwave Circuits and Systems (WMCS), Waco, TX, USA, 19–20 April 2022. [Google Scholar]

| Reference | [28] | [29] | [30] | [31] | This Work I (Split) | This Work II (Stack) |

|---|---|---|---|---|---|---|

| Process | GaN 0.25 μm | GaN 0.25 μm | GaN DFN packaged device ** | GaN 0.25 μm | GaN 0.25 μm GaAs IPD | GaN 0.25 μm GaAs IPD |

| Type | One-stage Cont. Class-B | Two-stage | Discrete two-stage | Two-stage | Quasi-MMIC two-stage Cont. Class-J | Quasi-MMIC two-stage cont. Class-J |

| Freq. (GHz) | 4.2–7.0 | 5.2–6.2 | 3.8–8.8 | 2.7–3.5 | 2.85–4.48 | 2.84–4.47 |

| BW (%) | 50 | 17.5 | 79.4 | 25.8 | 44.5 | 44.6 |

| Gain (dB) | 12.4 | 20 | 17 | 19.3 | 21.7 | 21.6 |

| Psat (dBm) | 36.4 | 43 | 37.7 | 34.6 | 40.3 | 40.0 |

| PAEpeak (%) * | 49 | 41 | 38 | 56.6 | 39.3 | 36.5 |

| Chip Size (mm2) | 2.16 | 15.75 | NA | 3.55 | 2.87 (GaN) 2.83 (GaAs) | 2.1 (GaN) 12.11 (GaAs) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chiou, H.-K.; Lin, H.-C.; Chang, D.-C. High-Efficiency and Cost-Effective 10 W Broadband Continuous Class-J Mode Quasi-MMIC Power Amplifier Design Utilizing 0.25 μm GaN/SiC and GaAs IPD Technology for 5G NR n77 and n78 Bands. Electronics 2023, 12, 3494. https://doi.org/10.3390/electronics12163494

Chiou H-K, Lin H-C, Chang D-C. High-Efficiency and Cost-Effective 10 W Broadband Continuous Class-J Mode Quasi-MMIC Power Amplifier Design Utilizing 0.25 μm GaN/SiC and GaAs IPD Technology for 5G NR n77 and n78 Bands. Electronics. 2023; 12(16):3494. https://doi.org/10.3390/electronics12163494

Chicago/Turabian StyleChiou, Hwann-Kaeo, Hsin-Chieh Lin, and Da-Chiang Chang. 2023. "High-Efficiency and Cost-Effective 10 W Broadband Continuous Class-J Mode Quasi-MMIC Power Amplifier Design Utilizing 0.25 μm GaN/SiC and GaAs IPD Technology for 5G NR n77 and n78 Bands" Electronics 12, no. 16: 3494. https://doi.org/10.3390/electronics12163494

APA StyleChiou, H.-K., Lin, H.-C., & Chang, D.-C. (2023). High-Efficiency and Cost-Effective 10 W Broadband Continuous Class-J Mode Quasi-MMIC Power Amplifier Design Utilizing 0.25 μm GaN/SiC and GaAs IPD Technology for 5G NR n77 and n78 Bands. Electronics, 12(16), 3494. https://doi.org/10.3390/electronics12163494