Anomalous PBTI Effects in N-Type Super Junction under High Gate Voltage Stress

Abstract

:1. Introduction

2. Result and Discussion

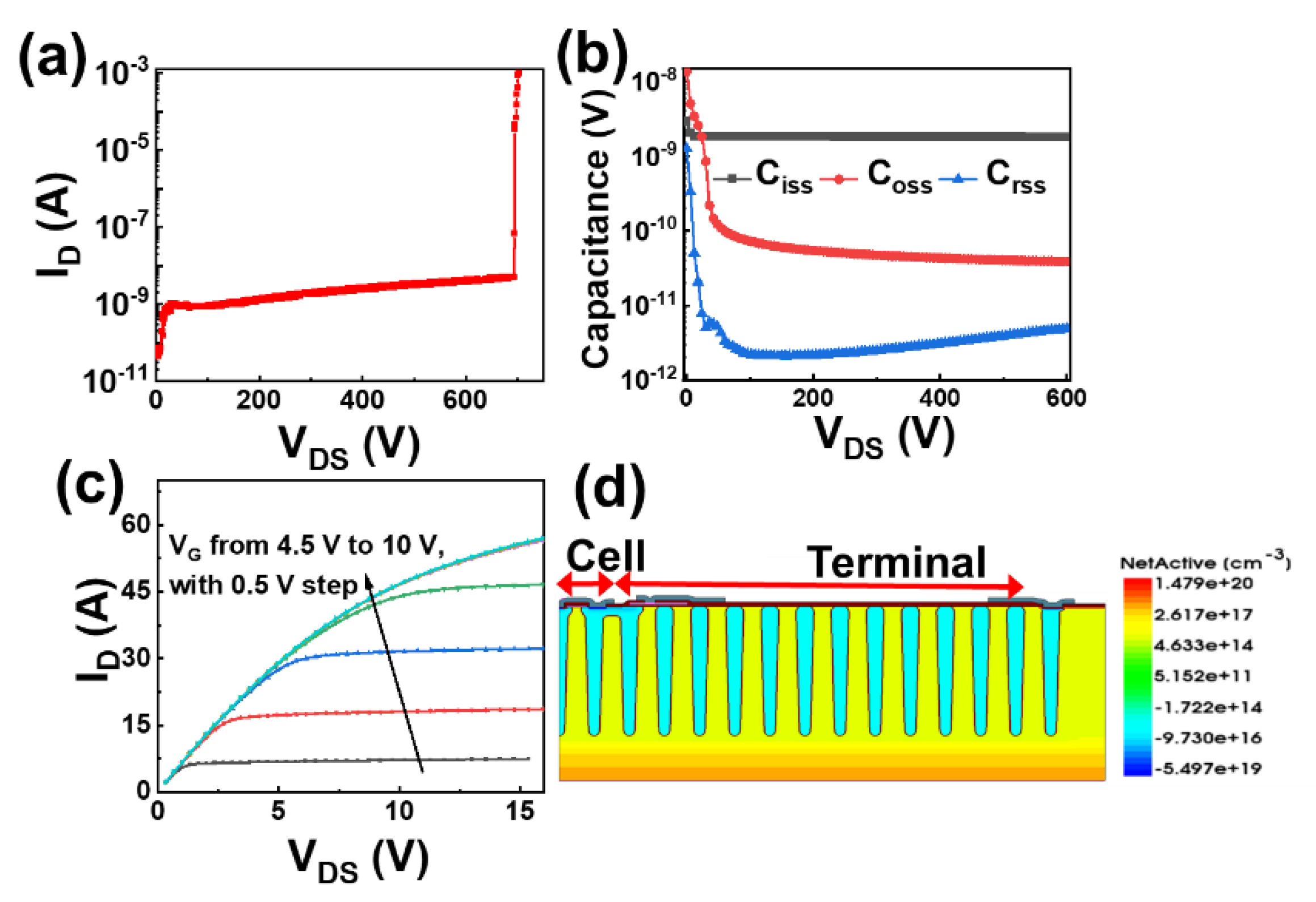

2.1. Device Structure

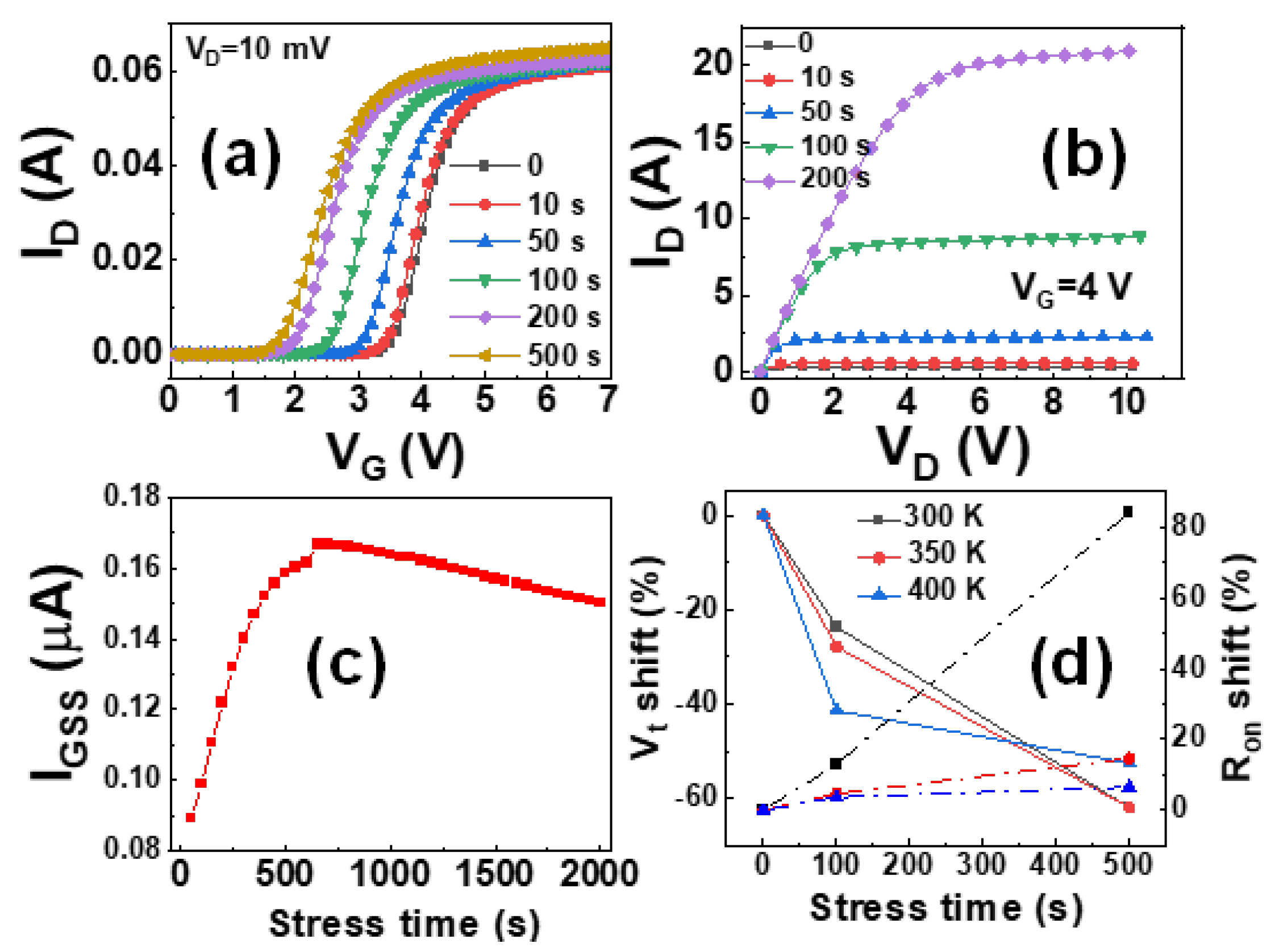

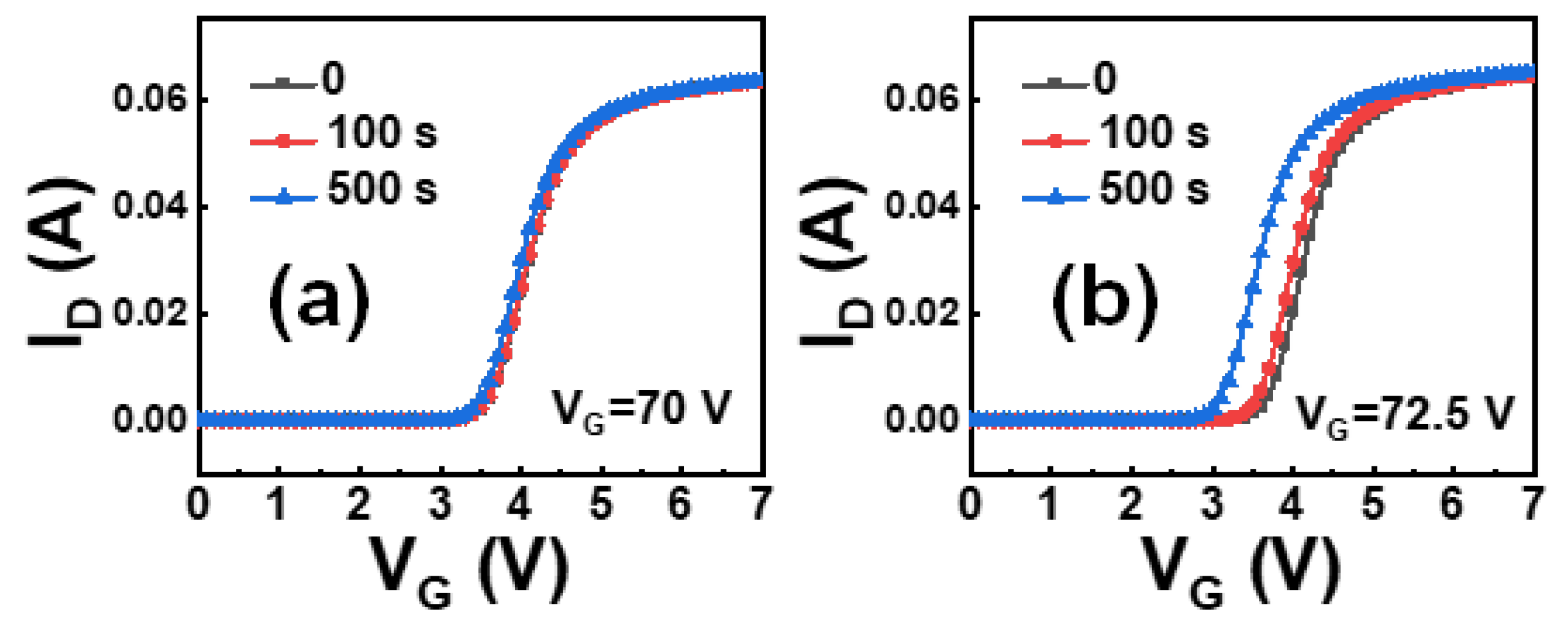

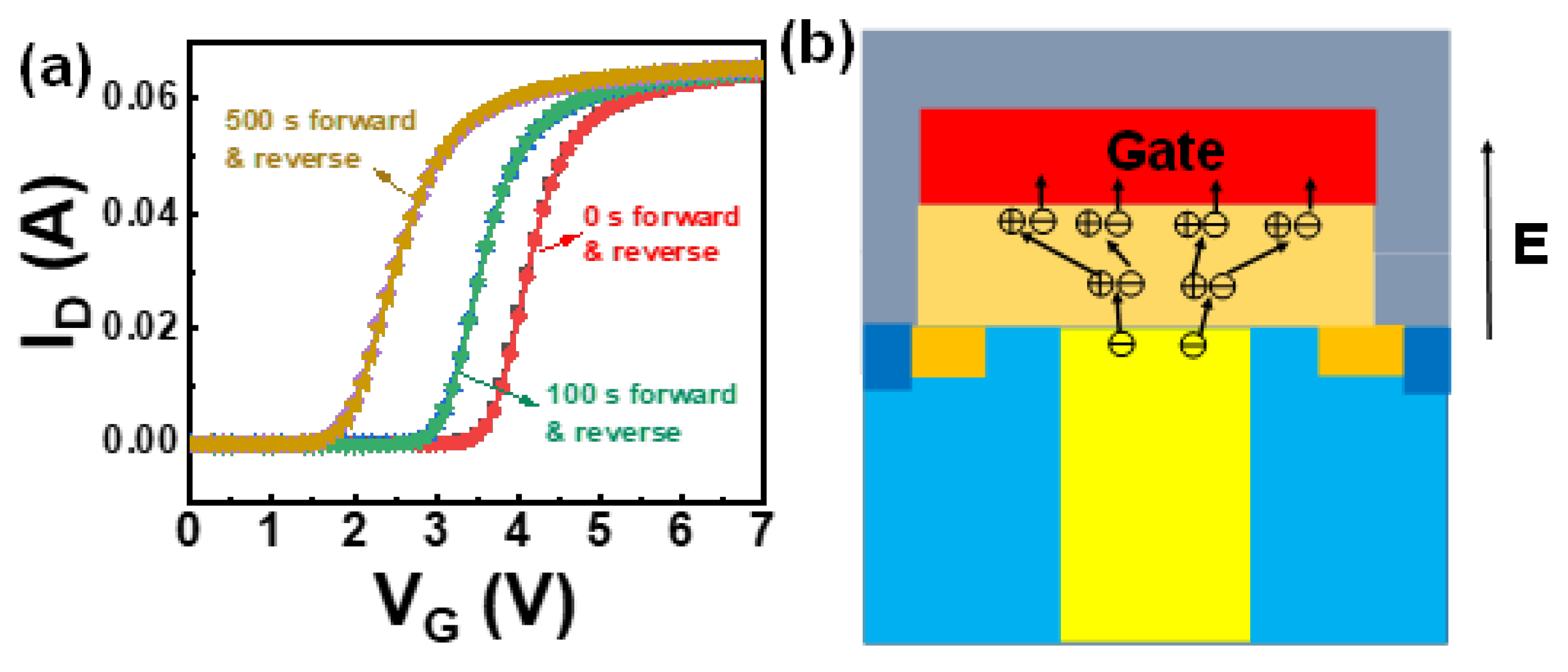

2.2. Measurement Results and Analysis

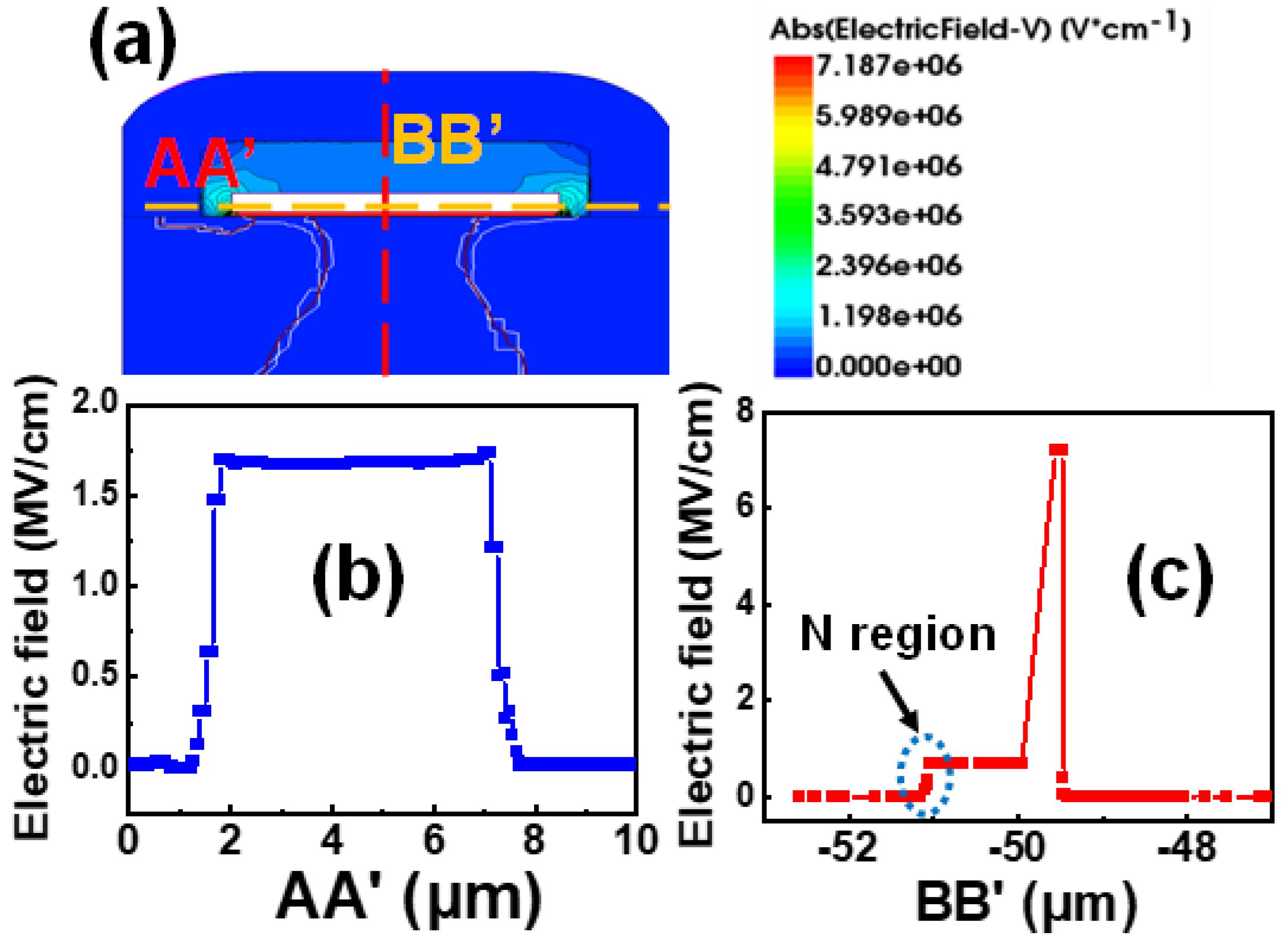

2.3. Mechanism Explanation

3. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Kobayashi, T.; Abe, H.; Niimura, Y.; Yamada, T.; Kurosaki, A.; Hosen, T.; Fujihira, T. High-voltage power MOSFETs reached almost to the silicon limit. In Proceedings of the 13th International Symposium on Power Semiconductor Devices & ICs. IPSD’01, Osaka, Japan, 4–7 June 2001. [Google Scholar] [CrossRef]

- Lorenz, L.; Deboy, G.; Knapp, A.; Marz, M. COOLMOS/sup TM/-a new milestone in high voltage power MOS. In Proceedings of the 11th International Symposium on Power Semiconductor Devices and ICs, Toronto, ON, Canada, 26–28 May 1999; pp. 3–10. [Google Scholar] [CrossRef]

- Saito, W.; Omura, I.; Aida, S.; Koduki, S.; Izumisawa, M.; Ogura, T. Semisuperjunction MOSFETs: New design concept for lower on-resistance and softer reverse-recovery body diode. IEEE Trans. Electron Devices 2003, 50, 1801–1806. [Google Scholar] [CrossRef]

- Cheng, B.; Brown, A.R.; Asenov, A. Impact of NBTI/PBTI on SRAM Stability Degradation. IEEE Electron Device Lett. 2011, 32, 740–742. [Google Scholar] [CrossRef]

- Denais, M.; Huard, V.; Parthasarathy, C.; Ribes, G.; Perrier, F.; Revil, N.; Bravaix, A. Interface Trap Generation and Hole Trapping Under NBTI and PBTI in Advanced CMOS Technology With a 2-nm Gate Oxide. IEEE Trans. Device Mater. Reliab. 2004, 4, 715–722. [Google Scholar] [CrossRef]

- Zafar, S.; Kim, Y.; Narayanan, V.; Cabral, C.; Paruchuri, V.; Doris, B.; Stathis, J.; Callegari, A.; Chudzik, M. A Comparative Study of NBTI and PBTI (Charge Trapping) in SiO2/HfO2 Stacks with FUSI, TiN, Re Gates. In Proceedings of the 2006 Symposium on VLSI Technology, Honolulu, HI, USA, 13–15 June 2006. [Google Scholar] [CrossRef]

- Cartier, E.; Frank, M.M.; Ando, T.; Rozen, J.; Narayanan, V. PBTI in InGaAs MOS capacitors with Al2O3/HfO2/TiN gate stacks: Interface-state generation. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018; pp. 5A.4-1–5A.4-4. [Google Scholar] [CrossRef]

- Rauch, S.E. Review and Reexamination of Reliability Effects Related to NBTI-Induced Statistical Variations. IEEE Trans. Device Mater. Reliab. 2007, 7, 524–530. [Google Scholar] [CrossRef]

- Zhang, J.; Eccleston, W. Positive bias temperature instability in MOSFETs. IEEE Trans. Electron Devices 1998, 45, 116–124. [Google Scholar] [CrossRef]

- Cartier, E.; Linder, B.P.; Narayanan, V.; Paruchuri, V.K. Fundamental understanding and optimization of PBTI in nFETs with SiO2/HfO2 gate stack. In Proceedings of the 2006 International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 2006; pp. 1–4. [Google Scholar] [CrossRef]

- Cartier, E.; Kerber, A. Stress-induced leakage current and defect generation in nFETs with HfO2/TiN gate stacks during positive-bias temperature stress. In Proceedings of the IEEE International Reliability Physics Symposium, Montreal, QC, Canada, 26–30 April 2009; pp. 486–492. [Google Scholar]

- Zhao, K.; Stathis, J.; Linder, B.P.; Cartier, E.; Kerber, A. PBTI under dynamic stress: From a single defect point of view. In Proceedings of the 2011 International Reliability Physics Symposium, Monterey, CA, USA, 10–14 April 2011; pp. 4A.3.1–4A.3.9. [Google Scholar] [CrossRef]

- Alwan, M.; Beydoun, B.; Ketata, K.; Zoaeter, M. Bias temperature instability from gate charge characteristics investigations in n-channel power MOSFET. Microelectron. J. 2007, 38, 727–734. [Google Scholar] [CrossRef]

- Alwan, M.; Beydoun, B.; Ketata, K.; Zoaeter, M. Gate charge behaviors in N-channel power VDMOSFETs during HEF and PBT stresses. Microelectron. Reliab. 2007, 47, 1406–1410. [Google Scholar] [CrossRef]

- Saito, W.; Omura, I.; Aida, S.; Koduki, S.; Izumisawa, M.; Yoshioka, H.; Okumura, H.; Yamaguchi, M.; Ogura, T. A 15.5m Ω cm2-680V Superjunction MOSFET Reduced On-Resistance by Lateral Pitch Narrowing. In Proceedings of the 2006 IEEE International Symposium on Power Semiconductor Devices and IC’s, Naples, Italy, 4–8 June 2006. [Google Scholar] [CrossRef]

- Moens, P.; Bogman, F.; Ziad, H.; De Vleeschouwer, H.; Baele, J.; Tack, M.; Loechelt, G.; Grivna, G.; Parsey, J.; Wu, Y.; et al. UltiMOS: A local charge-balanced trench-based 600V super-junction device. In Proceedings of the 2011 IEEE 23rd International Symposium on Power Semiconductor Devices and IC’s, San Diego, CA, USA, 23–26 May 2011; pp. 304–307. [Google Scholar] [CrossRef]

- Lee, S.C.; Oh, K.-H.; Kim, S.S.; Yun, C.M. 650V superjunction MOSFET using universal charge balance concept through drift region. In Proceedings of the 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Waikoloa, HI, USA, 15–19 June 2014; pp. 83–86. [Google Scholar] [CrossRef]

- Sugi, A.; Takei, M.; Takahashi, K.; Yajima, A.; Tomizawa, H.; Nakazawa, H. Super Junction MOSFETs above 600V with Parallel Gate Structure Fabricated by Deep Trench Etching and Epitaxial Growth. In Proceedings of the 2008 20th International Symposium on Power Semiconductor Devices and IC’s, Orlando, FL, USA, 18–22 May 2008; pp. 165–168. [Google Scholar] [CrossRef]

- Ono, S.; Saito, W.; Takashita, M.; Kurushima, S.; Tokano, K.; Yamaguchi, M. Design concept of n-buffer layer (n-Bottom Assist Layer) for 600V-class Semi-Super Junction MOSFET. In Proceedings of the 19th International Symposium on Power Semiconductor Devices and IC’s, Jeju, Korea, 27–30 May 2007; pp. 25–28. [Google Scholar] [CrossRef]

- Sentaurus™ Process User Guide, Version N-2017.09; Synopsys, Inc.: Mountain View, CA, USA, 2017.

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tang, H.; Xu, H.; Chen, L.; Zhu, H.; Sun, Q. Anomalous PBTI Effects in N-Type Super Junction under High Gate Voltage Stress. Electronics 2022, 11, 1362. https://doi.org/10.3390/electronics11091362

Tang H, Xu H, Chen L, Zhu H, Sun Q. Anomalous PBTI Effects in N-Type Super Junction under High Gate Voltage Stress. Electronics. 2022; 11(9):1362. https://doi.org/10.3390/electronics11091362

Chicago/Turabian StyleTang, Hua, Hang Xu, Lin Chen, Hao Zhu, and Qingqing Sun. 2022. "Anomalous PBTI Effects in N-Type Super Junction under High Gate Voltage Stress" Electronics 11, no. 9: 1362. https://doi.org/10.3390/electronics11091362

APA StyleTang, H., Xu, H., Chen, L., Zhu, H., & Sun, Q. (2022). Anomalous PBTI Effects in N-Type Super Junction under High Gate Voltage Stress. Electronics, 11(9), 1362. https://doi.org/10.3390/electronics11091362