Design and Verification of a Charge Pump in Local Oscillator for 5G Applications

Abstract

1. Introduction

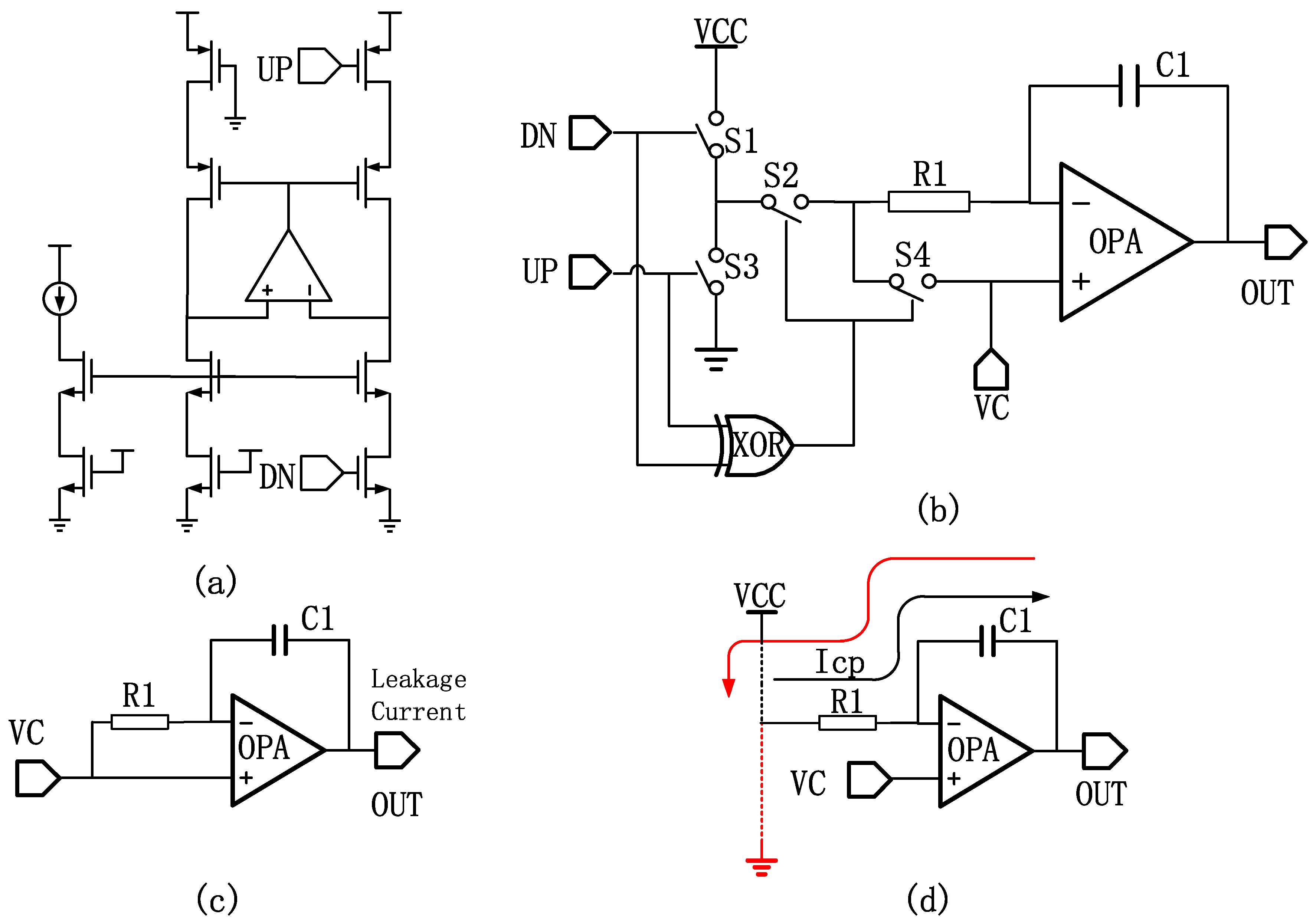

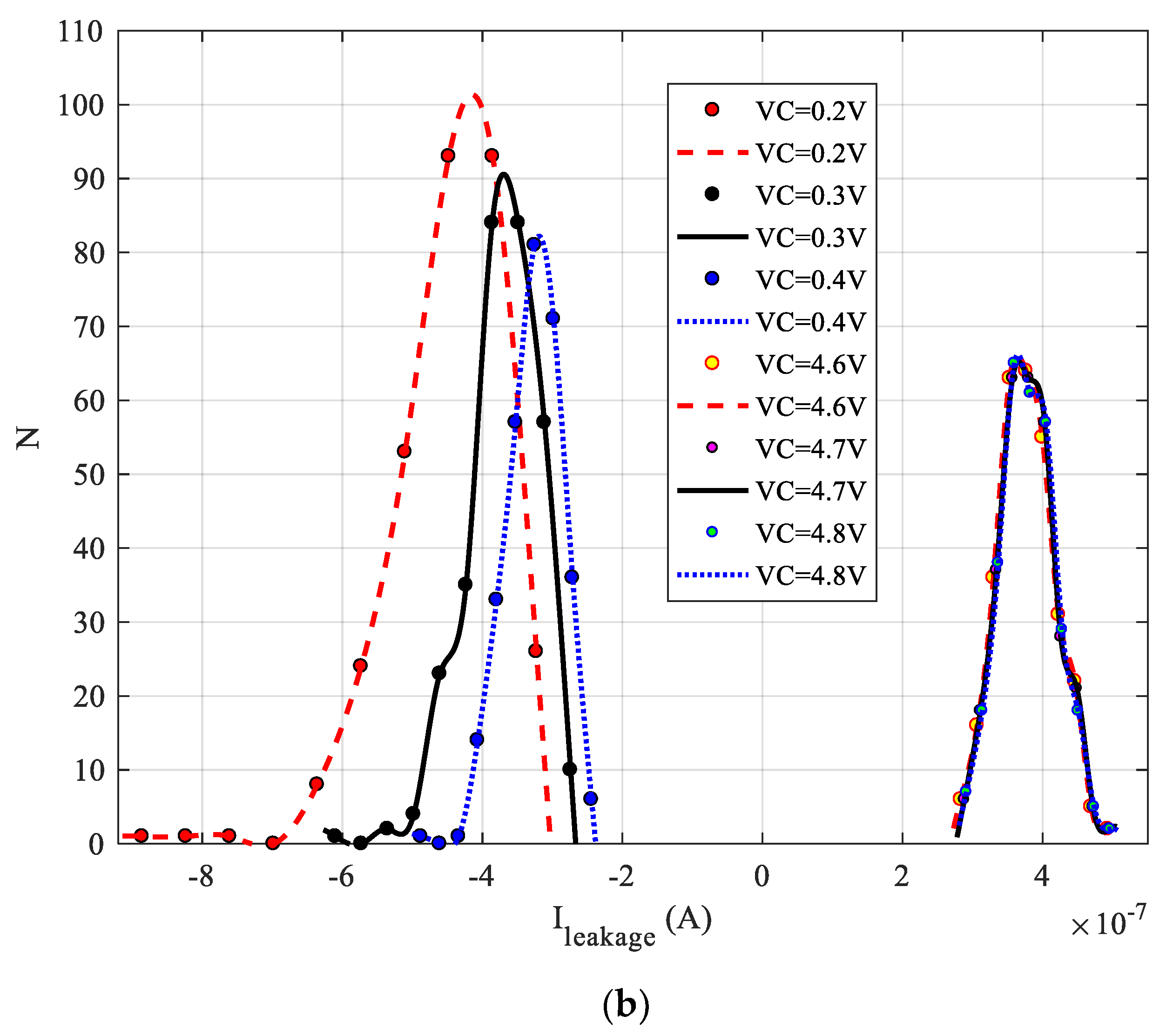

2. Design of Low Current Mismatch Charge Pump with Broad Voltage Headroom

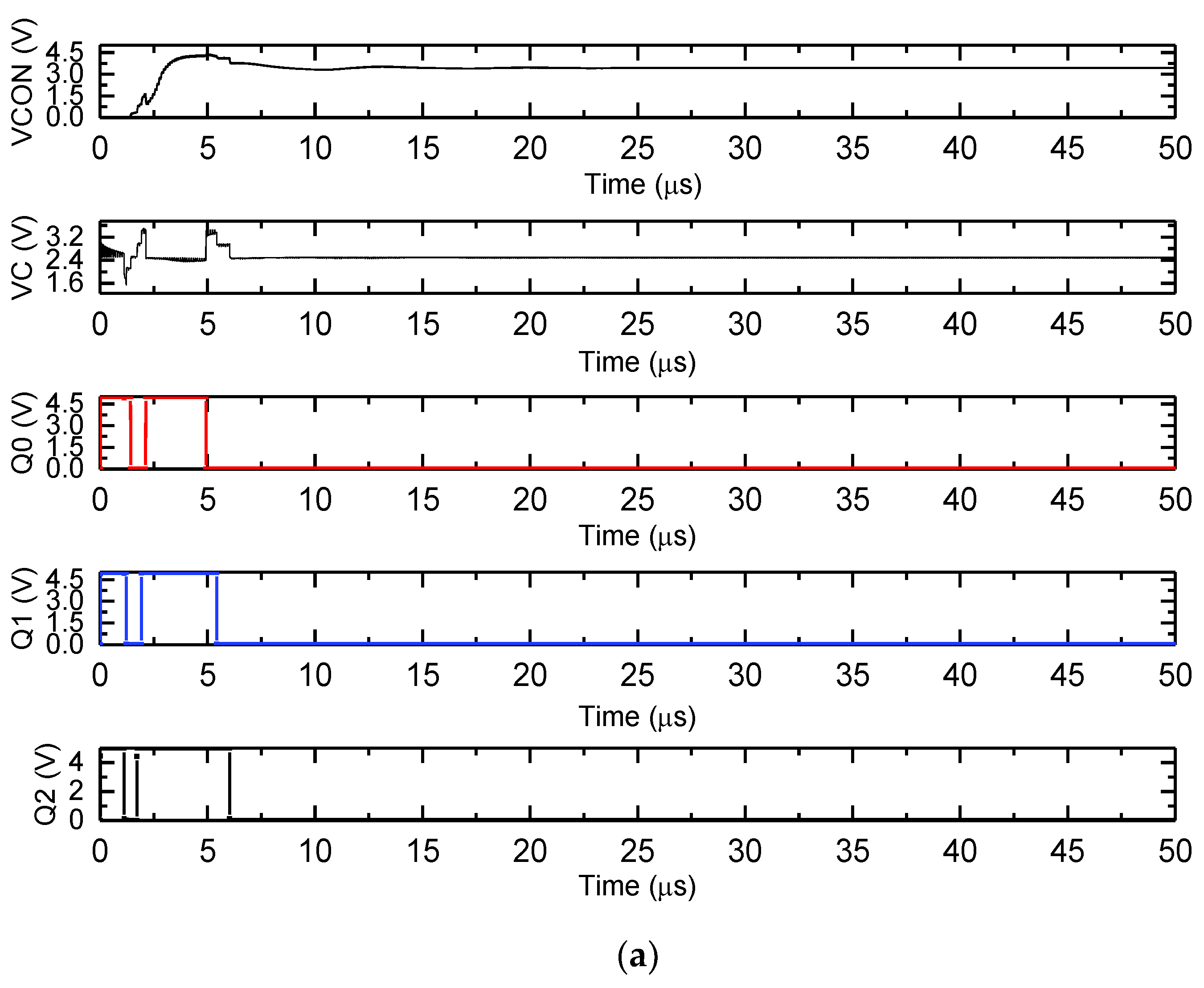

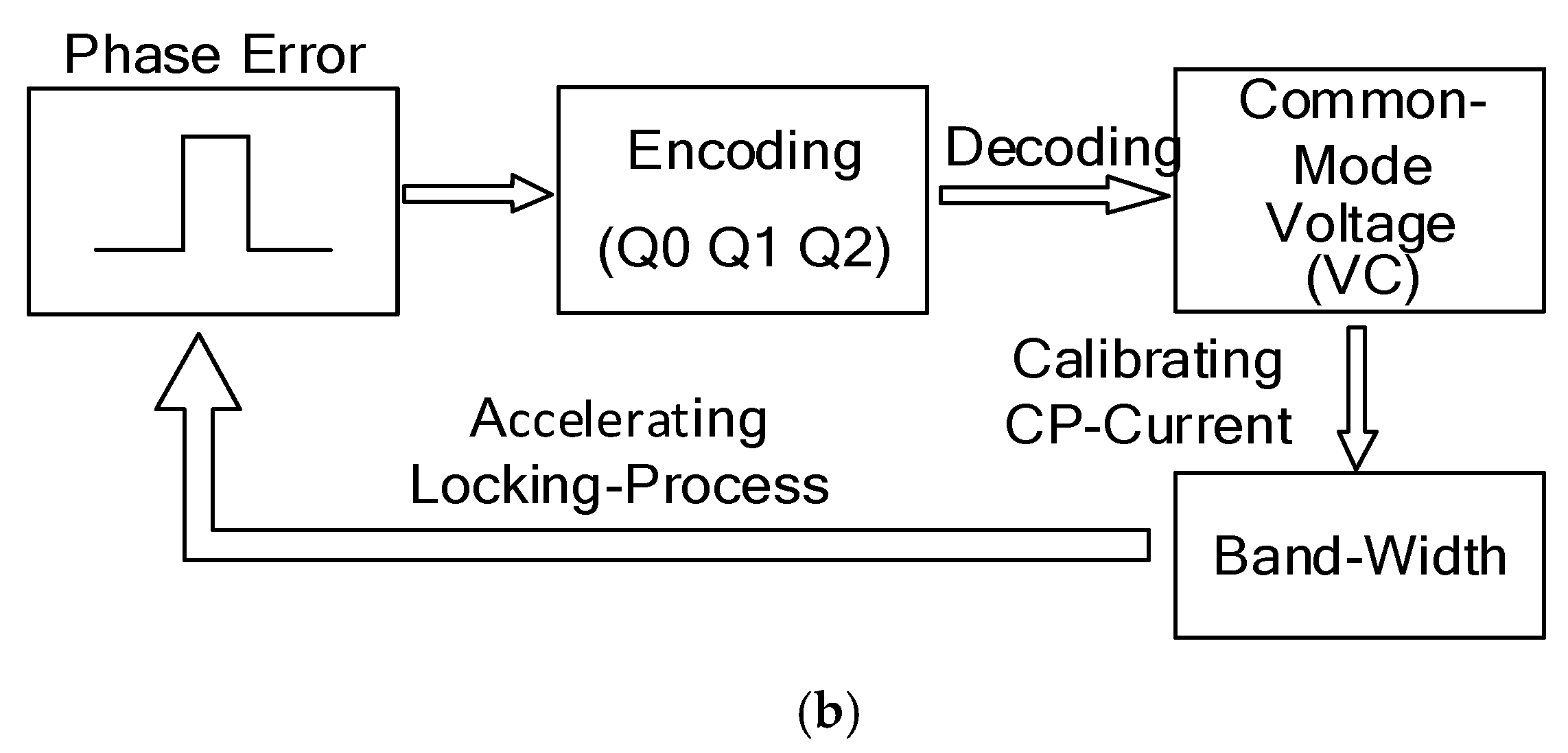

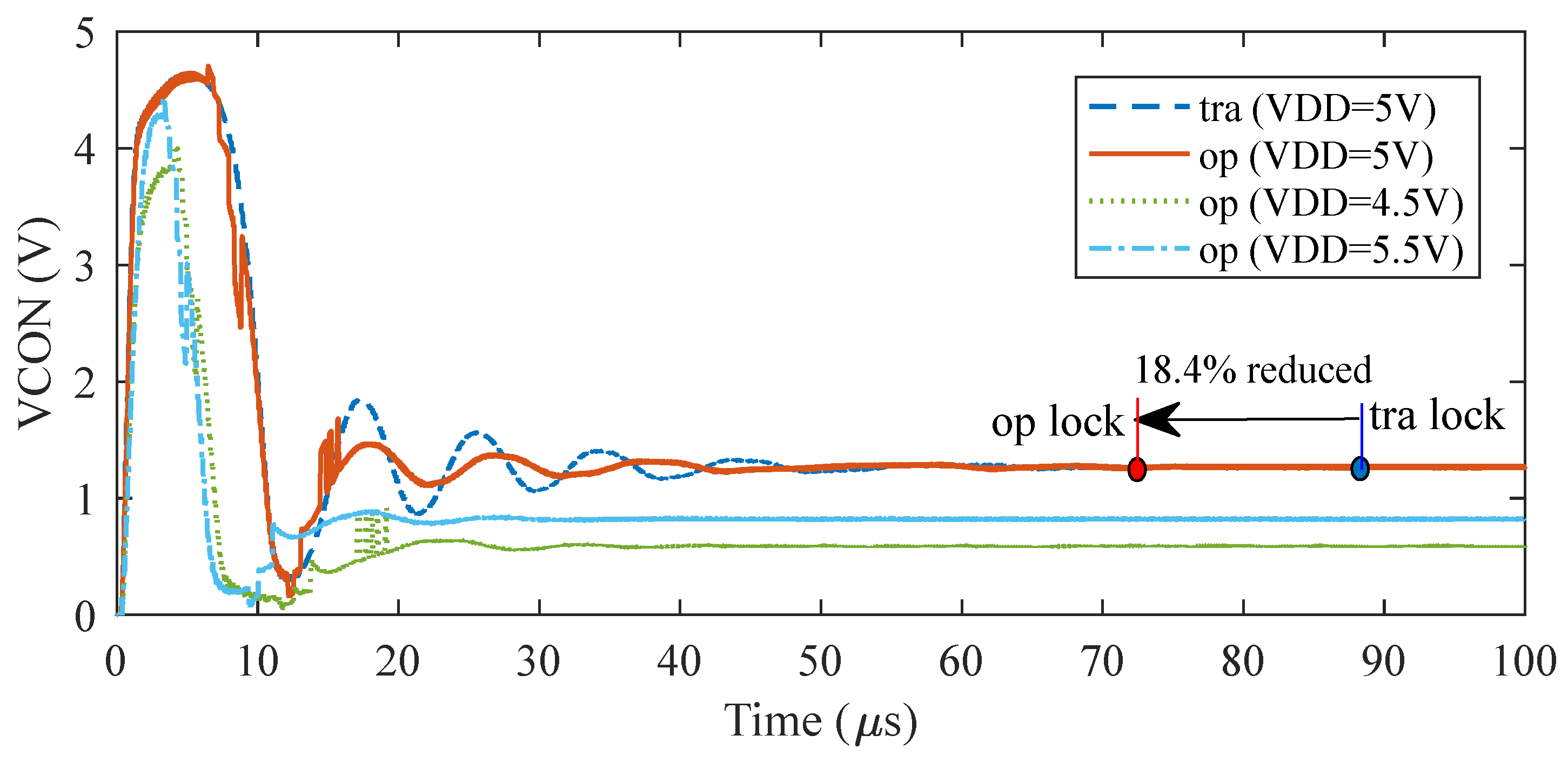

3. Design of Simplified Charge Pump for Fast Locking PLL

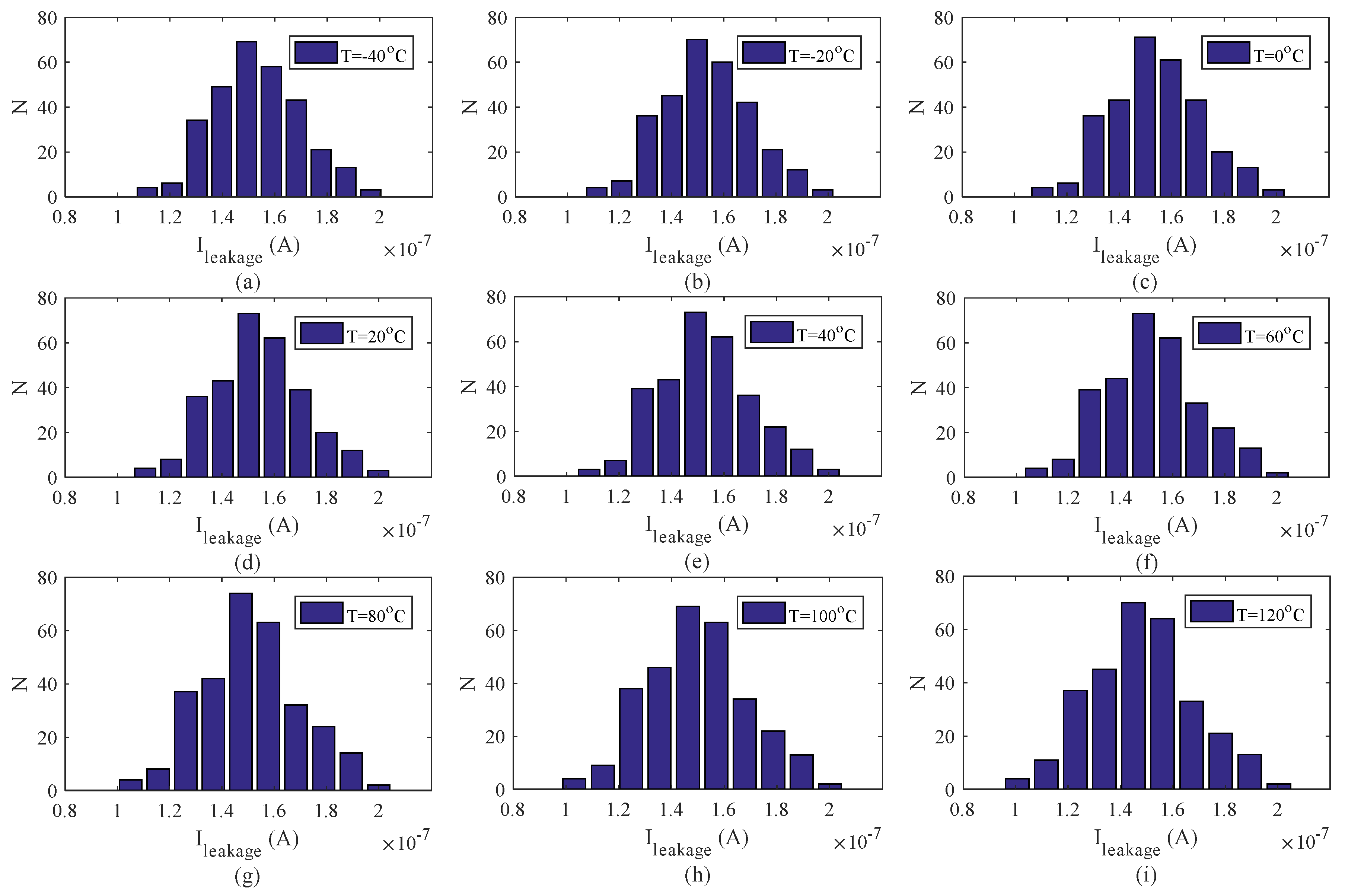

4. Simulation and Experimental Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Han, F.; Gao, J.; Li, X.; Chen, Z. A Four-Channel CMOS Front-End for Interference-Robust GNSS Receiver. Electronics 2020, 9, 291. [Google Scholar] [CrossRef]

- Sánchez-Azqueta, C.; Guerrero, E.; Gimeno, C.; Celma, S. A Reconfigurable Radio-Frequency Converter IC in 0.18 µm CMOS. Electronics 2019, 8, 1146. [Google Scholar] [CrossRef]

- Ali, E.; Hangmann, C.; Hedayat, C.; Haddad, F.; Rahajandraibe, W.; Hilleringmann, U. Event driven modeling and characterization of the second order voltage switched charge pump pll. IEEE Trans. Circuits Syst. I: Regul. Pap. 2016, 63, 347–358. [Google Scholar] [CrossRef]

- Kim, K.; Yoo, C. A fREF/5 bandwidth type-ii chargepump phase-locked loop with dual-edge phase comparison and sampling loop filter. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 825–827. [Google Scholar] [CrossRef]

- Homayoun, A.; Razavi, B. On the stability of chargepump phase-locked loops. IEEE Trans. Circuits Syst. I: Regul. Pap. 2016, 63, 741–750. [Google Scholar] [CrossRef]

- Choi, Y.S.; Han, D.H. Gain-boosting charge pump for current matching in phase-locked loop. IEEE Trans. Circuits Syst. II: Express Briefs 2006, 53, 1022–1025. [Google Scholar] [CrossRef]

- Lin, W.M.; Liu, S.I.; Kuo, C.H.; Li, C.H.; Hsieh, Y.J.; Liu, C.T. Aphase-locked loop with self-calibrated charge pumps in 3-m ltps-tft technology. IEEE Trans. Circuits Syst. II: Express Briefs 2009, 56, 142–146. [Google Scholar]

- Chen, Y.; Mak, P.I.; Zhou, Y. Self-tracking charge pump for fast-locking pll. Electron. Lett. 2010, 46, 755–757. [Google Scholar] [CrossRef]

- Yang, C.Y.; Liu, S.I. Fast-switching frequency synthesizer with a discriminator-aided phase detector. IEEE J. Solid-State Circuits 2000, 35, 1445–1452. [Google Scholar] [CrossRef]

- Chiu, W.H.; Huang, Y.H.; Lin, T.H. A dynamic phase error compensation technique for fast-locking phase-locked loops. IEEE J. Solid-State Circuits 2010, 45, 1137–1149. [Google Scholar] [CrossRef]

- Yao, C.W.; Ni, R.; Lau, C.; Wu, W.; Godbole, K.; Zuo, Y.; Ko, S.; Kim, N.-S.; Han, S.; Jo, I.; et al. A 14-nm 0.14-ps rms fractional-n digital pll with a 0.2-ps resolution adcassisted coarse/fine-conversion chopping tdc and tdc nonlinearity calibration. IEEE J. Solid-State Circuits 2017, 52, 3446–3457. [Google Scholar] [CrossRef]

- Wu, Y.; Shahmohammadi, M.; Chen, Y.; Lu, P.; Staszewski, R.B. A 3.5–6.8-ghz wide-bandwidth dtc-assisted fractional-n all-digital pll with a mash -tdc for low inband phase noise. IEEE J. Solid-State Circuits 2017, 52, 1885–1903. [Google Scholar] [CrossRef]

- Lee, M.; Kim, S.; Park, H.J.; Sim, J.Y. A 0.0043-mm 2 0.3–1.2-v frequency-scalable synthesized fractional-n digital pll with a speculative dual-referenced interpolating tdc. IEEE J. Solid-State Circuits 2018, 54, 99–108. [Google Scholar] [CrossRef]

- Liu, P.; Sun, P.; Jung, J.; Heo, D. Pll charge pump with adaptive body-bias compensation for minimum current variation. Electron. Lett. 2012, 48, 16–18. [Google Scholar] [CrossRef]

- Hwang, M.S.; Kim, J.; Jeong, D.K. Reduction of pump current mismatch in charge-pump pll. Electron. Lett. 2009, 45, 135–136. [Google Scholar] [CrossRef]

- Jalalifar, M.; Byun, G.S. Near-threshold charge pump circuit using dual feedback loop. Electron. Lett. 2013, 49, 1436–1438. [Google Scholar] [CrossRef]

- Joram, N.; Wolf, R.; Ellinger, F. High swing pll charge pump with current mismatch reduction. Electron. Lett. 2014, 50, 661–663. [Google Scholar] [CrossRef]

| Items | [14] | [15] | [16] | [17] | This Work |

|---|---|---|---|---|---|

| Technology node (nm) | 180 | 130 | 130 | 180 | 250 |

| Current mismatch (%) | ≤0.9 | ≤1.7 | ≤1 | ≤2.1 | ≤1 |

| Output voltage range (V, %) | 0.2–1, 66.6 | 0.2–1, 66.6 | 0.1–0.48, 76 | 0.2–2.7, 83.3 | 0.4–4.6, 84 |

| Supply voltage (V) | 1.2 | 1.2 | 0.5 | 3 | 5 |

| compensation method | Body-bias compensation | Dual compensation circuits | Dual feedback loop | 3 Rail-to-rail OPs | Elimination of source and sink currents |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Guo, R.; Lu, Z.; Hu, S.; Yu, Q.; Rong, L.; Liu, Y. Design and Verification of a Charge Pump in Local Oscillator for 5G Applications. Electronics 2021, 10, 1009. https://doi.org/10.3390/electronics10091009

Guo R, Lu Z, Hu S, Yu Q, Rong L, Liu Y. Design and Verification of a Charge Pump in Local Oscillator for 5G Applications. Electronics. 2021; 10(9):1009. https://doi.org/10.3390/electronics10091009

Chicago/Turabian StyleGuo, Rui, Zhenghao Lu, Shaogang Hu, Qi Yu, Limei Rong, and Yang Liu. 2021. "Design and Verification of a Charge Pump in Local Oscillator for 5G Applications" Electronics 10, no. 9: 1009. https://doi.org/10.3390/electronics10091009

APA StyleGuo, R., Lu, Z., Hu, S., Yu, Q., Rong, L., & Liu, Y. (2021). Design and Verification of a Charge Pump in Local Oscillator for 5G Applications. Electronics, 10(9), 1009. https://doi.org/10.3390/electronics10091009