Wideband Reconfigurable Integrated Low-Pass Filter for 5G Compatible Software Defined Radio Solutions

Abstract

1. Introduction

1.1. Background

1.2. Motivation

1.3. Related Work

2. Design of Low-Pass Filter

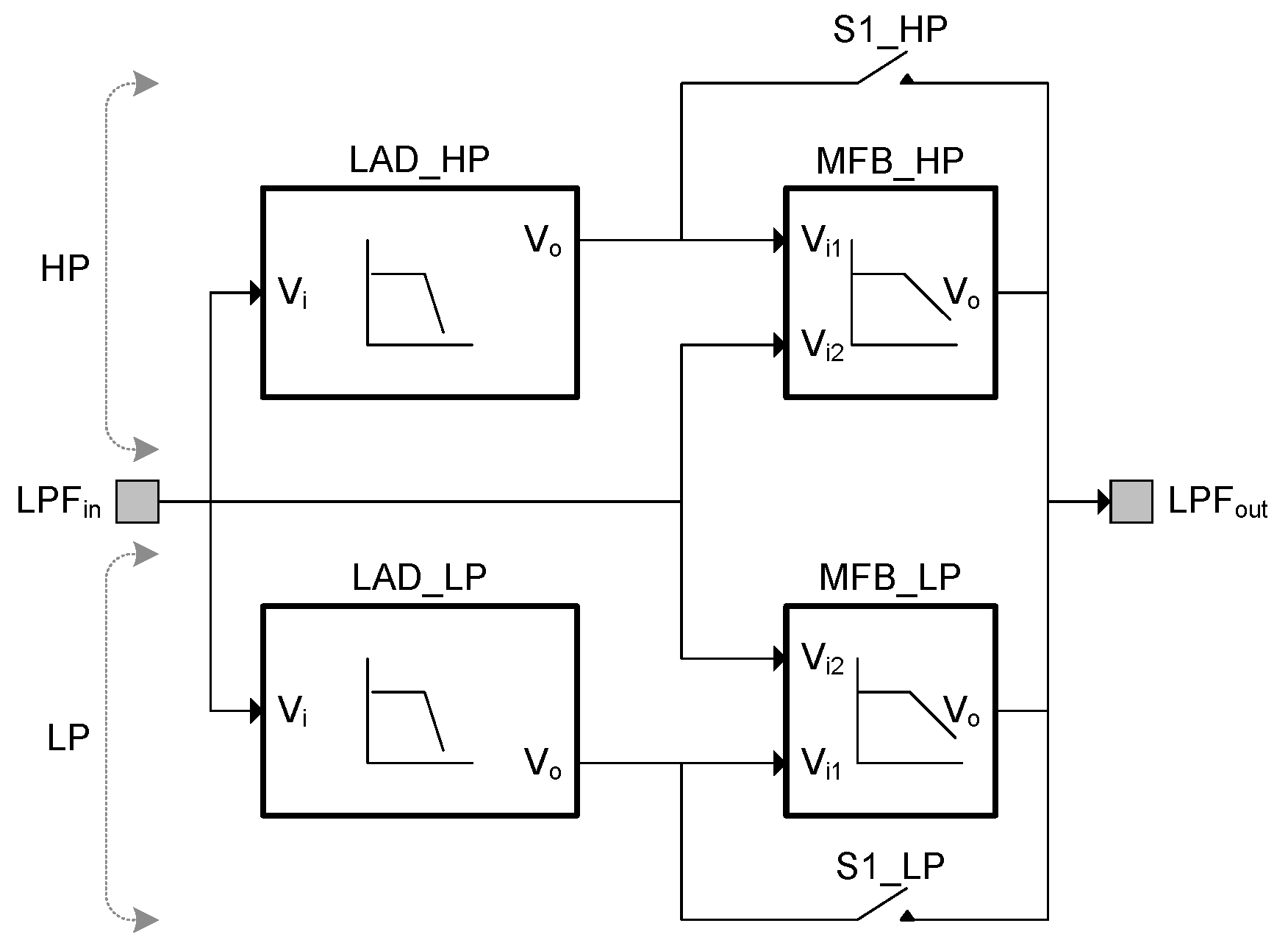

2.1. Reconfigurable Structure of the Filter

- Optimization of the active stage. This feature allows optimizing layout size and power dissipation for each path, since size and current consumption of the LP active stage can be scaled in respect to HP, while maintaining same performance.

- Compensation of each stage over the entire tuning range for each path can be optimized for large signal response.

- Count of passive elements of the tuning banks in the LPF can be distributed in both paths, which reduces the size of the bandwidth control step over the entire LPF tuning range for the same bit count of the control word. Hence, size of the control step can be reduced without adding additional parasitic capacitance due to a large number of switching elements.

- If the design requires, LP and HP can be split into two separate and independently controlled LPFs that can work with narrow and wide bandwidths simultaneously, for example in 5G NR NSA implementation.

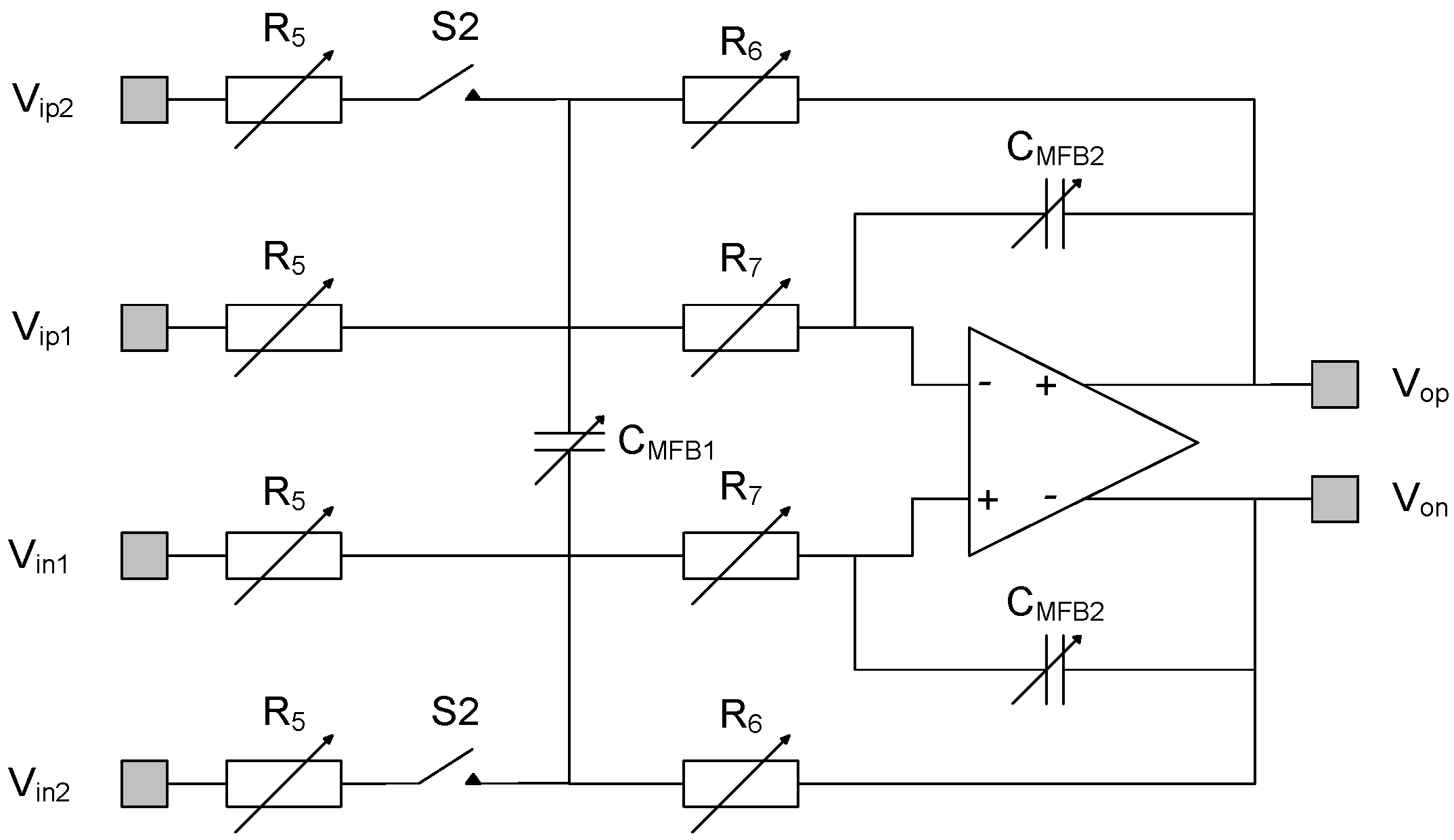

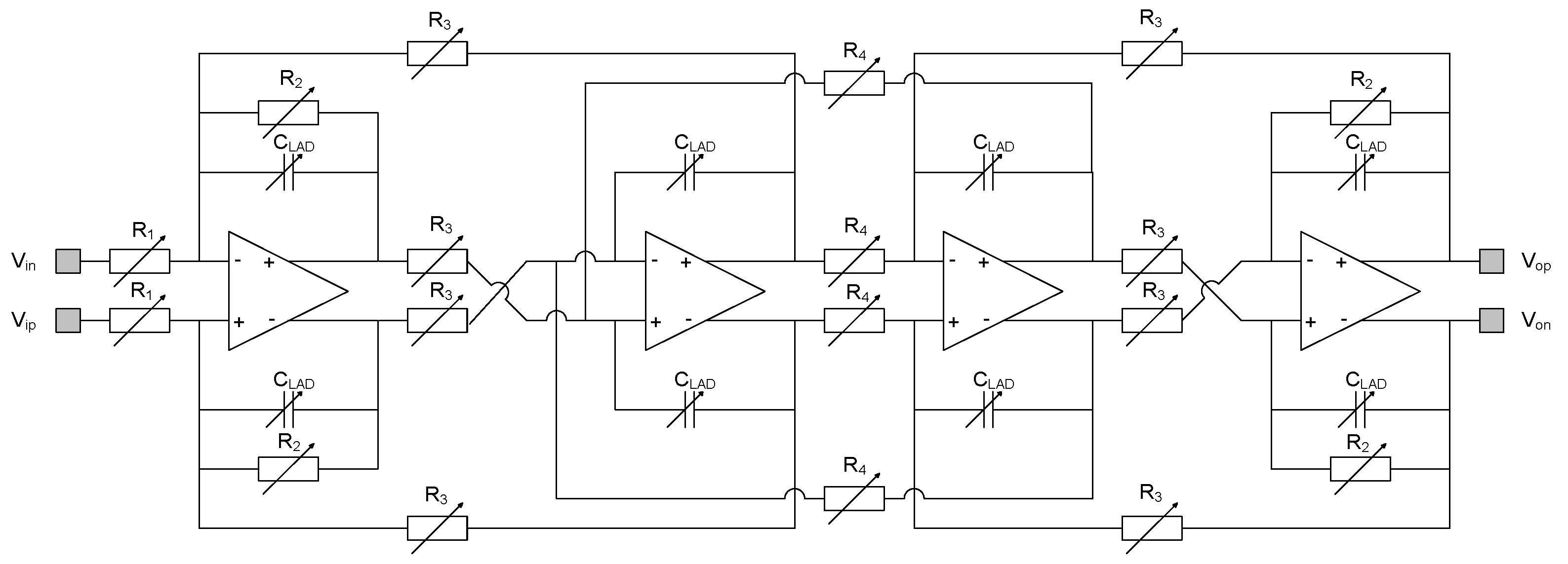

Design of the Filter Stages

2.2. Calibration and Bandwidth Tuning

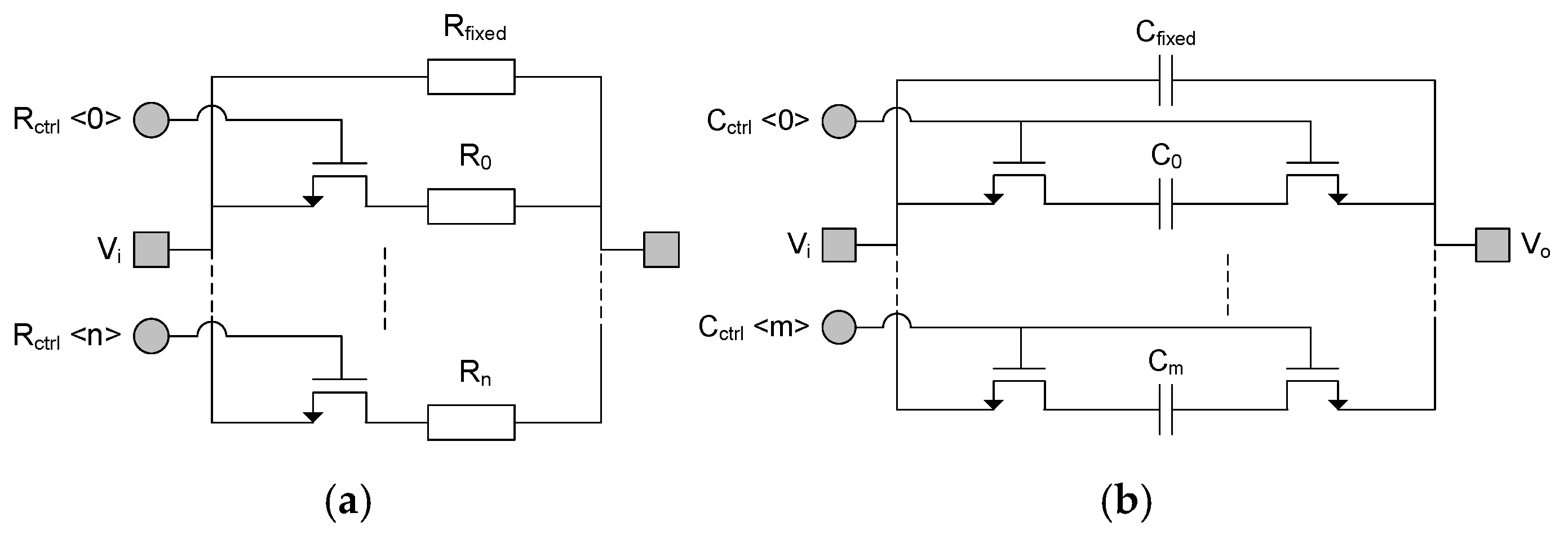

2.2.1. PVT Compensation

2.2.2. Bandwidth Tuning

2.2.3. Calibration

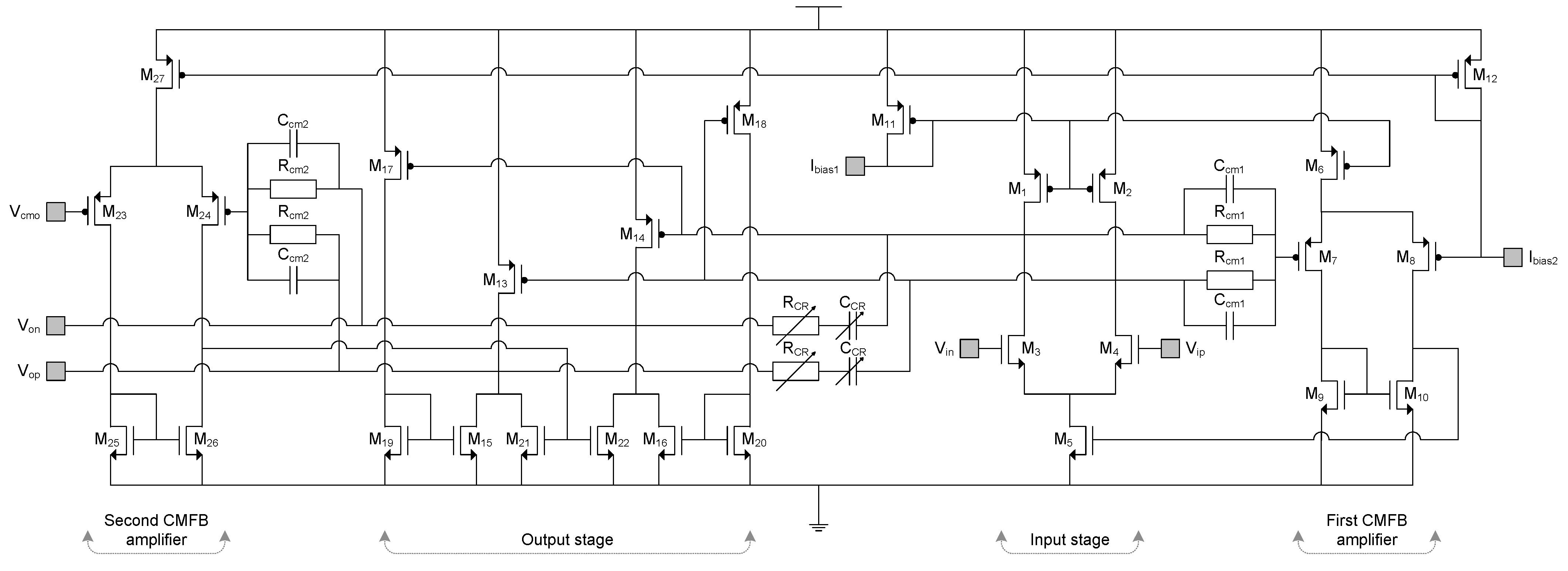

2.3. Operational Amplifier

3. Post-Layout Simulation Results

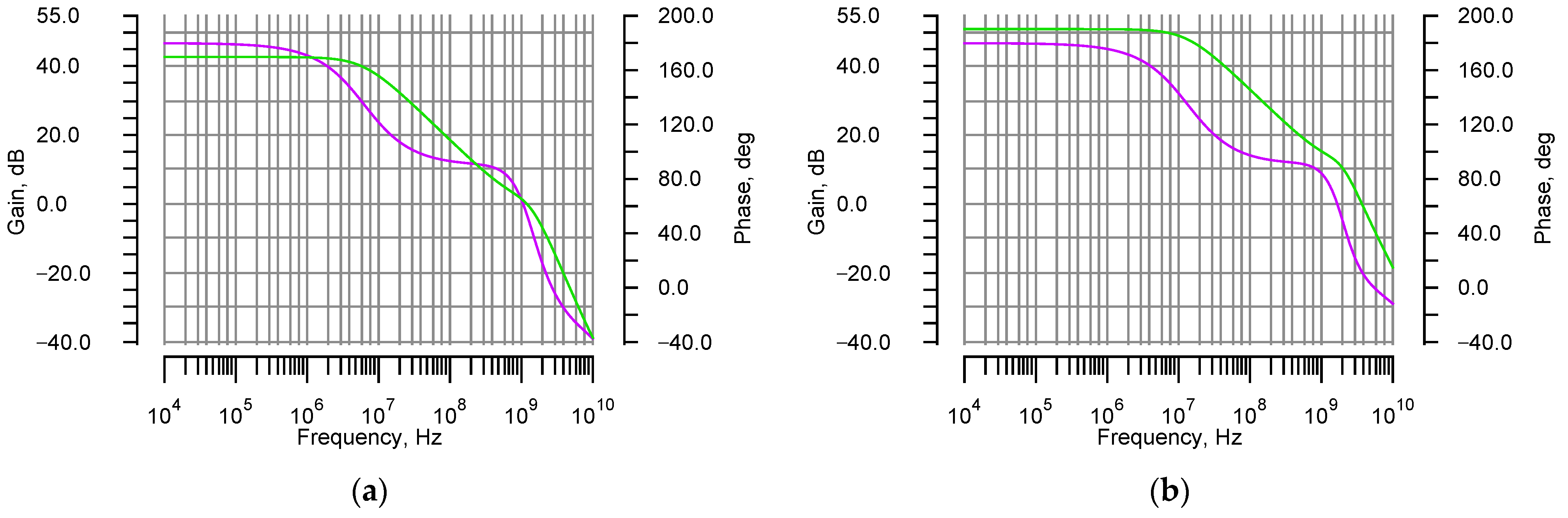

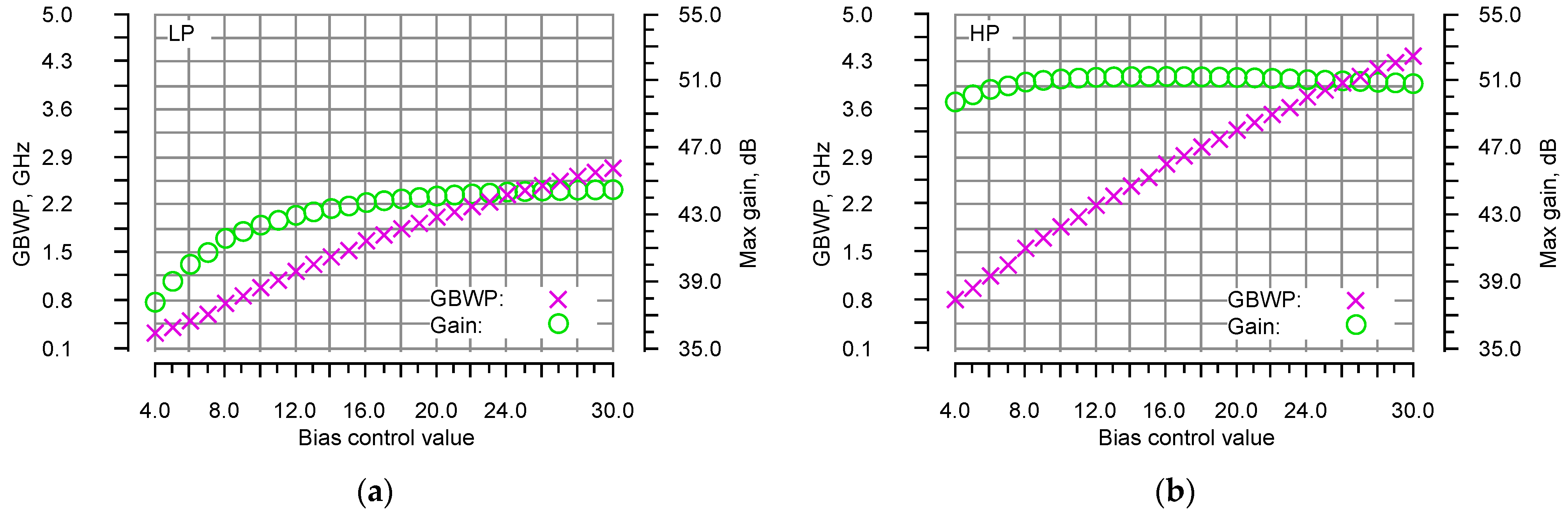

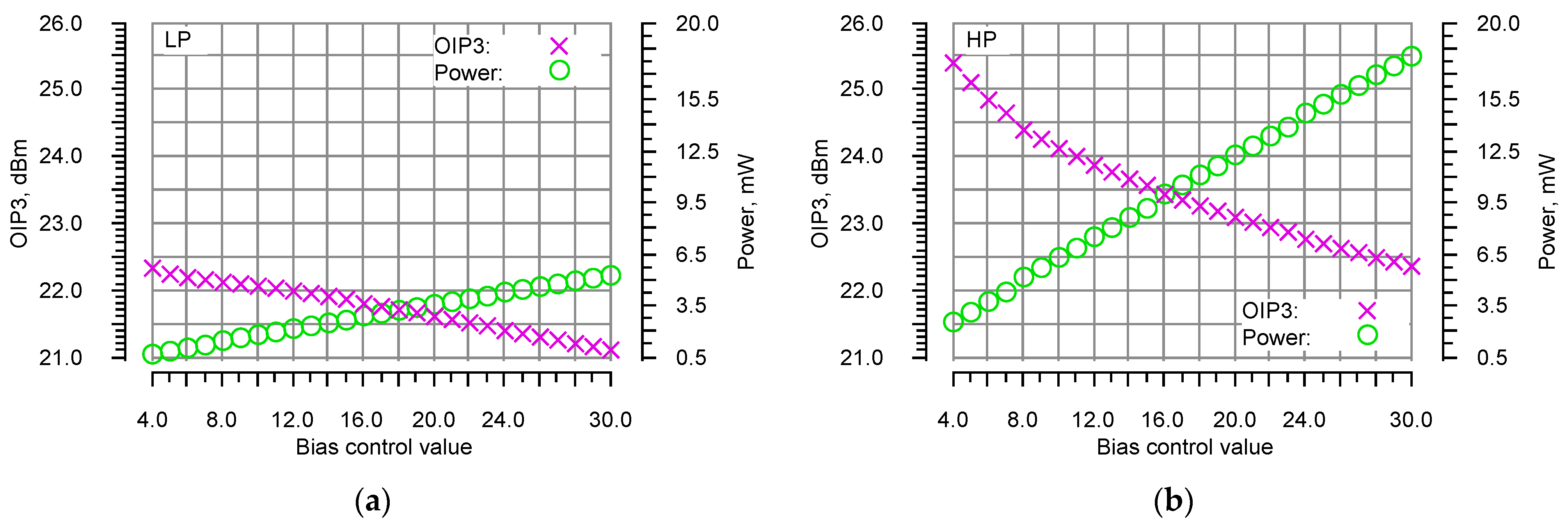

3.1. Operational Amplifier

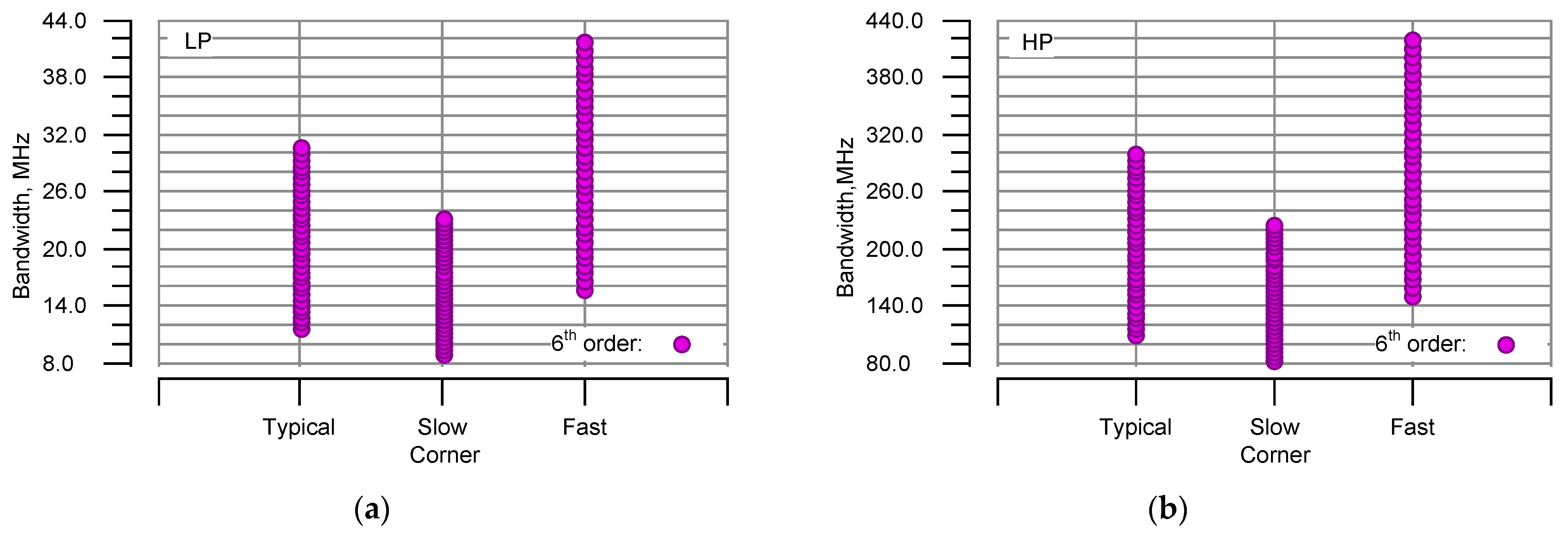

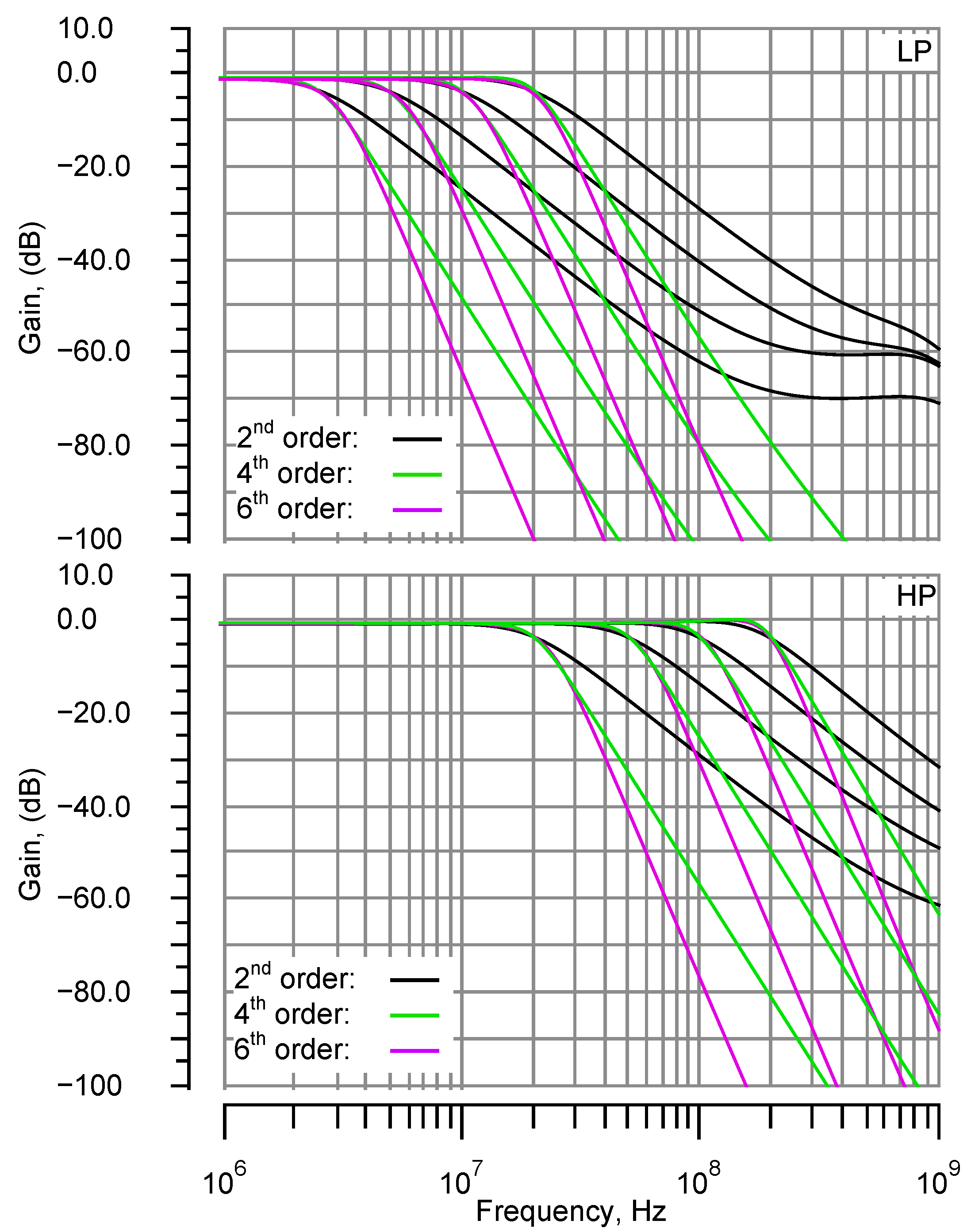

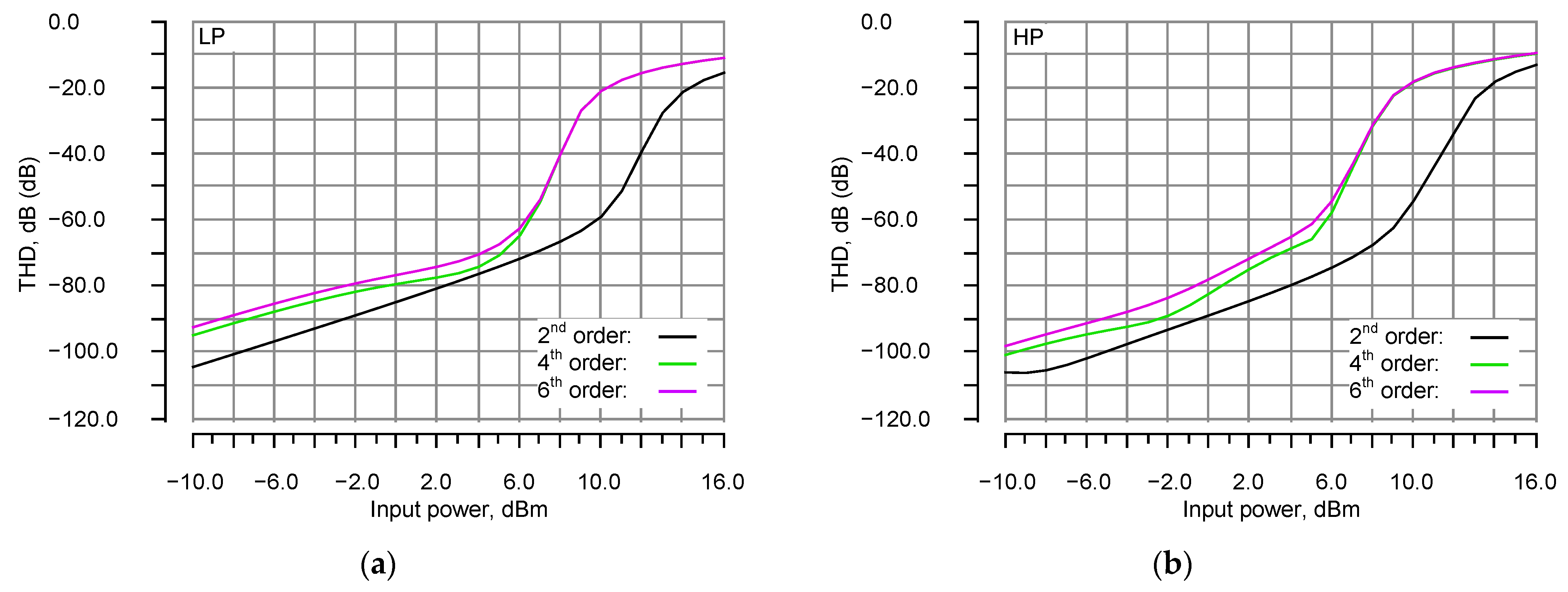

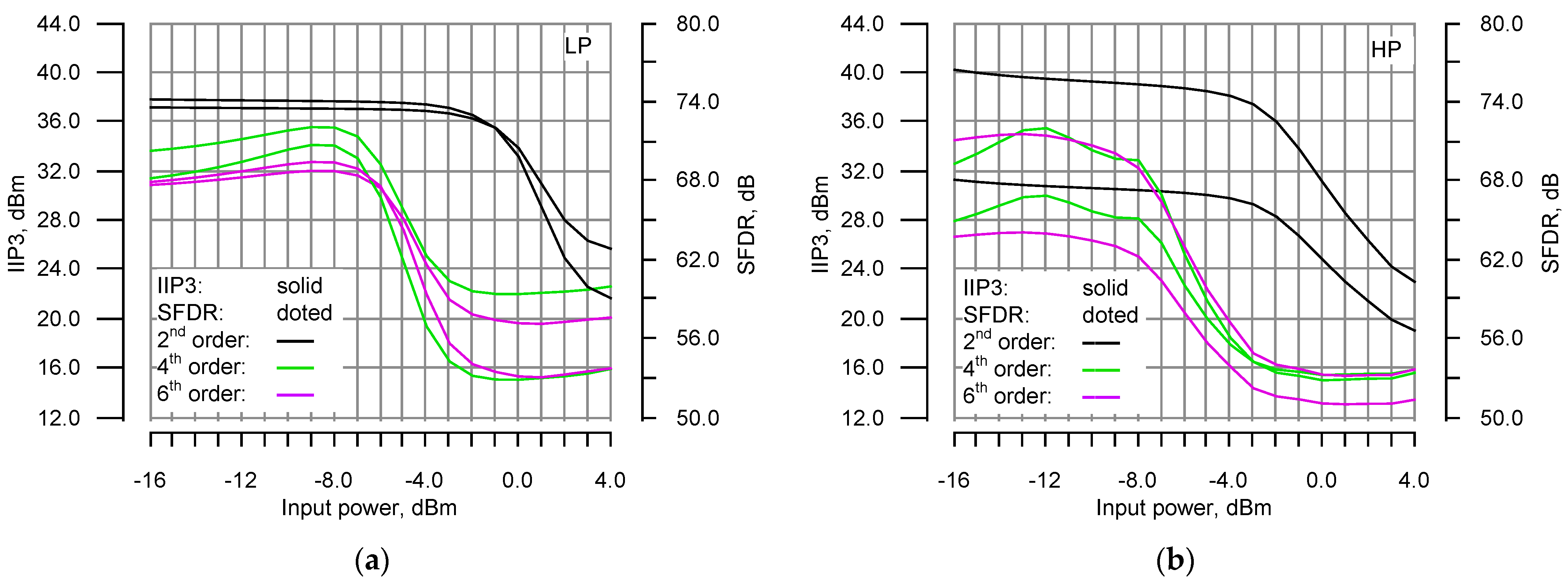

3.2. Low-Pass Filter

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Selva, A.F.B.; Reis, A.L.G.; Lenzi, K.G.; Meloni, L.G.P.; Barbin, S.E. Introduction to the software-defined radio approach. IEEE Latin Am. Trans. 2012, 10, 1156–1161. [Google Scholar]

- Seth, S.; Kwon, D.H.; Venugopalan, S.; Son, S.W.; Zuo, Y.; Bhagavatula, V.; Lim, J.; Oh, D.; Cho, T.B. A Dynamically Biased Multiband 2G/3G/4G Cellular Transmitter in 28 nm CMOS. IEEE J. Solid-State Circuits 2016, 51. [Google Scholar] [CrossRef]

- Savić, M.; Božić, M.; Bukvić, B.; Grujić, D.N.; Tamosevicius, Z.; Kiela, K.; Back, A. 5G CrowdCell with mm-Wave SDR Based Backhaul. In Lecture Notes of the Institute for Computer Sciences, Social-Informatics and Telecommunications Engineering, LNICST; Springer: Cham, Switzerland, 2019; Volume 291. [Google Scholar]

- Kiela, K.; Barzdenas, V.; Jurgo, M.; Macaitis, V.; Rafanavicius, J.; Vasjanov, A.; Kladovscikov, L.; Navickas, R. Review of V2X-IoT standards and frameworks for ITS applications. Appl. Sci. 2020, 10, 4314. [Google Scholar] [CrossRef]

- Ishihara, N.; Amakawa, S.; Masu, K. RF CMOS integrated circuit: History, current status and future prospects. IEICE Trans. Fundam. Electron. Commun. Comput. Sci. 2011, 94, 556–567. [Google Scholar] [CrossRef]

- Xu, Z.; Zhou, J.; Yu, Z.; Huang, W.; Ni, Y.; Huang, F.; Chu, Y. Design of high performance RF transceiver for next generation wireless communications. In Proceedings of the 2012 International Conference on Microwave and Millimeter Wave Technology, ICMMT 2012, Shenzhen, China, 5–8 May 2012; Volume 1. [Google Scholar]

- Chakraborty, S.; Parikh, V.; Sankaran, S.; Motos, T.; Fikstvedt, O.; Marienborg, J.T.; Griffith, D.; Prathapan, I.; Nagaraj, K.; Zhang, F.; et al. An ultra low power, reconfigurable, multi-standard transceiver using fully digital PLL. In Proceedings of the IEEE Symposium on VLSI Circuits, Kyoto, Japan, 12–14 June 2013. [Google Scholar]

- Borremans, J.; Van Liempd, B.; Martens, E.; Cha, S.; Craninckx, J. A 0.9 V low-power 0.4–6 GHz linear SDR receiver in 28 nm CMOS. In Proceedings of the IEEE Symposium on VLSI Circuits, Kyoto, Japan, 12–14 June 2013. [Google Scholar]

- Kladovščikov, L.; Navickas, R.; Kiela, K. Self-tuning system for multistandard active RC filters. Microelectron. J. 2019, 90. [Google Scholar] [CrossRef]

- Han, D.O.; Kim, J.H.; Lee, K.D.; Park, S.G.; Oh, S.M.; Kim, E.J. Fully integrated dual-band transceiver for IEEE 802.11a/b/g/j/n wireless local area network applications with hybrid up/down conversion architecture. IET Circuits Devices Syst. 2011, 5. [Google Scholar] [CrossRef]

- Huang, Y.; Li, W.; Hu, S.; Xie, R.; Li, X.; Fu, J.; Sun, Y.; Pan, Y.; Chen, H.; Jiang, C.; et al. A high-linearity WCDMA/GSM reconfigurable transceiver in 0.13-μm CMOS. IEEE Trans. Microw. Theory Tech. 2013, 61. [Google Scholar] [CrossRef]

- Al-Yasir, Y.I.A.; Parchin, N.O.; Abd-Alhameed, R.A.; Abdulkhaleq, A.M.; Noras, J.M. Recent progress in the design of 4G/5G reconfigurable filters. Electronics 2019, 8, 114. [Google Scholar] [CrossRef]

- Baschirotto, A.; D’Amico, S.; De Matteis, M. Advances on analog filters for telecommunications. In Proceedings of the Advanced Signal Processing, Circuits, and System Design Techniques for Communications—2006 IEEE International Symposium on Circuits and Systems, ISCAS 2006, Kos, Greece, 21–24 May 2006. [Google Scholar]

- Khattak, M.K.; Lee, C.; Park, H.; Kahng, S. RF channel-selectivity sensing by a small antenna of metamaterial channel filters for 5G sub-6-GHz bands. Sensors 2020, 20, 1989. [Google Scholar] [CrossRef] [PubMed]

- Chih-Lin, I.; Kuklinski, S.; Chen, T.C.; Ladid, L.L. A perspective of O-RAN integration with MEC, SON, and network slicing in the 5G era. IEEE Netw. 2020, 34, 3–4. [Google Scholar]

- NR, Base Station (BS) Radio Transmission and Reception (Release 17), Tech. Specification Group Radio Access Network (TSG RAN), 3GPP TR 38.104. 2021. Available online: https://www.3gpp.org/ftp//Specs/archive/38_series/38.104/38104-h00.zip (accessed on 29 January 2021).

- Evolved Universal Terrestrial Radio Access (E-UTRA). Base Station (BS) Radio Transmission and Reception (Release 17), Tech. Specification Group Radio Access Network (TSG RAN), 3GPP TS 36.104. 2021. Available online: https://www.3gpp.org/ftp//Specs/archive/36_series/36.104/36104-h00.zip (accessed on 29 January 2021).

- Wang, Y.; Ye, L.; Liao, H.; Huang, R.; Wang, Y. Highly Reconfigurable Analog Baseband for Multistandard Wireless Receivers in 65-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62. [Google Scholar] [CrossRef]

- Lavalle-Aviles, F.; Sanchez-Sinencio, E. A 0.6-V Power-Efficient Active-RC Analog Low-Pass Filter with Cutoff Frequency Selection. IEEE Trans. Very Large Scale Integr. Syst. 2020, 28. [Google Scholar] [CrossRef]

- Lee, I.Y.; Im, D.; Ko, J.; Lee, S.G. A 50-450 MHz Tunable RF Biquad Filter Based on a Wideband Source Follower With > 26 dBm IIP3, +12 dBm P1dB, and 15 dB Noise Figure. IEEE J. Solid-State Circuits 2015, 50. [Google Scholar] [CrossRef]

- Wu, W.; Mo, T.; Lu, Z. A 180 nm CMOS three stage feedforward compensation op-amp with linearity improvement technique for active RC LPF. In Proceedings of the 2016 10th IEEE International Conference on Anti-Counterfeiting, Security, and Identification (ASID), Xiamen, China, 23–25 September 2016. [Google Scholar]

- Wu, B.; Chiu, Y. A 40 nm CMOS derivative-free if Active-RC BPF with programmable bandwidth and center frequency achieving over 30 dBm IIP3. IEEE J. Solid-State Circuits 2015, 50. [Google Scholar] [CrossRef]

- D’Amico, S.; Baschirotto, A.; Philips, K.; Rousseaux, O.; Gyselinckx, B. A 240 MHz Programmable Gain Amplifier & filter for ultra low power low-rate UWB receivers. In Proceedings of the ESSCIRC 2009—35th European Solid-State Circuits Conference, Athens, Greece, 14–18 September 2009. [Google Scholar]

- Fary, F.; Mangiagalli, L.; Vallicelli, E.; De Matteis, M.; Baschirotto, A. A 28 nm bulk-CMOS 50 MHz 18 dBm-IIP3 Active-RC Analog Filter based on 7 GHz UGB OTA. In Proceedings of the ESSCIRC 2019—IEEE 45th European Solid State Circuits Conference, Cracow, Poland, 23–26 September 2019. [Google Scholar]

- Yen, M.Y.; Chen, H.C.; Wei, Y.L.; Chung, C.Y. A CMOS transmitter analog baseband for 5G mobile communication. Electronics 2019, 8, 1319. [Google Scholar] [CrossRef]

- Wang, H.F.; Hwang, C.P.; Chen, M.S. The Error Vector Magnitude (EVM) performance in LTE Downlink. In Proceedings of the 2019 Cross Strait Quad-Regional Radio Science and Wireless Technology Conference, CSQRWC 2019, Taiyuan, China, 18–21 July 2019. [Google Scholar]

- Aoki, Y.; Dao, M.T.; Min, K.; Hwang, Y.; Kim, Y.; Yang, S.G. 1.4-GHz Bandwidth Frequency-Dependent I/Q Imbalance Calibration for 5G mmWave Communications. In Proceedings of the IEEE MTT-S International Microwave Symposium, Boston, MA, USA, 2–7 June 2019. [Google Scholar]

- De Matteis, M.; Pipino, A.; Resta, F.; Pezzotta, A.; D’Amico, S.; Baschirotto, A. A 63-dB DR 22.5-MHz 21.5-dBm IIP3 Fourth-Order FLFB Analog Filter. IEEE J. Solid-State Circuits 2017, 52. [Google Scholar] [CrossRef]

| Path | Low Frequency Path (LP) | How Frequency Path (HP) | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Technology | 65 nm CMOS | |||||||||||

| Supply, V | 1.2 | |||||||||||

| Tuning ratio | 92.8 | |||||||||||

| 11.6 | 11.6 | |||||||||||

| Topology 1 | Active-RC | |||||||||||

| MFB | LAD | MFB + LAD | MFB | LAD | MFB + LAD | |||||||

| Type 2 | LPF-B | LPF-B | LPF-C-B | LPF-B | LPF-B | LPF-C-B | ||||||

| Order | 2nd | 4th | 6th | 2nd | 4th | 6th | ||||||

| Area, mm2 | 0.073 | 0.172 | 0.251 | 0.044 | 0.131 | 0.178 | ||||||

| Gain, dB | −0.55 | −0.57 | −0.84 | −0.48 | −0.26 | −0.39 | ||||||

| P1dB, dBm | 14.06 | 9.95 | 9.94 | 14.2 | 9.94 | 9.94 | ||||||

| Bandwidth, MHz | 2.5 | 20 | 2.5 | 20 | 2.5 | 20 | 20 | 200 | 20 | 200 | 20 | 200 |

| In-band IIP3, dBm 3 | 38.84 | 38.58 | 36.32 | 35.51 | 35.05 | 34.83 | 45.81 | 44.61 | 37.61 | 37.94 | 36.03 | 36.72 |

| 38.48 | 37.79 | 35.01 | 33.85 | 33.31 | 32.66 | 41.93 | 39.34 | 36.79 | 33.77 | 38.42 | 34.16 | |

| Out-band IIP3, dBm 4 | 38.94 | 36.98 | 28.19 | 24.32 | 25.66 | 22.17 | 35.72 | 37.37 | 32.57 | 20.66 | 30.21 | 16.06 |

| SFDR, dB 3 | 79.45 | 74.13 | 78.46 | 73.04 | 75.47 | 70.2 | 79.32 | 71.07 | 75.12 | 68.57 | 71.52 | 65.29 |

| 79.21 | 73.6 | 77.58 | 71.94 | 74.31 | 68.75 | 76.73 | 67.56 | 74.58 | 65.76 | 73.12 | 63.59 | |

| THD, dB 5 | −105 | −103.7 | −95.1 | −94.16 | −92.3 | −91.74 | −112.4 | −105.5 | −104.4 | −100.1 | −101.2 | −97.39 |

| −76.95 | −75.7 | −74.75 | −73.57 | −72.11 | −69.85 | −85.63 | −79.06 | −71.64 | −68.04 | −69.22 | −64.55 | |

| NF, dB | 29.65 | 28.34 | 28.62 | 26.9 | 31.83 | 30.48 | 27.78 | 28.95 | 25.87 | 26.05 | 29.7 | 29.74 |

| Intg. Noise, µVRMS 6 | 21.88 | 52.8 | 19.82 | 45.31 | 28.45 | 67.72 | 49.43 | 182.2 | 40.19 | 132.3 | 62.13 | 202.7 |

| Noise Floor, dBm | −80.35 | −72.63 | −78.17 | −70.48 | −78.17 | −70.48 | −73.19 | −62.02 | −75.08 | −64.92 | −71.26 | −61.23 |

| Dynamic range, dB 7 | 94.26 | 86.54 | 91.18 | 83.87 | 87.96 | 80.28 | 87.24 | 76.07 | 84.89 | 74.71 | 81.06 | 71.02 |

| 92.2 | 84.48 | 89.23 | 81.92 | 86.02 | 78.34 | 84.34 | 73.17 | 82.15 | 71.97 | 78.35 | 68.28 | |

| Dynamic range, dB-Hz 8 | 158.24 | 159.55 | 155.16 | 156.88 | 151.94 | 153.29 | 160.25 | 159.08 | 157.9 | 157.72 | 154.07 | 154.03 |

| Power, mW | 1.19 | 2.31 | 4.98 | 9.5 | 6.2 | 11.8 | 3.9 | 14.8 | 15.9 | 58.6 | 19.8 | 73.4 |

| [19] 3 | [24] 4 | [20] 5 | [28] 6 | This Work 7 | ||

|---|---|---|---|---|---|---|

| Process | 130 nm CMOS | 28 nm CMOS | 180 nm CMOS | 180 nm CMOS | 65 nm CMOS | |

| Supply, V | 0.6 | 1.1 | 1.8 | 1.8 | 1.2 | |

| Tuning ratio | 4 | N/A | 9 | N/A | 92.8 | |

| Topology 1 | A-RC | gm-C | A-RC | A-RC/A-gm-RC | A-RC | |

| C-BQ | - | SK-BQ | FLFB | MFB + LAD | ||

| Type 2 | LPF-B | LPF-B | LPF | LPF-B | LPF-C-B | |

| Order | 4th | 6th | 2 | 4 | 6th | |

| Bandwidth, MHz | 20–160 | 50 | 50–450 | 22.5 | 2.5 | 200 |

| Area, mm2 | 0.236 | 0.2 | 0.5 | 0.35 | 0.429 | |

| Gain, dB | 0 | −5.8 | 0 | 0.5 | −0.84 | −0.39 |

| P1dB, dBm | 6.96–4.26 | 2.8, 4.5 | 12 | 8.5 | 9.94 | 9.94 |

| In-band IIP3, dBm | 21–9.56 | 18, 16.5 | 27–24 | 21.5, 9 | 35.05 | 36.72 |

| Out-band IIP3, dBm | 17.4–9.7 | - | - | - | 25.66 | 16.06 |

| SFDR, dB | 66.6–50.7 | −42.5 | - | - | 75.47 | 65.29 |

| THD, dB | 66.2–50.7 | −40 | - | −40, −30 | −72.11 | −64.55 |

| NF, dB | - | - | 15 | - | 31.83 | 29.74 |

| Intg. Noise, µVRMS | 243–520 | 277 | - | 87 | 28.45 | 202.7 |

| Dynamic range, dB | 64.2–51 | - | 93.84–84.30 | 63 | 86.02 | 68.28 |

| Power, mW | 5.56–23.77 | 3.63 | 25.2 | 12.6 | 6.2 | 73.4 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kiela, K.; Jurgo, M.; Macaitis, V.; Navickas, R. Wideband Reconfigurable Integrated Low-Pass Filter for 5G Compatible Software Defined Radio Solutions. Electronics 2021, 10, 734. https://doi.org/10.3390/electronics10060734

Kiela K, Jurgo M, Macaitis V, Navickas R. Wideband Reconfigurable Integrated Low-Pass Filter for 5G Compatible Software Defined Radio Solutions. Electronics. 2021; 10(6):734. https://doi.org/10.3390/electronics10060734

Chicago/Turabian StyleKiela, Karolis, Marijan Jurgo, Vytautas Macaitis, and Romualdas Navickas. 2021. "Wideband Reconfigurable Integrated Low-Pass Filter for 5G Compatible Software Defined Radio Solutions" Electronics 10, no. 6: 734. https://doi.org/10.3390/electronics10060734

APA StyleKiela, K., Jurgo, M., Macaitis, V., & Navickas, R. (2021). Wideband Reconfigurable Integrated Low-Pass Filter for 5G Compatible Software Defined Radio Solutions. Electronics, 10(6), 734. https://doi.org/10.3390/electronics10060734