A 2.5-GS/s Four-Way-Interleaved Ringamp-Based Pipelined-SAR ADC with Digital Background Calibration in 28-nm CMOS

Abstract

:1. Introduction

2. Ring Amplifier Review

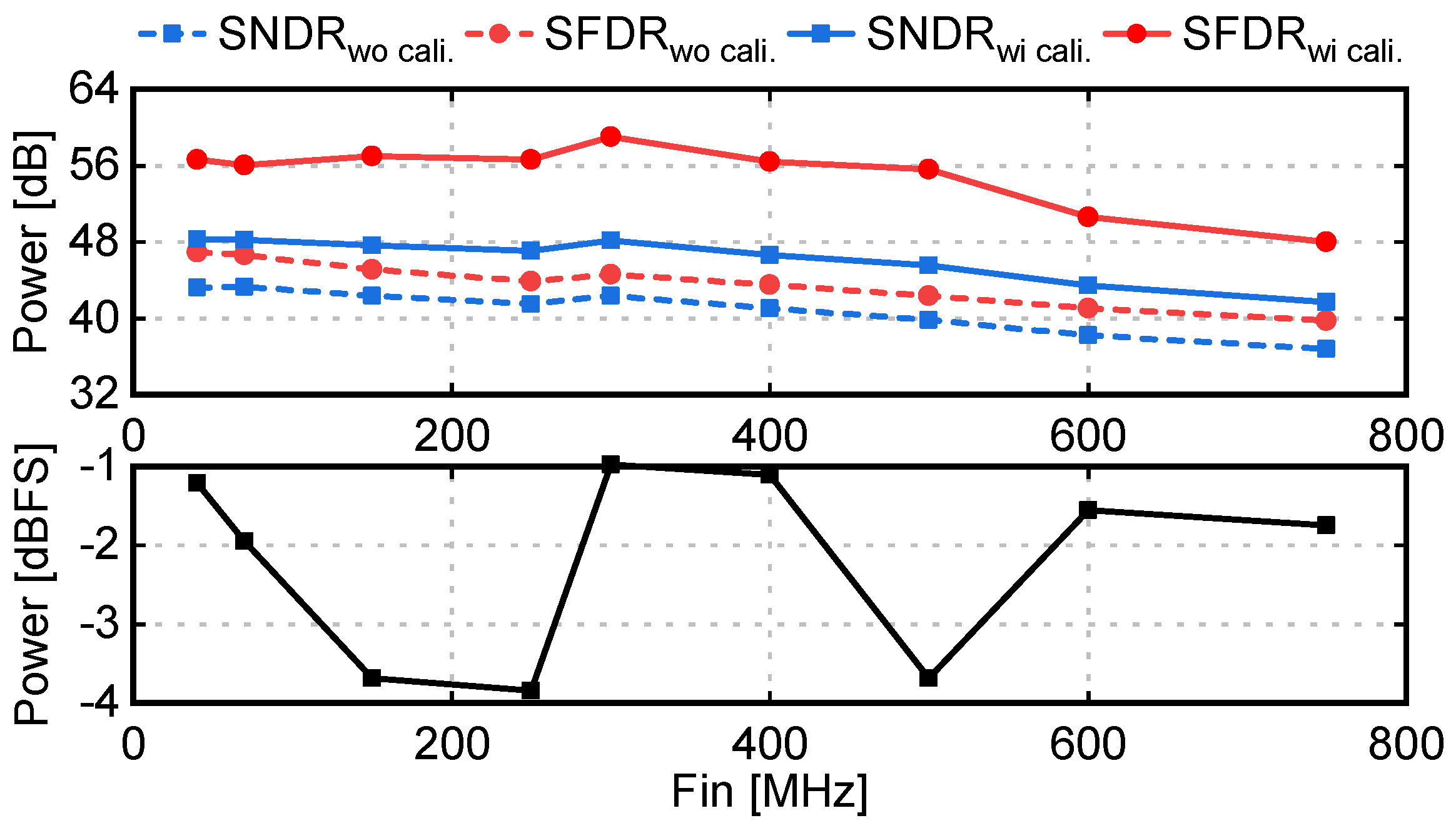

3. Proposed ADC Design

3.1. High-Linearity Front-End

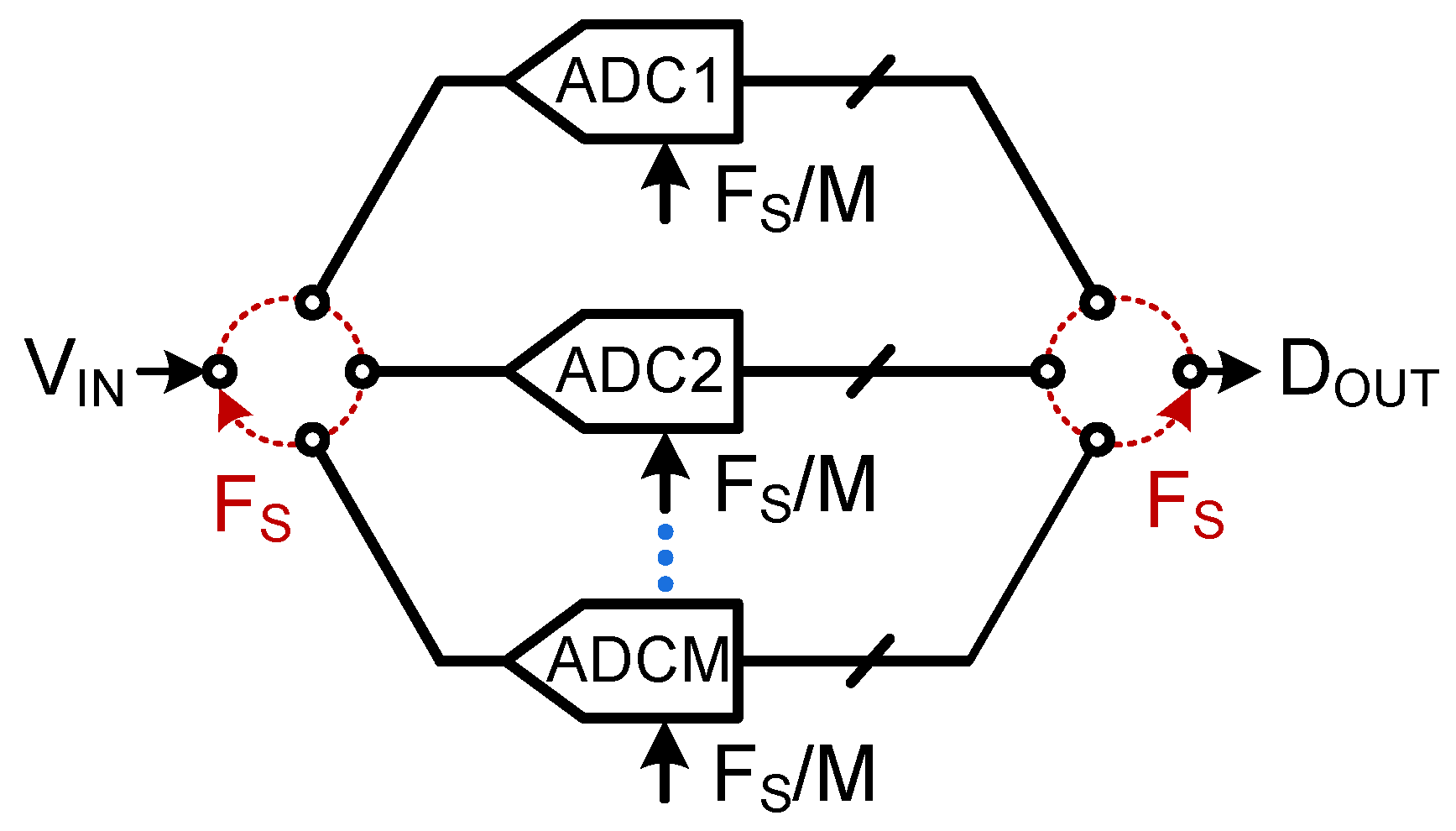

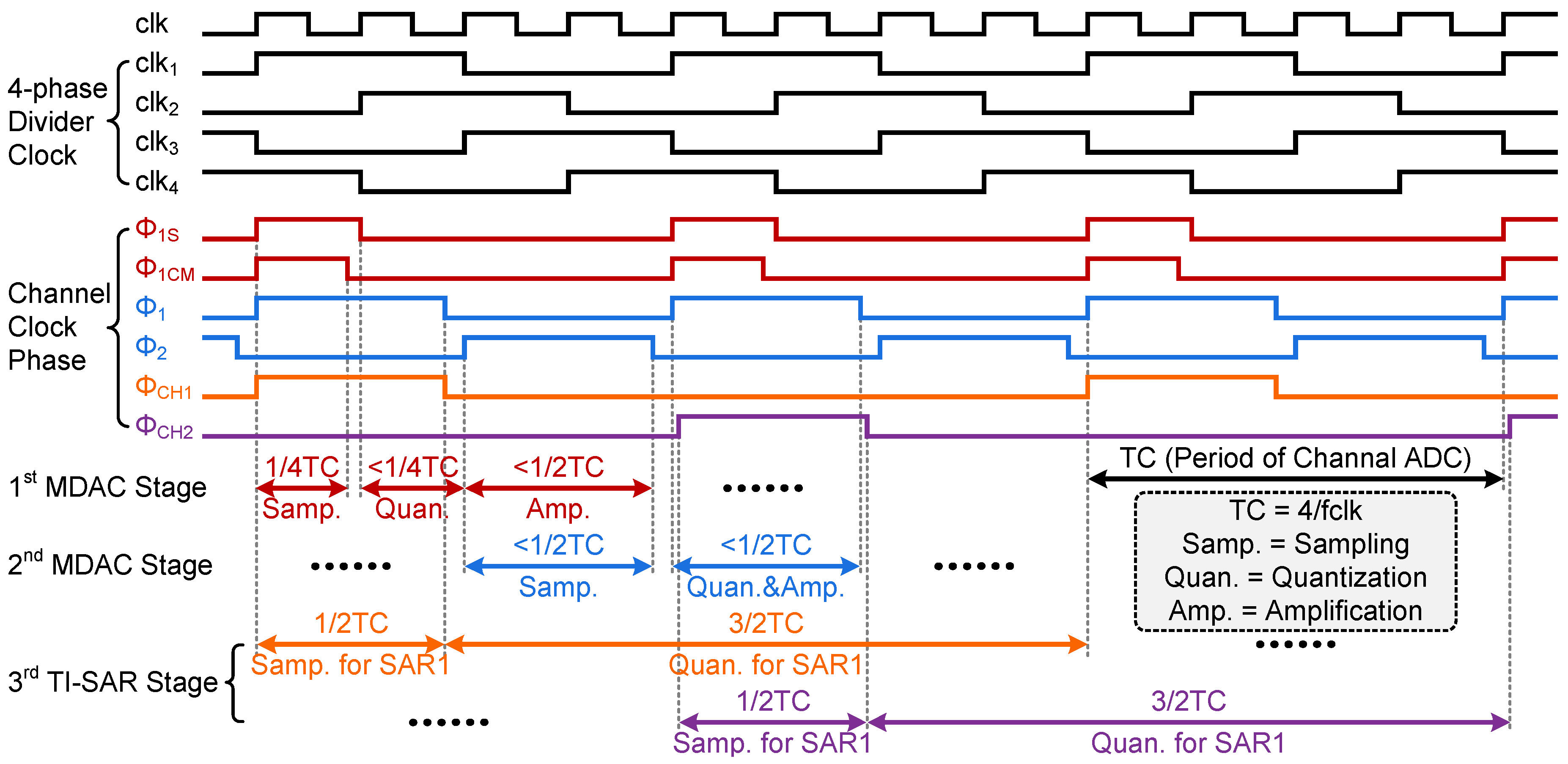

3.2. TI-ADC Architecture

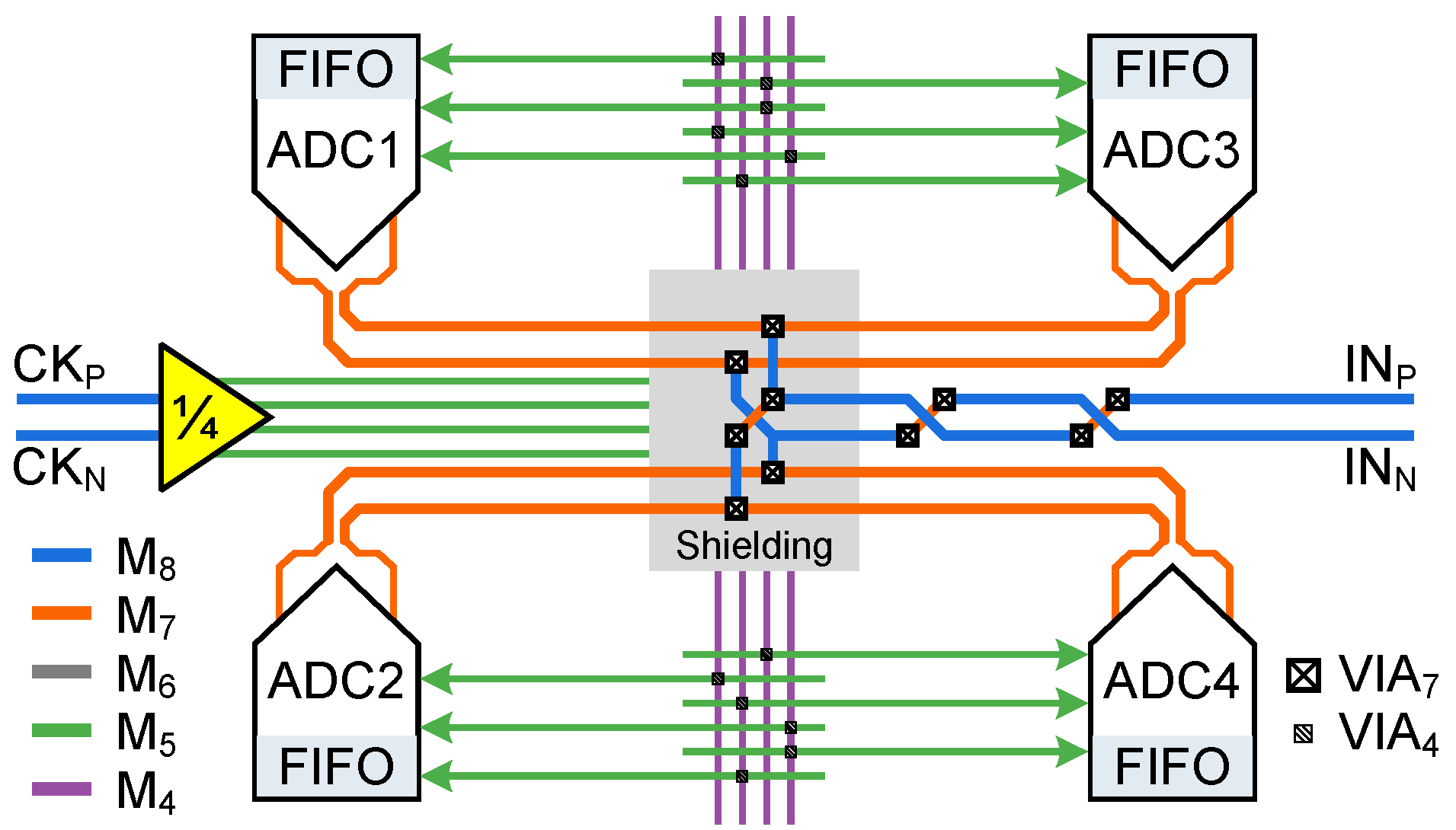

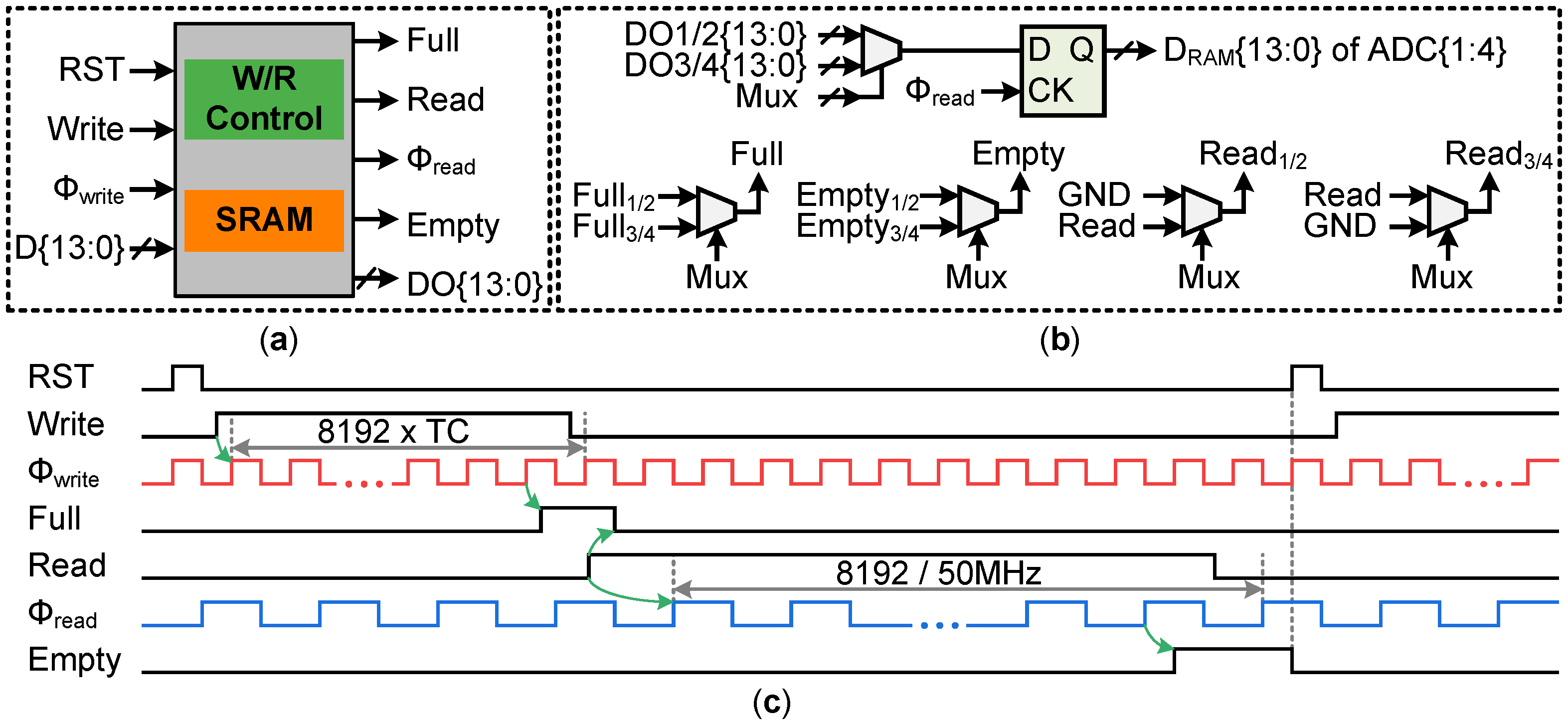

3.3. FIFO Details

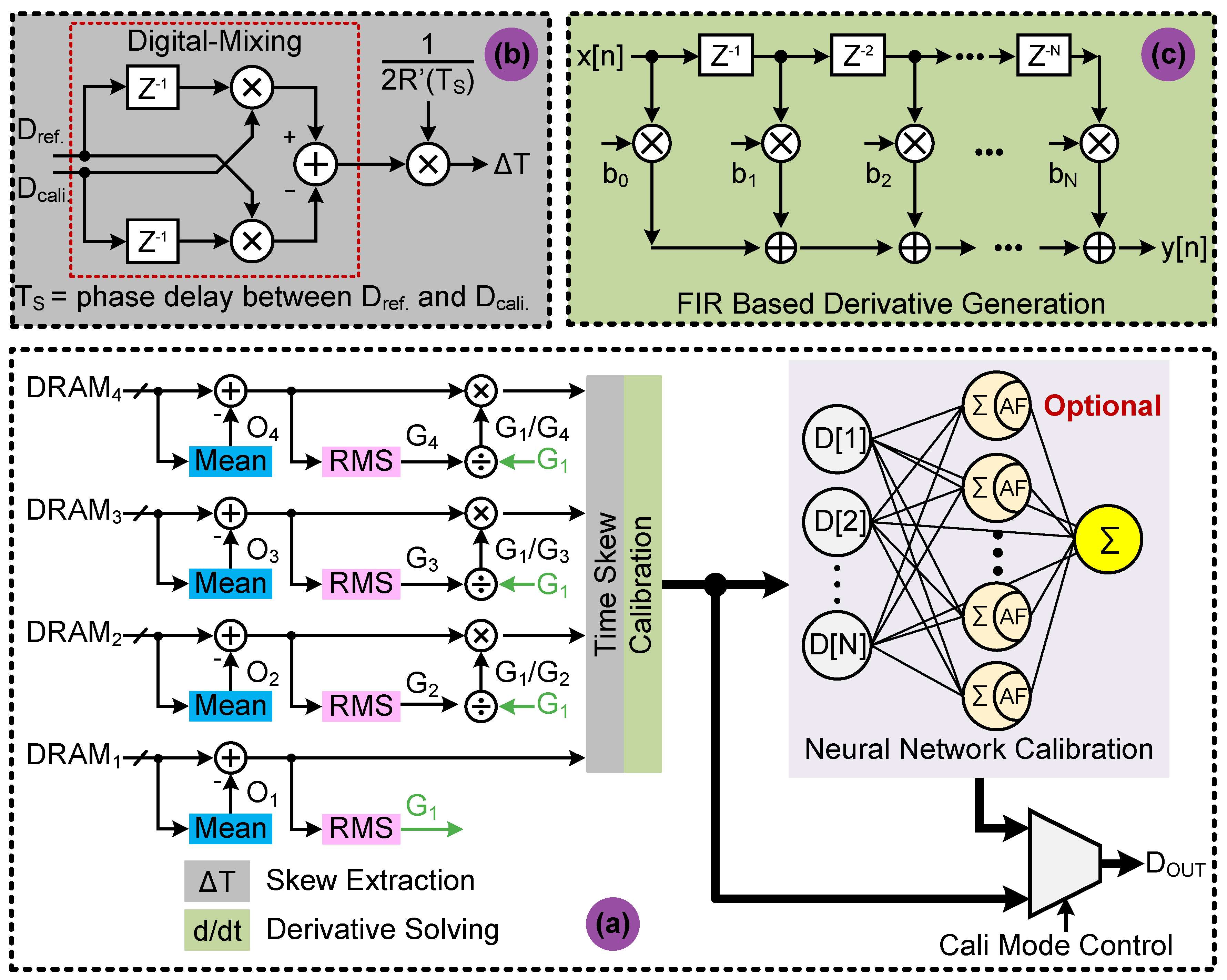

3.4. Digital Background Calibration

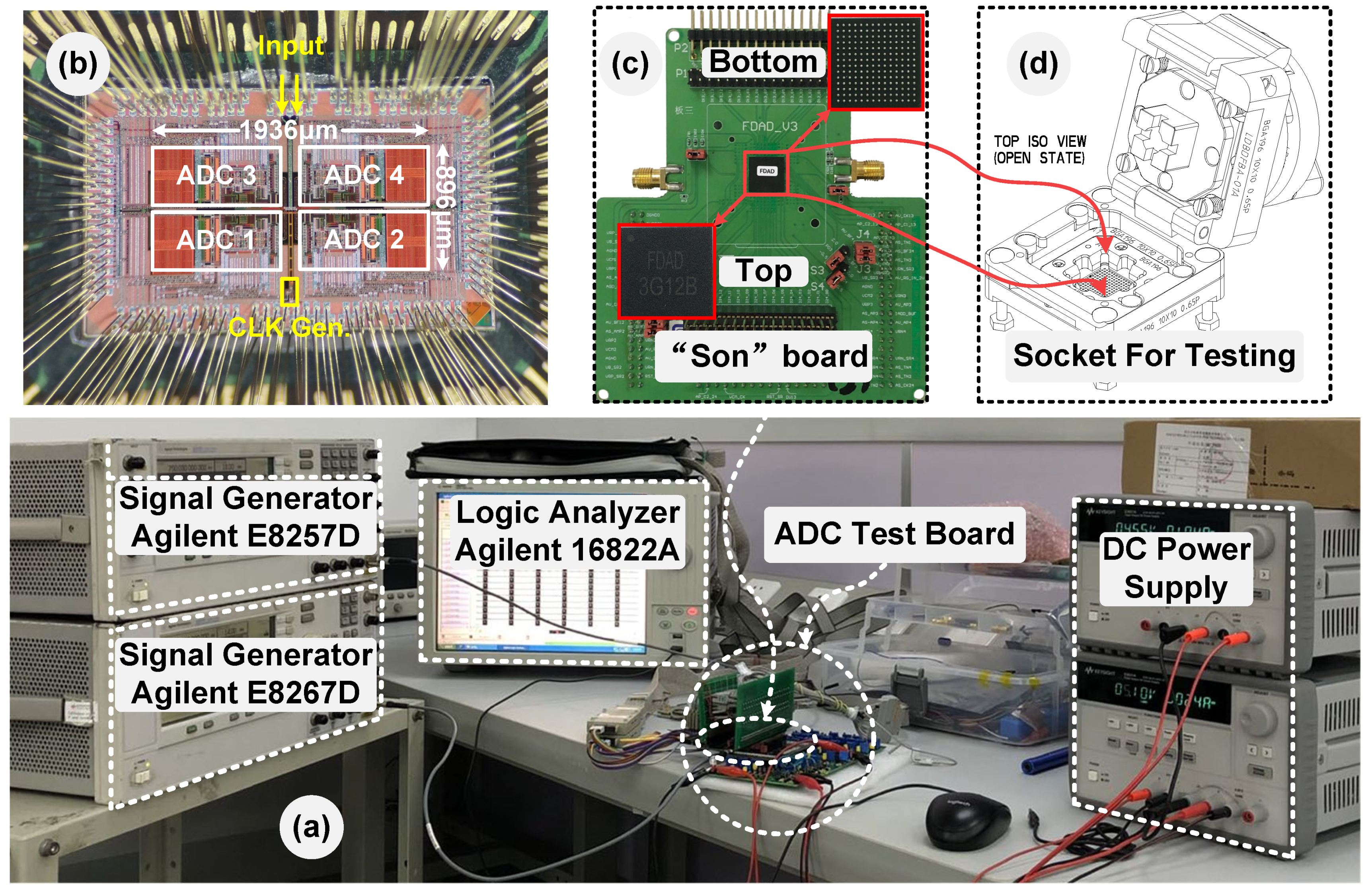

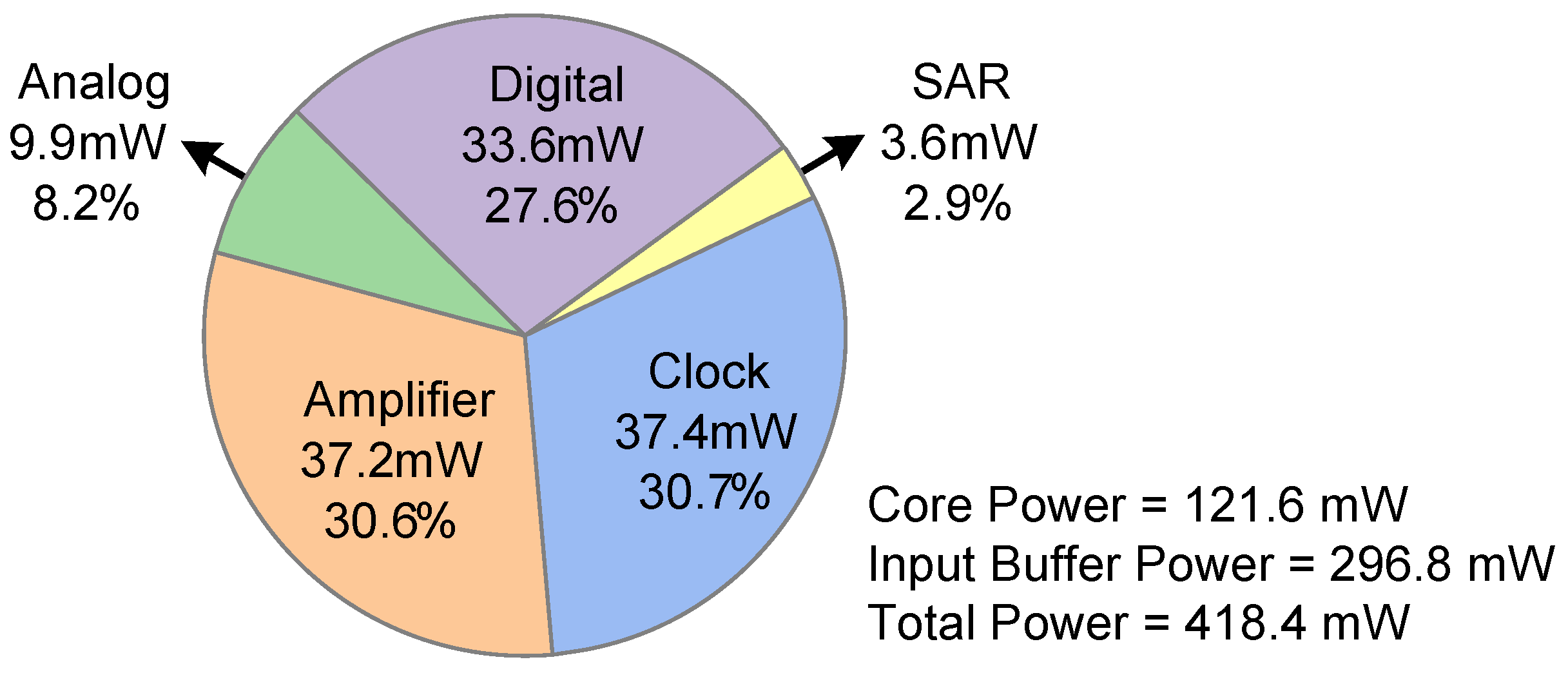

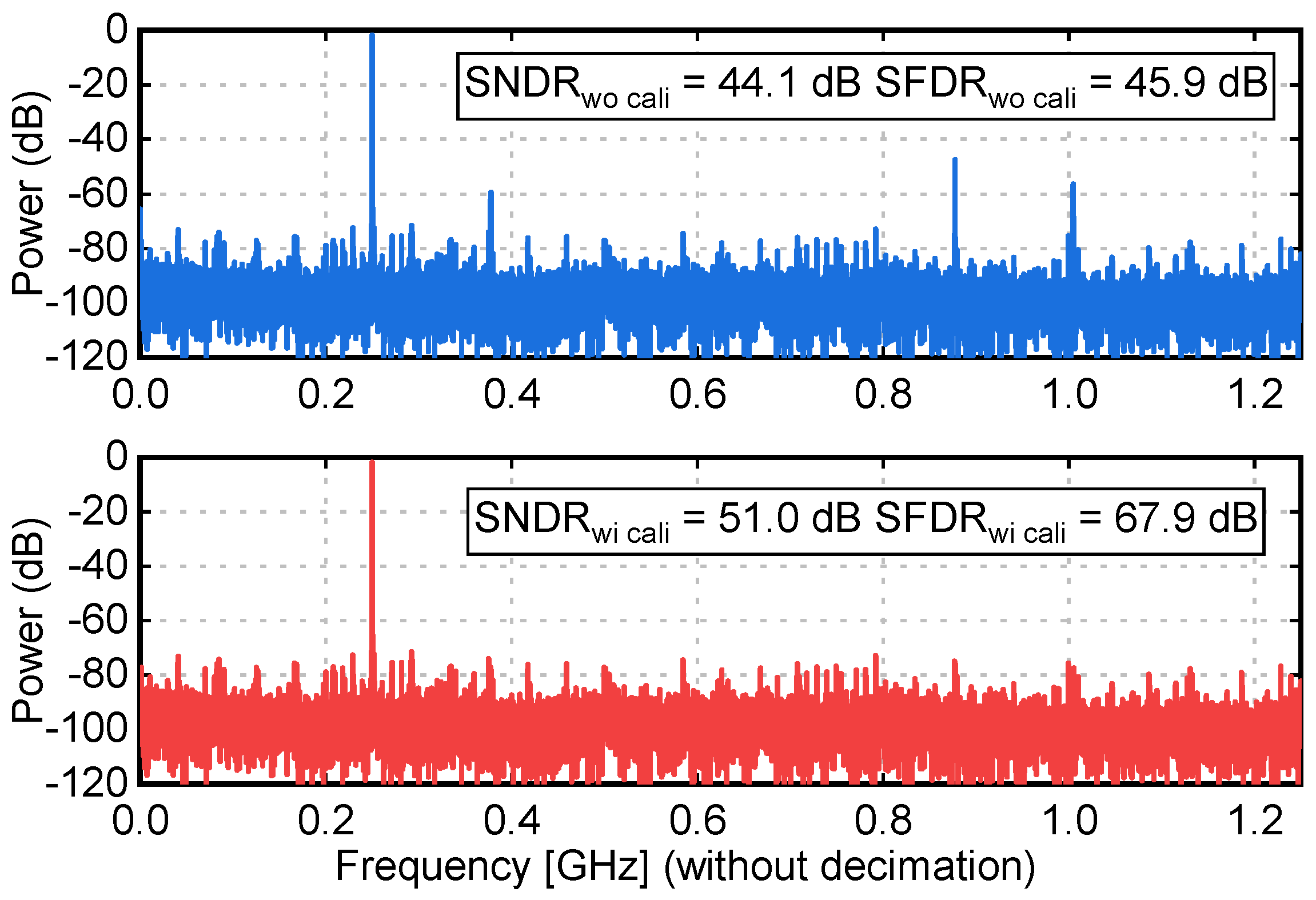

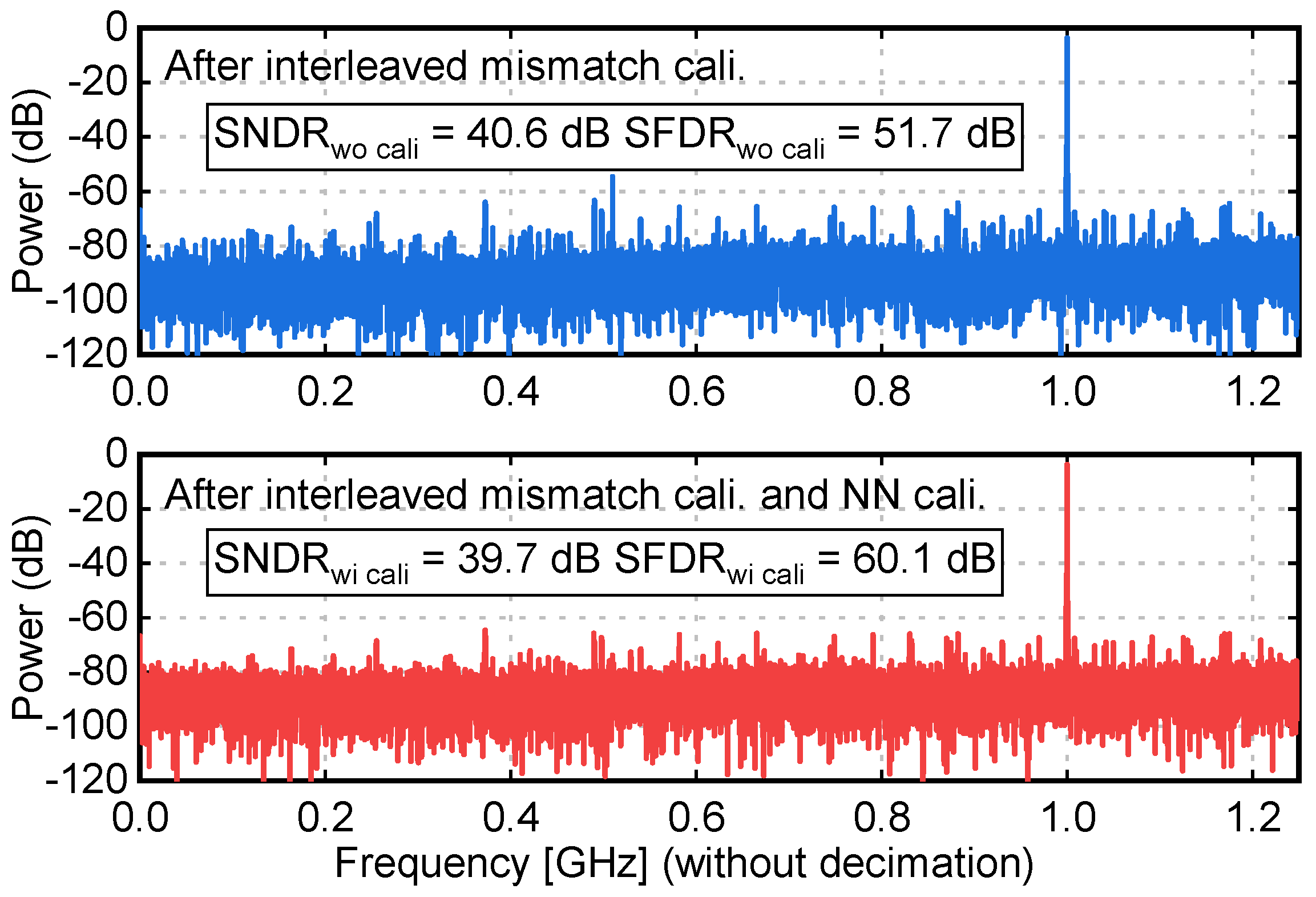

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| CMOS | Complementary metal oxide silicon |

| ADC | Analog-to-digital converter |

| DAC | Digital-to-analog converter |

| GS/s | Giga samples per second |

| HVT | High threshold voltage |

| LVT | Low threshold voltage |

| ESD | Electro-static discharge |

| BGA | Ball grid array |

| SHA | Sample and hold amplifier |

| RA | Residue amplifier |

| Ringamp | Ring amplifier |

| SAR | Successive-approximation register |

| TI | Time interleaved |

| NNC | Neural Network Calibration |

| FFT | Fast Fourier transform |

| FIR | Finite impulse response |

| FOM | Figure of merit |

| LDO | Low dropout regulator |

| MDAC | Multiplying digital-to-analog converter |

| SNDR | Signal-to-noise-and-distortion ratio |

| SFDR | Spurious free dynamic range |

| FIFO | First input first output |

| PCB | Printed circuit board |

References

- Brandolini, M.; Shin, Y.J.; Raviprakash, K.; Wang, T.; Wu, R.; Geddada, H.M.; Ko, Y.; Ding, Y.; Huang, C.; Shih, W.; et al. A 5 GS/s 150 mW 10 b SHA-Less Pipelined/SAR Hybrid ADC for Direct-Sampling Systems in 28 nm CMOS. IEEE J. Solid-State Circuits 2015, 50, 2922–2934. [Google Scholar] [CrossRef]

- Swindlehurst, E.; Jensen, H.; Petrie, A.; Song, Y.; Kuan, Y.C.; Qu, Y.; Chang, M.C.F.; Wu, J.T.; Chiang, S.H.W. An 8-bit 10-ghz 21-mw time-interleaved sar adc with grouped dac capacitors and dual-path bootstrapped switch. IEEE J. Solid-State Circuits 2021, 56, 2347–2359. [Google Scholar] [CrossRef]

- Chang, D.J.; Choi, M.; Ryu, S.T. A 28-nm 10-b 2.2-GS/s 18.2-mW Relative-Prime Time-Interleaved Sub-Ranging SAR ADC With On-Chip Background Skew Calibration. IEEE J. Solid-State Circuits 2021, 56, 2691–2700. [Google Scholar] [CrossRef]

- Guo, M.; Mao, J.; Sin, S.W.; Wei, H.; Martins, R.P. A 1.6-GS/s 12.2-mW seven-/eight-way split time-interleaved SAR ADC achieving 54.2-dB SNDR with digital background timing mismatch calibration. IEEE J. Solid-State Circuits 2019, 55, 693–705. [Google Scholar] [CrossRef]

- Yu, B.; Chen, C.; Ye, F.; Ren, J. A mixed sample-time error calibration technique in time-interleaved ADCs. IEICE Electron. Express 2013, 10, 1–11. [Google Scholar] [CrossRef] [Green Version]

- Wei, H.; Zhang, P.; Sahoo, B.D.; Razavi, B. An 8 Bit 4 GS/s 120 mW CMOS ADC. IEEE J. Solid-State Circuits 2014, 49, 1751–1761. [Google Scholar] [CrossRef]

- Ku, I.-N.; Xu, Z.; Kuan, Y.-C.; Wang, Y.-H.; Chang, M.-C.F. A 40-mW 7-bit 2.2-GS/s time-interleaved subranging CMOS ADC for low-power gigabit wireless communications. IEEE J. Solid-State Circuits 2012, 47, 1854–1865. [Google Scholar] [CrossRef]

- Wu, J.; Chou, A.; Yang, C.-H.; Ding, Y.; Ko, Y.-J.; Lin, S.-T.; Liu, W.; Hsiao, C.-M.; Hsieh, M.-H.; Huang, C.-C.; et al. A 5.4GS/s 12b 500mW Pipeline ADC in 28nm CMOS. In Proceedings of the 2013 Symposium on VLSI Circuits, Kyoto, Japan, 16 August 2013; pp. C92–C93. [Google Scholar]

- Singh, S.; Anttila, L.; Epp, M.; Schlecker, W.; Valkama, M. Frequency Response Mismatches in 4-channel Time-Interleaved ADCs: Analysis, Blind Identification, and Correction. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 2268–2279. [Google Scholar] [CrossRef]

- Zhou, Y.; Xu, B.; Chiu, Y. A 12-b 1-GS/s 31.5-mW Time-Interleaved SAR ADC With Analog HPF-Assisted Skew Calibration and Randomly Sampling Reference ADC. IEEE J. Solid-State Circuits 2019, 54, 2207–2218. [Google Scholar] [CrossRef]

- Yin, M.; Ye, Z. First order statistic based fast blind calibration of time skews for time-interleaved ADCs. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 162–166. [Google Scholar] [CrossRef]

- Razavi, B. Design considerations for interleaved ADCs. IEEE J. Solid-State Circuits 2013, 48, 1806–1817. [Google Scholar] [CrossRef] [Green Version]

- Wang, X.; Li, F.; Jia, W.; Wang, Z. A 14-bit 500-MS/s time-interleaved ADC with autocorrelation-based time skew calibration. IEEE Trans. Circuits Syst. II Express Briefs 2018, 66, 322–326. [Google Scholar] [CrossRef]

- Lin, C.-Y.; Wei, Y.-H.; Lee, T.-C. A 10-bit 2.6-GS/s time-interleaved SAR ADC with a digital-mixing timing-skew calibration technique. IEEE J. Solid-State Circuits 2018, 53, 1508–1517. [Google Scholar] [CrossRef]

- Le Dortz, N.; Blanc, J.P.; Simon, T.; Verhaeren, S.; Rouat, E.; Urard, P.; Le Tual, S.; Goguet, D.; Lelandais-Perrault, C.; Benabes, P. A 1.62 GS/s time-interleaved SAR ADC with digital background mismatch calibration achieving interleaving spurs below 70 dBFS. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 9–13 February 2014; pp. 386–388. [Google Scholar]

- Guo, M.; Mao, J.; Sin, S.W.; Wei, H.; Martins, R.P. A 29mW 5GS/s Time-interleaved SAR ADC achieving 48.5dB SNDR With Fully-Digital Timing-Skew Calibration Based on Digital-Mixing. In Proceedings of the IEEE Symposium on VLSI Circuits Digest of Technical Papers, Kyoto, Japan, 5–8 June 2017; pp. C76–C77. [Google Scholar]

- Janssen, E.; Doris, K.; Zanikopoulos, A.; Murroni, A.; Van Der Weide, G.; Lin, Y.; Alvado, L.; Darthenay, F.; Fregeais, Y. An 11b 3.6 GS/s time-interleaved SAR ADC in 65nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 17–21 February 2013; pp. 464–465. [Google Scholar]

- Doris, K.; Janssen, E.; Nani, C.; Zanikopoulos, A.; Van Der Weide, G. A 480 mW 2.6 GS/s 10b Time-Interleaved ADC With 48.5 dB SNDR up to Nyquist in 65 nm CMOS. IEEE J. Solid-State Circuits 2011, 46, 2821–2833. [Google Scholar] [CrossRef]

- Jia, H.; Guo, X.; Wu, D.; Zhou, L.; Luan, J.; Wu, N.; Huang, Y.; Zheng, X.; Wu, J.; Liu, X. A 12-Bit 2.4 GS/s Four-Channel Pipelined ADC with a Novel On-Chip Timing Mismatch Calibration. Electronics 2020, 9, 910. [Google Scholar] [CrossRef]

- Chen, C.Y.; Wu, J.; Hung, J.J.; Li, T.; Liu, W.; Shih, W.T. A 12-bit 3 GS/s pipeline ADC with 0.4 mm 2 and 500 mW in 40 nm digital CMOS. IEEE J. Solid-State Circuits 2012, 47, 1013–1021. [Google Scholar] [CrossRef]

- Li, J.; Guo, X.; Luan, J.; Wu, D.; Zhou, L.; Huang, Y.; Wu, N.; Jia, H.; Zheng, X.; Wu, J.; et al. A 3GSps 12-bit four-channel time-interleaved pipelined ADC in 40 nm CMOS process. Electronics 2019, 8, 1551. [Google Scholar] [CrossRef] [Green Version]

- Ramkaj, A.T.; Ramos, J.C.P.; Pelgrom, M.J.; Steyaert, M.S.; Verhelst, M.; Tavernier, F. A 5-GS/s 158.6-mW 9.4-ENOB passive-sampling time-interleaved three-stage pipelined-SAR ADC with Analog–Digital corrections in 28-nm CMOS. IEEE J. Solid-State Circuits 2020, 55, 1553–1564. [Google Scholar] [CrossRef]

- Ali, A.M.; Dinc, H.; Bhoraskar, P.; Dillon, C.; Puckett, S.; Gray, B.; Speir, C.; Lanford, J.; Brunsilius, J.; Derounian, P.R.; et al. A 14 bit 1 GS/s RF sampling pipelined ADC with background calibration. IEEE J. Solid-State Circuits 2014, 49, 2857–2867. [Google Scholar] [CrossRef]

- Hershberg, B.; Dermit, D.; Liempd, B.; Martens, E.; Markulic, N.; Lagos, J.; Craninckx, J. A 3.2 GS/s 10 ENOB 61mW ringamp ADC in 16 nm with background monitoring of distortion. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 17–21 February 2019. [Google Scholar]

- Verma, D.; Shehzad, K.; Khan, D.; Kim, S.J.; Pu, Y.G.; Yoo, S.S.; Hwang, K.C.; Yang, Y.; Lee, K.Y. A Design of Low-Power 10-bit 1-MS/s Asynchronous SAR ADC for DSRC Application. Electronics 2020, 9, 1100. [Google Scholar] [CrossRef]

- Aiello, O.; Crovetti, P.; Alioto, M. Fully synthesizable low-area analogue-to-digital converters with minimal design effort based on the dyadic digital pulse modulation. IEEE Access 2020, 8, 70890–70899. [Google Scholar] [CrossRef]

- Wan, P.; Su, L.; Zhang, H.; Chen, Z. A Power-Efficient Pipelined ADC with an Inherent Linear 1-Bit Flip-Around DAC. Electronics 2020, 9, 199. [Google Scholar] [CrossRef] [Green Version]

- Choi, M.Y.; Kong, B.S. Linearity Enhancement of VCO-Based Continuous-Time Delta-Sigma ADCs Using Digital Feedback Residue Quantization. Electronics 2021, 10, 2773. [Google Scholar] [CrossRef]

- Hershberg, B.; Weaver, S.; Sobue, K.; Takeuchi, S.; Hamashita, K.; Moon, U.-K. Ring Amplifiers for Switched Capacitor Circuits. IEEE J. Solid-State Circuits 2012, 47, 2928–2942. [Google Scholar] [CrossRef] [Green Version]

- Lim, Y.; Flynn, M. A 100 MS/s 10.5 b 2.46 mW comparator-less pipeline ADC using self-biased ring amplifiers. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Paper, San Francisco, CA, USA, 9–13 February 2014. [Google Scholar]

- Chen, Y.; Wang, J.; Hu, H.; Ye, F.; Ren, J. A 200 MS/s, 11 bit SAR-assisted pipeline ADC with bias-enhanced ring amplifier. In Proceedings of the IEEE International Symposium on Circuits and Systems, Baltimore, MD, USA, 28–31 May 2017. [Google Scholar]

- Lee, C.; Venkatachala, P.; ElSHater, A.; Xiao, B.; Hu, H.; Moon, U. Cascoded ring amplifiers for high speed and high accuracy settling. In Proceedings of the IEEE International Symposium on Circuits and Systems, Sapporo, Japan, 26–29 May 2019. [Google Scholar]

- Lagos, J.; Hershberg, B.; Martens, E.; Wambacq, P.; Craninckx, J. A 1-GS/s, 12-b, Single-Channel Pipelined ADC With Dead-Zone-Degenerated Ring Amplifiers. IEEE J. Solid-State Circuits 2019, 54, 646–658. [Google Scholar] [CrossRef]

- Elshater, A.; Venkatachala, P.K.; Lee, C.Y.; Muhlestein, J.; Leuenberger, S.; Sobue, K.; Hamashita, K.; Moon, U.-K. A 10-mW 16-b 15-MS/s Two-Step SAR ADC With 95-dB DR Using Dual-Deadzone Ring Amplifier. IEEE J. Solid-State Circuits 2019, 54, 3410–3420. [Google Scholar] [CrossRef]

- Lan, J.; Chen, Y.; Shen, X.; Ni, Z.; Wu, Y.; Ye, F.; Ren, J. Effective Gain Analysis and Statistic Based Calibration for Ring Amplifier with Robustness to PVT Variation. IEEE Trans. Circuits Syst. II Express Briefs 2021. early access. [Google Scholar] [CrossRef]

- Lee, J.; Lee, S.; Kim, K.; Chae, H. A Pipelined Noise-Shaping SAR ADC Using Ring Amplifier. Electronics 2021, 10, 1968. [Google Scholar] [CrossRef]

- Lagos, J.; Markulic, N.; Hershberg, B.; Dermit, D.; Shrivas, M.; Martens, E.; Craninckx, J. A 10.0 ENOB, 6.2 fJ/conv.-step, 500 MS/s Ringamp-Based Pipelined-SAR ADC with Background Calibration and Dynamic Reference Regulation in 16nm CMOS. In Proceedings of the 2013 Symposium on VLSI Circuits, Kyoto, Japan, 13–19 June 2021; pp. 1–2. [Google Scholar]

- Megawer, K.M.; Hussien, F.A.; Aboudina, M.M.; Mohieldin, A.N. A Systematic Design Methodology for Class-AB-Style Ring Amplifiers. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 1169–1173. [Google Scholar] [CrossRef]

- Conrad, J.; Vogelmann, P.; Mokhtar, M.A.; Ortmanns, M. Design Approach for Ring Amplifiers. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 67, 3444–3457. [Google Scholar] [CrossRef]

- Zhang, T.; Cao, Y.; Zhang, S.; Chen, C.; Ye, F.; Ren, J. Machine learning based prior-knowledge-free calibration for split pipelined-SAR ADCs with open-loop amplifiers achieving 93.7-dB SFDR. In Proceedings of the IEEE 45th European Solid State Circuits Conference, Krakow, Poland, 23–26 September 2019; pp. 189–192. [Google Scholar]

| Reference | [17] | [18] | [19] | [20] | [21] | This Work |

|---|---|---|---|---|---|---|

| resolution [b] | 11 | 10 | 12 | 12 | 12 | 12 |

| supplies [V] | 1.2/2.5 | 1.2/1.3/1.6 | 1.8 | 2.5 | 1.8 | 1.0/2.0/−0.5 |

| architecture | TI-SAR | TI-SAR | TI-Pipeline | TI-Pipeline | TI-Pipeline | TI-Pipelined-SAR |

| channel number | 4 × 16 | 4 × 16 | 4 | 2 | 4 | 4 |

| fs [GS/s] | 3.6 | 2.6 | 2.4 | 3.0 | 3.0 | 2.5 |

| technology [nm] | 65 | 65 | 40 | 40 | 40 | 28 |

| area | 7.4 | 5.1 | 9 | 0.4 a | 3.9 a | 1.73 a |

| SNDR [dB] | 42.0 b | 48.5 b | 49.7 b | 51.0 b | 52.3 b | 51.0 c |

| SFDR [dB] | 50.0 b | 53.8 b | 60.2 b | 59.0 b | 61.5 b | 68.0 c |

| power [mW] | 795 | 480 | 420 | 500 | 450 | 418.4 d |

| [pJ/conversion-step] e | 2.15 | 0.85 | 0.70 | 0.58 | 0.44 | 0.48 f |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lan, J.; Zhai, D.; Chen, Y.; Ni, Z.; Shen, X.; Ye, F.; Ren, J. A 2.5-GS/s Four-Way-Interleaved Ringamp-Based Pipelined-SAR ADC with Digital Background Calibration in 28-nm CMOS. Electronics 2021, 10, 3173. https://doi.org/10.3390/electronics10243173

Lan J, Zhai D, Chen Y, Ni Z, Shen X, Ye F, Ren J. A 2.5-GS/s Four-Way-Interleaved Ringamp-Based Pipelined-SAR ADC with Digital Background Calibration in 28-nm CMOS. Electronics. 2021; 10(24):3173. https://doi.org/10.3390/electronics10243173

Chicago/Turabian StyleLan, Jingchao, Danfeng Zhai, Yongzhen Chen, Zhekan Ni, Xingchen Shen, Fan Ye, and Junyan Ren. 2021. "A 2.5-GS/s Four-Way-Interleaved Ringamp-Based Pipelined-SAR ADC with Digital Background Calibration in 28-nm CMOS" Electronics 10, no. 24: 3173. https://doi.org/10.3390/electronics10243173

APA StyleLan, J., Zhai, D., Chen, Y., Ni, Z., Shen, X., Ye, F., & Ren, J. (2021). A 2.5-GS/s Four-Way-Interleaved Ringamp-Based Pipelined-SAR ADC with Digital Background Calibration in 28-nm CMOS. Electronics, 10(24), 3173. https://doi.org/10.3390/electronics10243173