1. Introduction

The development of wireless sensor networks (WSNs) has seen an increased demand in the last decade. The interest can be attributed to their cost-effective and easy implementation in a wide range of fields such as agriculture, environment monitoring, surveillance, etc. [

1]. Designing a sensor node requires several critical design considerations such as form factor, network size, operating conditions, power consumption, maintenance, etc. For WSNs, when designing a battery-less sensor node, minimizing the power consumption is a challenging task. Among the several functional blocks of a sensor node, most of the available power is used for carrier signal generation for data transmission. Using a local oscillator for carrier generation not only necessitates a significant amount of power consumption, but it is also quite difficult to achieve sufficient accuracy over process–voltage–temperature (PVT) variations [

2]. Thus, it is challenging to implement a low-power wireless communication architecture in low-cost WSNs without the availability of a stable reference frequency.

Backscattering the incoming signal to eliminate the need for carrier signal generation has been a popular and uncomplicated solution [

3]. However, backscattering can make the system prone to self-jamming [

4]. The phase-locked loop (PLL) architecture is another dominant choice for carrier frequency synthesis. Ref. [

5] shows the implementation of a transceiver that uses the received 915 MHz signal as input of a PLL to realize a 2.4-GHz RF carrier for wireless data transmission. However, due to the need for a VCO, a phase detector, and a frequency divider, a PLL is physically large and consumes a significant amount of power [

6]. The PLL also suffers from phase noise accumulation in the voltage-controlled oscillator (VCO) [

7].

In the last decade, the delay-locked loop (DLL)-based frequency synthesis has been under exploration [

8,

9,

10,

11,

12,

13] due to its low power, low complexity, and area-efficient performance. Ref. [

8] presents a DLL based on a voltage-controlled delay line (VCDL) and an edge combiner. This approach may suffer from duty cycle distortion due to the possible mismatches in the VCDL and because the frequency multiplier triggers on both the rising and the falling edge. Another DLL uses VCDL, which can be configured as a resettable VCO [

9]. However, this approach may have a high in-lock error due to the process of injecting back the frequency into the VCDL. Since the DLL operation does not require any inductors and for the most part consists of digital logic circuits, its implementation is area efficient. This paper presents the design of a low-power XOR logic-based DLL. The proposed DLL is designed as a part of a battery-less wireless sensor node. To conserve power, the sensor node extracts the carrier of an ISM band signal and divides the received frequency. The DLL then applies 8× multiplication to the input signal to generate a 2.44 GHz signal in the output. Therefore, it is critical for the DLL to be energy efficient for its application. The design uses current-starved voltage-controlled delay cells (VCDLs) to minimize power consumption. A series of three 2× multiplication stages are used to achieve 8× frequency multiplication. A new charge pump (CP)-based duty cycle control loop (DCCL) is implemented in each multiplication stage to achieve low duty cycle distortion over PVT variation.

This paper is organized as follows:

Section 2 describes the implemented DLL architecture. The circuit implementation is discussed in

Section 3.

Section 4 presents the experimental results, and a conclusion ends the paper.

2. DLL Architecture and Operation

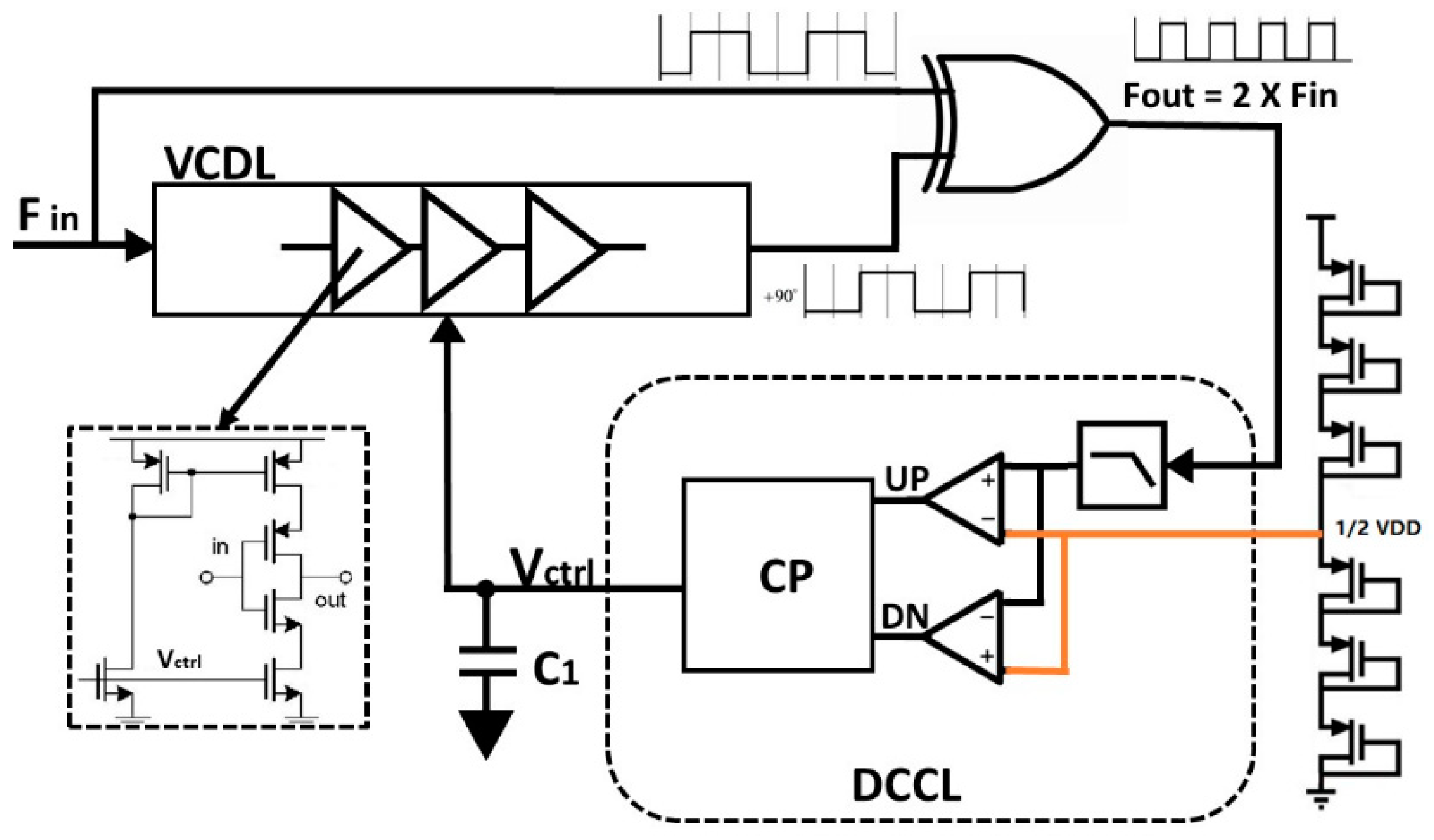

The block diagram of the proposed frequency multiplier is shown in

Figure 1.

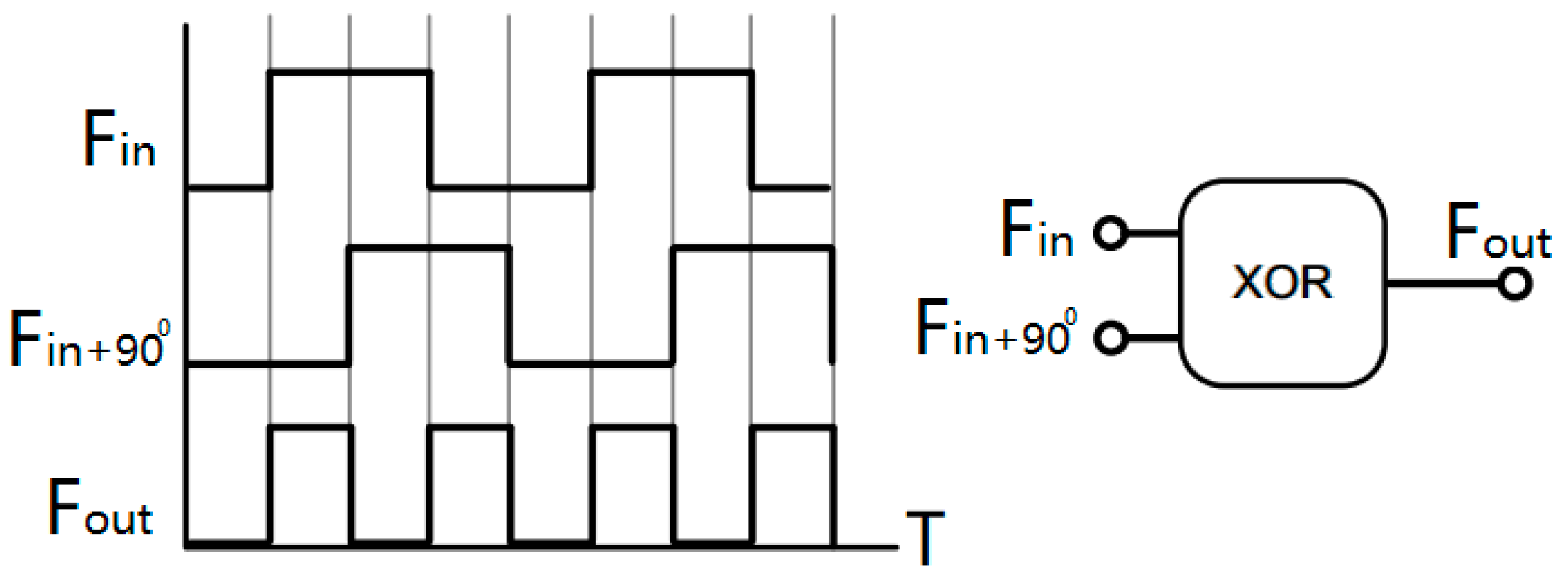

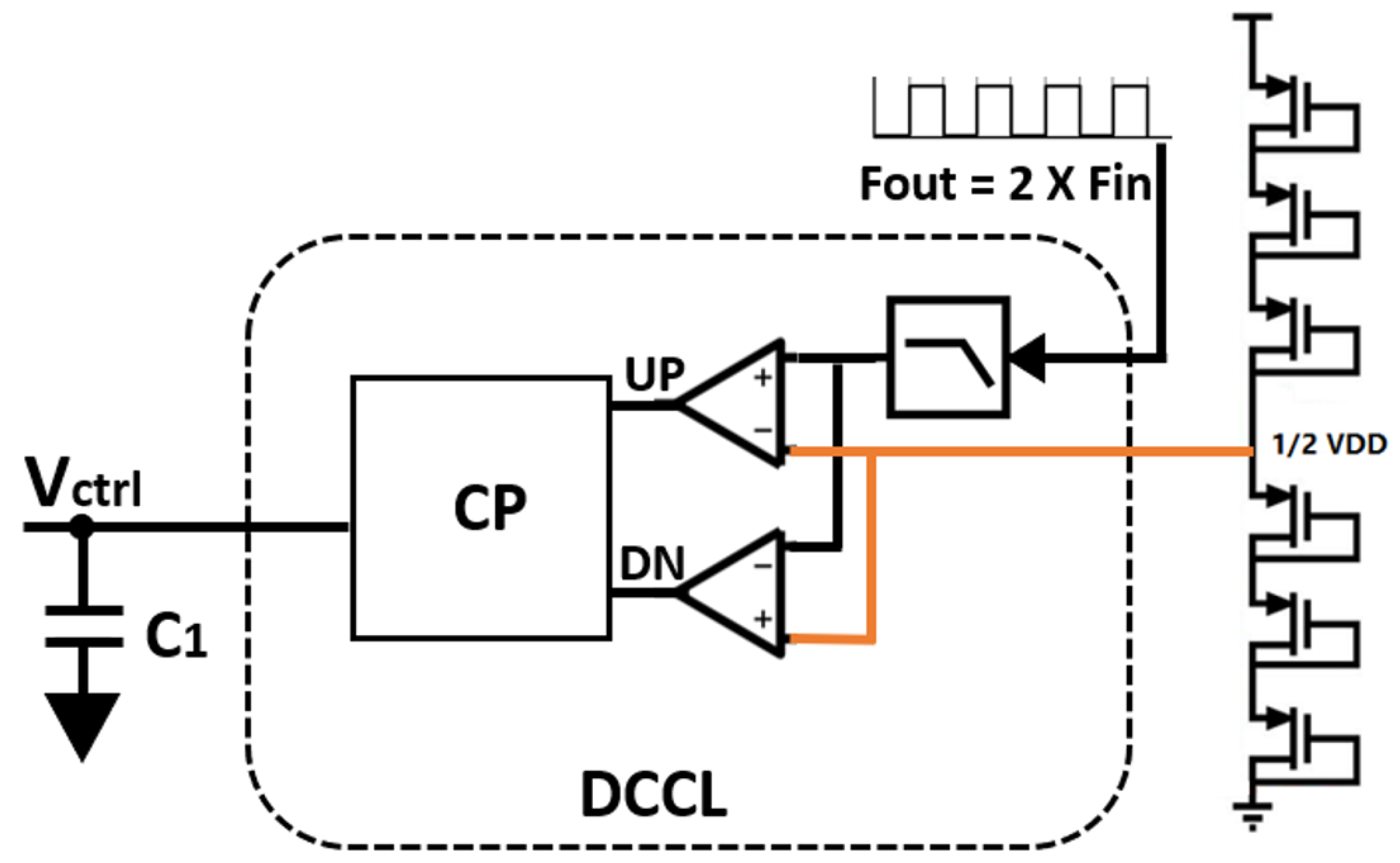

Each 2× multiplication comprises a VCDL, an XOR gate, and a duty cycle control loop (DCCL). A series of three 2× multipliers is used to achieve 8× frequency multiplication. VCDL is then followed by a low-power XOR gate. Given that frequency locking is not an issue, an XOR gate is preferred as the phase detector in our approach. The XOR gate takes in both the original signal and the delayed signal to output a 2× frequency, as shown in

Figure 2.

Initially, the delay introduced by the VCDL may not be exactly 90°. The duty cycle may be less than or greater than 50%. The duty cycle correction circuit uses a passive integrator to generate an average DC voltage proportional to the duty cycle. The output of the integrator is compared with a voltage level equal to half of the supply voltage (VDD) using comparators. After comparison, the DCCL circuit signals the charge pump (CP) circuit to generate feedback control voltages. The feedback coming from CP then varies Vctrl to correct the delay to 90°, achieving a 50% duty cycle. It is to be noted that in the case of a single 2× multiplication stage for an input frequency of 305 MHz, the whole circuit except the output of the XOR gate is switching at 610 MHz, i.e., twice the input frequency.

3. Circuit Implementation

3.1. Current-Starved Delay Cell

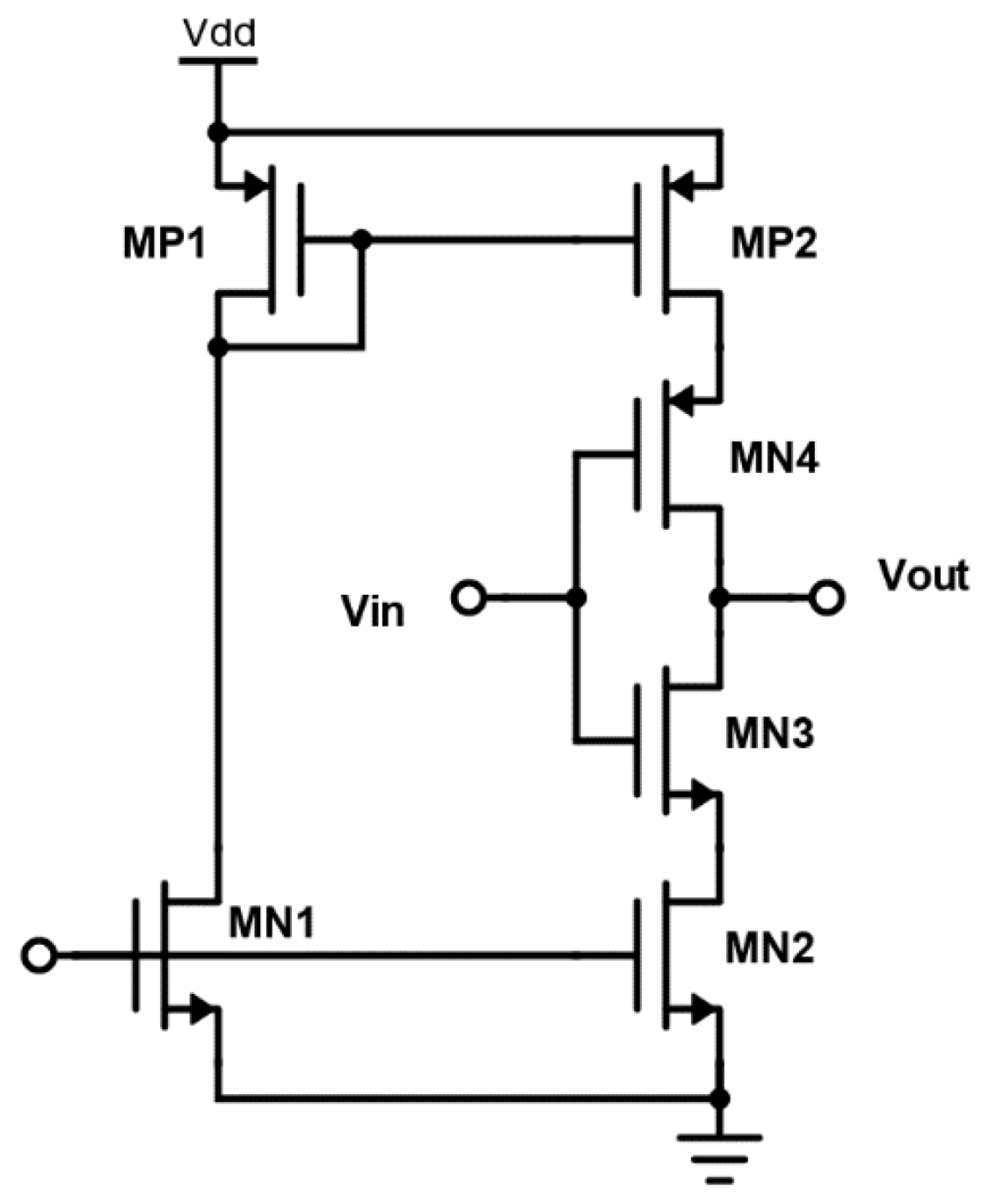

Current-starved full-swing inverter cells are used in the VCDL to generate the 90° delay. The implemented delay cell is optimized for low power consumption and is shown in

Figure 3. The current in the delay cell is controlled by the gate voltage of MN2 and MP2. The inverter is sized to produce only a fraction of the total delay. Too many or too few delay cells in VCDL can impact the process corner variation. Therefore, the number of delay cells in each VCDL is optimized to achieve better performance across process corners. Careful consideration in layout design is taken to minimize mismatches.

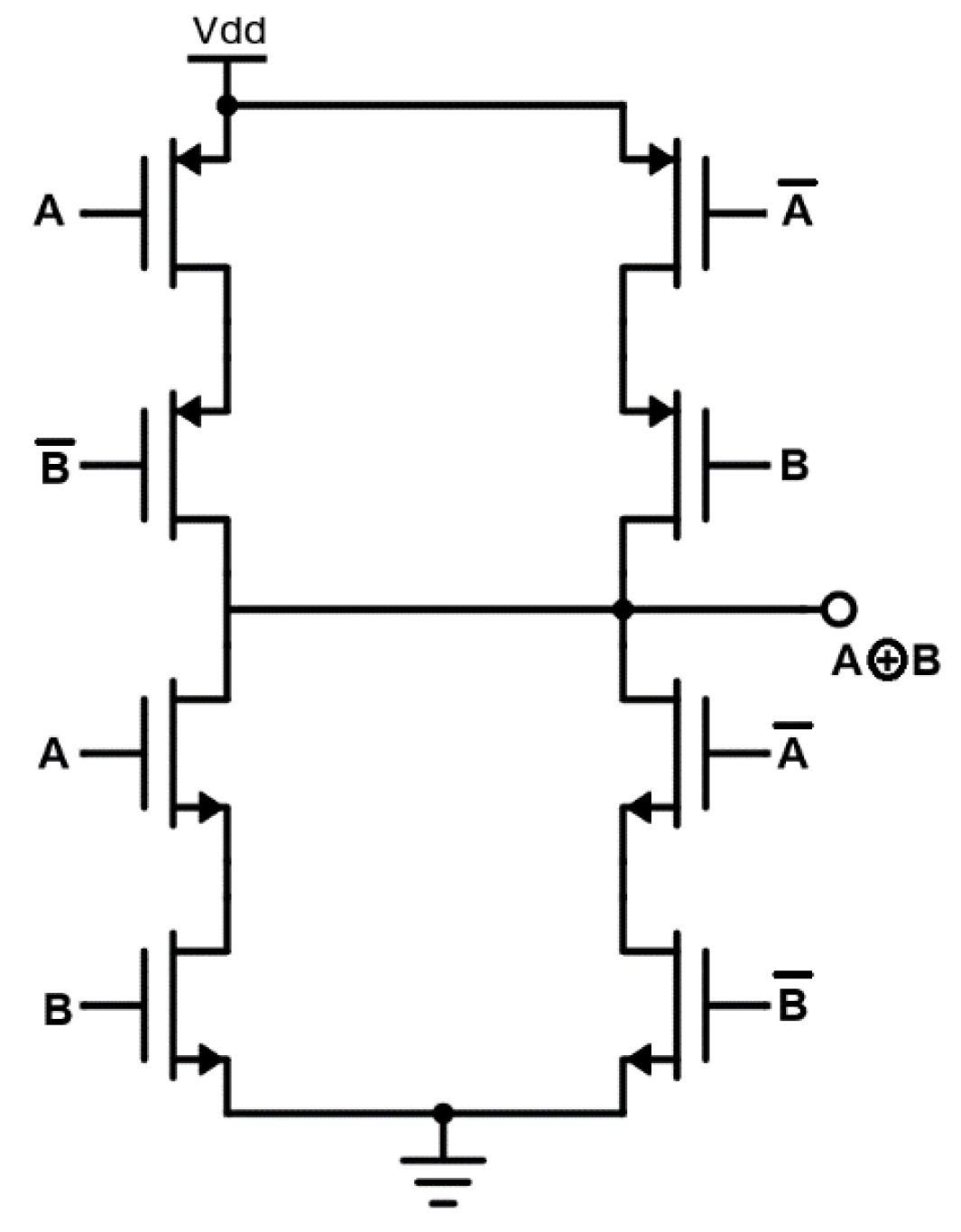

3.2. XOR Logic

Conventional XOR gates are used for frequency multiplication. The use of an edge combiner is avoided in this implementation to reduce the number of XOR gates. The current implementation uses only three XOR gates in total to achieve 8× frequency multiplication. Comparatively, an edge combiner will require seven XOR gates for 8× multiplication. The schematic of the implemented XOR gate topology is shown in

Figure 4. Since each multiplication stage has a different input frequency, each of the XOR gates is optimized for power consumption and frequency.

3.3. Duty Cycle Correction Loop

The DCCL ensures a 50% duty cycle of the output on all PVT corners. It controls the delay of VCDL using the signal Vctrl. The feedback forces the average (i.e., DC component) of the 2× signal to be equal to half of the VDD to achieve a 50% duty cycle. To save power and area, diode-connected stacked PMOS devices are used. The stacked MOS diodes generate a VREF equal to half of VDD. A passive RC integrator extracts the DC of the 2× signal and compares it with VREF using OTAs, as shown in

Figure 5. The OTAs are biased in the subthreshold region to achieve ultra-low-power operation. The UP and DN signals coming from the OTAs are fed into the charge pump circuit to generate Vctrl.

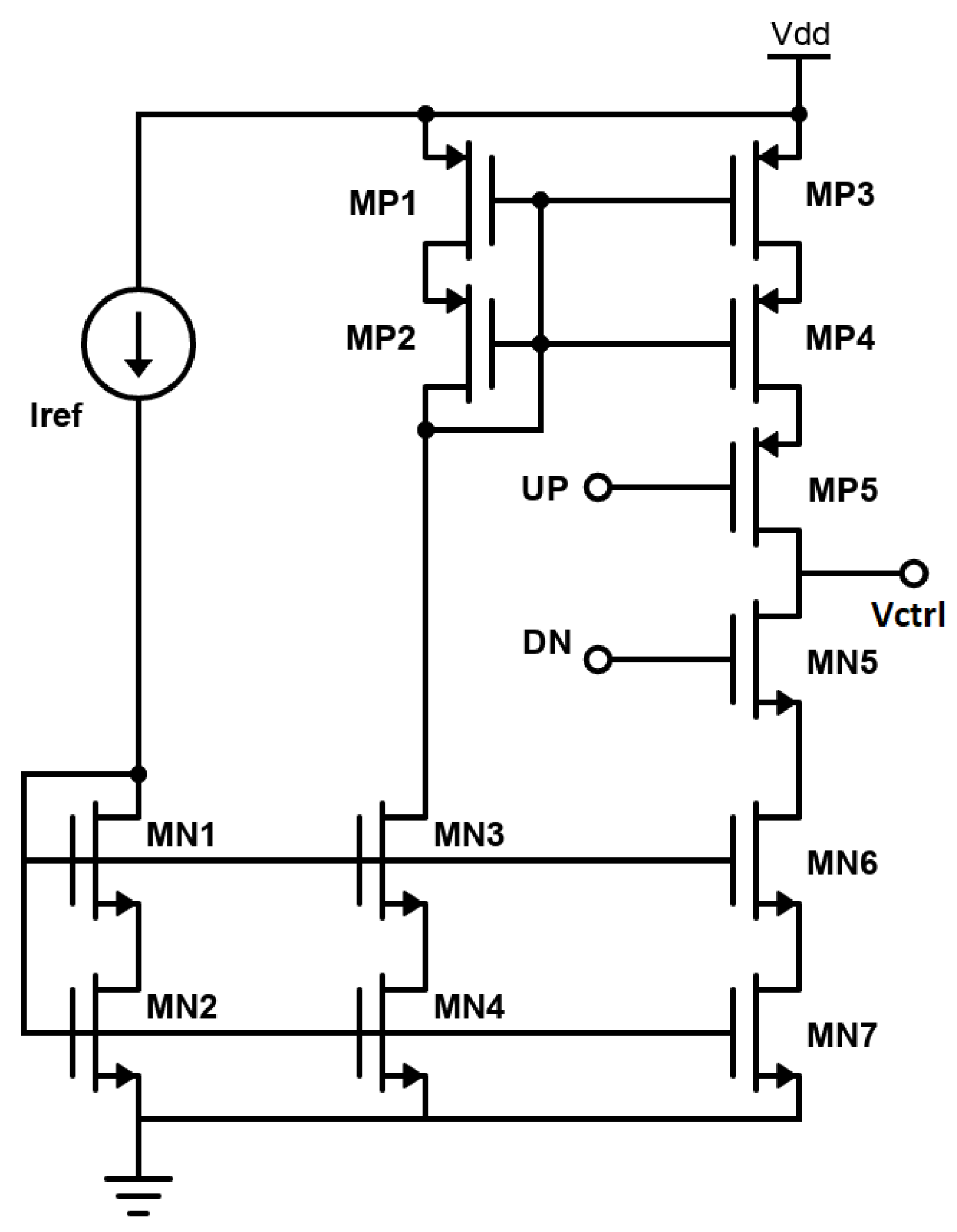

The implemented charge pump (CP) circuit is shown in

Figure 6. The CP is biased in the subthreshold region for low current consumption. Self-cascoded transistors are used in the current mirrors to boost the output resistance allowing a high output voltage swing. When the duty cycle is >50%, the UP signal is High, and the DN signal is Low so that C1 charges and Vctrl increases. This increase in Vctrl decreases the delay in the VCDL until the duty cycle becomes 50%. When the duty cycle is <50%, the UP signal is Low and the DN signal is High, thus correcting the duty cycle by decreasing Vctrl. This feedback loop ensures a 50% duty cycle across all PVT corners.

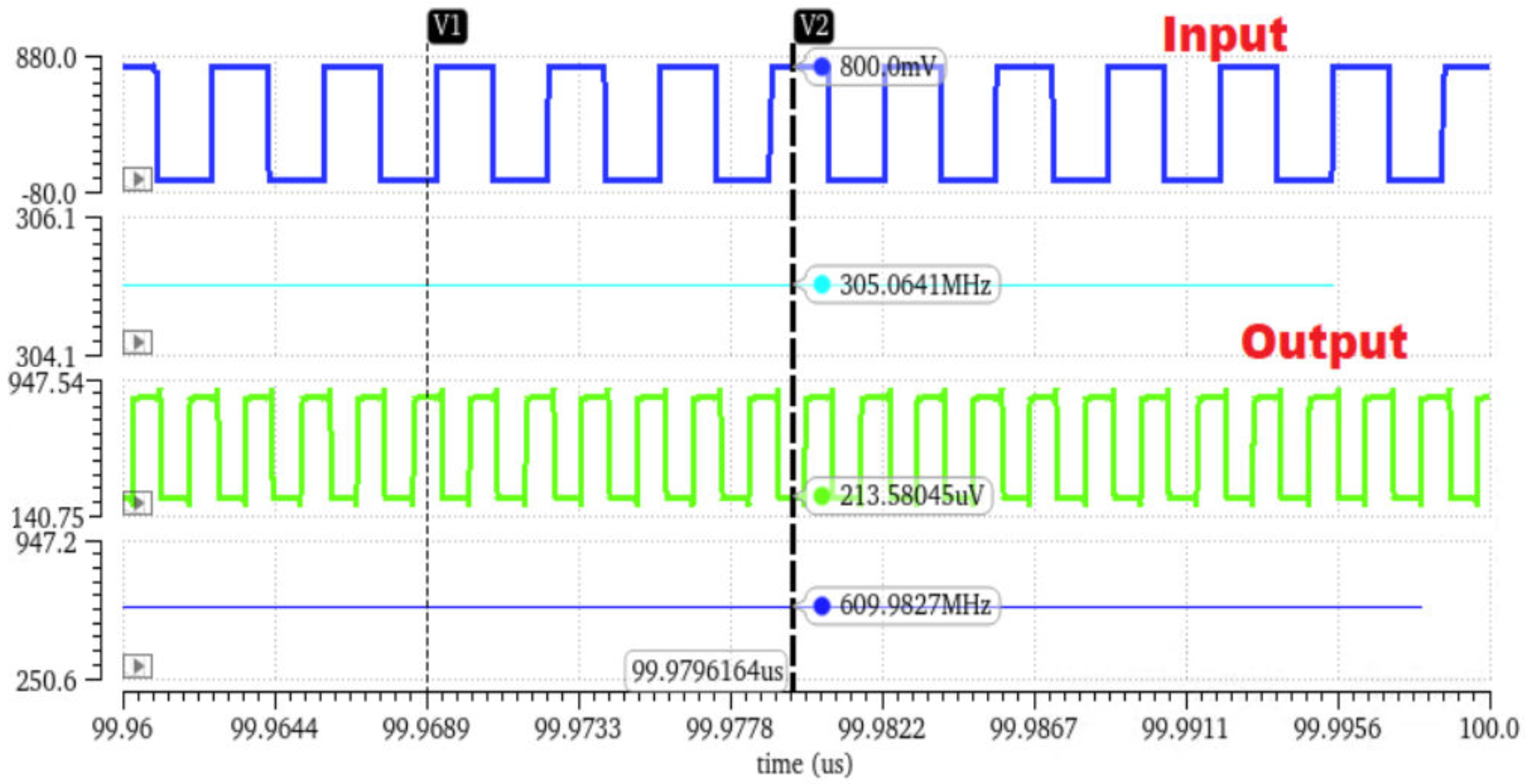

3.4. Simulation Results of a Single 2× Multiplication Stage

Figure 7 illustrates a transient simulation of a single stage of 2× frequency multiplication. The input frequency provided to the 2× multiplier is 305 MHz, yielding a 605 MHz signal at the output. Due to the action of the duty cycle correction loop, the circuit achieves a 50% duty cycle across all simulated process corners. The simulated power consumption of the 2× multiplier is approximately 40 μW at a 0.8 V supply.

For the implementation of DLL in this work, 22 nm FD-SOI (Fully Depleted Silicon-On-Insulator) process technology is used. FD-SOI transistor technology offers superior electrical performance due to its reduced parasitic capacitance, energy efficiency, and improved isolation as compared to the transistor fabricated over bulk silicon [

14], leading to enhanced signal integrity and lower power consumption. Additionally, the improved short-channel effects in FD-SOI contribute to better device scaling, allowing for the integration of more compact and efficient DLL components. Overall, the utilization of the FD-SOI process in DLL implementation promises superior performance, reduced power consumption, and increased design flexibility compared to traditional CMOS processes.

4. Experimental Results

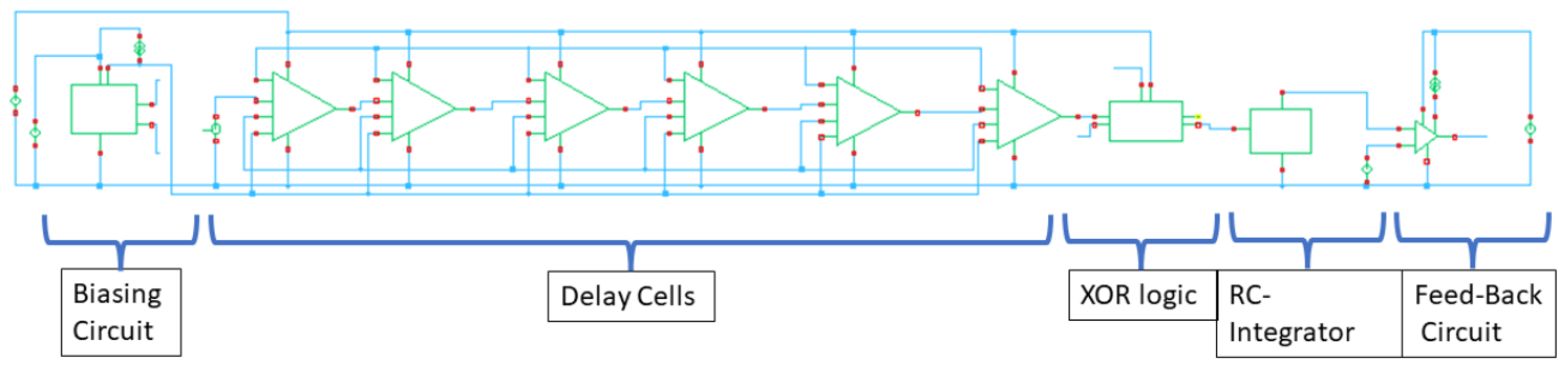

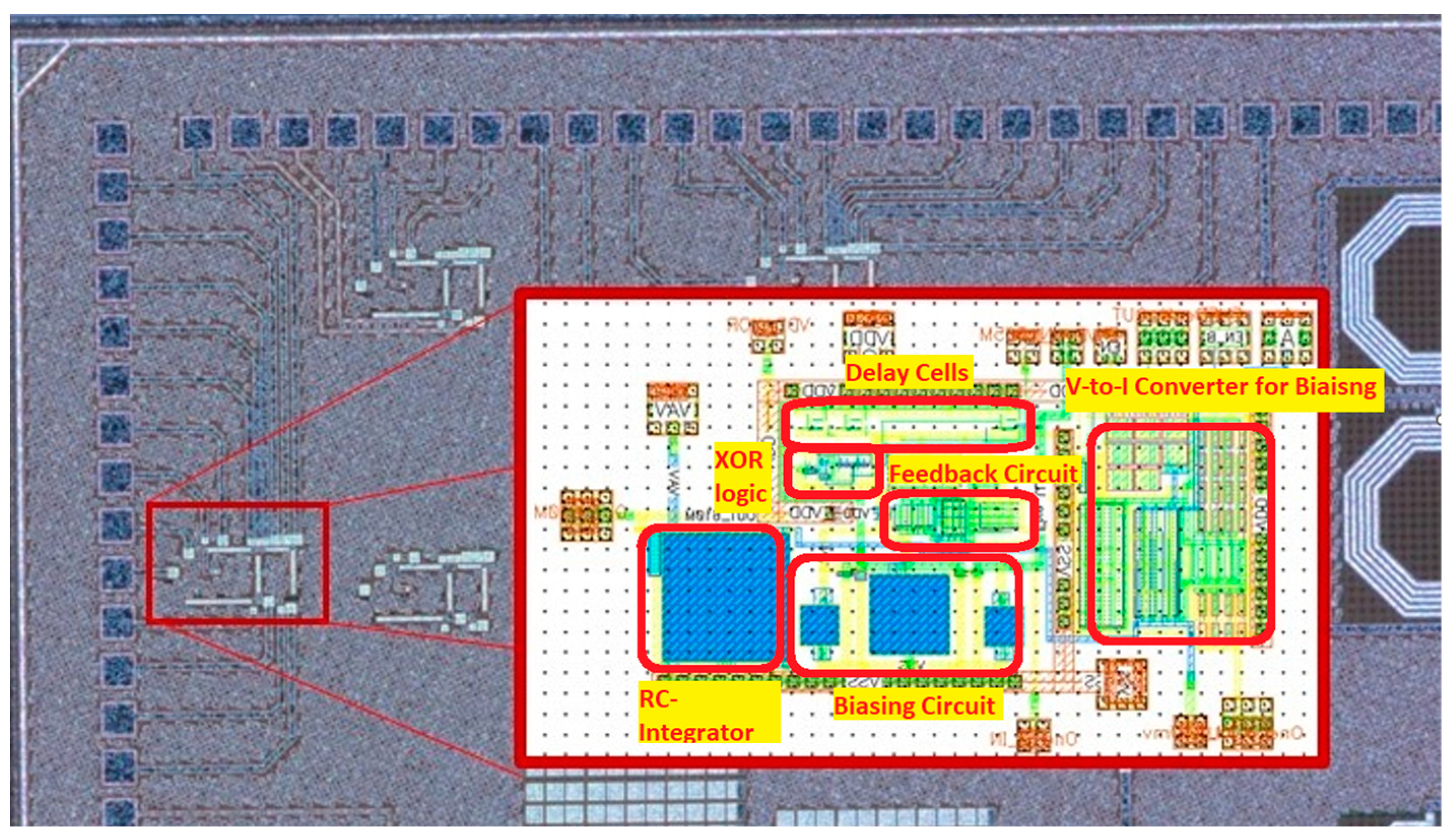

The circuit is implemented in 22 nm FD-SOI technology and is designed in Cadence Virtuoso. The block schematic of the 2× multiplier is shown in

Figure 8 which highlights all the sub-blocks of the circuit. The proposed 8× multiplication circuit occupies an active area of 0.09 mm

2. The layout and micrograph of the circuit is shown in

Figure 9.

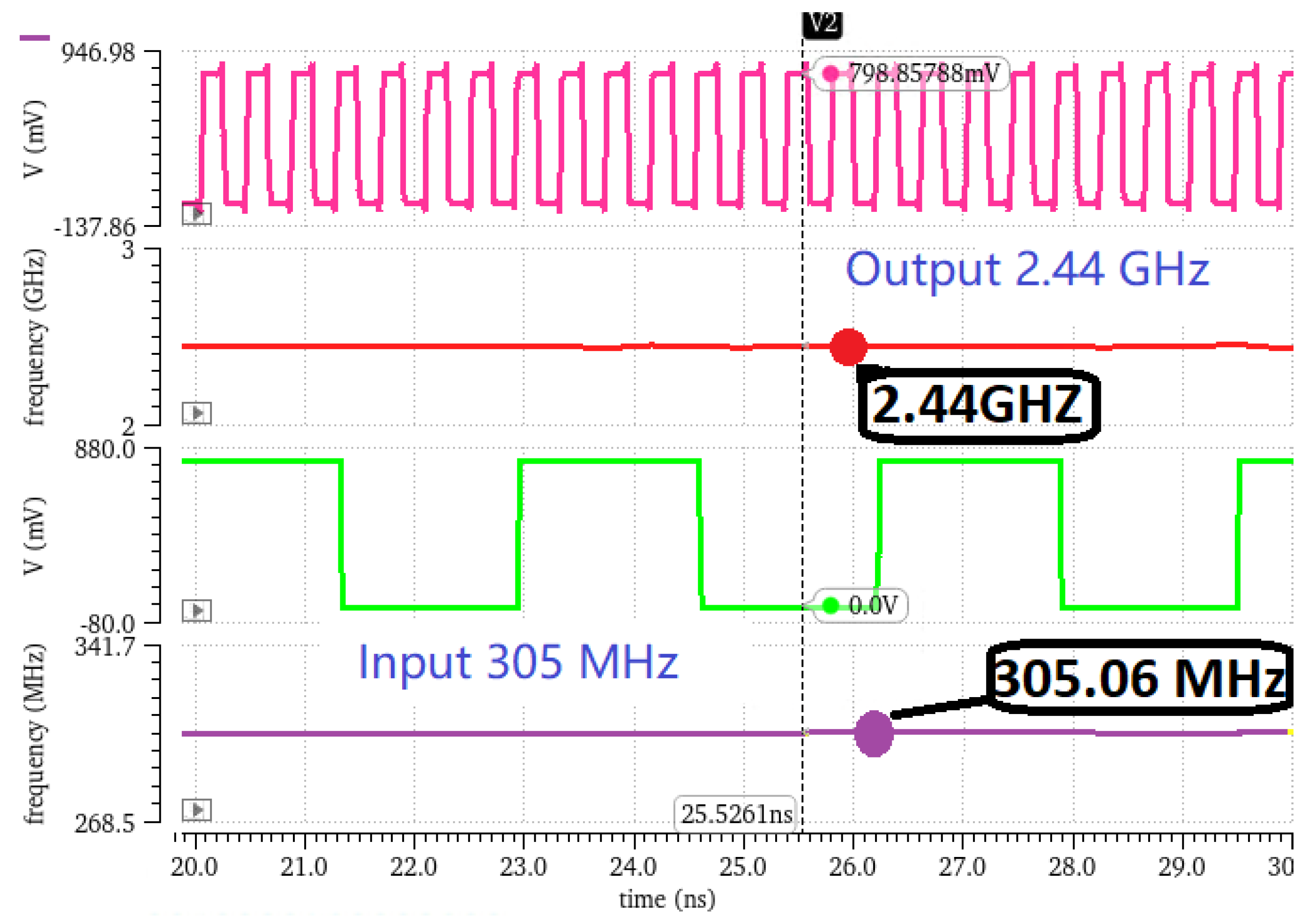

Figure 10 shows the post-layout performance of the 8× frequency multiplier. Here, 305 MHz is given as input frequency to the multiplier, which generates an output frequency of 2.44 GHz.

Figure 11 shows the action of the control loop to correct the duty cycle of the output signal. It takes about 40 μs to achieve a 50% duty cycle. The measured power consumption of the 8× multiplier is about 130 μW at 0.8 V.

The circuit passed all the post-layout process corner simulations for a temperature range of −20 to 110 °C while the supply voltage was kept constant at 0.8 V.

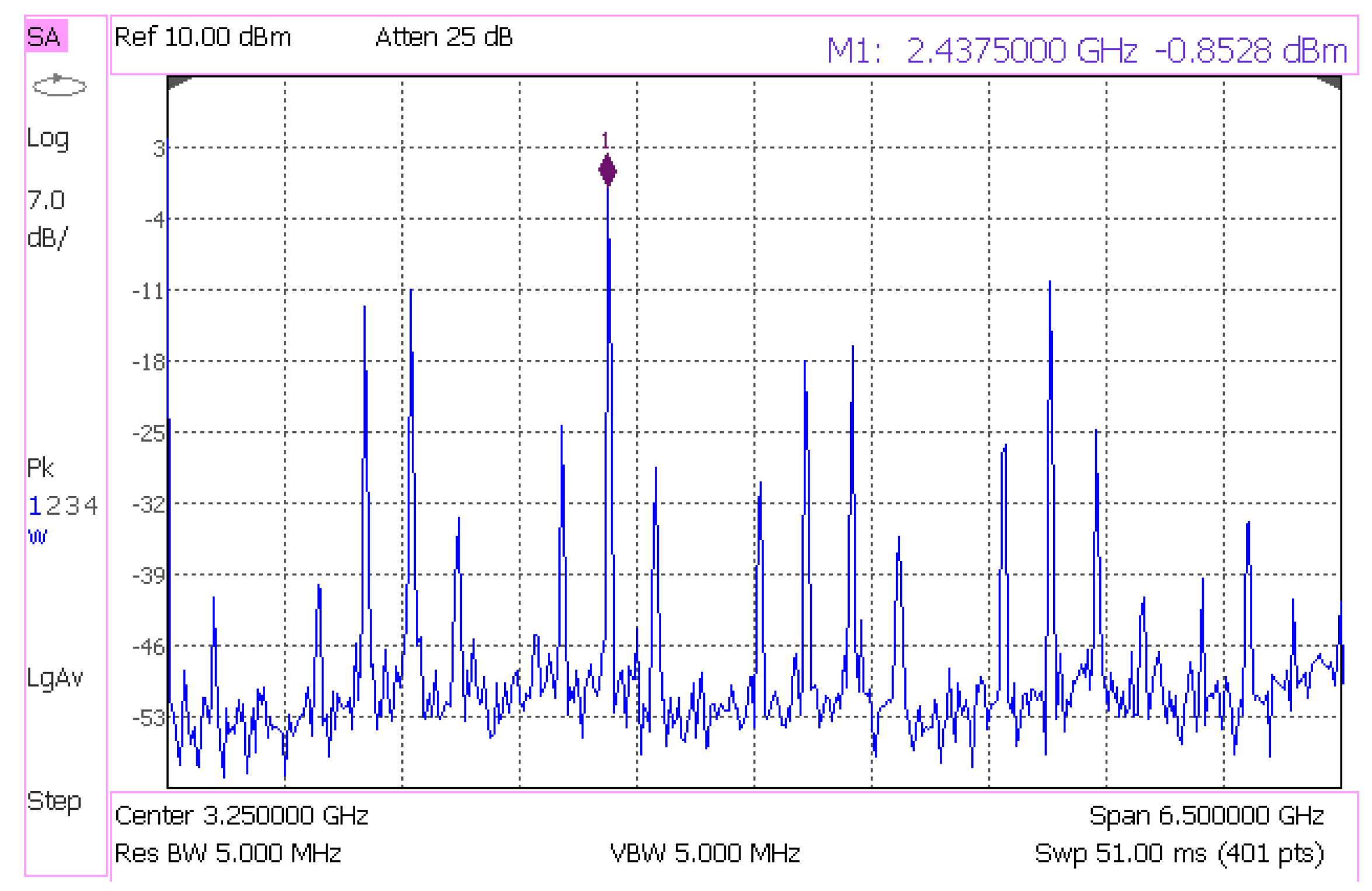

The DC offset of the OTAs for error corrections changes across process corners and appears as a static duty cycle error. This error can be seen as spurious tones in the output frequency spectrum. For all process and temperature corners, the duty cycle error remains in an acceptable range of −5% to 3%. For all the process and temperature corners, the number of delay stages is chosen such that the duty cycle error before correction is always positive. The observation shows that the feedback loop can correct a max duty cycle error of 30% before saturating.

Figure 12 shows the measured frequency spectrum of the output. The sideband harmonics power level is seen at least 25 dB lower than the carrier. The simulation shows a timing jitter of 24 ps (pk-pk).

A FOM (figure of merit) is derived from [

15] to make a performance comparison with the state of the art. Equation (1) calculates the FOM using multiplication factor (N), Power Consumption (Pdc), Process minimum length (L

min), operating bandwidth (BW in %), and Area (A). The comparison of performance is summarized in

Table 1. The proposed multiplier achieves the best FOM due to lower power consumption, wider operating bandwidth, and better multiplication factor/area ratio. Note that a lower FOM is an indication of better performance.

5. Conclusions

An XOR logic-based, low-power DLL frequency multiplier is presented. The circuit achieves 8× multiplication in three 2× stages. The design eliminates the need for edge combining, effectively minimizing the power consumption to 130 µW at 0.8 V supply. The circuit utilizes a new simpler duty cycle correction loop offering multiplication of a wide frequency. The duty cycle correction loop also ensures minimal duty cycle distortion across all PVT corners. A timing jitter of 24 ps (pk-pk) is observed at 2.44 GHz output comparable to the state-of-the-art options. The proposed design is a suitable low-power frequency multiplier for battery-less wireless sensor nodes.

Author Contributions

Conceptualization, N. and J.D.; methodology, N. and J.D.; software, N.; validation, N.; formal analysis, N.; investigation, N.; resources, J.D.; data curation, N.; writing—original draft preparation, N.; writing—review and editing, N. and J.D.; visualization, N. and J.D.; supervision, J.D.; project administration, J.D.; funding acquisition, J.D. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Data Availability Statement

Data are contained within the article.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Sansoy, M.; Buttar, A.S.; Goyal, R. Empowering Wireless Sensor Networks with RF Energy Harvesting. In Proceedings of the 2020 IEEE 7th International Conference on Signal Processing and Integrated Networks (SPIN), Noida, India, 27–28 February 2020; pp. 273–277. [Google Scholar]

- Hou, B.; Chen, H.; Wang, Z.; Mo, J.; Chen, J.; Yu, F.; Wang, W. A 11 mW 2.4 GHz 0.18 µm CMOS Transceivers for Wireless Sensor Networks. Sensors 2017, 17, 223. [Google Scholar] [CrossRef] [PubMed]

- Vauche, R.; Bergeret, E.; Gaubert, J.; Bourdel, S.; Fourquin, O.; Dehaese, N. A remotely UHF-powered UWB transmitter for high precision localization of RFID tag. In Proceedings of the 2011 IEEE International Conference on Ultra-Wideband (ICUWB), Bologna, Italy, 14–16 September 2011; pp. 494–498. [Google Scholar]

- Finkenzeller, K. RFID Handbook: Fundamentals and Applications in Contactless Smart Cards and Identification, 2nd ed.; Wiley: West Sussex, UK, 2003; pp. 134–136. [Google Scholar]

- Papotto, G.; Carrara, F.; Finocchiaro, A.; Palmisano, G. A 90-nm CMOS 5-Mbps crystal-less RF-powered transceiver for wireless sensor network nodes. IEEE J. Solid-State Circuits 2014, 40, 335–346. [Google Scholar] [CrossRef]

- Saavedra, C.E.; Zhang, Y. A clock frequency doubler using a passive integrator and emitter-coupled comparator circuit. In Proceedings of the 2004 IEEE Canadian Conference on Electrical and Computer Engineering, Niagara Falls, ON, Canada, 2–5 May 2004; Volume 1, pp. 137–140. [Google Scholar]

- Du, Q.; Zhuang, J.; Kwasniewski, T. A Low-Phase Noise, Anti-Harmonic Programmable DLL Frequency Multiplier with Period Error Compensation for Spur Reduction. IEEE Trans. Circuits Syst. II Expr. Briefs 2006, 53, 1205–1209. [Google Scholar] [CrossRef]

- Foley, D.J. CMOS DLL-Based 2-V 3.2-ps Jitter 1-GHz Clock Synthesizer and Temperature-Compensated Tunable Oscillator. IEEE J. Solid-State Circuits 2001, 36, 417–423. [Google Scholar] [CrossRef]

- Wei, G.-Y.; Stonick, J.T.; Weinlader, D.; Sonntag, J.; Searles, S. A 500MHz MP/DLL clock generator for a 5Gb/s backplane transceiver in 0.25 µm CMOS. In Proceedings of the 2003 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 3 February 2003; Volume 1, pp. 464–465. [Google Scholar]

- Farjad-Rad, R.; Dally, W.; Ng, H.T.; Senthinathan, R.; Lee, M.J.; Rathi, R.; Poulton, J. A Low-Power Multiplying DLL for Low-Jitter Multi-gigahertz Clock Generation. IEEE J. Solid-State Circuits 2002, 37, 1804–1811. [Google Scholar] [CrossRef]

- Cochet, M.; Clerc, S.; Naceur, M.; Schamberger, P.; Croain, D.; Autran, J.L.; Roche, P. A 28 nm FD-SOI standard cell 0.6–1.2 V open-loop frequency multiplier for low power SoC clocking. In Proceedings of the 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, Canada, 22–25 May 2016; pp. 1206–1209. [Google Scholar]

- Lee, W.; Dinc, T.; Valdes-Garcia, A. Reconfigurable 60-GHz Radar Transmitter SoC with Broadband Frequency Tripler in 45-nm SOI CMOS. In Proceedings of the 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2–4 June 2019; pp. 43–46. [Google Scholar]

- Balasubramaniyan, A.; Bellaouar, A. Digital Frequency Multiplier for LO Generation using 22-nm FDSOI. In Proceedings of the 2018 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Burlingame, CA, USA, 15 October 2018; pp. 1–2. [Google Scholar]

- Celis, J.-P.; Prakash, B. Chapter 4—Surface Modification of Materials by Plasma Immersion Ion Implantation. In European Materials Research Society Series, Materials Surface Processing by Directed Energy Techniques; Pauleau, Y., Ed.; Elsevier: Amsterdam, The Netherlands, 2006; pp. 111–149. [Google Scholar]

- Nam, K.-H.; Hong, N.-P.; Park, J.-S. A 16-Times Frequency Multiplier for 5G Synthesizer. IEEE Trans. Microw. Theory Tech. 2021, 69, 4961–4976. [Google Scholar] [CrossRef]

| Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).