Reduction of Interface State Density in 4H-SiC MOS Capacitors Modified by ALD-Deposited Interlayers

Abstract

1. Introduction

2. Experimental Methods

2.1. Fabrication of SiC MOS Capacitors

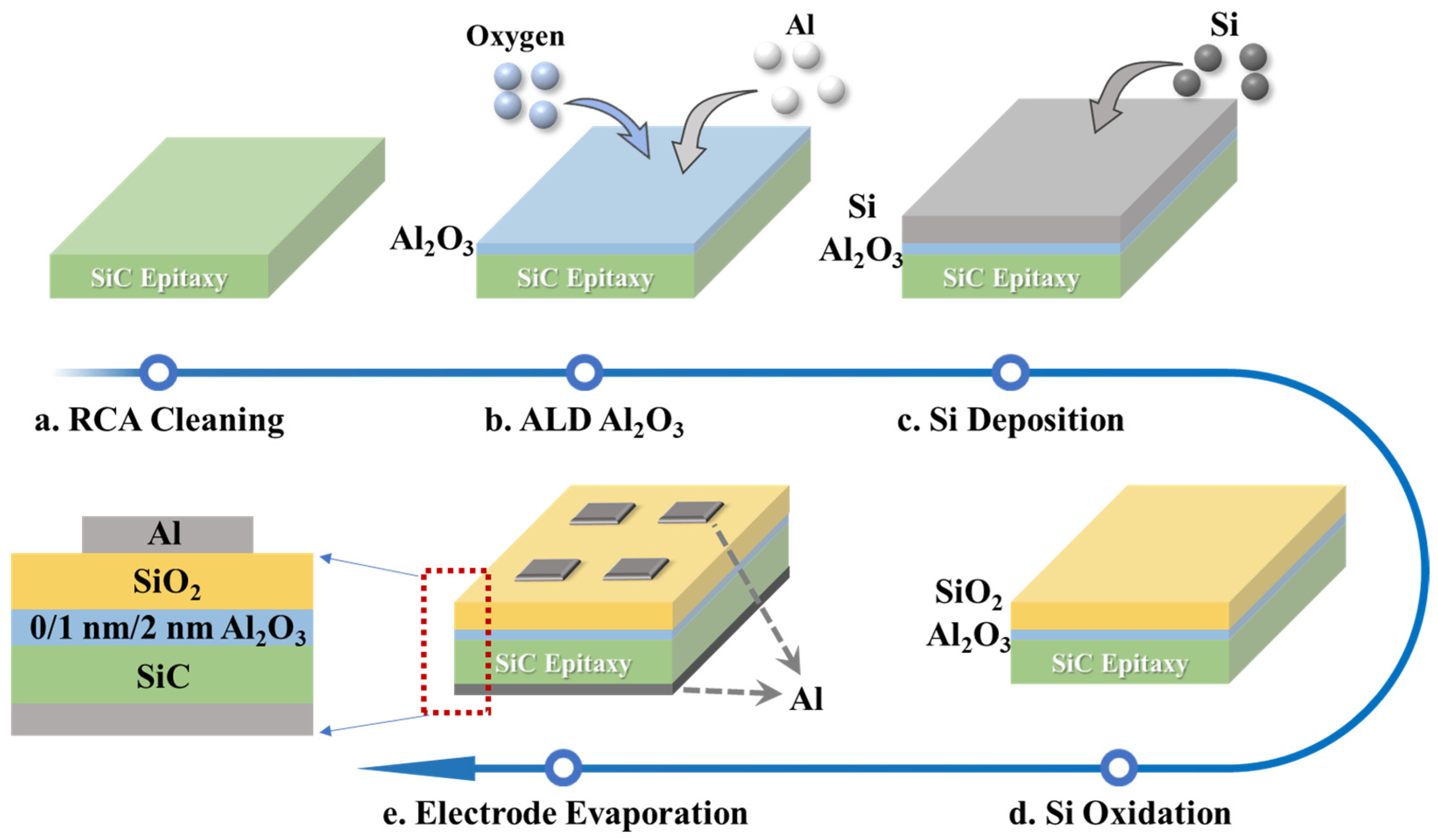

- (a)

- The SiC epitaxial wafers were subjected to RCA cleaning to remove surface impurities, ensuring that the wafer surface was clean for the smooth progression of subsequent processes.

- (b)

- Al2O3 was deposited on the epitaxial wafer surface using ALD technology with 10 and 20 cycles, while a sample without Al2O3 deposition was prepared as a control group.

- (c)

- A 20 nm thick Si layer was grown on the prepared three groups of samples in a conventional plasma-enhanced chemical vapor deposition (PECVD) system. The Si film was deposited using SiH4 gas highly diluted with H4. The PECVD system operated at a radio frequency of 13.56 MHz, a substrate temperature of 250 °C, and an r.f. power of 50 W.

- (d)

- The samples underwent wet oxidation at 1100 °C for 2 h, during which the PECVD-grown silicon films were fully oxidized into SiO2 layers, with consistent silicon growth and thermal oxidation conditions maintained across all samples to ensure experimental uniformity. The samples were classified as follows: SiO2/SiC-A sample without Al2O3 deposition; SiO2/1 nm-Al2O3/SiC-A sample with 10 cycles of Al2O3 passivation layers; SiO2/2 nm-Al2O3/SiC-A sample with 20 cycles of Al2O3 passivation layers.

- (e)

- After coating a layer of photoresist on the front side of the sample, hydrofluoric acid was used to remove the excess SiO2 from the back side of the samples. The photoresist was then removed, and square electrodes, 200 μm in width and 200 nm in thickness, were deposited on the front side using electron beam evaporation. Additionally, a 200 μm thick aluminum electrode was also deposited on the back side of the sample.

2.2. Characterization

3. Results and Discussion

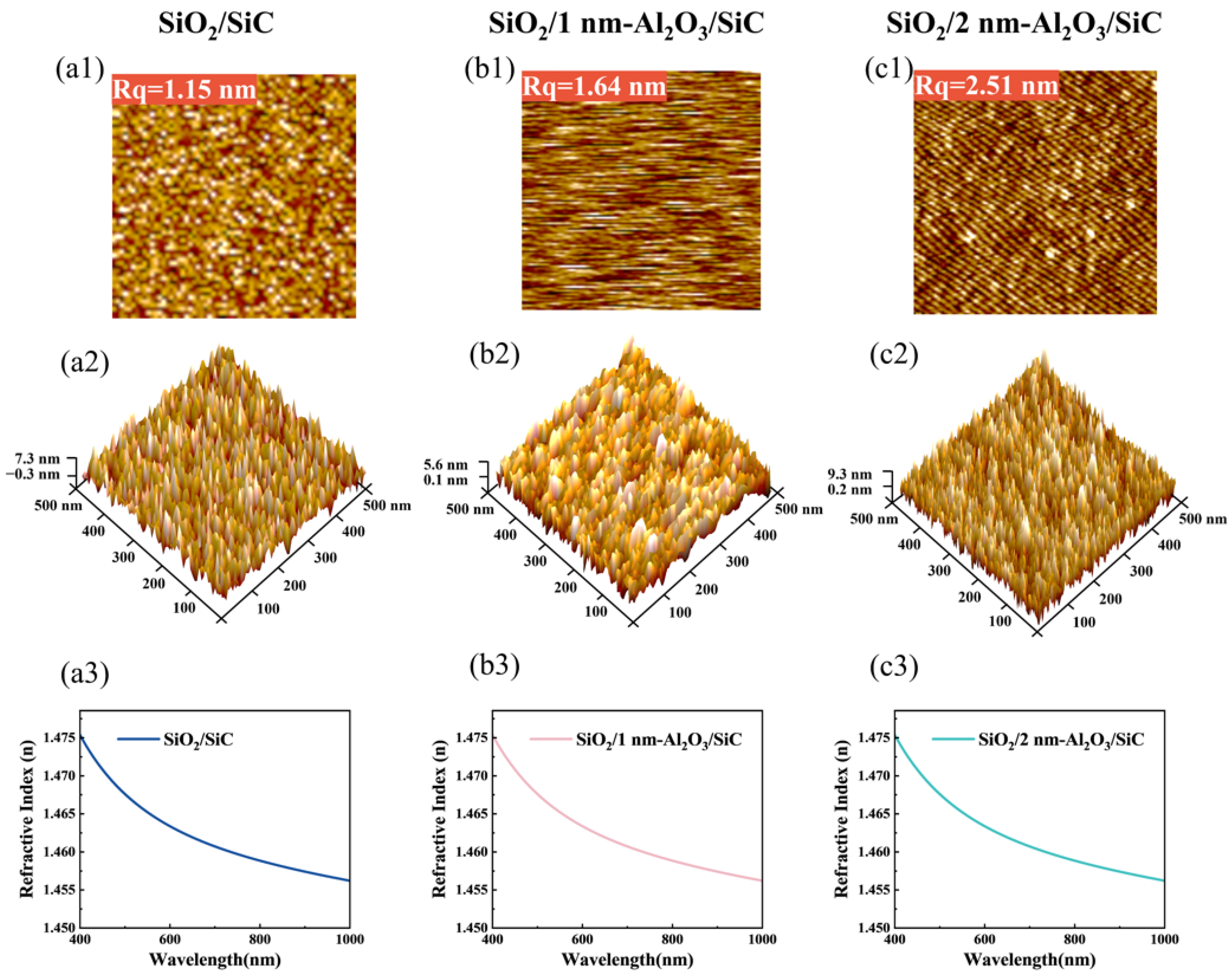

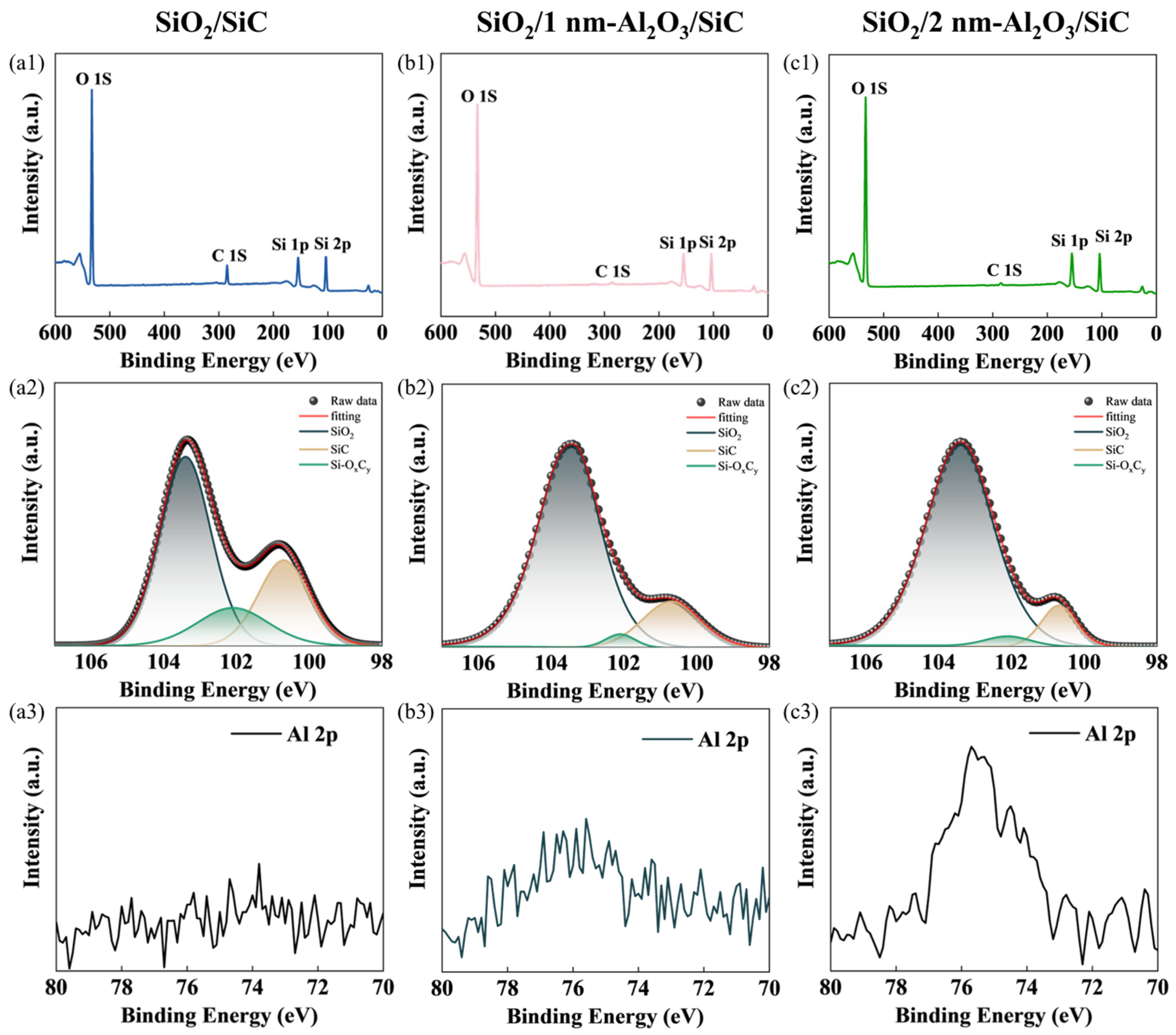

3.1. Interfacial Qualities and Characteristics of the SiO2 Films

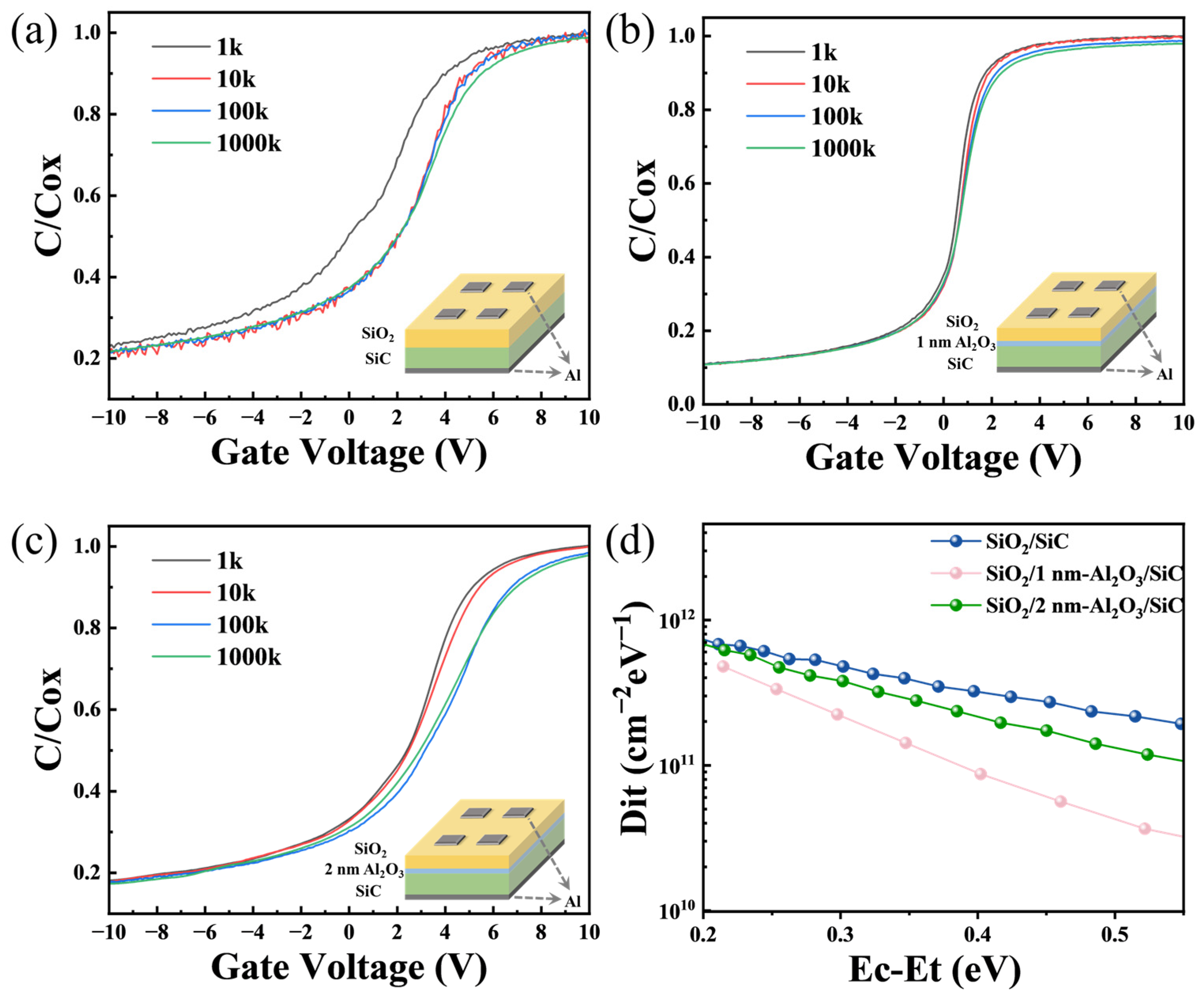

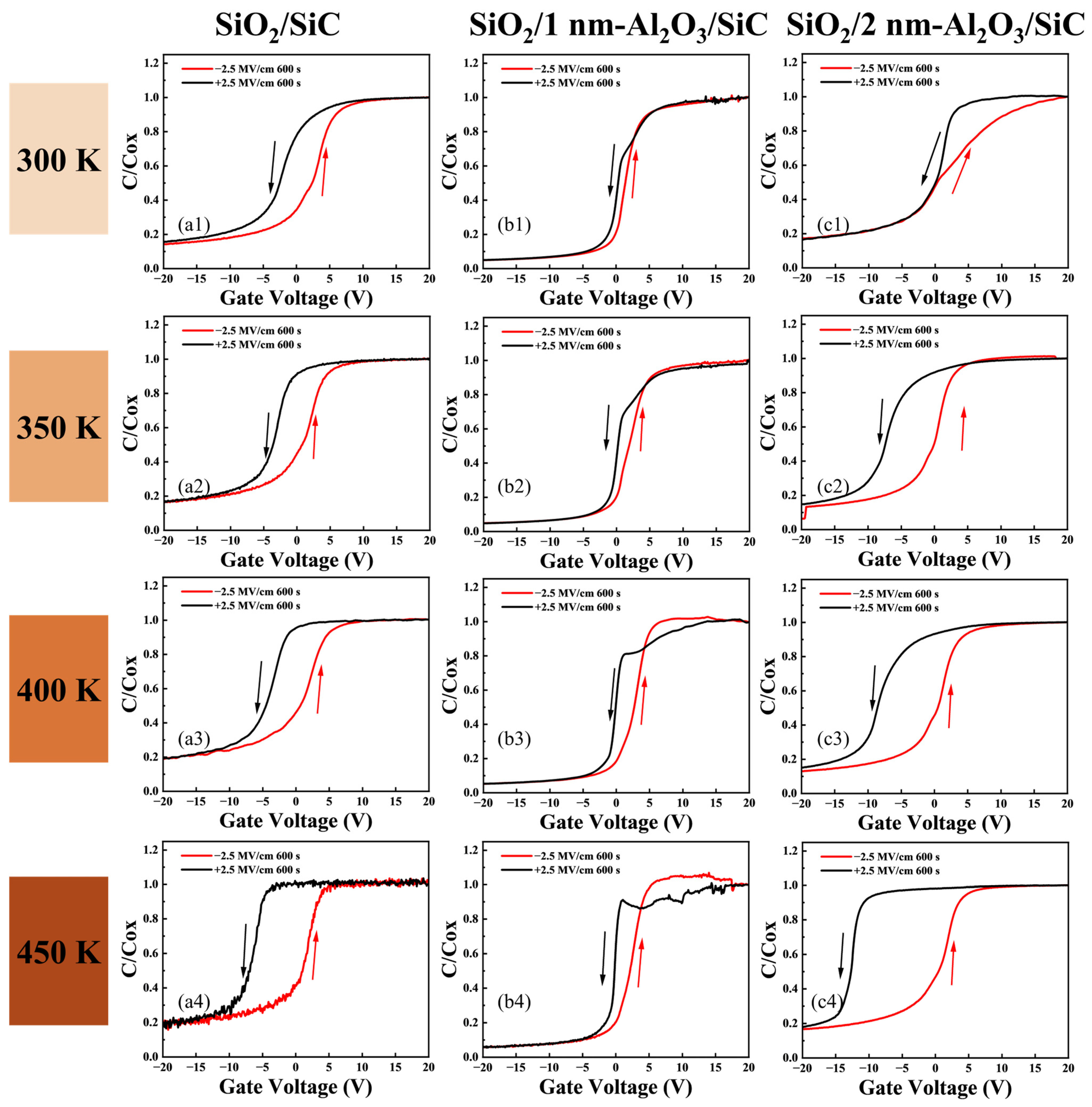

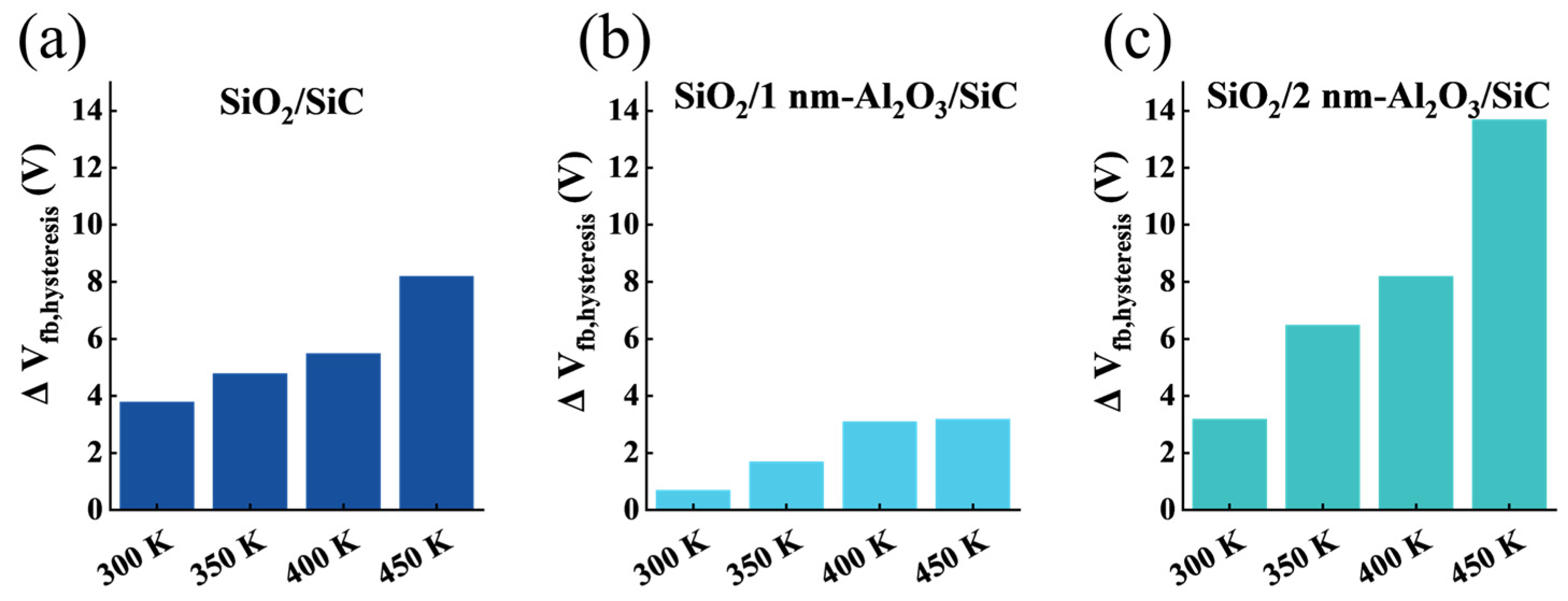

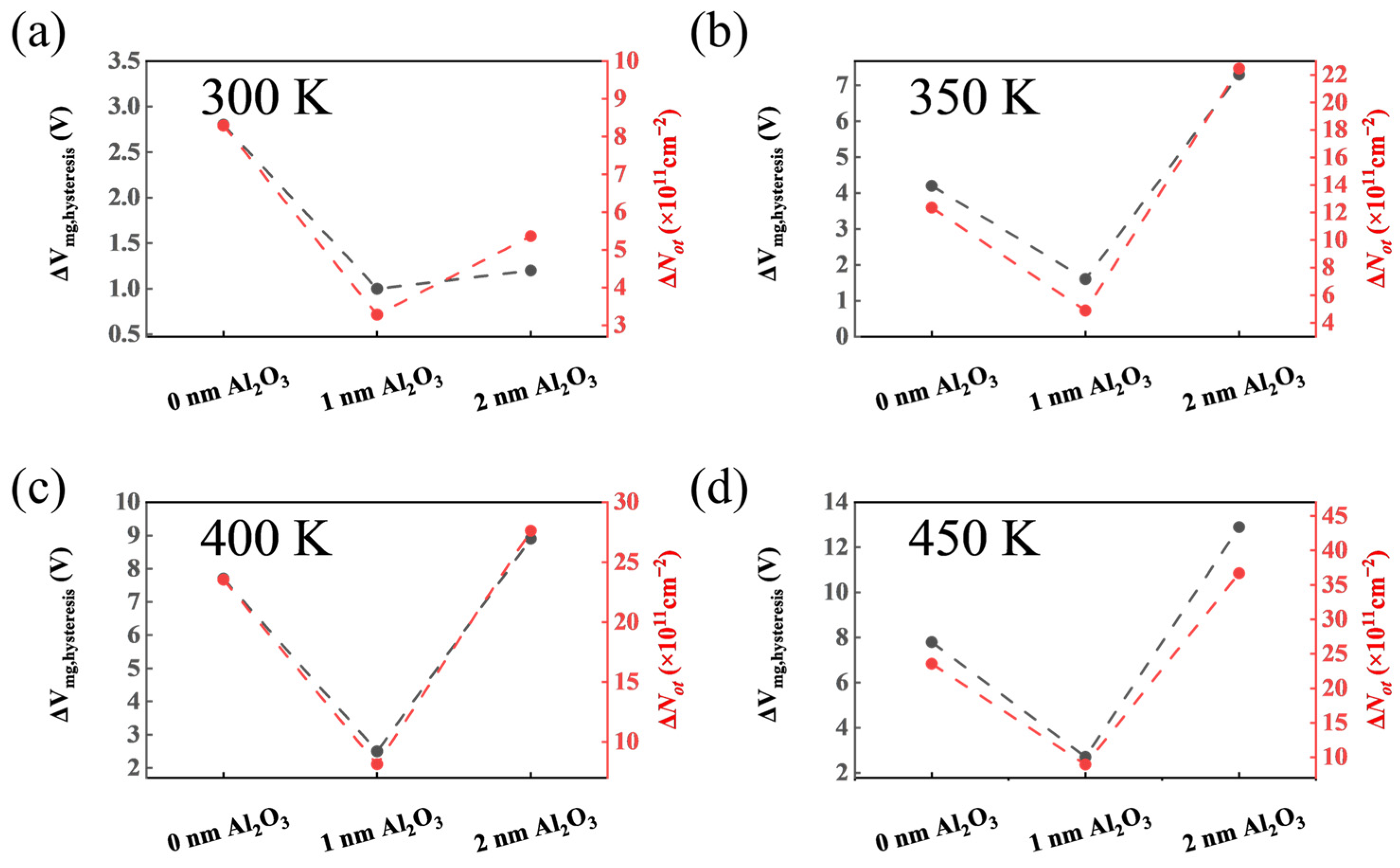

3.2. Thermal Stability of SiC MOS Capacitors

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Baliga, B.J. Silicon carbide power devices: Progress and future outlook. IEEE J. Emerg. Sel. Top. Power Electron. 2023, 11, 2400–2411. [Google Scholar]

- Liu, G.; Tuttle, B.R.; Dhar, S. Silicon carbide: A unique platform for metal-oxide-semiconductor physics. Appl. Phys. Rev. 2015, 2, 021307. [Google Scholar] [CrossRef]

- Millan, J.; Godignon, P.; Perpiñà, X.; Pérez-Tomás, A.; Rebollo, J. A survey of wide bandgap power semiconductor devices. IEEE Trans. Power Electron. 2013, 29, 2155–2163. [Google Scholar]

- Lipkin, L.; Palmour, J. Improved oxidation procedures for reduced SiO2/SiC defects. J. Electron. Mater. 1996, 25, 909–915. [Google Scholar]

- Roy, J.; Chandra, S.; Das, S.; Maitra, S. Oxidation behaviour of silicon carbide—A review. Rev. Adv. Mater. Sci. 2014, 38, 29–39. [Google Scholar]

- Wang, Y.; Ding, Y.; Yin, Y. Reliability of wide band gap power electronic semiconductor and packaging: A review. Energies 2022, 15, 6670. [Google Scholar] [CrossRef]

- Cabello, M.; Soler, V.; Rius, G.; Montserrat, J.; Rebollo, J.; Godignon, P. Advanced processing for mobility improvement in 4H-SiC MOSFETs: A review. Mater. Sci. Semicond. Process. 2018, 78, 22–31. [Google Scholar]

- Pande, P.; Haasmann, D.; Han, J.; Moghadam, H.A.; Tanner, P.; Dimitrijev, S. Electrical characterization of SiC MOS capacitors: A critical review. Microelectron. Reliab. 2020, 112, 113790. [Google Scholar] [CrossRef]

- Buffolo, M.; Favero, D.; Marcuzzi, A.; De Santi, C.; Meneghesso, G.; Zanoni, E.; Meneghini, M. Review and outlook on GaN and SiC power devices: Industrial state-of-the-art, applications, and perspectives. IEEE Trans. Electron Devices 2024, 71, 1344–1355. [Google Scholar]

- Zhang, Q.; You, N.; Liu, P.; Wang, J.; Xu, Y.; Wang, S. Study of defects distribution in SiO2/SiC with plasma oxidation and post oxidation annealing. Appl. Surf. Sci. 2023, 610, 155500. [Google Scholar]

- Zhang, Q.; You, N.; Wang, J.; Xu, Y.; Zhang, K.; Wang, S. Effect of Temperature-Dependent Low Oxygen Partial Pressure Annealing on SiC MOS. Nanomaterials 2024, 14, 192. [Google Scholar] [CrossRef] [PubMed]

- Sharma, Y.; Ahyi, A.; Issacs-Smith, T.; Shen, X.; Pantelides, S.; Zhu, X.; Feldman, L.; Rozen, J.; Williams, J. Phosphorous passivation of the SiO2/4H–SiC interface Solid-State. Electronics 2012, 68, 103–107. [Google Scholar]

- Okamoto, D.; Sometani, M.; Harada, S.; Kosugi, R.; Yonezawa, Y.; Yano, H. Improved channel mobility in 4H-SiC MOSFETs by boron passivation. IEEE Electron Device Lett. 2014, 35, 1176–1178. [Google Scholar] [CrossRef]

- Wang, R.; Noguchi, M.; Watanabe, H.; Kita, K. Dependence of the incorporated boron concentration near SiO2/4H–SiC interface on trap passivation reduction. AIP Adv. 2024, 14, 075304. [Google Scholar] [CrossRef]

- Okamoto, D.; Sometani, M.; Harada, S.; Kosugi, R.; Yonezawa, Y.; Yano, H. Effect of boron incorporation on slow interface traps in SiO2/4H-SiC structures. Appl. Phys. A 2017, 123, 133. [Google Scholar] [CrossRef]

- Zheng, Y.; Isaacs-Smith, T.; Ahyi, A.; Dhar, S. 4H-SiC MOSFETs with borosilicate glass gate dielectric and antimony counter-doping. IEEE Electron Device Lett. 2017, 38, 1433–1436. [Google Scholar] [CrossRef]

- Jia, Y.; Lv, H.; Tang, X.; Han, C.; Song, Q.; Zhang, Y.; Zhang, Y.; Dimitrijev, S.; Han, J. Growth and characterization of nitrogen-phosphorus hybrid passivated gate oxide film on N-type 4H-SiC epilayer. J. Cryst. Growth 2019, 507, 98–102. [Google Scholar] [CrossRef]

- Kobayashi, T.; Okuda, T.; Tachiki, K.; Ito, K.; Matsushita, Y.-I.; Kimoto, T. Design and formation of SiC (0001)/SiO2 interfaces via Si deposition followed by low-temperature oxidation and high-temperature nitridation. Appl. Phys. Express 2020, 13, 091003. [Google Scholar] [CrossRef]

- Li, Y.; Zhao, S.; Wei, M.; Jiao, J.; Yan, G.; Liu, X. Preparation and oxidation characteristics of Si layers grown on 4H–SiC substrates. Vacuum 2024, 227, 113418. [Google Scholar] [CrossRef]

- Nigro, R.L.; Fiorenza, P.; Greco, G.; Schilirò, E.; Roccaforte, F. Structural and insulating behaviour of high-permittivity binary oxide thin films for silicon carbide and gallium nitride electronic devices. Materials 2022, 15, 830. [Google Scholar] [CrossRef]

- Siddiqui, A.; Khosa, R.Y.; Usman, M. High-k dielectrics for 4H-silicon carbide: Present status and future perspectives. J. Mater. Chem. C 2021, 9, 5055–5081. [Google Scholar] [CrossRef]

- Wirths, S.; Arango, Y.; Mihaila, A.; Bellini, M.; Romano, G.; Alfieri, G.; Belanche, M.; Knoll, L.; Bianda, E.; Mengotti, E. Vertical power SiC MOSFETs with high-k gate dielectrics and superior threshold voltage stability. In Proceedings of the 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), IEEE, Vienna, Austria, 13–18 September 2020; pp. 226–229. [Google Scholar]

- Chang, P.; Hwu, J. Electrical characterization of 4H-SiC metal–oxide–semiconductor structure with Al2O3 stacking layers as dielectric. Appl. Phys. A 2018, 124, 87. [Google Scholar] [CrossRef]

- Khosa, R.Y.; Thorsteinsson, E.; Winters, M.; Rorsman, N.; Karhu, R.; Hassan, J.; Sveinbjörnsson, E. Electrical characterization of amorphous Al2O3 dielectric films on n-type 4H-SiC. Aip Adv. 2018, 8, 025304. [Google Scholar]

- Shukla, M.; Dutta, G.; Mannam, R.; DasGupta, N. Electrical properties of reactive-ion-sputtered Al2O3 on 4H-SiC. Thin Solid Film. 2016, 607, 1–6. [Google Scholar]

- Qin, B.; Liu, S.; You, N.; Liu, J.; Li, X.; Wang, S.; Li, X. Lowering of interface state density between deposited gate oxide and SiC substrate via controlling substrate oxidation. Vacuum 2024, 222, 112999. [Google Scholar]

- Schilirò, E.; Fiorenza, P.; Di Franco, S.; Bongiorno, C.; Saggio, M.; Roccaforte, F.; Nigro, R.L. Effect of SiO2 interlayer on the properties of Al2O3 thin films grown by plasma enhanced atomic layer deposition on 4H-SiC substrates. Phys. Status Solidi (a) 2017, 214, 1600365. [Google Scholar] [CrossRef]

- Chen, X.; Ge, L.; Cheong, K.Y.; Han, J.; Phan, H.-P.; Xu, M. Performance improvement of silicon carbide gate oxide interface by pre-oxidation. Appl. Surf. Sci. 2025, 688, 162359. [Google Scholar]

- Corrêa, S.A.; Marmitt, G.G.; Bom, N.M.; Da Rosa, A.; Stedile, F.C.; Radtke, C.; Soares, G.V.; Baumvol, I.J.R.; Krug, C.; Gobbi, A.L. Enhancement in interface robustness regarding thermal oxidation in nanostructured Al2O3 deposited on 4H-SiC. Appl. Phys. Lett. 2009, 95, 051916. [Google Scholar]

- Lu, J.; He, G.; Wang, W.; Jiang, S.; Wu, Q.; Fang, Z. Interface chemistry and defect state optimization of the ErSmO/InP heterojunction modified by ALD-driven Al2O3 interlayers. ACS Appl. Electron. Mater. 2023, 5, 935–947. [Google Scholar] [CrossRef]

- Shao, Z.; Xu, H.; Wang, H.; Ren, N.; Sheng, K. Saturation thickness of stacked SiO2 in atomic-layer-deposited Al2O3 gate on 4H-SiC. Chin. Phys. B 2023, 32, 087106. [Google Scholar]

- Yin, Z.; Wei, S.; Bai, J.; Xie, W.; Qin, F.; Wang, D. SiC/SiO2 interface properties formed by low-temperature ozone re-oxidation annealing. Ceram. Int. 2022, 48, 10874–10884. [Google Scholar]

- Wei, S.; Bai, J.; Xie, W.; Su, Y.; Qin, F.; Wang, D. Reliability and stability improvement of MOS capacitors via nitrogen–hydrogen mixed plasma pretreatment for SiC surfaces. ACS Appl. Mater. Interfaces 2023, 15, 18537–18549. [Google Scholar] [PubMed]

- Yang, C.; Yin, Z.; Zhang, F.; Su, Y.; Qin, F.; Wang, D. Synergistic passivation effects of nitrogen plasma and oxygen plasma on improving the interface quality and bias temperature instability of 4H-SiC MOS capacitors. Appl. Surf. Sci. 2020, 513, 145837. [Google Scholar]

- Guo, Y.-D.; Wang, A.-F.; Huang, Q.-M.; Wang, Z.-Y.; Ma, H.-P.; Zhang, Q. Performance Comparison of Al2O3 Gate Dielectric Grown on 4H-SiC Substrates via Thermal and Plasma-Enhanced Atomic Layer Deposition Methods. ECS J. Solid State Sci. Technol. 2025, 14, 023005. [Google Scholar]

- Lee, E.; Kim, T.H.; Lee, S.W.; Kim, J.H.; Kim, J.; Jeong, T.G.; Ahn, J.-H.; Cho, B. Improved electrical performance of a sol–gel IGZO transistor with high-k Al2O3 gate dielectric achieved by post annealing. Nano Converg. 2019, 6, 24. [Google Scholar]

- Nunomura, S.; Ota, H.; Irisawa, T.; Endo, K.; Morita, Y. Defect generation and recovery in high-k HfO2/SiO2/Si stack fabrication. Appl. Phys. Express 2023, 16, 061004. [Google Scholar]

- Kim, C.; Moon, J.H.; Yim, J.H.; Lee, D.H.; Lee, J.H.; Lee, H.H.; Kim, H.J. Comparison of thermal and atomic-layer-deposited oxides on 4H-SiC after post-oxidation-annealing in nitric oxide. Appl. Phys. Lett. 2012, 100, 082112. [Google Scholar]

- Chanana, R.K. Determination of hole effective mass in SiO2 and SiC conduction band offset using Fowler–Nordheim tunneling characteristics across metal-oxide-semiconductor structures after applying oxide field corrections. J. Appl. Phys. 2011, 109, 104508. [Google Scholar]

- Wang, Z.; Lin, Z.; Li, J.; Liu, W. Low-pressure oxidation for improving interface properties and voltage instability of SiO2/4H-SiC MOS capacitor. Appl. Surf. Sci. 2025, 681, 161604. [Google Scholar] [CrossRef]

- Chanthaphan, A.; Hosoi, T.; Mitani, S.; Nakano, Y.; Nakamura, T.; Shimura, T.; Watanabe, H. Investigation of unusual mobile ion effects in thermally grown SiO2 on 4H-SiC (0001) at high temperatures. Appl. Phys. Lett. 2012, 100, 252103. [Google Scholar]

| Theoretical [28] | SiO2/SiC | SiO2/1 nm-Al2O3/SiC | SiO2/2 nm-Al2O3/SiC | |

|---|---|---|---|---|

| φB (eV) @25 °C | 2.7 | 2.15 | 2.51 | 2.37 |

| Ebd (MV cm−1) | 10 | 9.64 | 10.9 | 9.94 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, Z.; Bai, Z.; Guo, Y.; Ding, C.; Huang, Q.; Gu, L.; Shen, Y.; Zhang, Q.; Ma, H. Reduction of Interface State Density in 4H-SiC MOS Capacitors Modified by ALD-Deposited Interlayers. Nanomaterials 2025, 15, 555. https://doi.org/10.3390/nano15070555

Wang Z, Bai Z, Guo Y, Ding C, Huang Q, Gu L, Shen Y, Zhang Q, Ma H. Reduction of Interface State Density in 4H-SiC MOS Capacitors Modified by ALD-Deposited Interlayers. Nanomaterials. 2025; 15(7):555. https://doi.org/10.3390/nano15070555

Chicago/Turabian StyleWang, Zhenyu, Zhaopeng Bai, Yunduo Guo, Chengxi Ding, Qimin Huang, Lin Gu, Yi Shen, Qingchun Zhang, and Hongping Ma. 2025. "Reduction of Interface State Density in 4H-SiC MOS Capacitors Modified by ALD-Deposited Interlayers" Nanomaterials 15, no. 7: 555. https://doi.org/10.3390/nano15070555

APA StyleWang, Z., Bai, Z., Guo, Y., Ding, C., Huang, Q., Gu, L., Shen, Y., Zhang, Q., & Ma, H. (2025). Reduction of Interface State Density in 4H-SiC MOS Capacitors Modified by ALD-Deposited Interlayers. Nanomaterials, 15(7), 555. https://doi.org/10.3390/nano15070555