Photogating Regimes in Graphene: Memory-Bearing and Reset-Free Operation

Abstract

1. Introduction

2. Device Fabrication

3. Results and Discussion

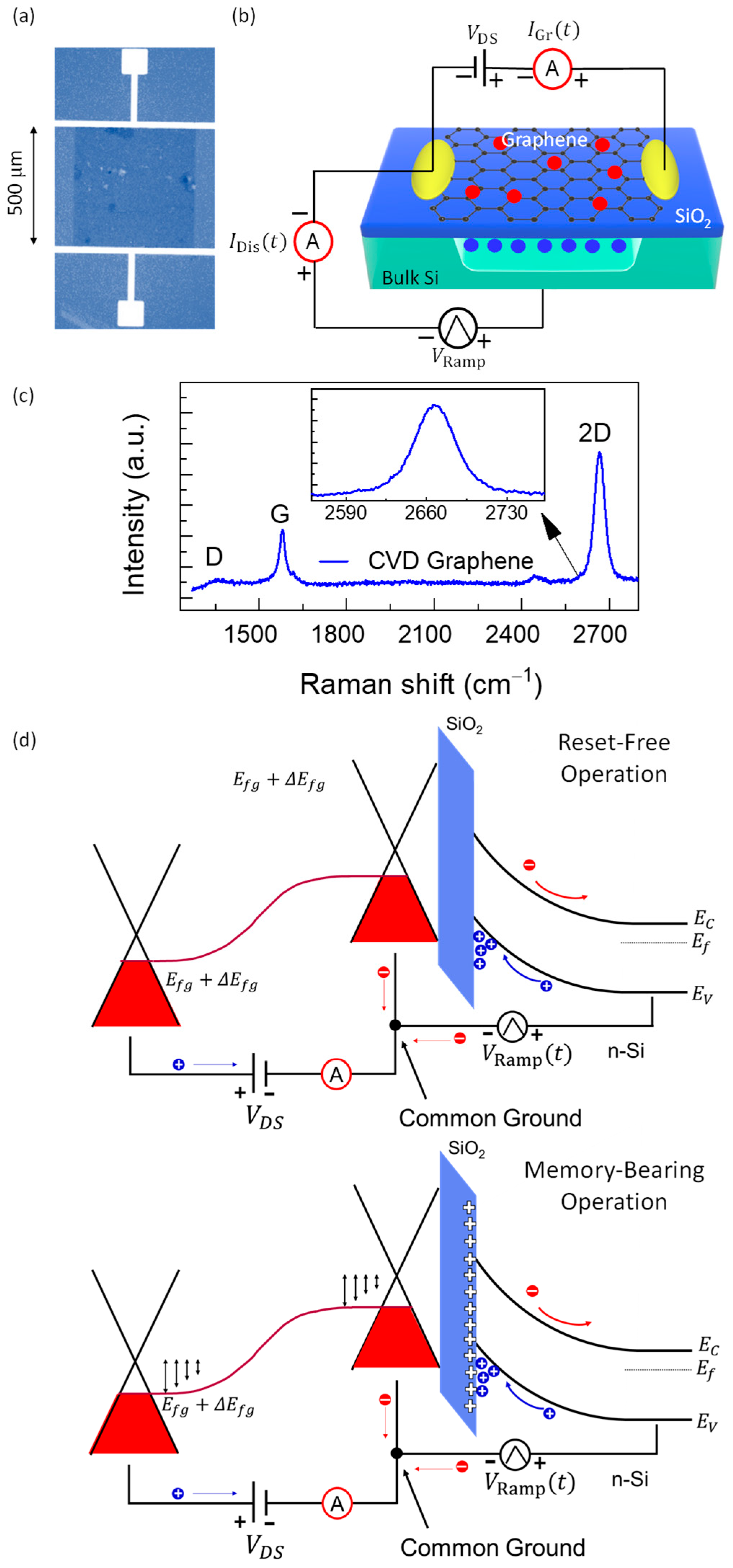

3.1. Device Layout, Measurement Scheme, and Operating Band Diagram

3.2. Performance Parameters

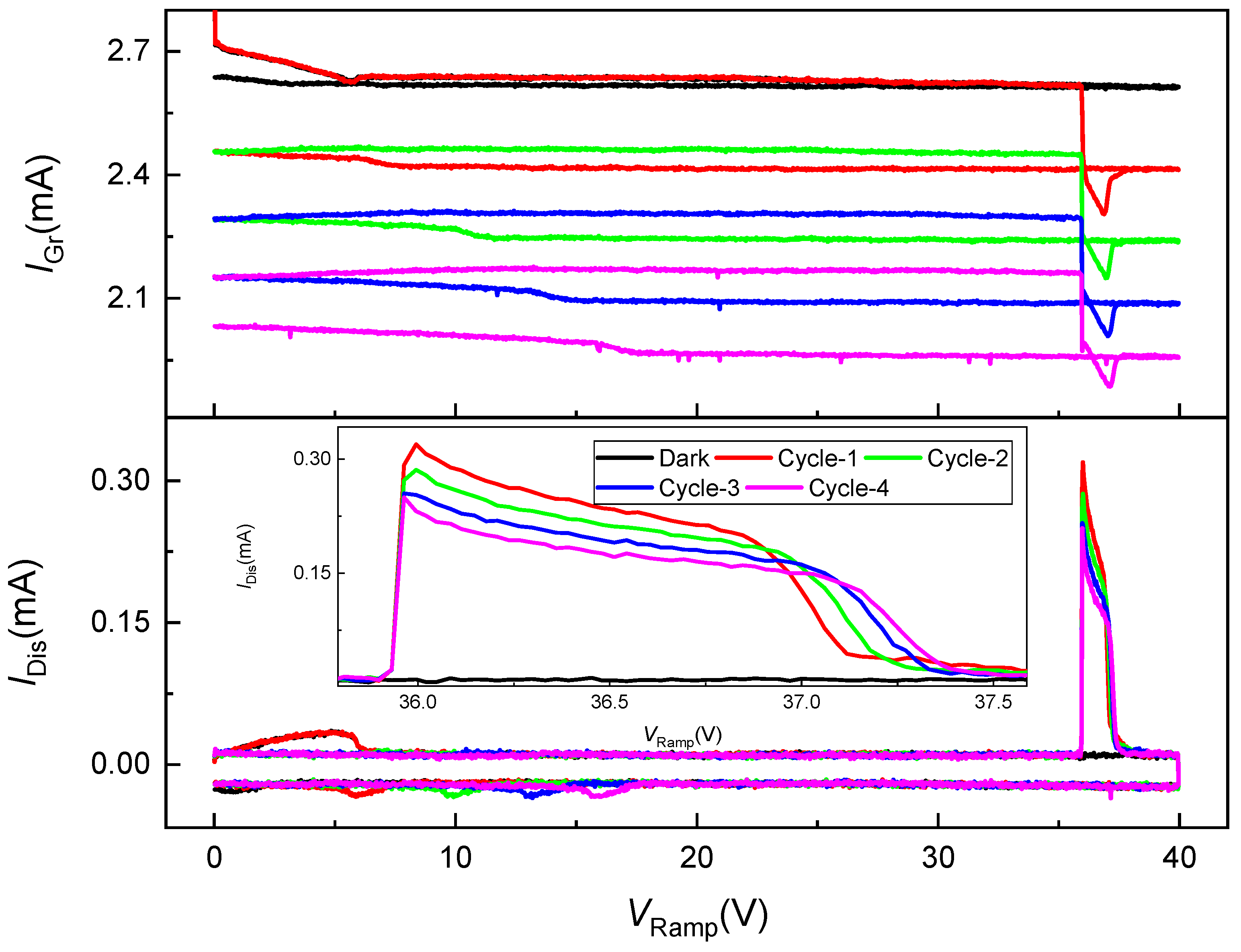

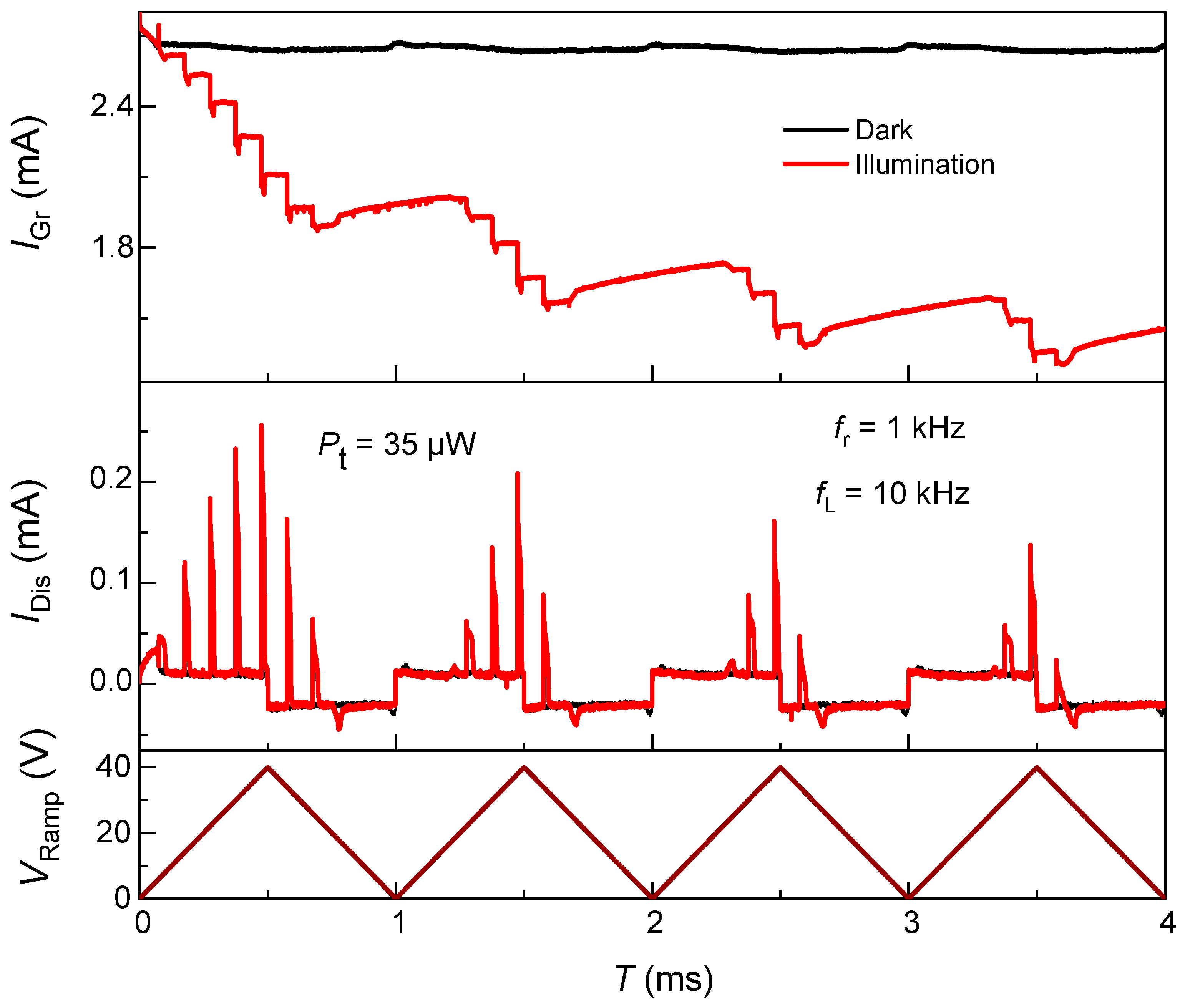

3.3. Memory-Bearing Operation: Device A

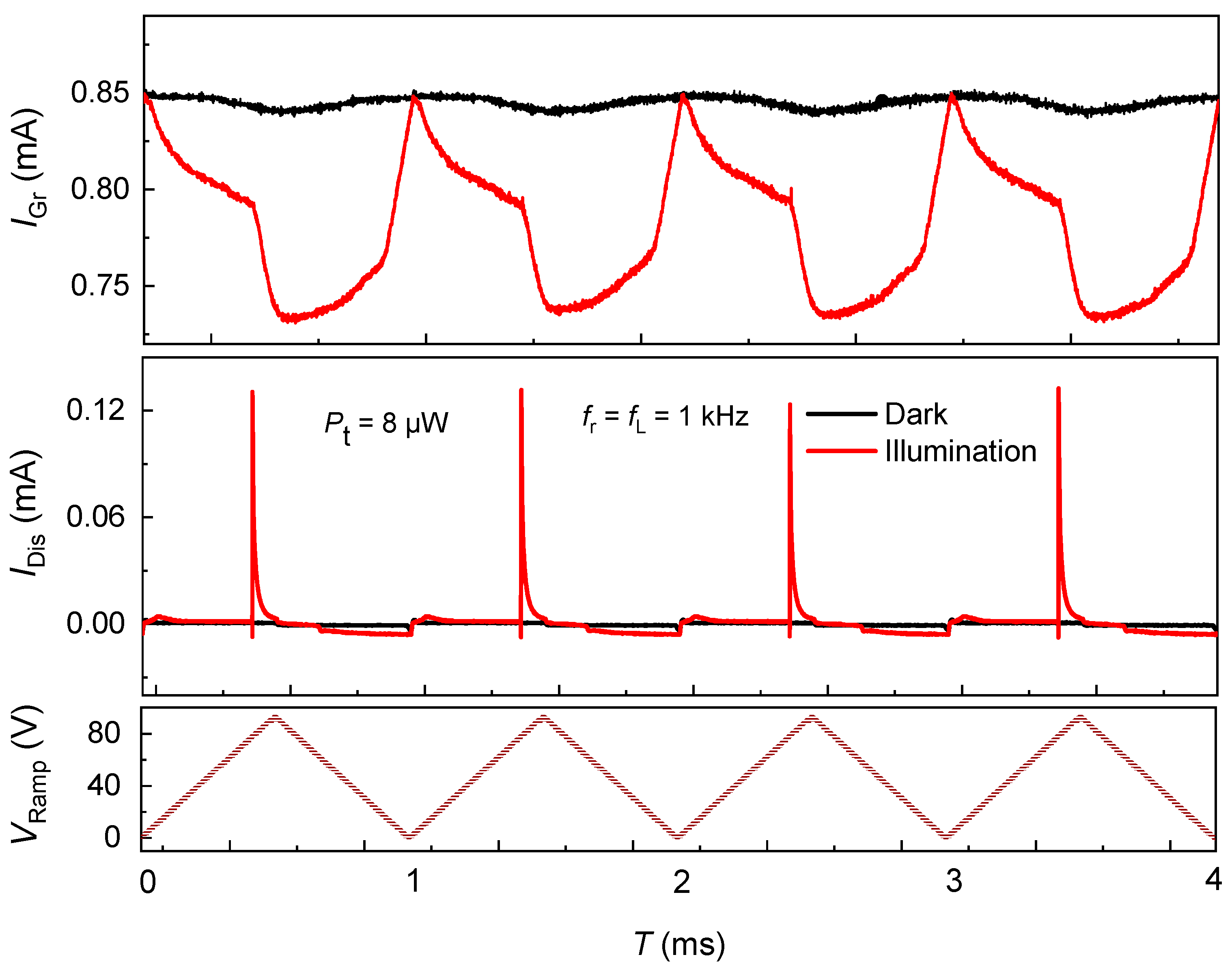

3.4. Reset-Free Operation: Device B

4. Future Work and Outlook

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Liu, W.; Yu, Y.; Peng, M.; Zheng, Z.; Jian, P.; Wang, Y.; Zou, Y.; Zhao, Y.; Wang, F.; Wu, F.; et al. Integrating 2D layered materials with 3D bulk materials as van der Waals heterostructures for photodetections: Current status and perspectives. InfoMat 2023, 5, e12470. [Google Scholar] [CrossRef]

- Liu, M.; Wei, J.; Qi, L.; An, J.; Liu, X.; Li, Y.; Shi, Z.; Li, D.; Novoselov, K.S.; Qiu, C.-W.; et al. Photogating-assisted tunneling boosts the responsivity and speed of heterogeneous WSe2/Ta2NiSe5 photodetectors. Nat. Commun. 2024, 15, 141. [Google Scholar] [CrossRef] [PubMed]

- Bassi, G.; Kaur, D.; Dahiya, R.; Kumar, M. 2D–3D heterostructure of PtS2−x/Ga2O3 and their band alignment studies for high performance and broadband photodetector. Nanotechnology 2024, 35, 325706. [Google Scholar] [CrossRef] [PubMed]

- Huang, P.-C.; Huang, S.-K.; Lai, T.-C.; Shih, M.-C.; Hsu, H.-C.; Chen, C.-H.; Lin, C.-C.; Chiang, C.-H.; Lin, C.-Y.; Tsukagoshi, K.; et al. Visualizing band alignment across 2D/3D perovskite heterointerfaces of solar cells with light-modulated scanning tunneling microscopy. Nano Energy 2021, 89, 106362. [Google Scholar] [CrossRef]

- Tang, Q.; Zhong, F.; Li, Q.; Weng, J.; Li, J.; Lu, H.; Wu, H.; Liu, S.; Wang, J.; Deng, K.; et al. Infrared Photodetection from 2D/3D van der Waals Heterostructures. Nanomaterials 2023, 13, 1169. [Google Scholar] [CrossRef]

- Shin, J.; Yoo, H. Photogating Effect-Driven Photodetectors and Their Emerging Applications. Nanomaterials 2023, 13, 882. [Google Scholar] [CrossRef]

- Li, H.; Yang, Z. Recent progress in mid-infrared photodetection devices using 2D/nD (n = 0, 1, 2, 3) heterostructures. Mater. Des. 2023, 225, 111446. [Google Scholar] [CrossRef]

- Raimond, J.M.; Brune, M.; Computation, Q.; De Martini, F.; Monroe, C. Electric Field Effect in Atomically Thin Carbon Films. Science 2004, 306, 666–670. [Google Scholar] [CrossRef]

- Geim, A.K. Graphene: Status and Prospects. Science 2009, 324, 1530–1535. [Google Scholar] [CrossRef]

- Banszerus, L.; Schmitz, M.; Engels, S.; Dauber, J.; Oellers, M.; Haupt, F.; Watanabe, K.; Taniguchi, T.; Beschoten, B.; Stampfer, C. Ultrahigh-mobility graphene devices from chemical vapor deposition on reusable copper. Sci. Adv. 2015, 1, e1500222. [Google Scholar] [CrossRef]

- Mak, K.F.; Ju, L.; Wang, F.; Heinz, T.F. Optical spectroscopy of graphene: From the far infrared to the ultraviolet. Solid State Commun. 2012, 152, 1341–1349. [Google Scholar] [CrossRef]

- Xia, F.; Yan, H.; Avouris, P. The interaction of light and graphene: Basics, devices, and applications. Proc. IEEE 2013, 101, 1717–1731. [Google Scholar] [CrossRef]

- Qadir, A.; Le, T.K.; Malik, M.; Amedome Min-Dianey, K.A.; Saeed, I.; Yu, Y.; Choi, J.R.; Pham, P.V. Representative 2D-material-based nanocomposites and their emerging applications: A review. RSC Adv. 2021, 11, 23860–23880. [Google Scholar] [CrossRef]

- Koppens, F.H.L.; Mueller, T.; Avouris, P.; Ferrari, A.C.; Vitiello, M.S.; Polini, M. Photodetectors based on graphene, other two-dimensional materials and hybrid systems. Nat. Nanotechnol. 2014, 9, 780–793. [Google Scholar] [CrossRef]

- Ruiz, I.; Beechem, T.E.; Goldflam, M.D.; Thelen, P.M.; Howell, S.W.; Goodman, K. Depleted Graphene-Insulator-Silicon Junctions for High Energy Detection of Ions and Gamma Rays; Sandia National Laboratories: Albuquerque, NM, USA, 2019.

- Ruiz, I.; Beechem, T.E.; Smith, S.; Dickens, P.; Paisley, E.A.; Shank, J.; Howell, S.W.; Sarma, R.; Draper, B.L.; Goldflam, M.D. Interface Defect Engineering for Improved Graphene-Oxide-Semiconductor Junction Photodetectors. ACS Appl. Nano Mater. 2019, 2, 6162–6168. [Google Scholar] [CrossRef]

- Howell, S.W.; Ruiz, I.; Davids, P.S.; Harrison, R.K.; Smith, S.W.; Goldflam, M.D.; Martin, J.B.; Martinez, N.J.; Beechem, T.E. Graphene-Insulator-Semiconductor Junction for Hybrid Photodetection Modalities. Sci. Rep. 2017, 7, 14651. [Google Scholar] [CrossRef]

- Ruiz, I.; Beechem, T.E.; Vizkelethy, G.; Thelen, P.M.; Shank, J.; Howell, S.W.; Goldflam, M.D. Depleted Graphene-Oxide-Semiconductor Junctions for High Energy Radiation Detection. In Proceedings of the 2019 Device Research Conference (DRC), Ann Arbor, MI, USA, 23–26 June 2019; pp. 131–132. [Google Scholar] [CrossRef]

- Matacena, I.; Guerriero, P.; Lancellotti, L.; Bobeico, E.; Lisi, N.; Chierchia, R.; Delli Veneri, P.; Daliento, S. Forward bias capacitance investigation as a powerful tool to monitor graphene/silicon interfaces. Sol. Energy 2021, 226, 1–8. [Google Scholar] [CrossRef]

- Zhou, K.; Jia, Z.; Ma, X.-Q.; Niu, W.; Zhou, Y.; Huang, N.; Ding, G.; Yan, Y.; Han, S.-T.; Roy, V.A.L.; et al. Manufacturing of graphene based synaptic devices for optoelectronic applications. Int. J. Extrem. Manuf. 2023, 5, 42006. [Google Scholar] [CrossRef]

- Sun, M.; Xu, Z.; Qu, S.; Liu, L.; Zhu, Q.; Xu, W. Synaptic Transistors Using Scalable Graphene Nanoribbons. J. Phys. Chem. Lett. 2024, 15, 8956–8963. [Google Scholar] [CrossRef]

- Das, R.R.; Reghuvaran, C.; James, A. Graphene-based RRAM devices for neural computing. Front. Neurosci. 2023, 17, 1253075. [Google Scholar] [CrossRef] [PubMed]

- Chouprik, A.; Guberna, E.; Mutaev, I.; Margolin, I.; Guberna, E.; Rybin, M. Biorealistic response in a technology-compatible graphene synaptic transistor. Appl. Phys. Lett. 2025, 126, 123502. [Google Scholar] [CrossRef]

- Schranghamer, T.F.; Oberoi, A.; Das, S. Graphene memristive synapses for high precision neuromorphic computing. Nat. Commun. 2020, 11, 5474. [Google Scholar] [CrossRef]

- Abunahla, H.; Halawani, Y.; Alazzam, A.; Mohammad, B. NeuroMem: Analog Graphene-Based Resistive Memory for Artificial Neural Networks. Sci. Rep. 2020, 10, 9473. [Google Scholar] [CrossRef]

- Walters, B.; Jacob, M.V.; Amirsoleimani, A.; Rahimi Azghadi, M. A Review of Graphene-Based Memristive Neuromorphic Devices and Circuits. Adv. Intell. Syst. 2023, 5, 2300136. [Google Scholar] [CrossRef]

- Daliento, S.; Tari, O.; Lancellotti, L. Closed-form analytical expression for the conductive and dissipative parameters of the MOS-C equivalent circuit. IEEE Trans. Electron Devices 2011, 58, 3643–3646. [Google Scholar] [CrossRef]

- Lou, L.F.; Tettemer, G.L. Characterization of metal-oxide-semiconductor capacitors with a fast-ramp technique. J. Appl. Phys. 1988, 63, 5398–5405. [Google Scholar] [CrossRef]

- Lou, L.-F.; Kitazaki, K.S. Charge accumulation and multiplication photodetector. In Proceedings of the SPIE’s 1993 International Symposium on Optics, Imaging, and Instrumentation, Washington, DC, USA, 15 October 1993; Volume 2022, pp. 121–131. [Google Scholar]

- Lou, L.F.; Tettemer, G.L. An experimental study of a metal-oxide-semiconductor photomultiplier. J. Appl. Phys. 1989, 66, 2678–2688. [Google Scholar] [CrossRef]

- Nicollian, E.; Berglund, C. Avalanche Injection of Electrons into Insulating SiO2 Using MOS Structures. J. Appl. Phys. 1970, 41, 3052–3057. [Google Scholar] [CrossRef]

- Goetzberger, A.; Nicollian, E.H. MOS Avalanche and Tunneling Effects in Silicon Surfaces. J. Appl. Phys. 1967, 38, 4582–4588. [Google Scholar] [CrossRef]

- Wieder, H.H. MOS (Metal Oxide Semiconductors) Physics and Technology by E. H. Nicollian and J. R. Brews. J. Vac. Sci. Technol. 1982, 21, 1048–1049. [Google Scholar] [CrossRef]

- Bulucea, C. Deep-Depletion Breakdown Voltage of Silicon-Dioxide/Silicon MOS Capacitors. IEEE Trans. Electron Devices 1979, 26, 201–205. [Google Scholar] [CrossRef]

- Boyle, W.S.; Smith, G.E. Charge-coupled devices-a new approach to MIS device structures. IEEE Spectr. 1971, 8, 18–27. [Google Scholar] [CrossRef]

- Li, X.; Cai, W.; An, J.; Kim, S.; Nah, J.; Yang, D.; Colombo, L.; Ruoff, R.S. Large-Area Synthesis of High-Quality and Uniform Graphene Films on Copper Foils. Science 2009, 3893, 1312–1315. [Google Scholar] [CrossRef] [PubMed]

- Dresselhaus, M.S.; Jorio, A.; Filho, A.G.S.; Saito, R. Defect characterization in graphene and carbon nanotubes using Raman spectroscopy. Phil. Trans. R. Soc. A 2010, 368, 5355–5377. [Google Scholar] [CrossRef]

- Zandiatashbar, A.; Lee, G.H.; An, S.J.; Lee, S.; Mathew, N.; Terrones, M.; Hayashi, T.; Picu, C.R.; Hone, J.; Koratkar, N. Effect of defects on the intrinsic strength and stiffness of graphene. Nat. Commun. 2014, 5, 3186. [Google Scholar] [CrossRef]

- Eckmann, A.; Felten, A.; Mishchenko, A.; Britnell, L.; Krupke, R.; Novoselov, K.S.; Casiraghi, C. Probing the nature of defects in graphene by Raman spectroscopy. Nano Lett. 2012, 12, 3925–3930. [Google Scholar] [CrossRef]

- Ferrari, A.C. Raman spectroscopy of graphene and graphite: Disorder, electron-phonon coupling, doping and nonadiabatic effects. Solid State Commun. 2007, 143, 47–57. [Google Scholar] [CrossRef]

- Araujo, P.T.; Terrones, M.; Dresselhaus, M.S. Defects and impurities in graphene-like materials. Mater. Today 2012, 15, 98–109. [Google Scholar] [CrossRef]

- Ferrari, A.C.; Meyer, J.C.; Scardaci, V.; Casiraghi, C.; Lazzeri, M.; Mauri, F.; Piscanec, S.; Jiang, D.; Novoselov, K.S.; Roth, S.; et al. Raman Spectrum of Graphene and Graphene Layers. Phys. Rev. Lett. 2006, 97, 187401. [Google Scholar] [CrossRef] [PubMed]

- Neumaier, D.; Pindl, S.; Lemme, M.C. Lemme Integrating graphene into semiconductor fabrication lines. Nat. Mater. 2019, 18, 520–524. [Google Scholar] [CrossRef] [PubMed]

- Wu, C.; Brems, S.; Yudistira, D.; Cott, D.; Milenin, A.; Vandersmissen, K.; Maestre, A.; Centeno, A.; Zurutuza, A.; Van Campenhout, J.; et al. Wafer-Scale Integration of Single Layer Graphene Electro-Absorption Modulators in a 300 mm CMOS Pilot Line. Laser Photonics Rev. 2023, 17, 2200789. [Google Scholar] [CrossRef]

- Fan, X.; He, C.; Ding, J.; Gao, Q.; Ma, H.; Lemme, M.C.; Zhang, W. Graphene MEMS and NEMS. Microsyst. Nanoeng. 2024, 10, 154. [Google Scholar] [CrossRef] [PubMed]

- Yang, C.; Wang, G.; Liu, M.; Yao, F.; Li, H. Mechanism, material, design, and implementation principle of two-dimensional material photodetectors. Nanomaterials 2021, 11, 2688. [Google Scholar] [CrossRef]

- Xue, M.; Mackin, C.; Weng, W.H.; Zhu, J.; Luo, Y.; Luo, S.X.L.; Lu, A.Y.; Hempel, M.; McVay, E.; Kong, J.; et al. Integrated biosensor platform based on graphene transistor arrays for real-time high-accuracy ion sensing. Nat. Commun. 2022, 13, 5064. [Google Scholar] [CrossRef]

- Elviretti, M.; Lisker, M.; Lukose, R.; Lukosius, M.; Akhtar, F.; Mai, A. Reliable metal-graphene contact formation process flows in a CMOS-compatible environment. Nanoscale Adv. 2022, 4, 4373–4380. [Google Scholar] [CrossRef]

- Soikkeli, M.; Murros, A.; Rantala, A.; Txoperena, O.; Kilpi, O.P.; Kainlauri, M.; Sovanto, K.; Maestre, A.; Centeno, A.; Tukkiniemi, K.; et al. Wafer-Scale Graphene Field-Effect Transistor Biosensor Arrays with Monolithic CMOS Readout. ACS Appl. Electron. Mater. 2023, 5, 4925–4932. [Google Scholar] [CrossRef] [PubMed]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Khaliq, A.; Xu, H.; Qadir, A.; Salman, A.; Du, S.; Ali, M.; Huang, S. Photogating Regimes in Graphene: Memory-Bearing and Reset-Free Operation. Nanomaterials 2025, 15, 1667. https://doi.org/10.3390/nano15211667

Khaliq A, Xu H, Qadir A, Salman A, Du S, Ali M, Huang S. Photogating Regimes in Graphene: Memory-Bearing and Reset-Free Operation. Nanomaterials. 2025; 15(21):1667. https://doi.org/10.3390/nano15211667

Chicago/Turabian StyleKhaliq, Afshan, Hongsheng Xu, Akeel Qadir, Ayesha Salman, Sichao Du, Munir Ali, and Shihua Huang. 2025. "Photogating Regimes in Graphene: Memory-Bearing and Reset-Free Operation" Nanomaterials 15, no. 21: 1667. https://doi.org/10.3390/nano15211667

APA StyleKhaliq, A., Xu, H., Qadir, A., Salman, A., Du, S., Ali, M., & Huang, S. (2025). Photogating Regimes in Graphene: Memory-Bearing and Reset-Free Operation. Nanomaterials, 15(21), 1667. https://doi.org/10.3390/nano15211667