Comparison of Nondestructive Testing Methods for Solder, Sinter, and Adhesive Interconnects in Power and Opto-Electronics

Abstract

1. Introduction

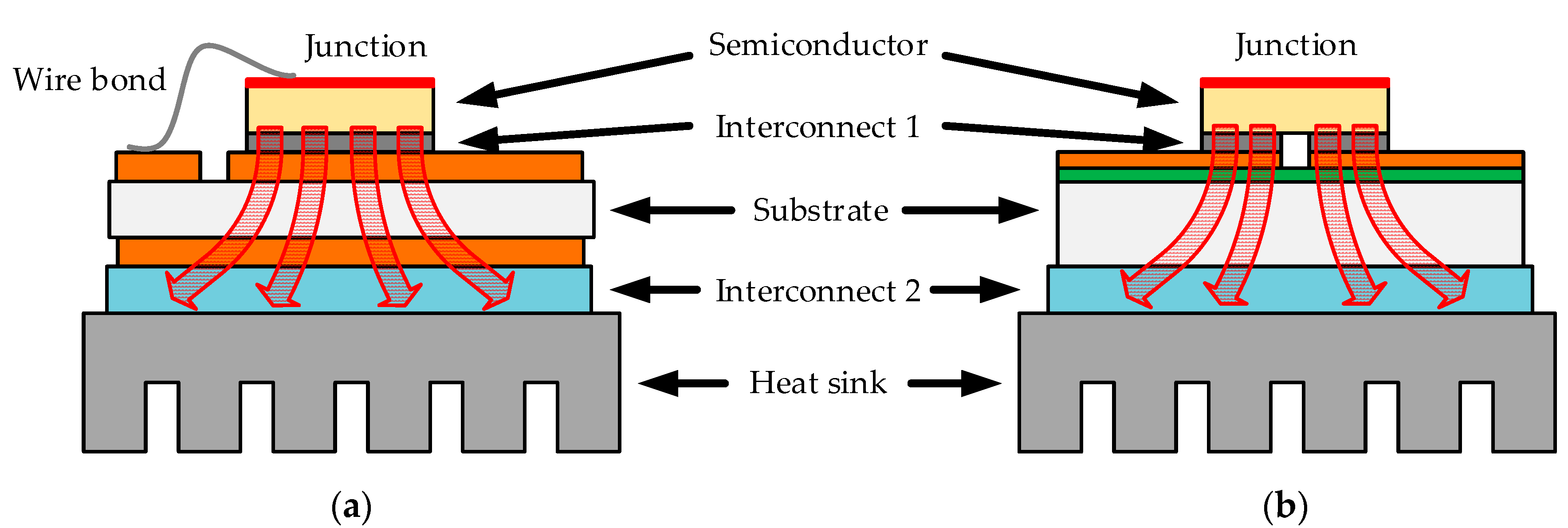

2. Interconnect Technologies in Power Electronics and SSL

2.1. Soldering

2.2. Sintering

2.3. Adhesive

3. Nondestructive Testing Methods

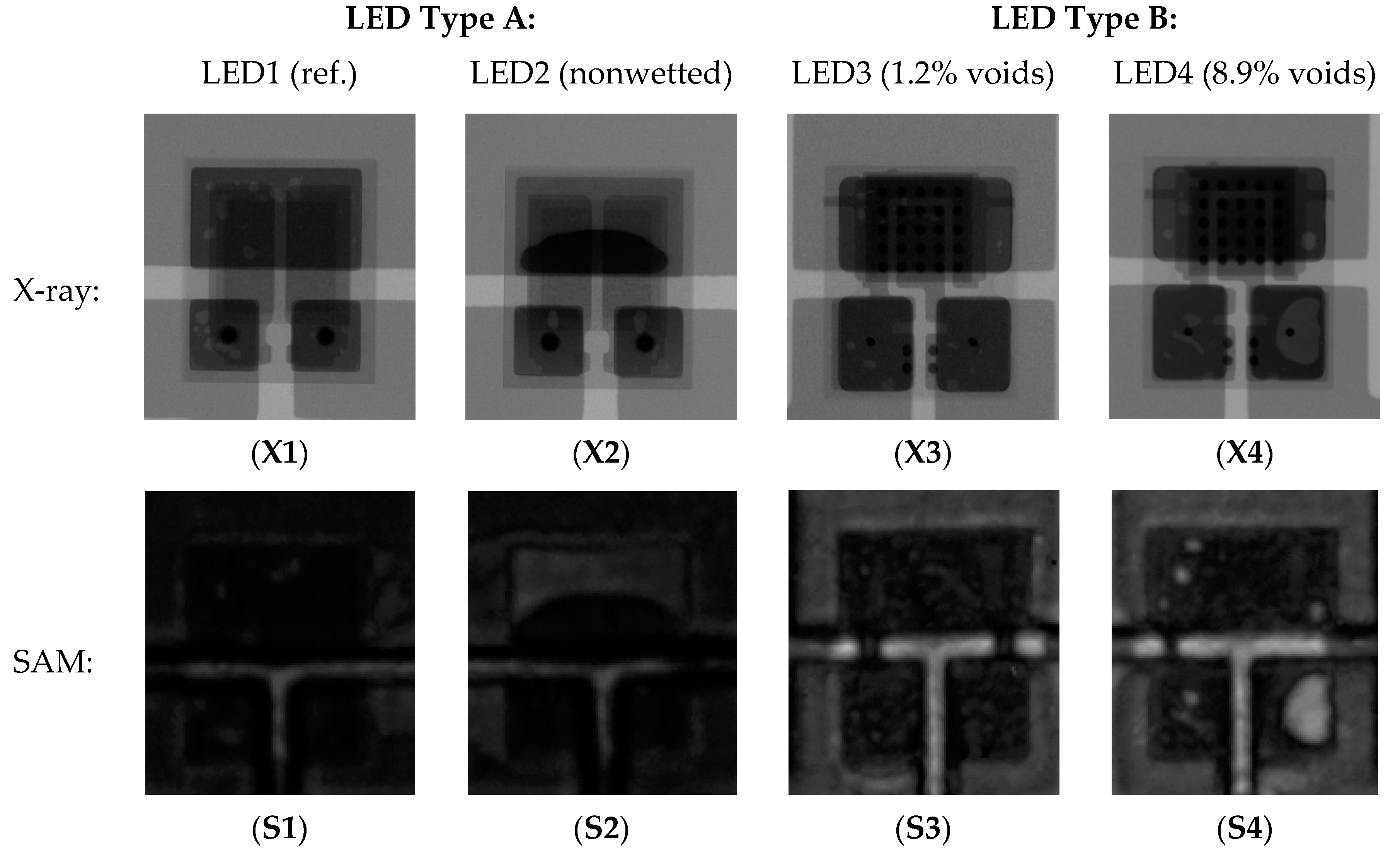

3.1. X-ray

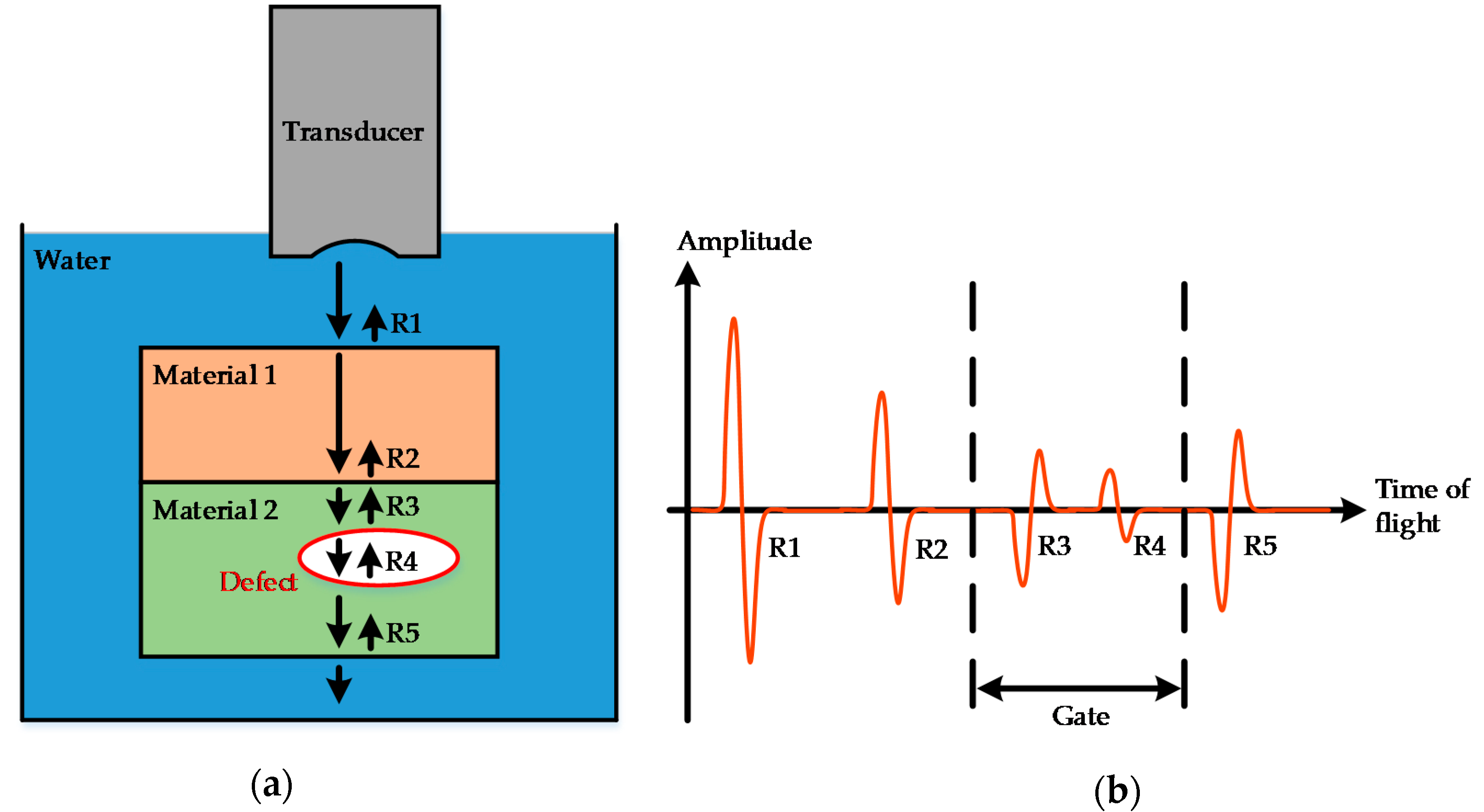

3.2. Scanning Acoustic Microscopy (SAM)

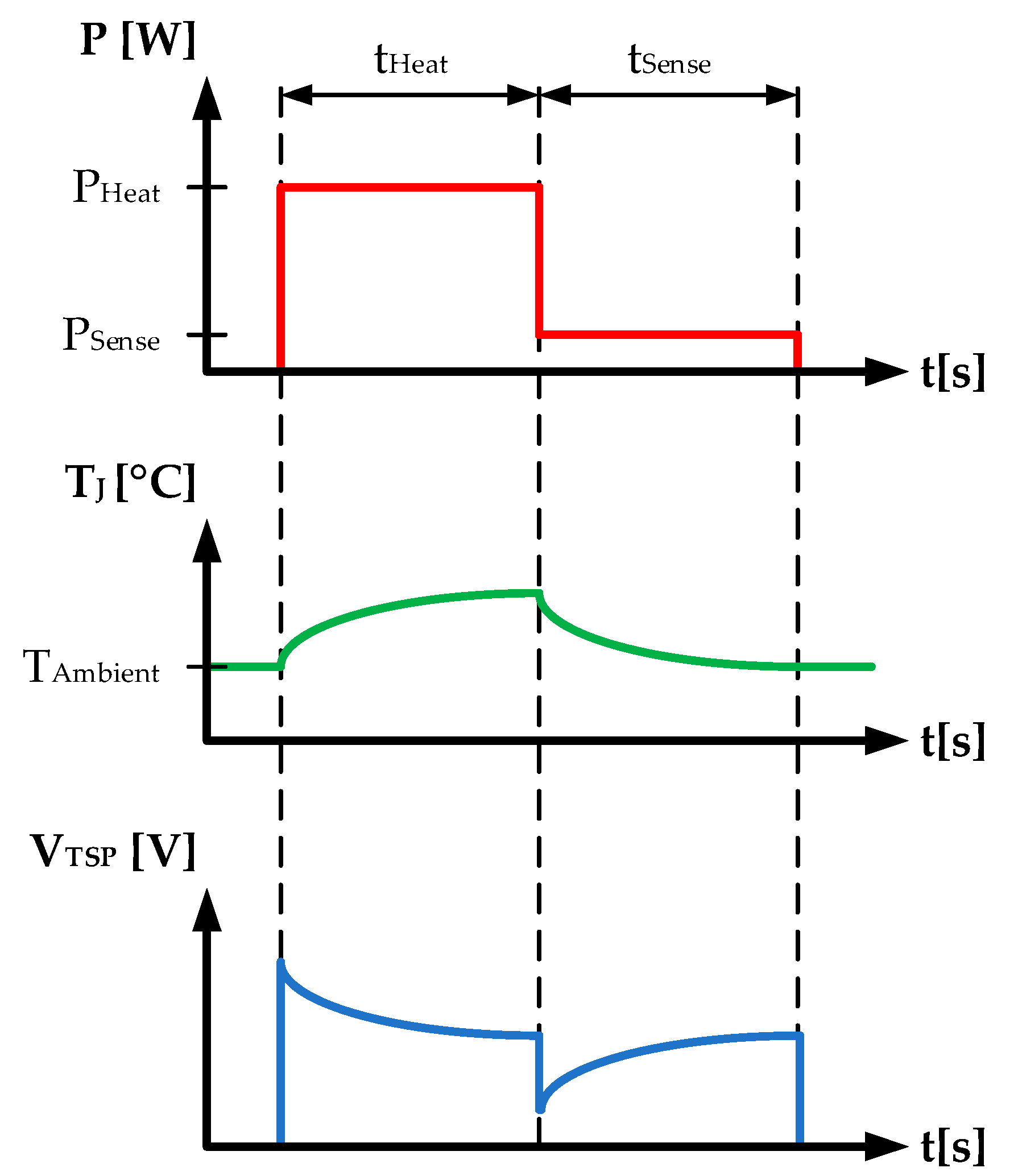

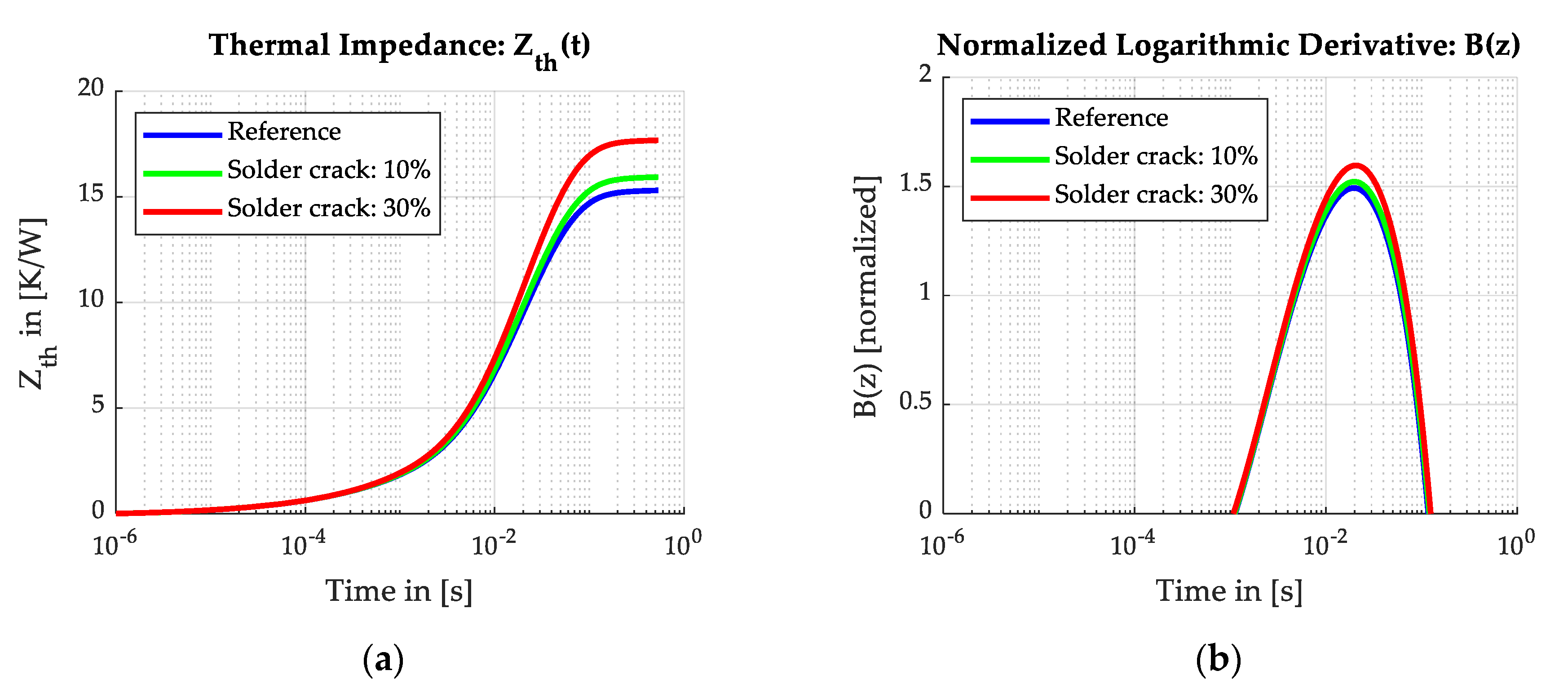

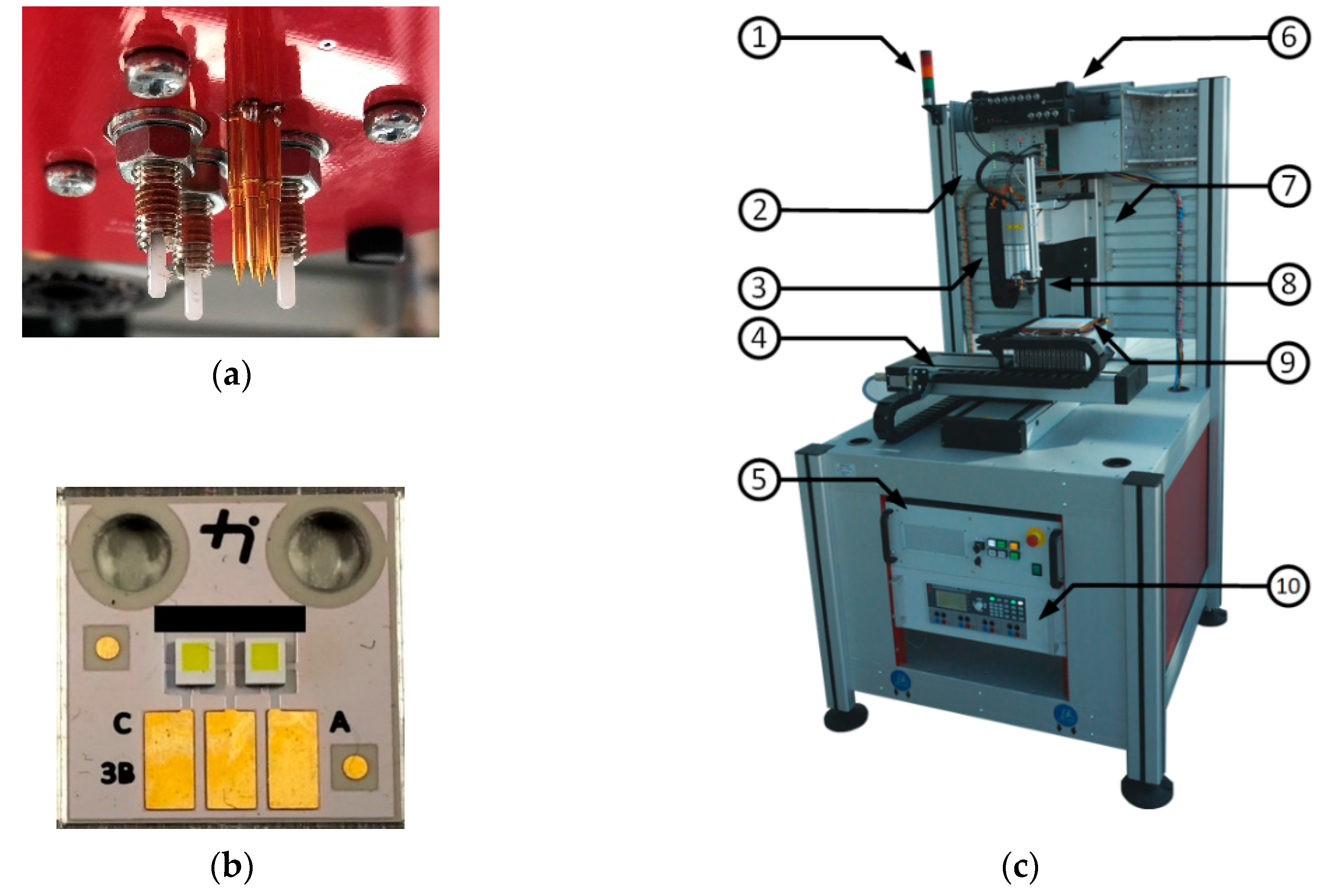

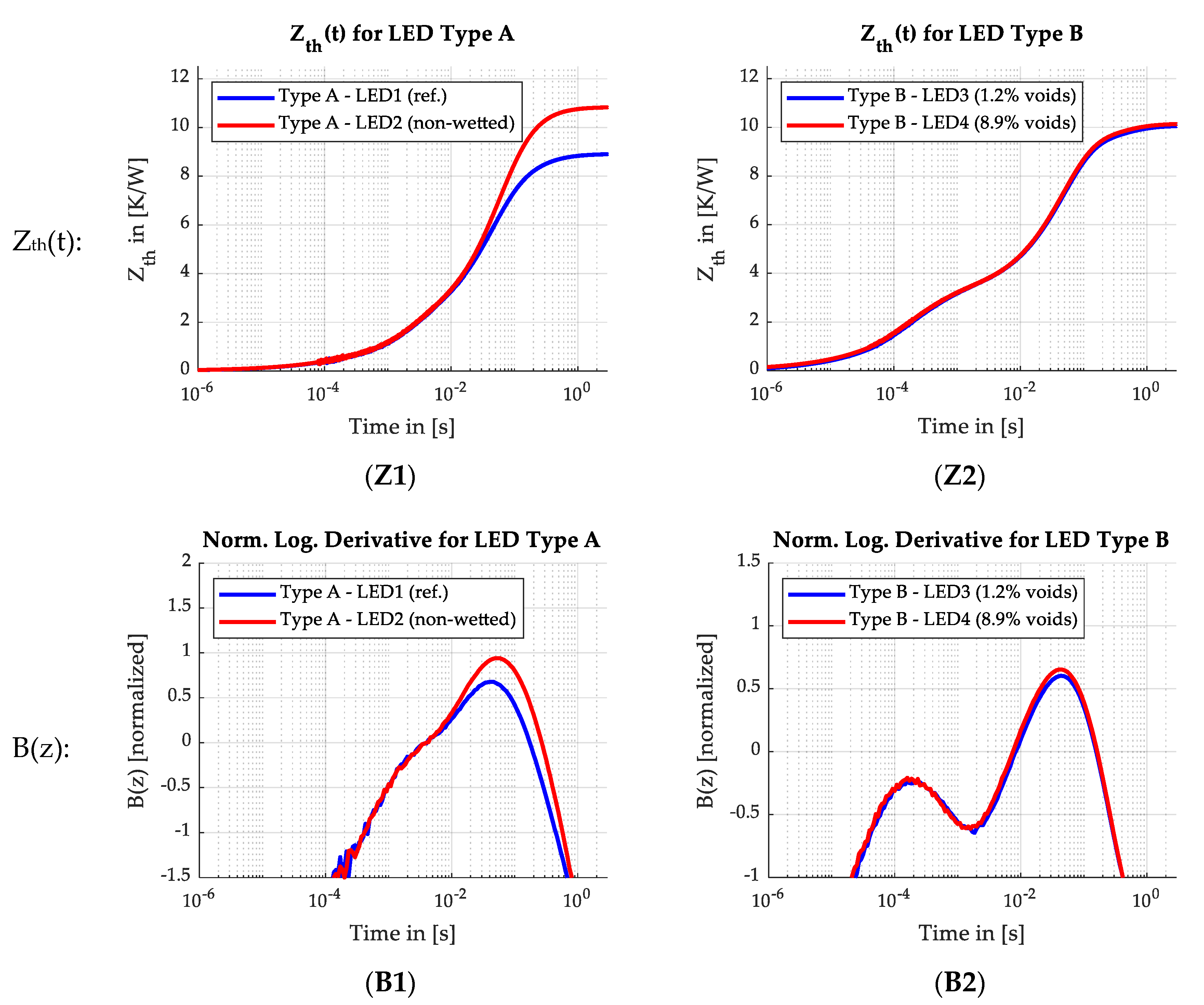

3.3. Transient Thermal Analysis (TTA)

4. Results

4.1. Inspection of Soldered Interface

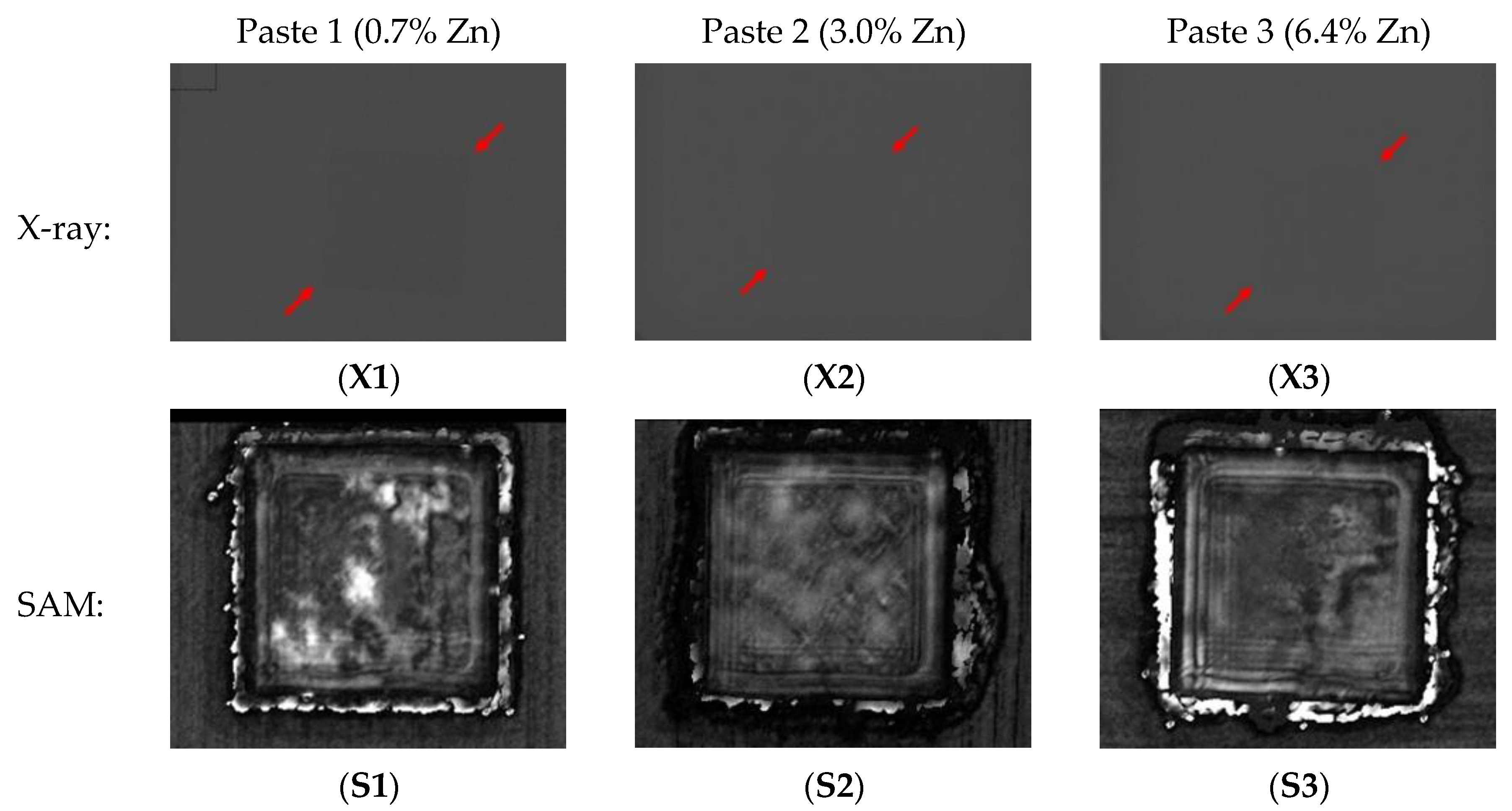

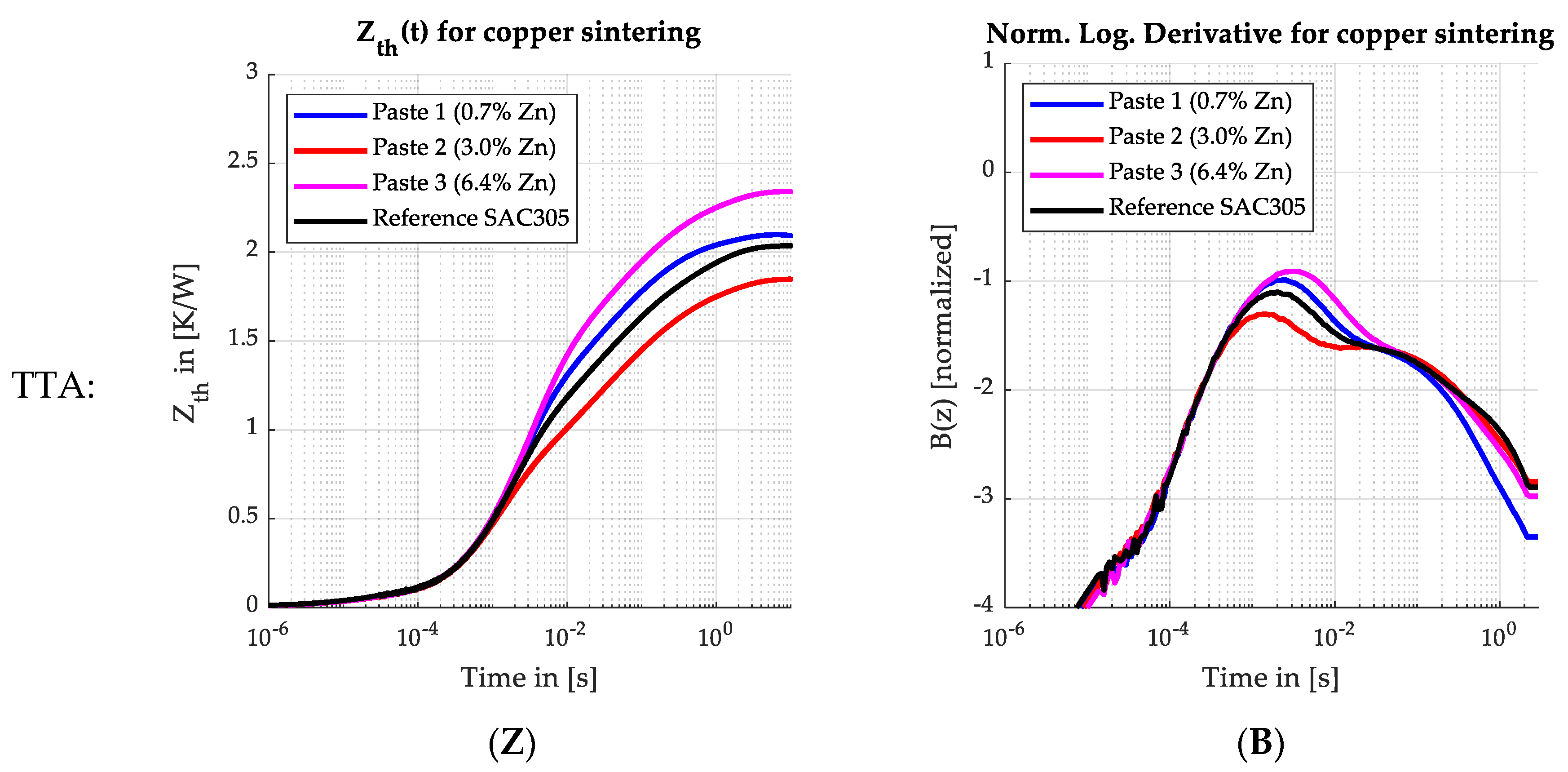

4.2. Inspection of Sintered Interfaces

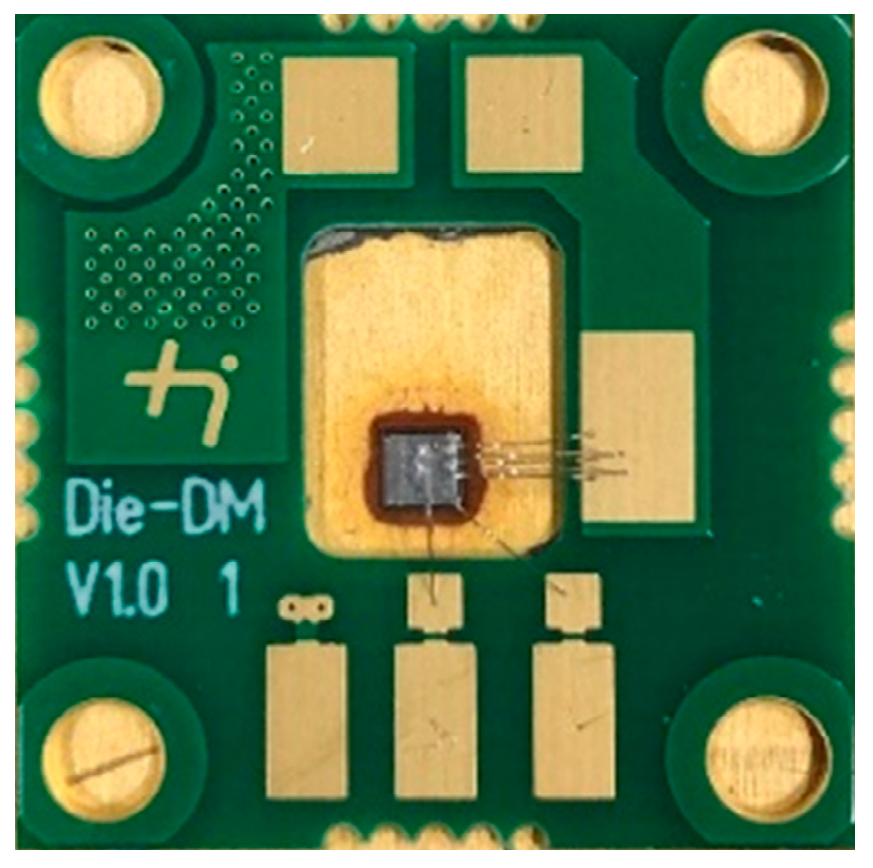

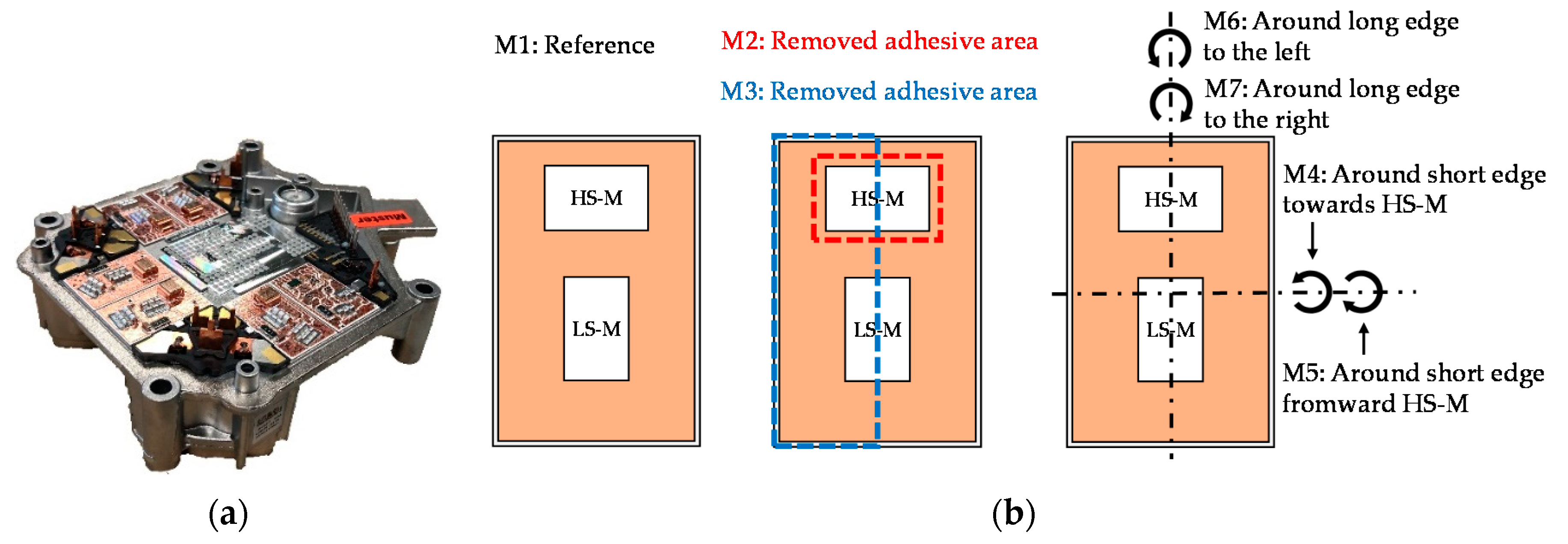

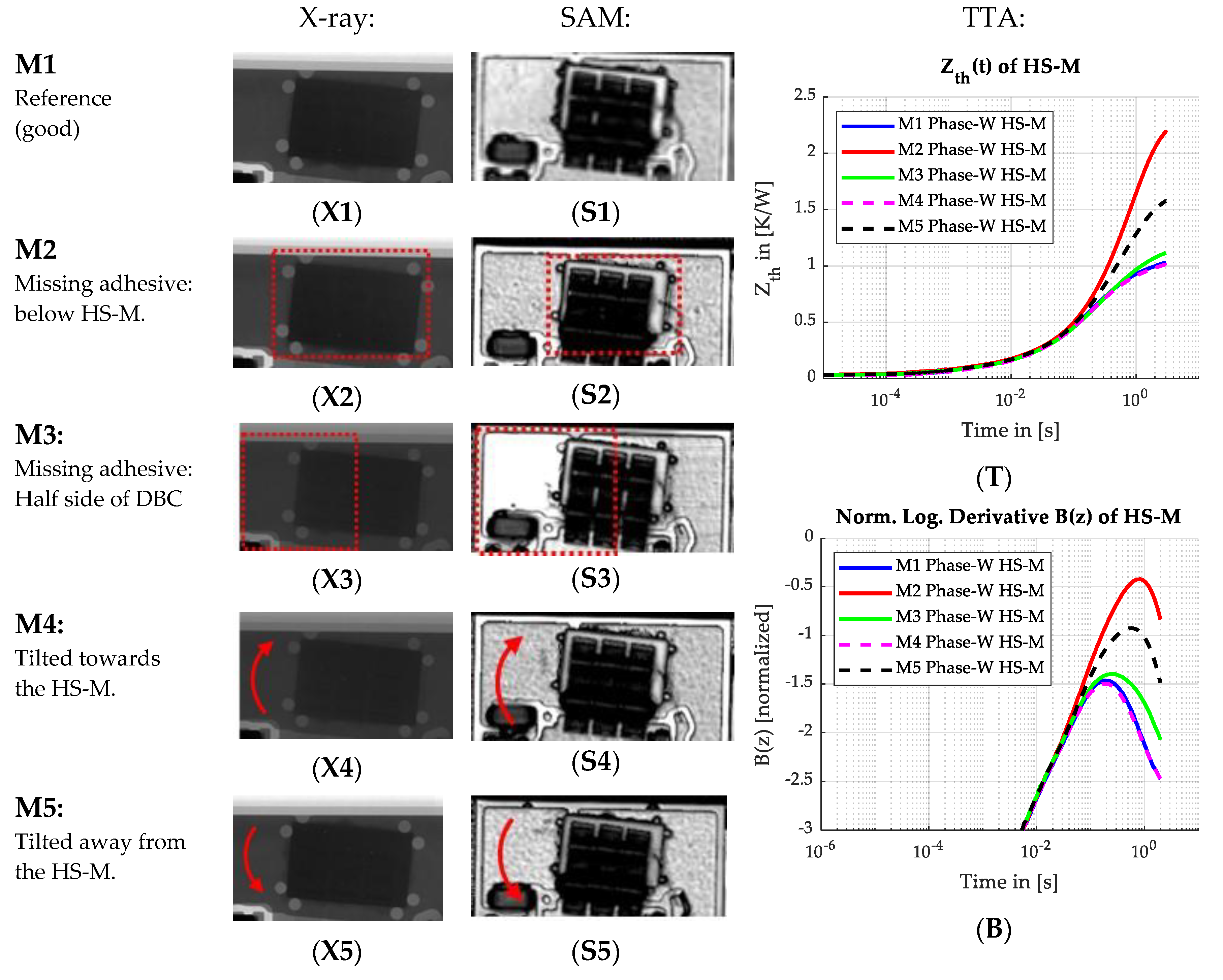

4.3. Inspection of Adhesive Interfaces

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Avinash, S.; Asavari, P.; Vineet, K. Power Electronics Market by Device Type (Power Discrete, Power Module, and Power IC), Material (Silicon Carbide, Gallium Nitride, Sapphire, and Other), and Application (Power Management, UPS, Renewable, and Others), and End User (Telecommunication, Industrial, Automotive, Consumer Electronics, Military & Defense, Energy & Power, and Other): Global Opportunity Analysis and Industry Forecast, 2020–2027; Allied Market Research: Portland, USA, 2020. [Google Scholar]

- Ruchal, H.; Vineet, K. Solid State Lighting Market by Type (Light Emitting Diodes (LED), Organic Light Emitting Diodes (OLED), and Polymer Light Emitting Diodes (PLED)), Installation Type (New Installation and Retrofit), and Application (Indoor Lighting, Outdoor Lighting, and Specialty Lighting), and Industry Vertical (Residential, Industrial and Commercial, Medical, Transportation, Others): Global Opportunity Analysis and Industry Forecast, 2020–2027; Allied Market Research: Portland, USA, 2020. [Google Scholar]

- Wang, H.; Liserre, M.; Blaabjerg, F. Toward Reliable Power Electronics: Challenges, Design Tools, and Opportunities. IEEE Ind. Electron. Mag. 2013, 7, 17–26. [Google Scholar] [CrossRef]

- Schulz-Harder, J. Advantages and new development of direct bonded copper substrates. Microelectron. Reliab. 2003, 43, 359–365. [Google Scholar] [CrossRef]

- Asai, S.; Funaki, M.; Sawa, H.; Katō, K. Fabrication of an insulated metal substrate (IMS), having an insulating layer with a high dielectric constant. IEEE Trans. Components, Hybrids, Manuf. Technol. 1993, 16, 499–504. [Google Scholar] [CrossRef]

- Wintrich, A.; Nicolai, U.; Tursky, W.; Reimann, T. Application Manual Power Semiconductors, 2nd ed.; ISLE Verlag: Ilmenau, Germany, 2015; ISBN 9783938843833. [Google Scholar]

- Aryan, P.; Sampath, S.; Sohn, H. An Overview of Non-Destructive Testing Methods for Integrated Circuit Packaging Inspection. Sensors 2018, 18, 1981. [Google Scholar] [CrossRef] [PubMed]

- Rudzki, J.; Jensen, L.; Poech, M.; Schmidt, L.; Osterwald, F. Quality Evaluation for Silver Sintering Layers in Power Electronic Modules. In Proceedings of the CIPS 2012, 7th International Conference on Integrated Power Electronics Systems, Nuremberg, Germany, 6–8 March 2012; incl. CD-ROM. VDE-Verl.: Berlin, Germany, 2012. ISBN 9783800734146. [Google Scholar]

- da Silva, L.F.M.; Öchsner, A.; Adams, R.D. Handbook of Adhesion Technology, 2nd ed.; Springer International Publishing: Cham, Switzerland, 2018; ISBN 978-3-319-55411-2. [Google Scholar]

- Elger, G.; Schmid, M.; Hanss, A. Thermal Analysis Of Semiconductor Devices. Available online: https://uspto.report/patent/app/20200018711 (accessed on 27 November 2020).

- Schmid, M.; Bhogaraju, S.K.; Hanss, A.; Elger, G. A new Noise-Suppression Algorithm for Transient Thermal Analysis in Semiconductors over Pulse Superposition. IEEE Trans. Instrum. Meas. 2020, 1. [Google Scholar] [CrossRef]

- Schmid, M.; Hanss, A.; Bhogaraju, S.K.; Elger, G. Time Saving Averaging Algorithm for Transient Thermal Analyses over Deterministic Pulse Superposition. In Proceedings of the 2019 25th International Workshop on Thermal Investigations of ICs and Systems (THERMINIC), Lecco, Italy, 25–27 September 2019; Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2019; pp. 1–6. [Google Scholar]

- Hanss, A.; Elger, G. Residual free solder process for fluxless solder pastes. Solder. Surf. Mt. Technol. 2018, 30, 118–128. [Google Scholar] [CrossRef]

- IPC/JEDEC. J-STD-020E. Moisture/Reflow Sensitivity Classification for Nonhermetic Surface Mount Devices; IPC: Bannockburn, IL, USA, 2014. [Google Scholar]

- Liu, Y.; Leung, S.Y.; Zhao, J.; Wong, C.K.; Yuan, C.A.; Zhang, G.; Sun, F.; Luo, L. Thermal and mechanical effects of voids within flip chip soldering in LED packages. Microelectron. Reliab. 2014, 54, 2028–2033. [Google Scholar] [CrossRef]

- Arra, M.; Shangguan, D.; Ristolainen, E.; Lepistö, T. Effect of reflow profile on wetting and intermetallic formation between Sn/Ag/Cu solder components and printed circuit boards. Solder. Surf. Mt. Technol. 2002, 14, 18–25. [Google Scholar] [CrossRef]

- Vandevelde, B.; Griffoni, A.; Zanon, F.; Willems, G. Methodology for Solder-Joint Lifetime Prediction of LED-Based PCB Assemblies. IEEE Trans. Device Mater. Reliab. 2018, 18, 377–382. [Google Scholar] [CrossRef]

- Suganuma, K.; Jiu, J. Advanced Bonding Technology Based on Nano- and Micro-metal Pastes; Springer Science and Business Media LLC: Berlin/Heidelberg, Germany, 2017; pp. 589–626. [Google Scholar]

- Siow, K.S.; Lin, Y.T. Identifying the Development State of Sintered Silver (Ag) as a Bonding Material in the Microelectronic Packaging via a Patent Landscape Study. J. Electron. Packag. 2016, 138, 020804. [Google Scholar] [CrossRef]

- Bhogaraju, S.K.; Mokhtari, O.; Conti, F.; Elger, G. Die-attach bonding for high temperature applications using thermal decomposition of copper(II) formate with polyethylene glycol. Scr. Mater. 2020, 182, 74–80. [Google Scholar] [CrossRef]

- Siow, K.S. Are Sintered Silver Joints Ready for Use as Interconnect Material in Microelectronic Packaging? J. Electron. Mater. 2014, 43, 947–961. [Google Scholar] [CrossRef]

- Jin Yim, M.; Paik, K.W. Review of Electrically Conductive Adhesive Technologies for Electronic Packaging. Electron. Mater. Lett. 2006, 2006, 183–194. [Google Scholar]

- Kisiel, R.; Szczepański, Z. Die-attachment solutions for SiC power devices. Microelectron. Reliab. 2009, 49, 627–629. [Google Scholar] [CrossRef]

- Maurer, A. Adhesive Bonding to Replace Soldering of Power Modules. Adhes. Adhes. 2017, 14, 24–27. [Google Scholar] [CrossRef]

- Povolotskaya, E.; Mach, P. Failure analysis of adhesive joining in electronics. In Conference Proceedings, “New Trends in Micro/Nanotechnology”, High Tatras, Slovakia, 11–15 May 2011; 2011 34th International Spring Seminar on Electronics Technology (ISSE), Tratanska Lomnica, Slovakia, 11–15 May 2011; IEEE: Piscataway, NJ, USA, 2011; pp. 247–252. ISBN 978-1-4577-2111-3. [Google Scholar]

- Gilfrich, J.V.; Birks, L.S. Spectral distribution of X-ray tubes for quantitative X-ray fluorescence analysis. Anal. Chem. 1968, 40, 1077–1080. [Google Scholar] [CrossRef]

- Martz, H.E.; Logan, C.M.; Schneberk, D.J.; Shull, P.J. X-ray Imaging. In Fundamentals, Industrial Techniques, and Applications; Martz, H.E., Logan, C.M., Schneberk, D.J., Shull, P.J., Eds.; CRC Press: Boca Raton, FL, USA, 2016; ISBN 9781315357263. [Google Scholar]

- Vaga, R.; Bryant, K. Recent advances in X-ray technology. In Proceedings of the 2016 Pan Pacific Microelectronics Symposium (Pan Pacific), Big Island, HI, USA, 25–28 January 2016; IEEE: Piscataway, NJ, USA, 2016. ISBN 9780988887398. [Google Scholar]

- Gilmore, R.S.; Tam, K.C.; Young, J.D.; Howard, D.R.; Almond, E. Acoustic microscopy from 10 to 100 MHz for industrial applications. Philos. Trans. R. Soc. London. Ser. A Math. Phys. Sci. 1986, 320, 215–235. [Google Scholar] [CrossRef]

- Yazdan Mehr, M.; Bahrami, A.; Fischer, H.; Gielen, S.; Corbeij, R.; van Driel, W.D.; Zhang, G.Q. An overview of scanning acoustic microscope, a reliable method for non-destructive failure analysis of microelectronic components. In Proceedings of the 2015 16th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE), Budapest, Hungary, 19–22 April 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 1–4, ISBN 978-1-4799-9950-7. [Google Scholar]

- Bertocci, F.; Grandoni, A.; Djuric-Rissner, T. Scanning Acoustic Microscopy (SAM): A Robust Method for Defect Detection during the Manufacturing Process of Ultrasound Probes for Medical Imaging. Sensors 2019, 19, 4868. [Google Scholar] [CrossRef]

- Briggs, A.; Kolosov, O.V. Acoustic Microscopy, 2nd ed.; Oxford University Press: Oxford, UK, 2010; ISBN 9780199232734. [Google Scholar]

- JEDEC. JESD51-14. Transient Dual Interface Test Method for the Measurement of the Thermal Resistance Junction to Case of Semiconductor Devices with Heat Flow through a Single Path; JEDEC Solid State Technology Association: Arlington, VA, USA, 2010. [Google Scholar]

- JEDEC. JESD282B.01. Silicon Rectifier Diodes; JEDEC Solid State Technology Association: Arlington, VA, USA, 2002. [Google Scholar]

- JEDEC. JESD51-51. Implementation of the Electrical Test Method for the Measurement of Real Thermal Resistance and Impedance of Light-Emitting Diodes with Exposed Cooling; JEDEC Solid State Technology Association: Arlington, VA, USA, 2012. [Google Scholar]

- JEDEC. JESD24-3. Thermal Impedance Measurements for Vertical Power MOSFETs (Delta Source-Drain Voltage Method); JEDEC Solid State Technology Association: Arlington, VA, USA, 1990. [Google Scholar]

- JEDEC. JESD24-6. Thermal Impedance Measurements for Insulated Gate Bipolar Transistors; JEDEC Solid State Technology Association: Arlington, VA, USA, 1991. [Google Scholar]

- JEDEC. JESD24-12. Thermal Impedance Measurement for Insulated Gate Bipolar Transistors-(Delta VCE(on) Method); JEDEC Solid State Technology Association: Arlington, VA, USA, 2004. [Google Scholar]

- JEDEC. JESD24-4. Thermal Impedance Measurements for Bipolar Transistors (Delta Base-Emitter Voltage Method); JEDEC Solid State Technology Association: Arlington, VA, USA, 1990. [Google Scholar]

- JEDEC. JESD51-1. Integrated Circuits Thermal Measurement Method-Electrical Test Method (Single Semiconductor Device); JEDEC Solid State Technology Association: Arlington, VA, USA, 1995. [Google Scholar]

- Daiminger, F.X.; Gruber, M.; Dendorfer, C.; Zahner, T. Experimental and theoretical considerations on the offset correction of transient cooling curves of light emitting diodes based on JESD51-14. In Proceedings of the 20th International Workshop on Thermal Investigations of ICs and Systems, London, UK, 24–26 September 2014; pp. 1–6. [Google Scholar]

- Schmid, M.; Gordon, E. Measurement of the Transient Thermal Impedance of MOSFETs over the Sensitivity of the Threshold Voltage. In Proceedings of the 20th European Conference on Power Electronics and Applications, Riga, Latvia, 17–21 September 2018. [Google Scholar]

- Hans, A.; Schmid, M.; Liu, E.; Elger, G. Transient thermal analysis as measurement method for IC package structural integrity. Chin. Phys. B 2015, 24, 068105. [Google Scholar] [CrossRef]

- Elger, G.; Kandaswamy, S.V.; Liu, E.; Hanss, A.; Schmid, M.; Derix, R.; Conti, F. Analysis of solder joint reliability of high power LEDs by transient thermal testing and transient finite element simulations. Microelectron. J. 2015, 46, 1230–1238. [Google Scholar] [CrossRef]

- Hanss, A.; Liu, E.; Schmid, M.; Elger, G. The influence of voids in solder joints on thermal performance and reliability investigated with transient thermal analysis. In Proceedings of the 2015 21st International Workshop on Thermal Investigations of ICs and Systems (THERMINIC), Paris, France, 30 September–2 October 2015; Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2015; pp. 1–6. [Google Scholar]

- Székely, V. A new evaluation method of thermal transient measurement results. Microelectron. J. 1997, 28, 277–292. [Google Scholar] [CrossRef]

- Székely, V.; Van Bien, T. Fine structure of heat flow path in semiconductor devices: A measurement and identification method. Solid-State Electron. 1988, 31, 1363–1368. [Google Scholar] [CrossRef]

- Schweitzer, D.; Pape, H.; Chen, L. Transient Measurement of the Junction-To-Case Thermal Resistance Using Structure Functions: Chances and Limits. In Proceedings of the 2008 Twenty-fourth Annual IEEE Semionductor Thermal Measurement and Management Symposium, San Jose, CA, USA, 16–20 March 2008; pp. 191–197. [Google Scholar] [CrossRef]

- Elger, G.; Schmid, M.; Hanss, A.; Müller, D. Automatic Panel Level Transient Thermal Tester. In LED professional Symposium + Expo 2017; Luger Research e.U.: Bregenz, Austria, 2017. [Google Scholar]

- Schmid, M.; Krishna, B.S.; Elger, G. Automatic Transient Thermal Impedance Tester for Quality Inspection of Soldered and Sintered Power Electronic Devices on Panel and Tile Level. In Proceedings of the 2019 IEEE 69th Electronic Components and Technology Conference (ECTC), Institute of Electrical and Electronics Engineers (IEEE), Las Vegas, NV, USA, 28–31 May 2019; pp. 2324–2330. [Google Scholar]

- Bhogaraju, S.K.; Conti, F.; Kotadia, H.R.; Keim, S.; Tetzlaff, U.; Elger, G. Novel approach to copper sintering using surface enhanced brass micro flakes for microelectronics packaging. J. Alloys Compd. 2020, 844, 156043. [Google Scholar] [CrossRef]

| Gr. | Description of Manipulation | Sample Count | High-Side MOSFET | Low-Side MOSFET |

|---|---|---|---|---|

| M1 | Reference | 10 | 1.00 | 1.00 |

| M2 | Adhesive remove under HS-M | 10 | 2.11 | 1.09 |

| M3 | Adhesive half removed | 10 | 1.08 | 1.18 |

| M4 | Tilt around short edge toward HS-M | 6 | 1.03 | 1.36 |

| M5 | Tilt around short edge from HS-M | 6 | 2.61 | 1.24 |

| M6 | Tilt around long edge to the left side | 4 | 1.25 | 1.57 |

| M7 | Tilt around long edge to the right side | 4 | 1.35 | 1.4 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Schmid, M.; Bhogaraju, S.K.; Liu, E.; Elger, G. Comparison of Nondestructive Testing Methods for Solder, Sinter, and Adhesive Interconnects in Power and Opto-Electronics. Appl. Sci. 2020, 10, 8516. https://doi.org/10.3390/app10238516

Schmid M, Bhogaraju SK, Liu E, Elger G. Comparison of Nondestructive Testing Methods for Solder, Sinter, and Adhesive Interconnects in Power and Opto-Electronics. Applied Sciences. 2020; 10(23):8516. https://doi.org/10.3390/app10238516

Chicago/Turabian StyleSchmid, Maximilian, Sri Krishna Bhogaraju, E Liu, and Gordon Elger. 2020. "Comparison of Nondestructive Testing Methods for Solder, Sinter, and Adhesive Interconnects in Power and Opto-Electronics" Applied Sciences 10, no. 23: 8516. https://doi.org/10.3390/app10238516

APA StyleSchmid, M., Bhogaraju, S. K., Liu, E., & Elger, G. (2020). Comparison of Nondestructive Testing Methods for Solder, Sinter, and Adhesive Interconnects in Power and Opto-Electronics. Applied Sciences, 10(23), 8516. https://doi.org/10.3390/app10238516