CMOS Low-Power Optical Transceiver for Short Reach

Abstract

1. Introduction

2. Low-Power Design Methodology for Optical Transceivers

2.1. System-Level Consideration

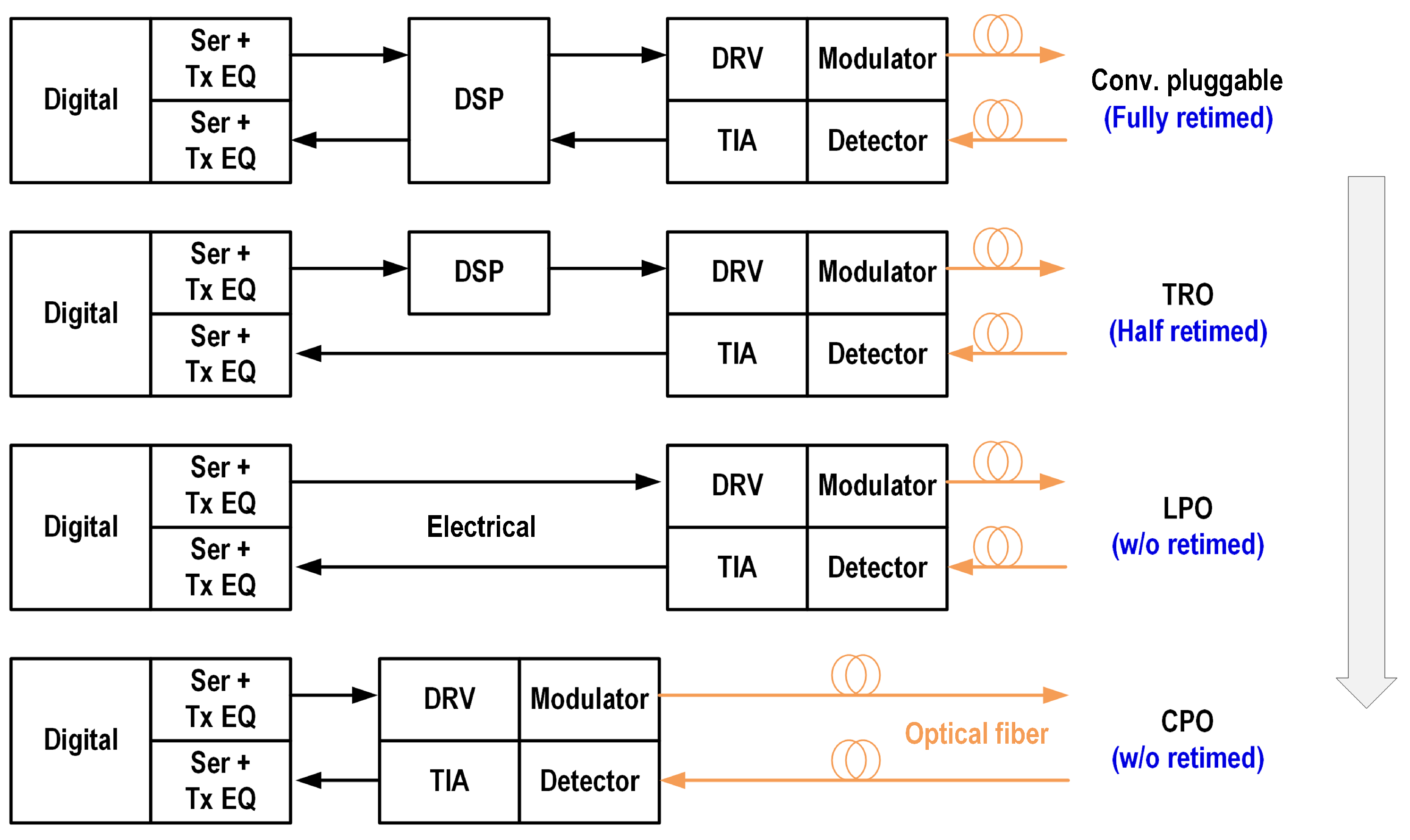

- Shorten the electrical interface: change the optical module structure from pluggable optical modules with long PCB traces to CPOs with ultra-short interconnects, reducing the electrical insertion losses and enabling low-complexity equalization (e.g., CTLE, FFE, DFE) integration with the analog front end.

- Eliminate high-order DSP equalization: short-reach application relaxes the dispersion tolerance, eliminating the need for DSP for dispersion compensation.

- Retimed Tx/Rx topology: integration with clock data recovery (CDR) circuits brings better signal integrity with a lower jitter, which eliminates power-hungry, high-speed analog-to-digital converters (ADCs) at the receiver.

2.2. Circuit-Level Techniques

2.2.1. Low-Power Techniques for Drivers

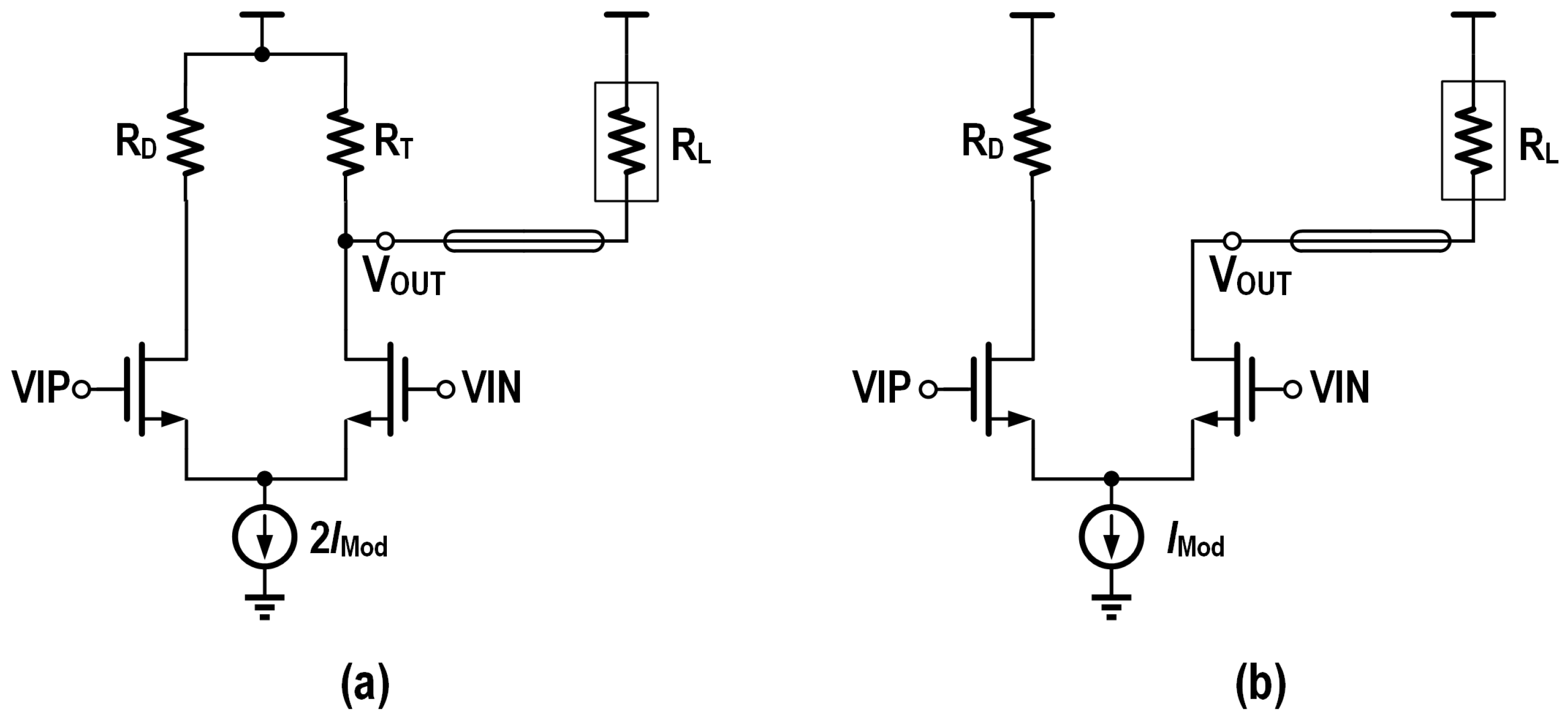

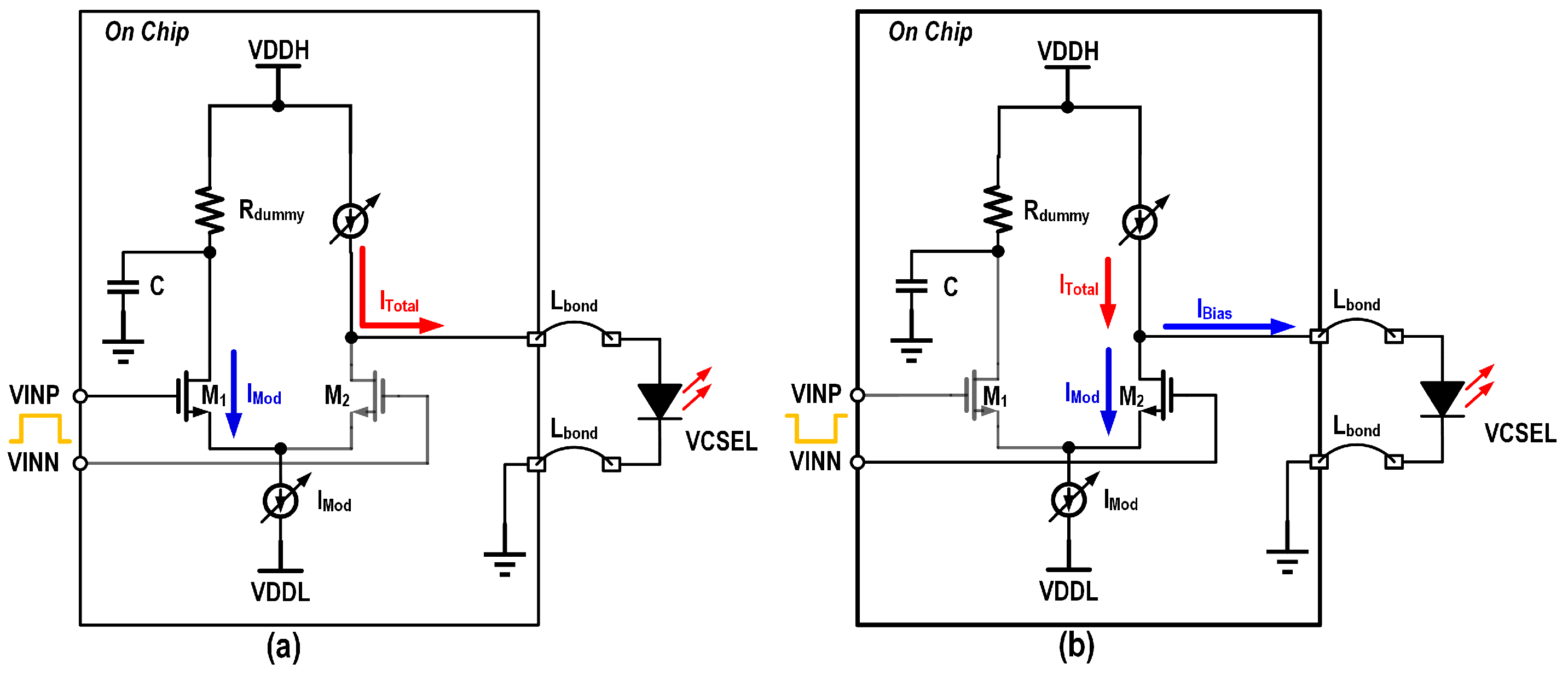

- Open-drain output topology: employing compact uncooled modulators with direct coupling avoids transmission line effects, eliminating the need for termination for impedance matching, as shown in Figure 2b, where the open-drain output topology can be utilized to eliminate the shunt current of the terminal resistors and improve the current modulation efficiency.

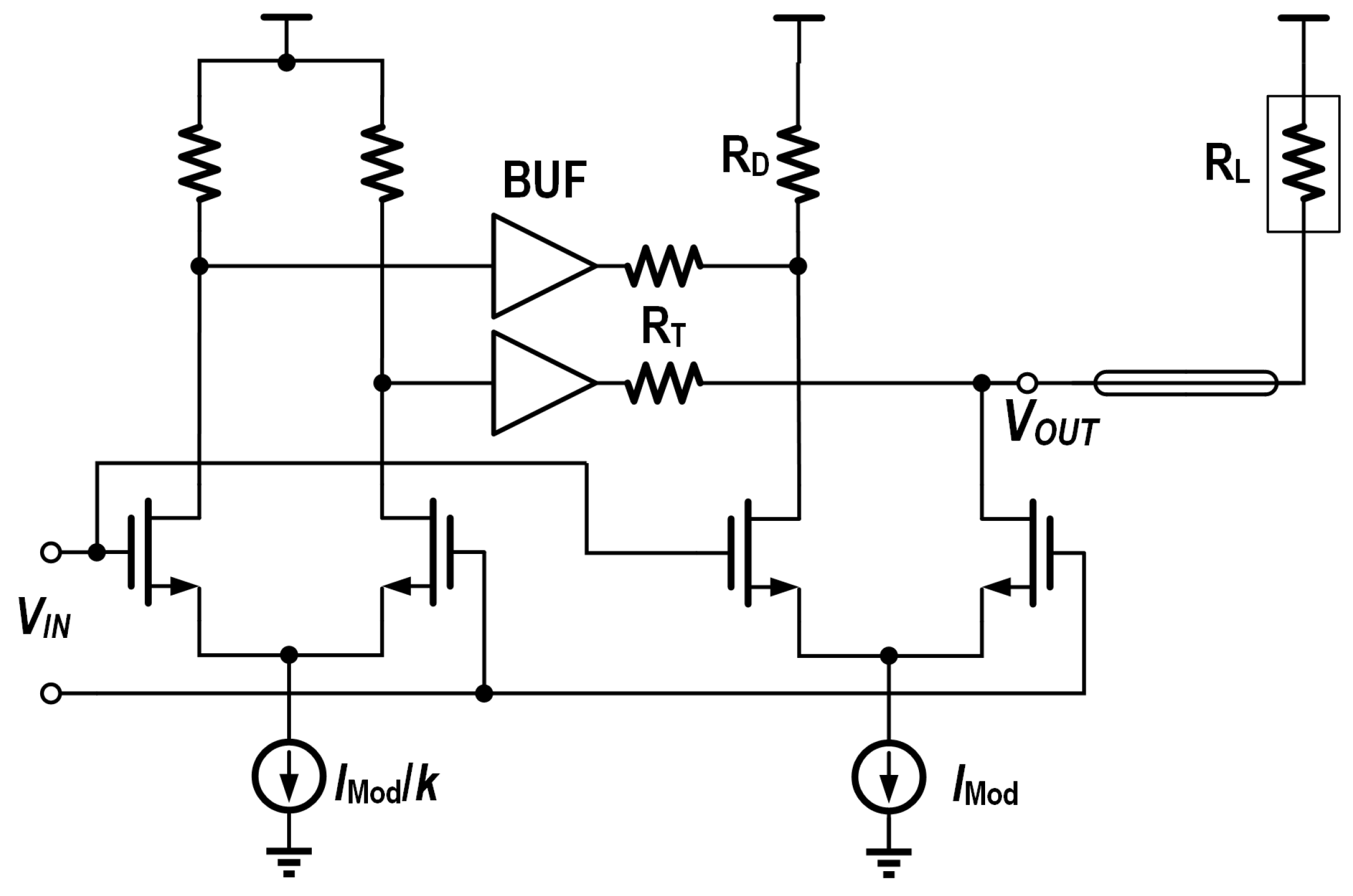

- Stack structure: For direct-coupled VCSEL anode driving, a higher common-mode voltage is needed at the output node. To eliminate the need for additional low-dropout regulators (LDOs), the output stage can be stacked on top of the previous stage. This not only raises the output node voltage level but also reuses the current, thereby achieving significant power savings [16].

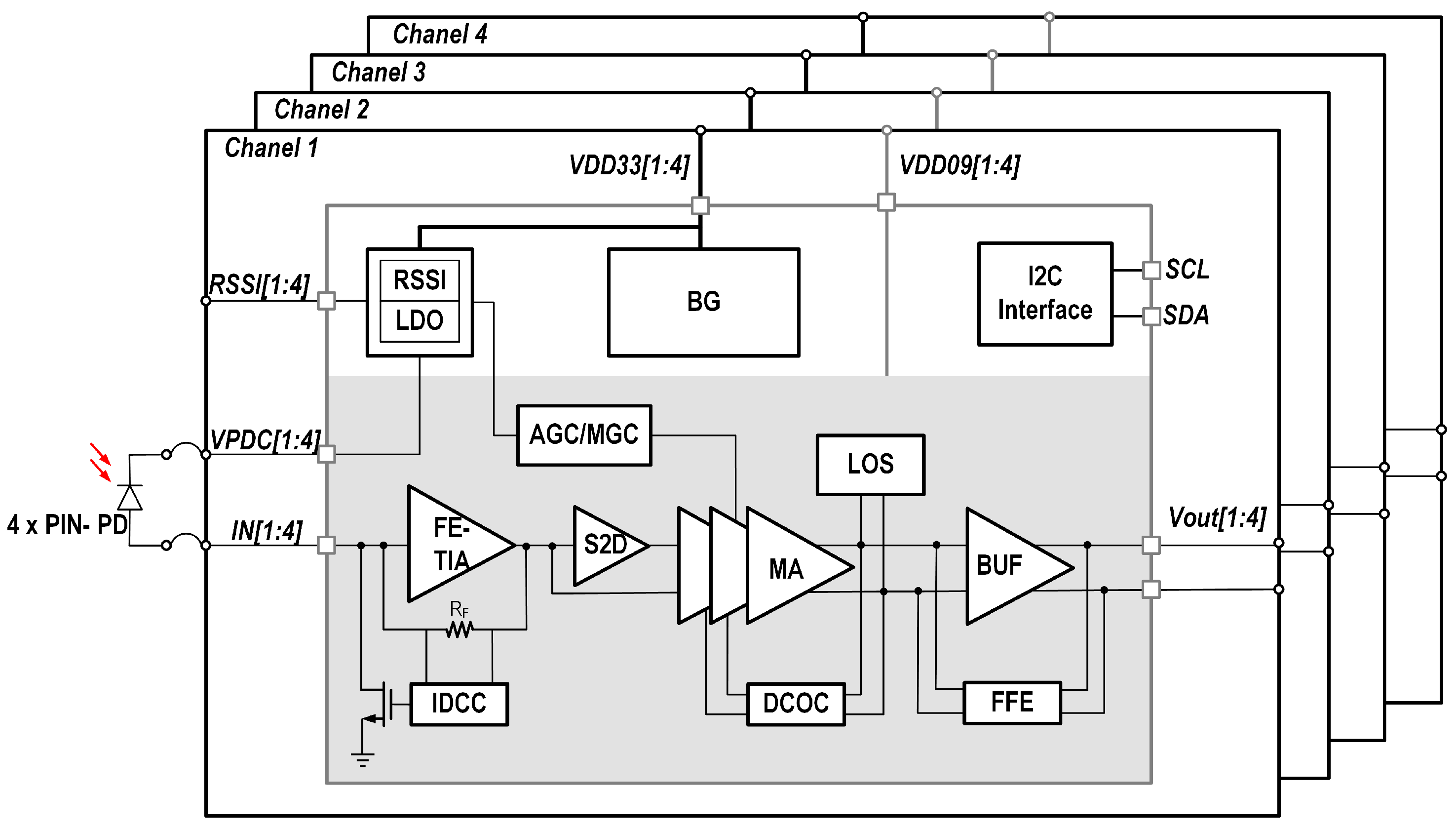

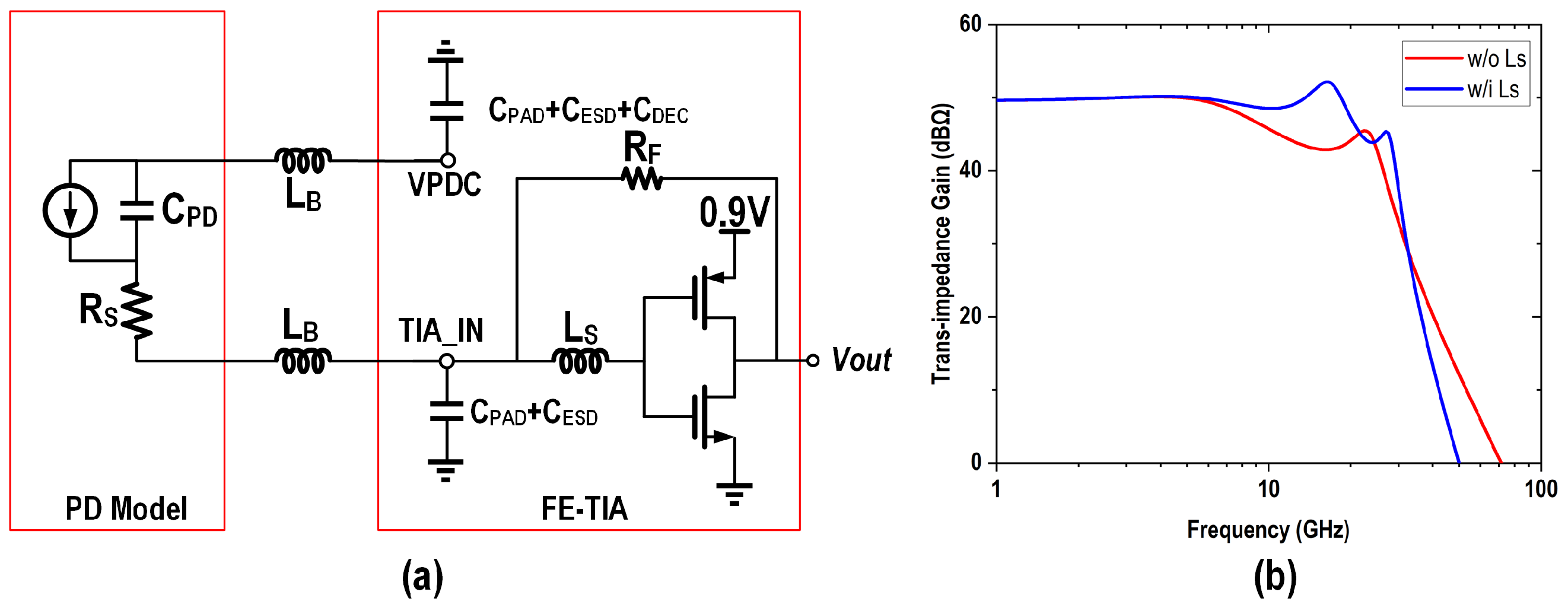

2.2.2. Low-Power Techniques for TIAs

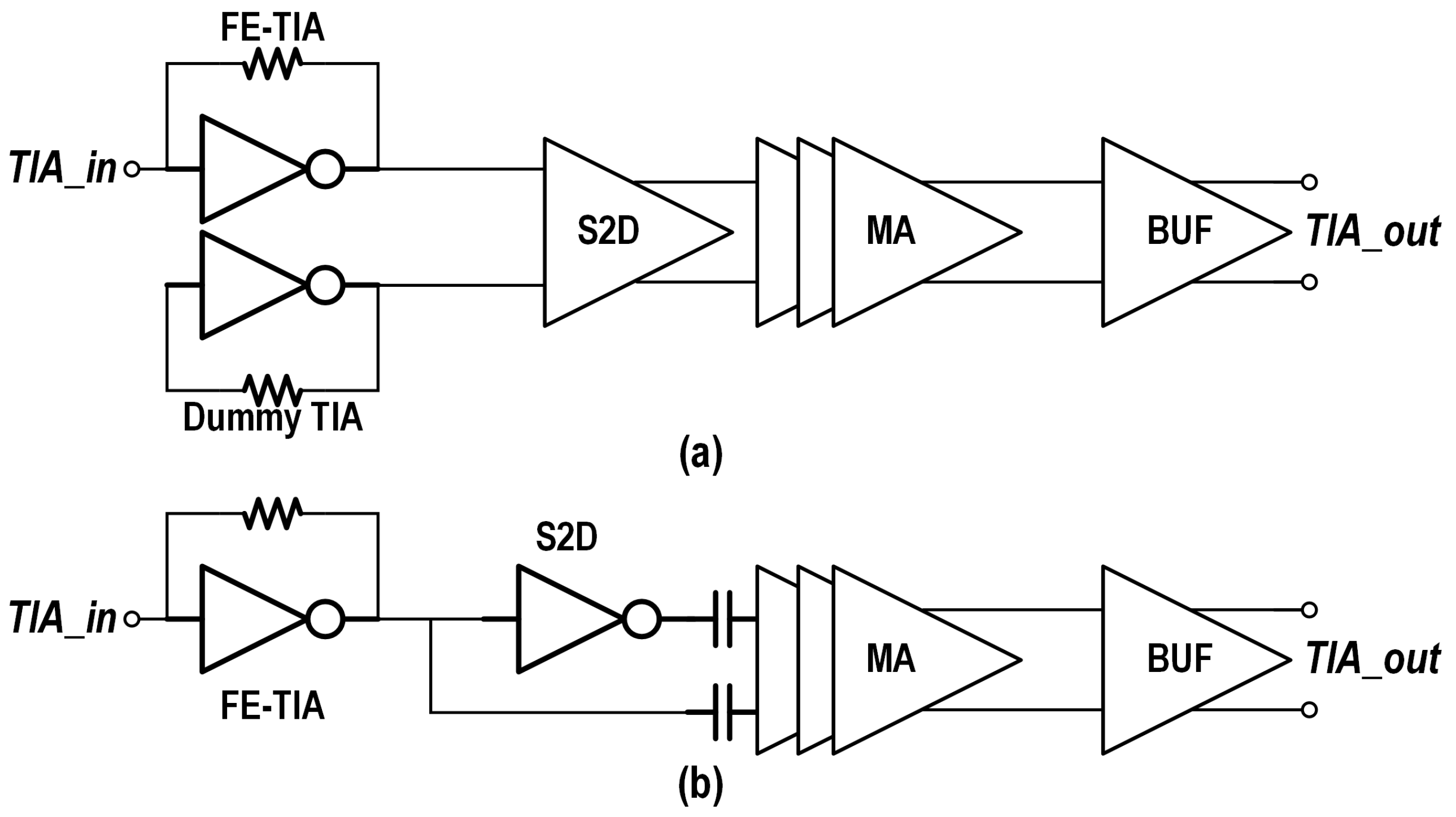

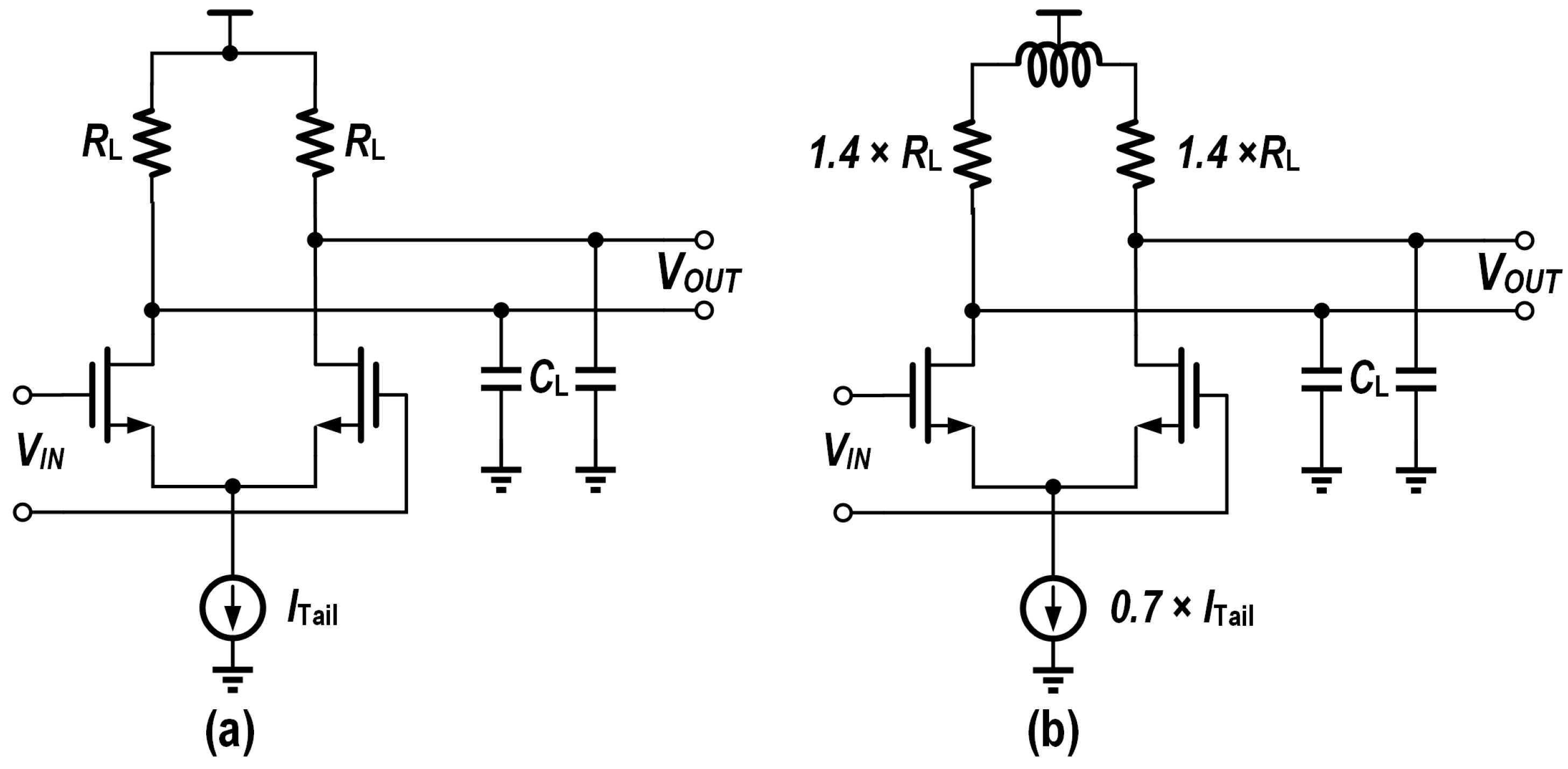

- Single-ended front-end TIA without a dummy TIA: Though integration with a dummy TIA can reduce the offset of single-ended to differential converter (S2D), as shown in Figure 4a, it brings additional power consumption. By balancing the parasitic capacitance and area consumption, AC coupling can be utilized to eliminate the offset without additional power consumption.

- Adaptive biasing: A received signal strength indicator (RSSI) dynamically adjusts the TIA gain with a variable power distribution to match the received optical power. This avoids over-biasing under high-signal conditions. And noise-adaptive biasing: lowering the bias currents in low-noise regimes (high input power) optimizes noise–power tradeoffs.

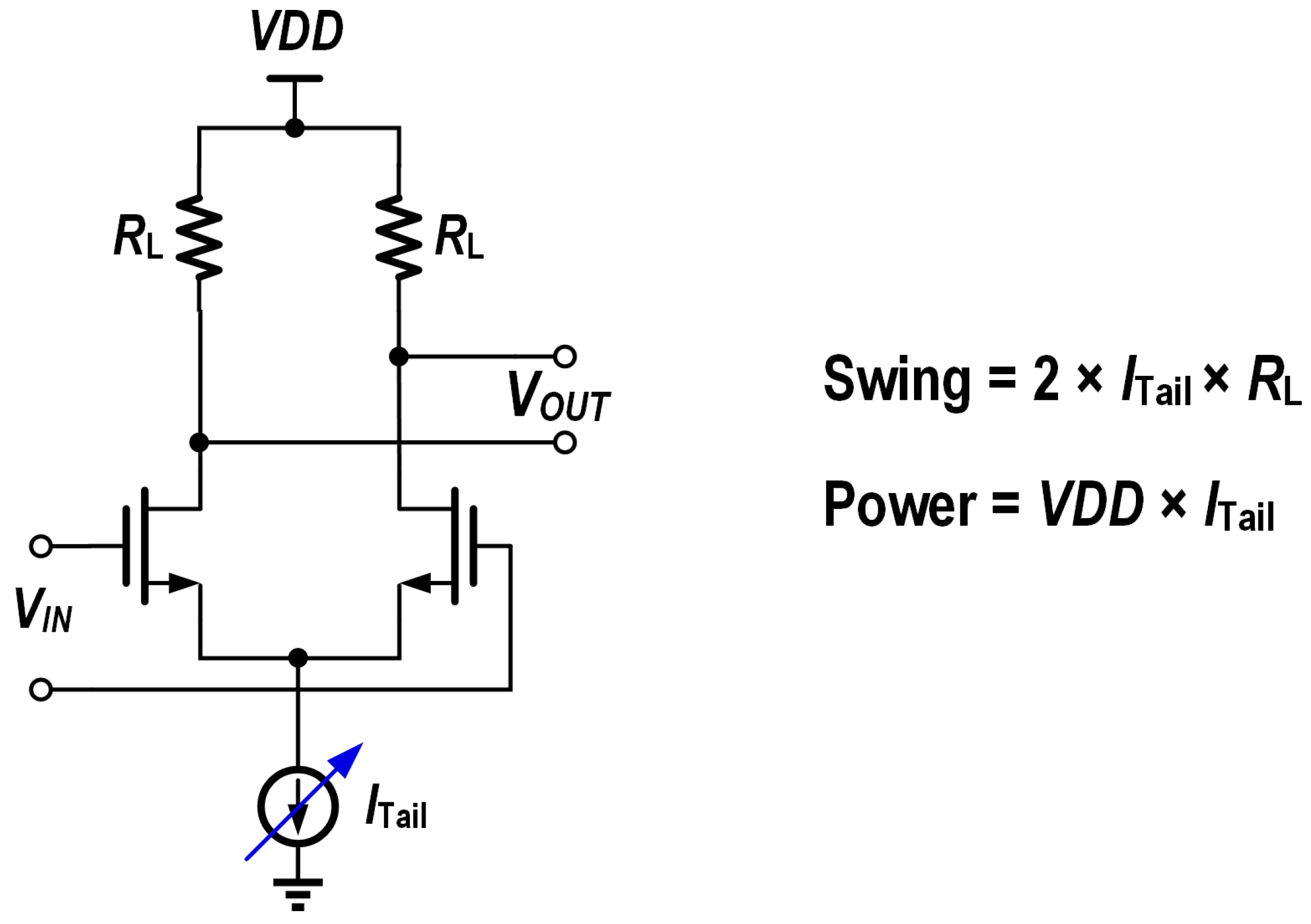

- Adaptive output swing: For the output buffer, which often utilizes the current-steering structure for impedance matching, the output swing is defined by the tail current, as shown in Figure 5. An adaptive output swing with a variable tail current can reduce the power consumption significantly when operating at a low output swing.

2.2.3. Shared Low-Power Design Methods

- Burst mode operation: burst mode operation shuts down the main path in the idle state, thus effectively reducing the power consumption.

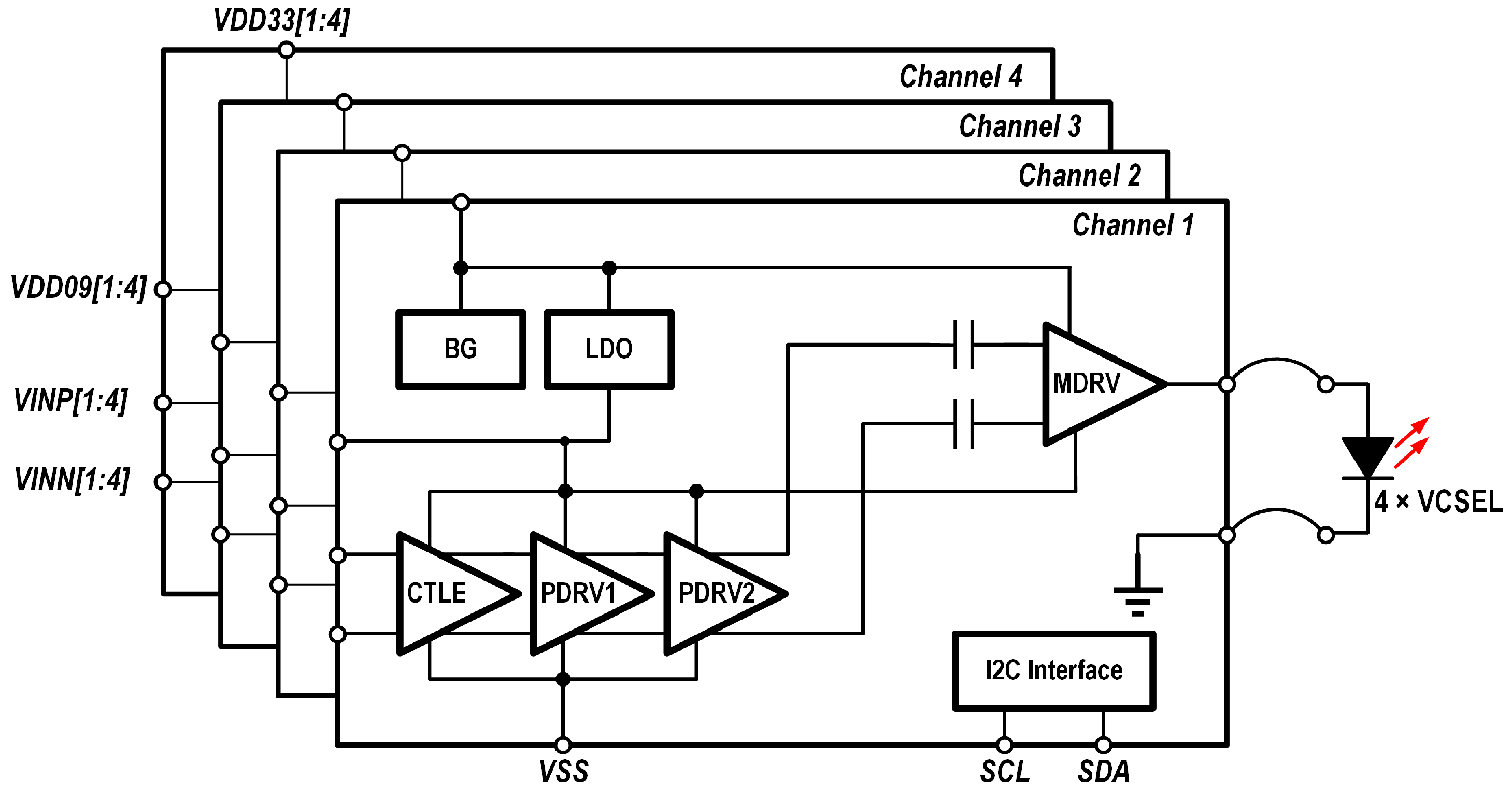

3. Circuit Design

3.1. Driver Design

3.2. TIA Design

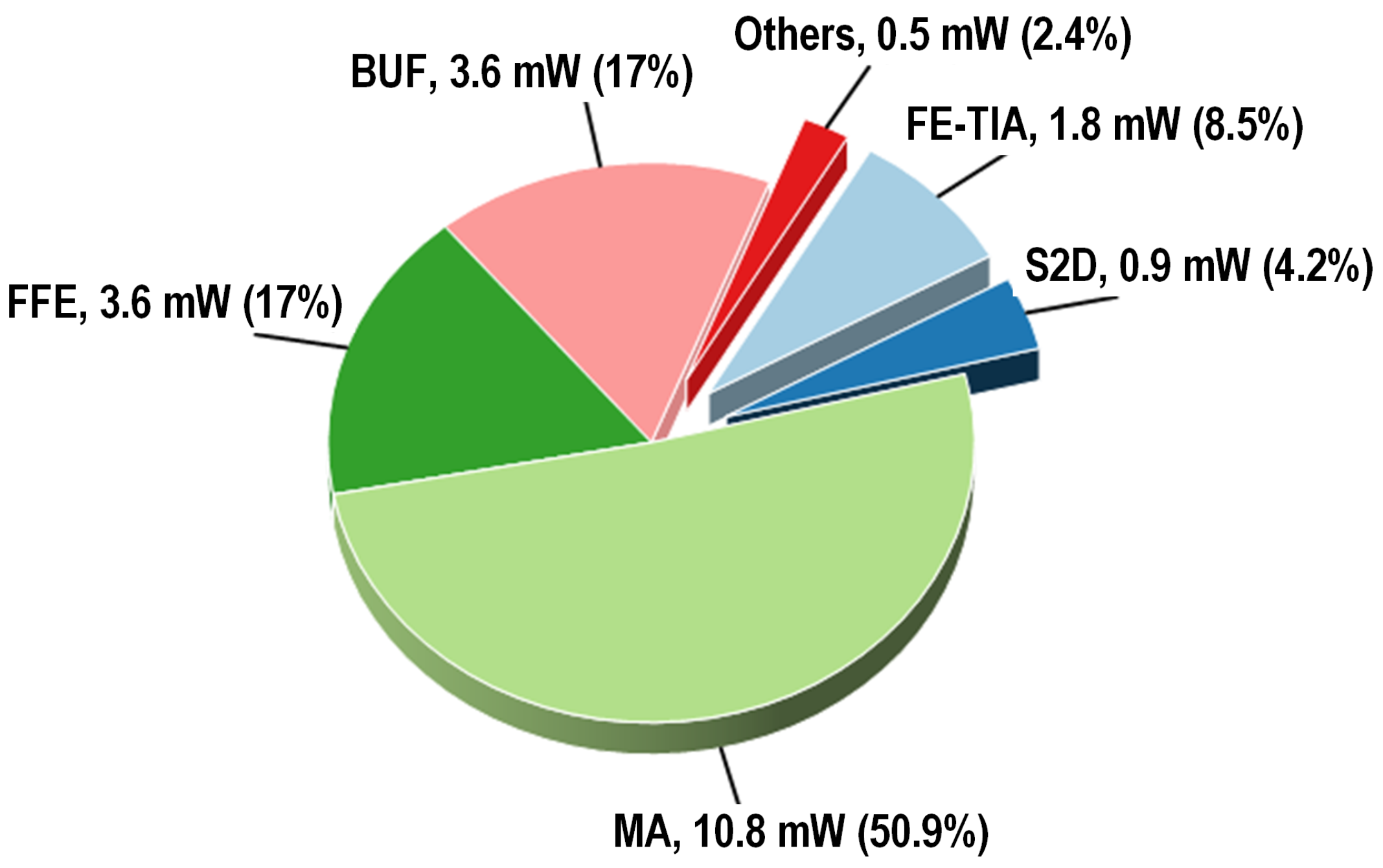

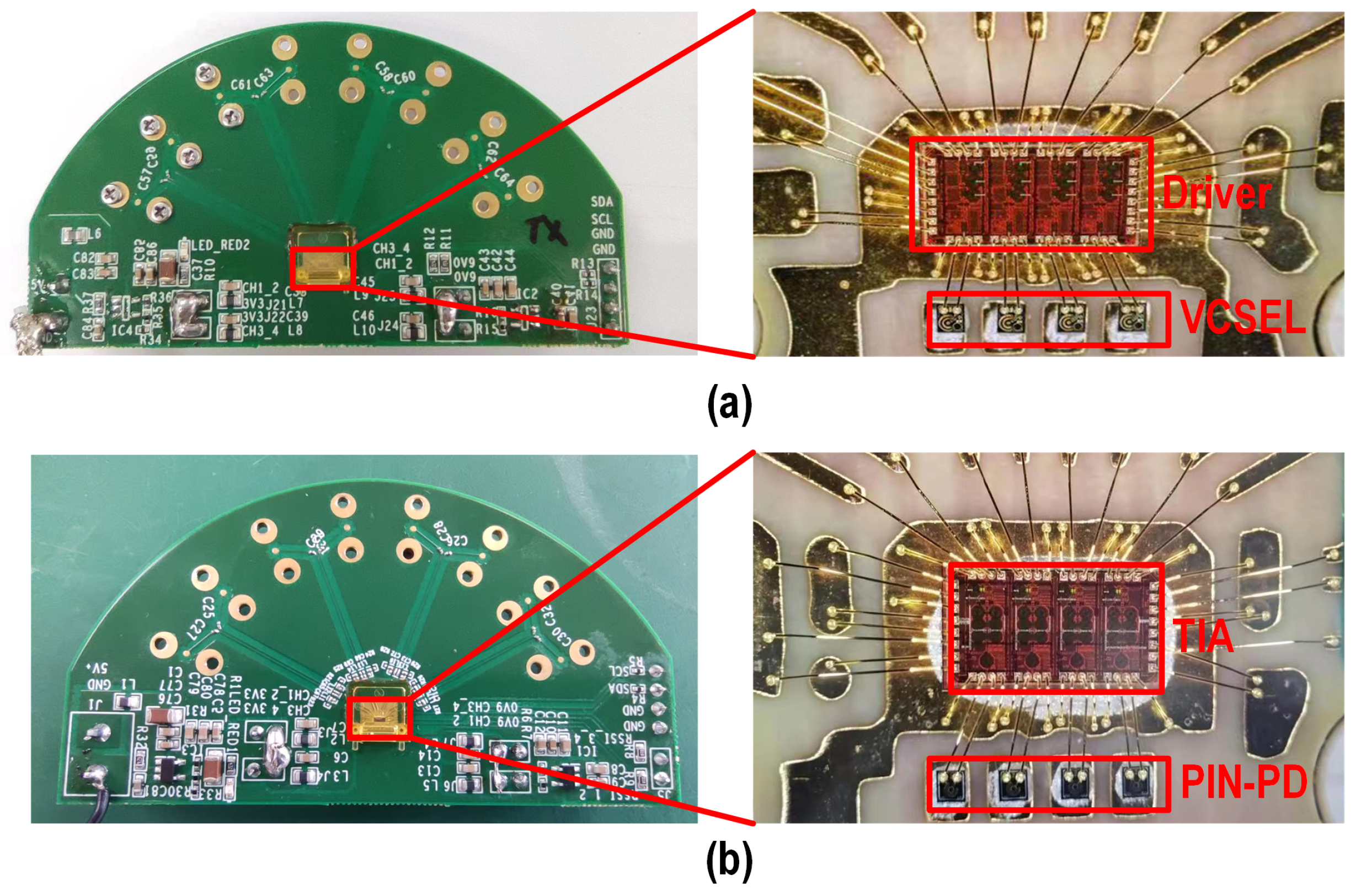

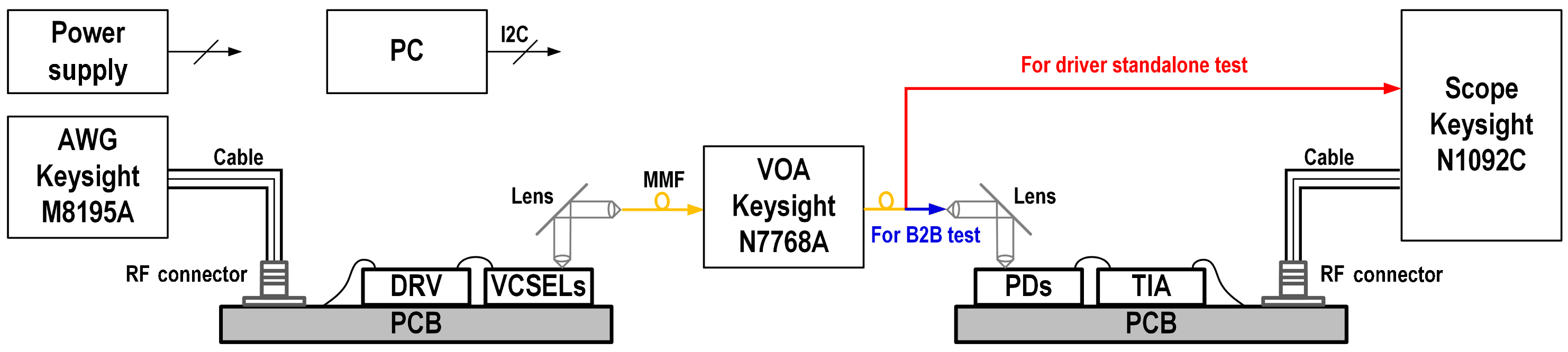

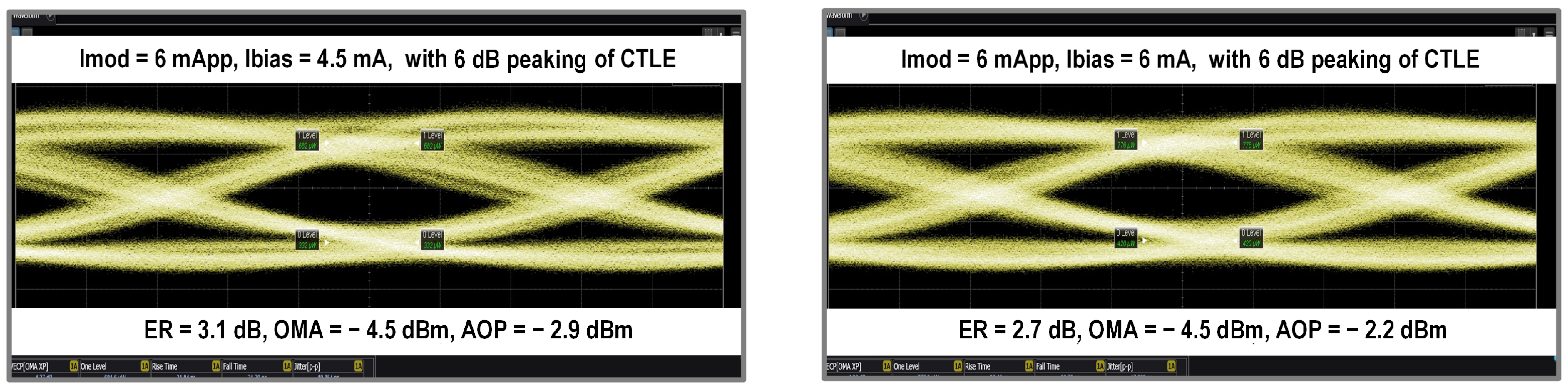

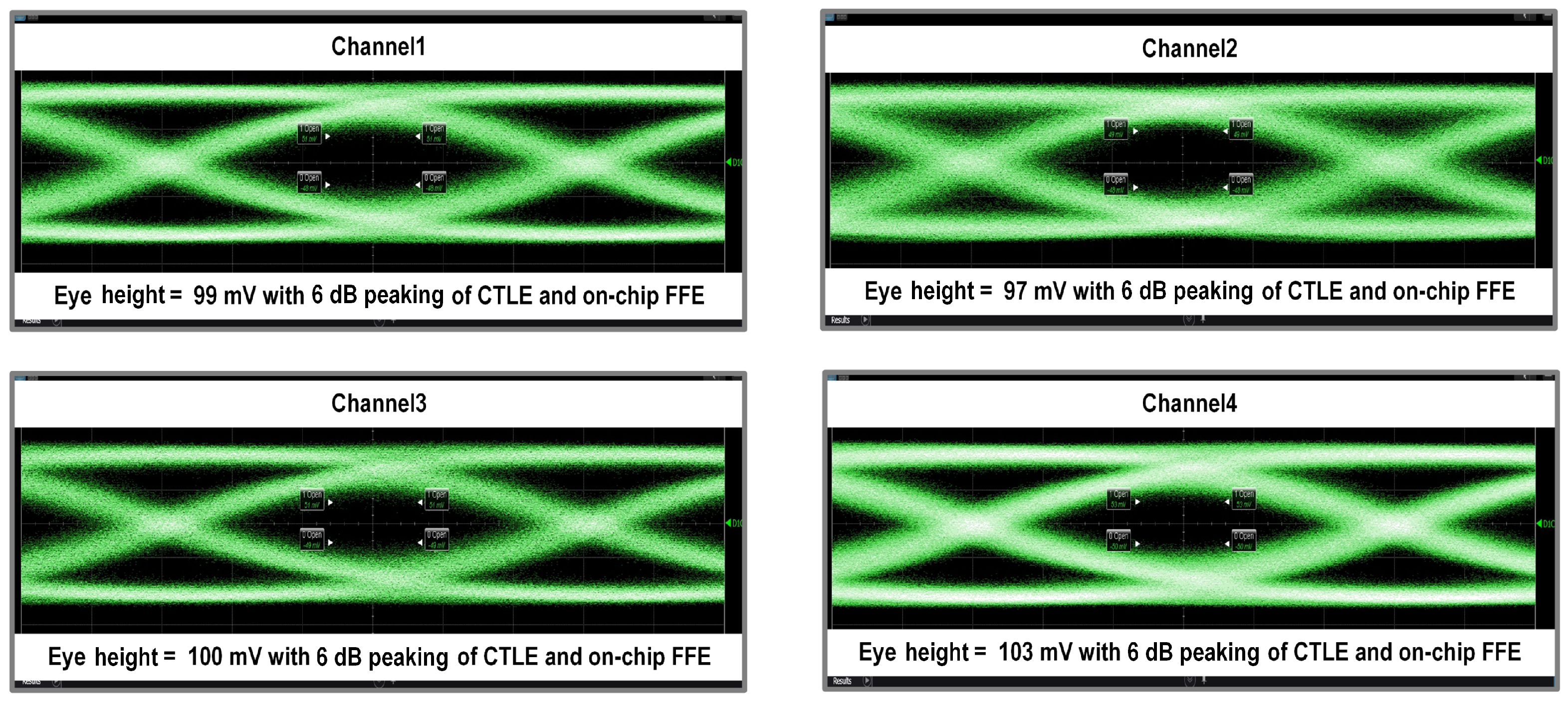

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Xie, C. Datacenter optical interconnects: Requirements and challenges. In Proceedings of the 2017 IEEE Optical Interconnects Conference (OI), Santa Fe, NM, USA, 5–7 June 2017; pp. 37–38. [Google Scholar] [CrossRef]

- Narasimha, A.; Analui, B.; Balmater, E.; Clark, A.; Gal, T.; Guckenberger, D.; Gutierrez, S.; Harrison, M.; Ingram, R.; Koumans, R.; et al. A 40-Gb/s QSFP optoelectronic transceiver in a 0.13 μm CMOS silicon-on-insulator technology. In Proceedings of the 2008 Optical Fiber Communication Conference/National Fiber Optic Engineers Conference, San Diego, CA, USA, 24–28 February 2008; Available online: https://opg.optica.org/abstract.cfm?URI=OFC-2008-OMK7 (accessed on 10 May 2025).

- Nisa, U.U.; Bashir, J. Towards efficient on-chip communication: A survey on silicon nanophotonics and optical networks-on-chip. J. Syst. Archit. 2024, 152, 103171. [Google Scholar] [CrossRef]

- Xie, C.; Zhang, B. Scaling optical interconnects for hyperscale data center networks. Proc. IEEE 2022, 110, 1699–1713. [Google Scholar] [CrossRef]

- Khani, M.; Ghobadi, M.; Alizadeh, M.; Zhu, Z.; Glick, M.; Bergman, K.; Vahdat, A.; Klenk, B.; Ebrahimi, E. SiP-ML: High-bandwidth optical network interconnects for machine learning training. In Proceedings of the 2021 ACM SIGCOMM 2021 Conference, Virtual, 23–27 August 2021; pp. 657–675. [Google Scholar] [CrossRef]

- Minkenberg, C.; Krishnaswamy, R.; Zilkie, A.; Nelson, D. Co-packaged datacenter optics: Opportunities and challenges. IET Optoelectron. 2021, 15, 77–91. [Google Scholar] [CrossRef]

- Cheng, H.T.; Yang, Y.C.; Liu, T.H.; Wu, C.H. Recent Advances in 850 nm VCSELs for High-Speed Interconnects. Photonics 2022, 9, 107. [Google Scholar] [CrossRef]

- Xiang, C.; Bowers, S.M.; Bjorlin, A.; Blum, R.; Bowers, J.E. Perspective on the future of silicon photonics and electronics. Appl. Phys. Lett. 2021, 118, 220501. [Google Scholar] [CrossRef]

- Balemarthy, K.; Shubochkin, R.; Sun, Y. Next-generation wideband multimode fibers for data centers. In Proceedings of the 2016 SPIE OPTO, San Francisco, CA, USA, 13–18 February 2016; Volume 9775. [Google Scholar] [CrossRef]

- Thraskias, C.A.; Lallas, E.N.; Neumann, N.; Schares, L.; Offrein, B.J.; Henker, R.; Plettemeier, D.; Ellinger, F.; Leuthold, J.; Tomkos, I. Survey of photonic and plasmonic interconnect technologies for intra-datacenter and high-performance computing communications. IEEE Commun. Surv. Tutor. 2018, 20, 2758–2783. [Google Scholar] [CrossRef]

- Krishnamoorthy, A.V.; Schwetman, H.; Zheng, X.; Ho, R. Energy-efficient photonics in future high-connectivity computing systems. J. Light. Technol. 2015, 33, 889–900. [Google Scholar] [CrossRef]

- Keuper, J.; Preundt, F.J. Distributed training of deep neural networks: Theoretical and practical limits of parallel scalability. In Proceedings of the 2016 2nd Workshop on Machine Learning in HPC Environments (MLHPC), Salt Lake City, UT, USA, 14 November 2016; pp. 19–26. [Google Scholar] [CrossRef]

- Li, S.A.; Huang, H.; Pan, Z.; Yin, R.; Wang, Y.; Fang, Y.; Zhang, Y.; Bao, C.; Ren, Y.; Li, Z.; et al. Enabling technology in high-baud-rate coherent optical communication systems. IEEE Access 2020, 8, 111318–111329. [Google Scholar] [CrossRef]

- Eid, M.M.; Ibrahim, A.; Rashed, A.N. In line and post erbium-doped fiber amplifiers with ideal dispersion compensation fiber Bragg grating for upgrading optical access networks. J. Opt. Commun. 2025, 45, s271–s279. [Google Scholar] [CrossRef]

- Makwana, M.; Khant, S.; Patel, A. Advancements in Long-Distance PON Connectivity using WDM and EDFA. In Proceedings of the 2024 11th International Conference on Reliability, Infocom Technologies and Optimization (Trends and Future Directions) (ICRITO), Noida, India, 14–15 March 2024; pp. 1–6. [Google Scholar] [CrossRef]

- Hu, S.; Bai, R.; Wang, X.; Peng, Y.; Wang, J.; Xia, T.; Ma, J.; Wang, L.; Zhang, Y.; Chen, X.; et al. A 4 × 25 Gb/s Optical Transmitter Using Low-Cost 10 Gb/s VCSELs in 40-nm CMOS. IEEE Photon. Technol. Lett. 2019, 31, 967–970. [Google Scholar] [CrossRef]

- Peng, P.J.; Huang, H.E.; Huang, W.C.; Lee, P.L.; Lin, M.W.; Juang, Y.Z.; Tseng, S.H. A 56-Gb/s PAM-4 Optical Transceiver with Nonlinear FFE for VCSEL Driver in 40 nm CMOS. In Proceedings of the 2021 IEEE Asian Solid-State Circuits Conference (A-SSCC), Busan, Republic of Korea, 7–10 November 2021; pp. 1–3. [Google Scholar] [CrossRef]

- Khafaji, M.M.; Belfiore, G.; Pliva, J.; Henker, R.; Ellinger, F. A 4 × 45 Gb/s Two-Tap FFE VCSEL Driver in 14-nm FinFET CMOS Suitable for Burst Mode Operation. IEEE J. Solid-State Circuits 2018, 53, 2686–2695. [Google Scholar] [CrossRef]

- Jeong, G.S.; Chi, H.; Kim, K.; Jeong, D.K. A 20-Gb/s 1.27pJ/b low-power optical receiver front-end in 65 nm CMOS. In Proceedings of the 2014 IEEE International Symposium on Circuits and Systems (ISCAS), Melbourne, VIC, Australia, 1–5 June 2014; pp. 1492–1495. [Google Scholar] [CrossRef]

- Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.W.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J.; et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; pp. T230–T231. [Google Scholar] [CrossRef]

- Shi, J.; Yin, B.; Qi, N.; Bai, R.; Li, Z.; Hong, Z.; Chiang, P.Y. Design Techniques for Signal Reflection Suppression in High-Speed 25-Gb/s Laser Drivers in CMOS. IEEE Photon. Technol. Lett. 2018, 30, 39–42. [Google Scholar] [CrossRef]

- Shekhar, S.; Walling, J.S.; Allstot, D.J. Bandwidth Extension Techniques for CMOS Amplifiers. IEEE J. Solid-State Circuits 2006, 41, 2424–2439. [Google Scholar] [CrossRef]

- Yang, R.; Ma, S.; Xia, Y.X.; Yang, Y.Y.; Li, D. Low-Power Inductor-Less Optical Receiver for 50G PON in 28nm CMOS. In Proceedings of the 2023 IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA), Hefei, China, 27–29 October 2023; pp. 124–125. [Google Scholar] [CrossRef]

- Xia, Y.; Ma, S.; Zhao, W.; Li, J.; Yang, R.; Yano, Y.; Liu, X.; Zhang, F.; Yang, J.; Shi, W.; et al. An Integrated Burst-Mode 2R Receiver Employing Fast Residual Offset Canceller for XGS-PON in 40-nm CMOS. In Proceedings of the 2024 IEEE Custom Integrated Circuits Conference (CICC), Denver, CO, USA, 21–24 April 2024; pp. 1–2. [Google Scholar] [CrossRef]

- Lakshmikumar, K.R.; Kurylak, A.; Nagaraju, M.; Booth, R.; Nandwana, R.K.; Pampanin, J.; Boccuzzi, V. A process and temperature insensitive CMOS linear TIA for 100 Gbps/λ PAM-4 optical links. In Proceedings of the 2018 IEEE Custom Integrated Circuits Conference (CICC), San Diego, CA, USA, 8–11 April 2018; pp. 1–4. [Google Scholar] [CrossRef]

- Fard, M.M.; Liboiron-Ladouceur, O.; Cowan, G.E. 1.23-pJ/bit 25-Gb/s Inductor-Less Optical Receiver with Low-Voltage Silicon photodetector. IEEE J. Solid-State Circuits 2018, 53, 1793–1805. [Google Scholar] [CrossRef]

- Zhou, G.; Mao, L.; Xie, S.; Min, C. A 30Gbps 1.25 pJ/b CMOS receiver analog front-end with low supply voltage. IEICE Electron. Express 2021, 18, 20210114. [Google Scholar] [CrossRef]

| Scenarios | Short-Reach | Medium-Reach | Long-Reach |

|---|---|---|---|

| Applications | Intra-rack, LAN | Inter-rack, metro access | Regional networks |

| Latency | Ultra-low | Moderate | High |

| Requirements | High density | Scalability | Robustness |

| Technologies | VCSELs, SiPh, MMF | EMLs, SiPh, SMF | Coherent, EDFAs, WDM |

| Power Efficiency | 1–5 pJ/bit | 5–15 pJ/bit | 15–100+ pJ/bit |

| Structure | Conv. pluggable | TRO | LPO | CPO |

|---|---|---|---|---|

| DSP integration | Tx/Rx DSP | Tx DSP | No DSP | No DSP |

| Power efficiency | 10–15 pJ/bit | 7–10 pJ/bit | 3–5 pJ/bit | 1–2 pJ/bit |

| Thermal | High | Medium | Low | Ultra-low |

| Reach | 10 km+ | <2 km | <500 m | <100 m |

| Device | VCSEL | DFB | EML | MZM |

|---|---|---|---|---|

| Modulation type | Direct | Direct | External | External |

| Drive swing | <10 mA | ∼40 mA | 1–2 V | 3–5 V |

| Power consumption | Very low | Low | Moderate | High |

| Chirp | Moderate | High | Low | Very low |

| Launch power | Low | Medium | Medium | High |

| Transmission range | <2 km | ∼10 km | ∼40 km | >100 km |

| [16] | [17] | [18] | This Work | |

|---|---|---|---|---|

| Process | 40 nm CMOS | 40 nm CMOS | 14 nm FinFET | 28 nm CMOS |

| Data rate (Gbps) | 25 | 56 | 45 | 25 |

| Signaling | NRZ | PAM4 | NRZ | NRZ |

| Driving type | Anode | Cathode | Anode | Anode |

| VCSEL BW (GHz) | 10 | 16 | 20 | 14 |

| Negative supply | No | No | Yes | No |

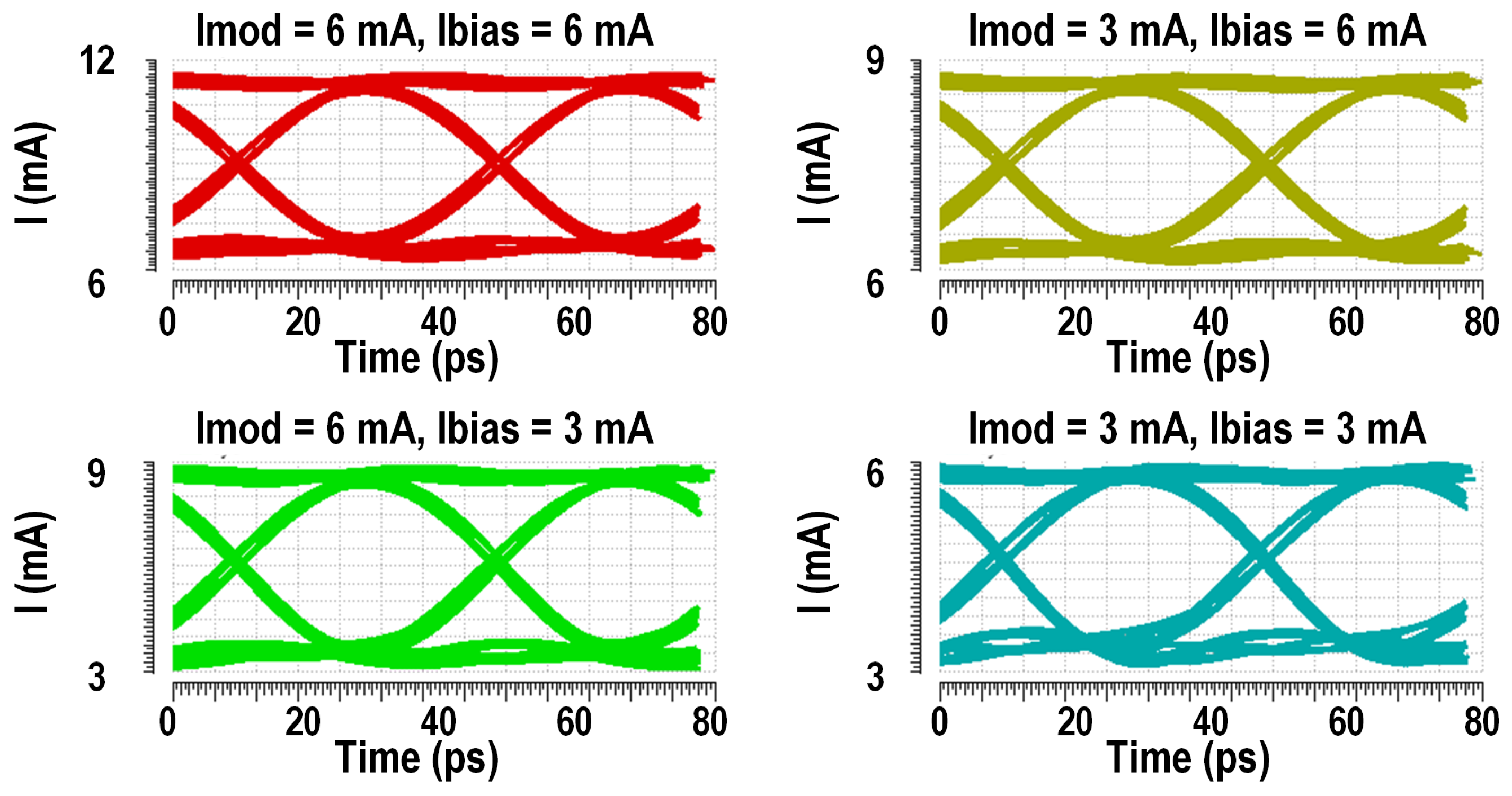

| OMA (dBm) | N/A | −0.9 | 1.4 | −4.5 * |

| ER (dB) | 4.5 | N/A | N/A | 3.1 * |

| () | 6 | N/A | 7 | 6 |

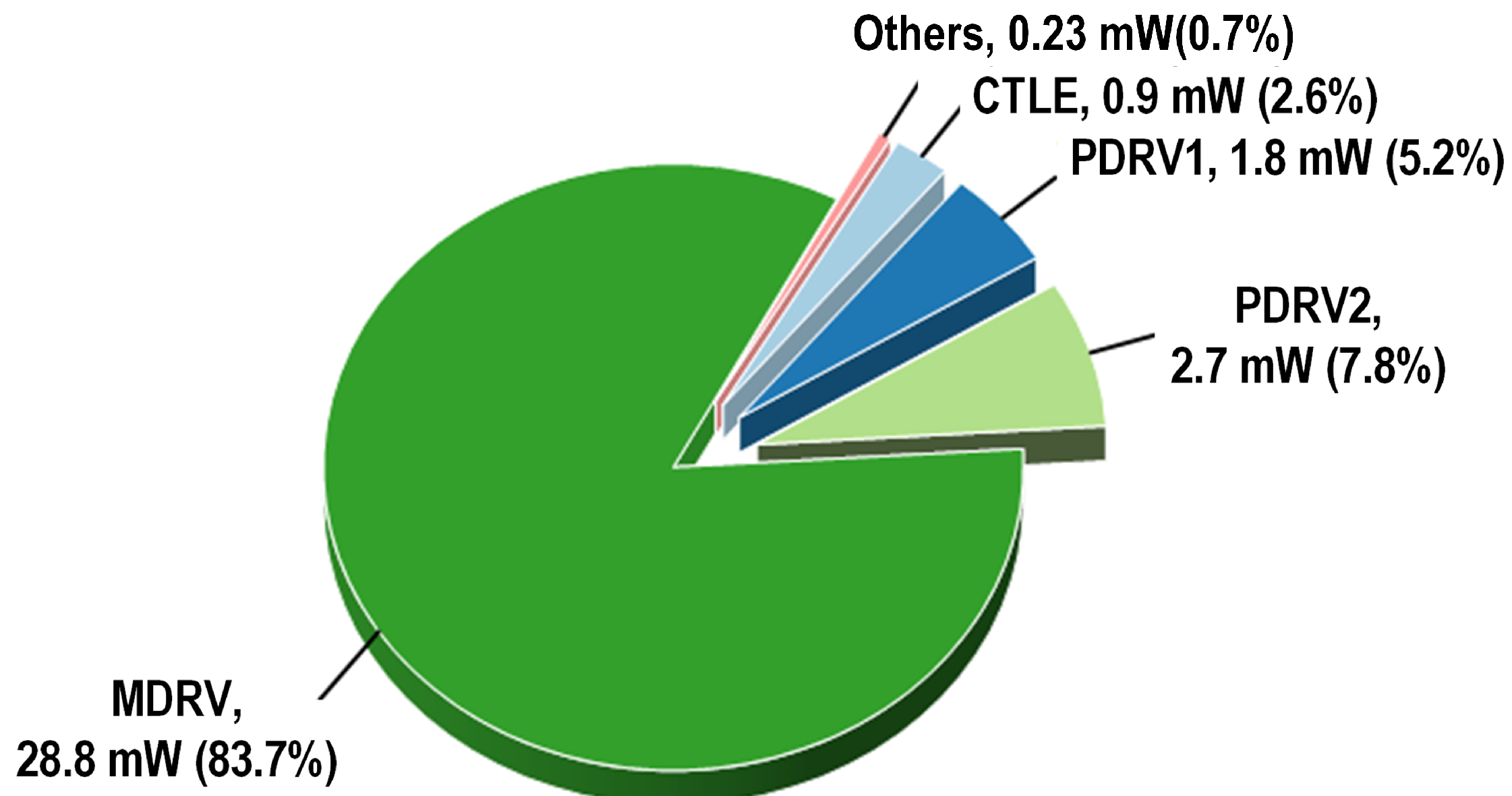

| Power (mW) | 280 | 97 | 81.5 | 29.9 †–39.8 ‡ |

| Efficiency (pJ/bit) | 11.2 | 1.73 | 1.81 | 1.20 †–1.59 ‡ |

| [19] | [26] | [27] | This Work | |

|---|---|---|---|---|

| Process | 65 nm CMOS | 65 nm CMOS | 40 nm CMOS | 28 nm CMOS |

| Data rate (Gbps) | 20 | 25 | 30 | 20 |

| Channel | 1 | 1 | 1 | 4 |

| Gain (dB) | 78 | 69.4 | 63.8 | 68.4–78.5 |

| IRN (A) | 3.9 | 3.28 | 14.9 | 1.64 † |

| Power (mW) | 45.3 | 30.8 | 37.5 | 13.2 †–21.2 ‡ |

| Efficiency (pJ/bit) | 1.27 | 1.23 | 1.25 | 0.66 †–1.06 ‡ |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yang, R.; Dang, Y.; Chen, J.; Li, D.; Svelto, F. CMOS Low-Power Optical Transceiver for Short Reach. Micromachines 2025, 16, 587. https://doi.org/10.3390/mi16050587

Yang R, Dang Y, Chen J, Li D, Svelto F. CMOS Low-Power Optical Transceiver for Short Reach. Micromachines. 2025; 16(5):587. https://doi.org/10.3390/mi16050587

Chicago/Turabian StyleYang, Ruixuan, Yiming Dang, Jinhao Chen, Dan Li, and Francesco Svelto. 2025. "CMOS Low-Power Optical Transceiver for Short Reach" Micromachines 16, no. 5: 587. https://doi.org/10.3390/mi16050587

APA StyleYang, R., Dang, Y., Chen, J., Li, D., & Svelto, F. (2025). CMOS Low-Power Optical Transceiver for Short Reach. Micromachines, 16(5), 587. https://doi.org/10.3390/mi16050587