The Planar Core–Shell Junctionless MOSFET

Abstract

1. Introduction

2. Architecture of the CS-JL Transistor

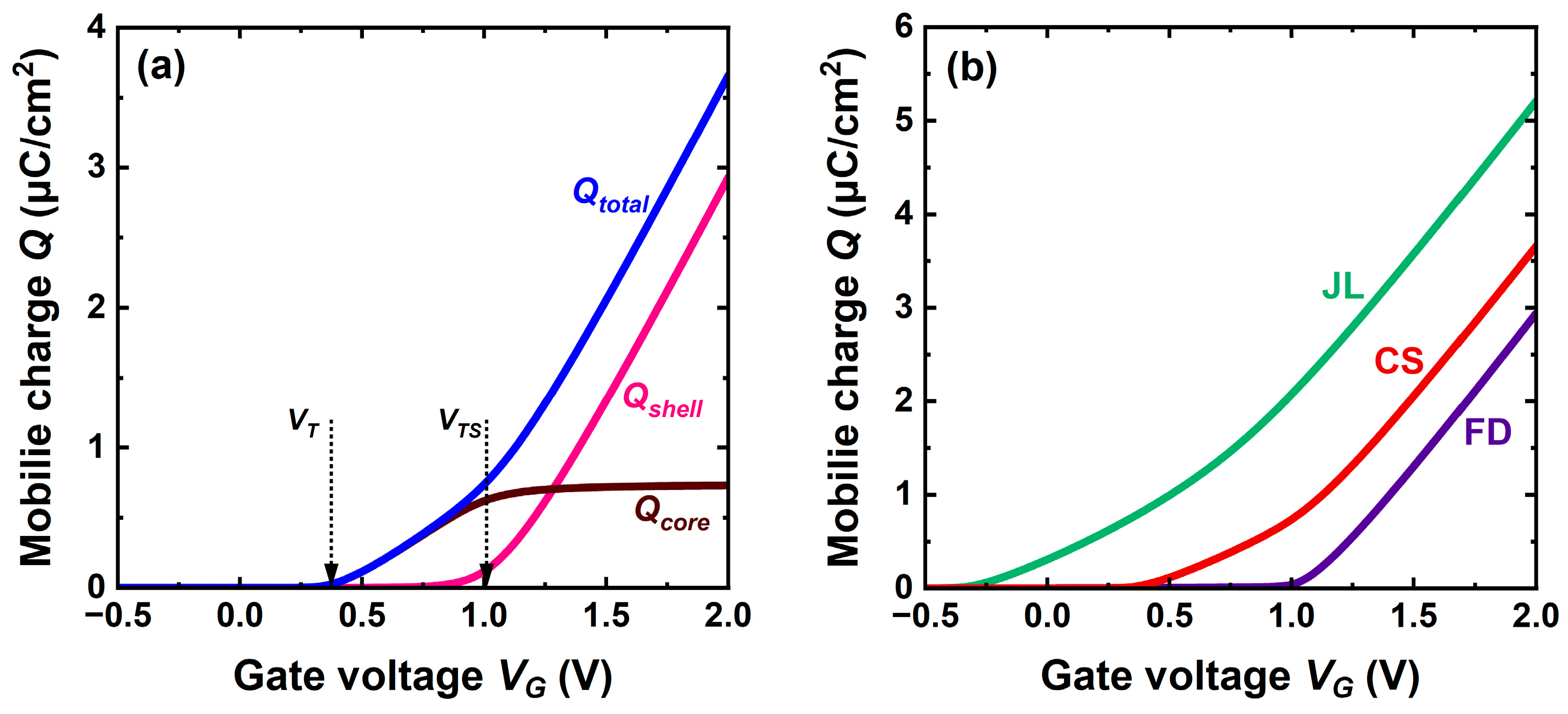

3. Gate-Induced Charge Distribution

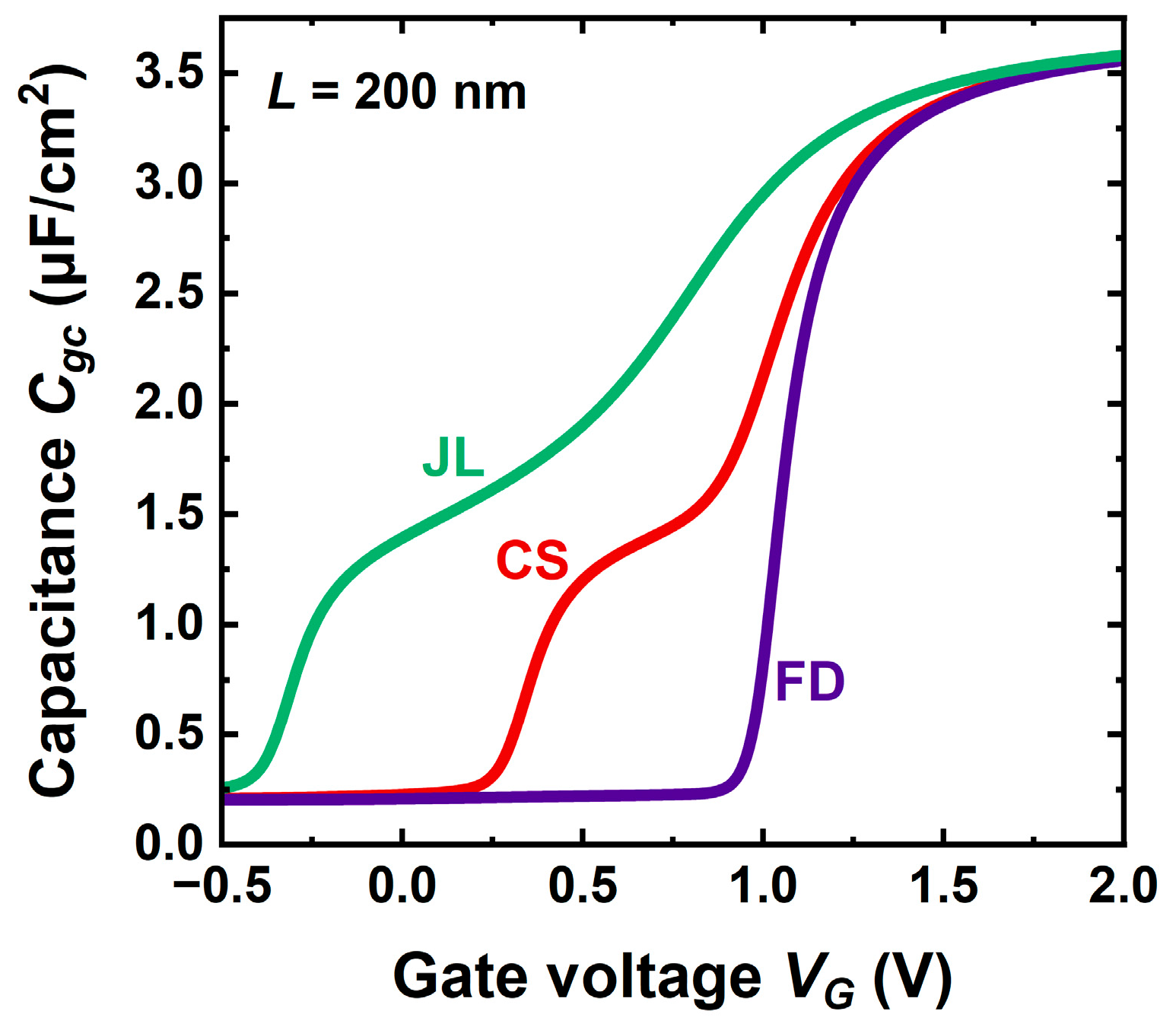

4. Capacitance Characteristics

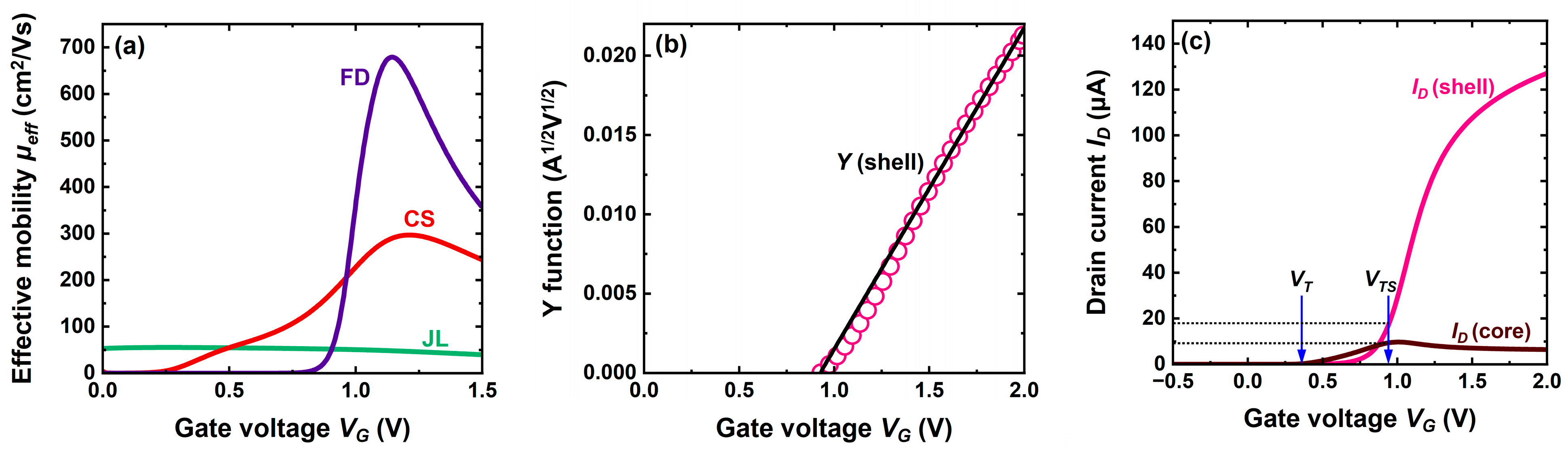

5. Drain Current, Transconductance, and Mobility

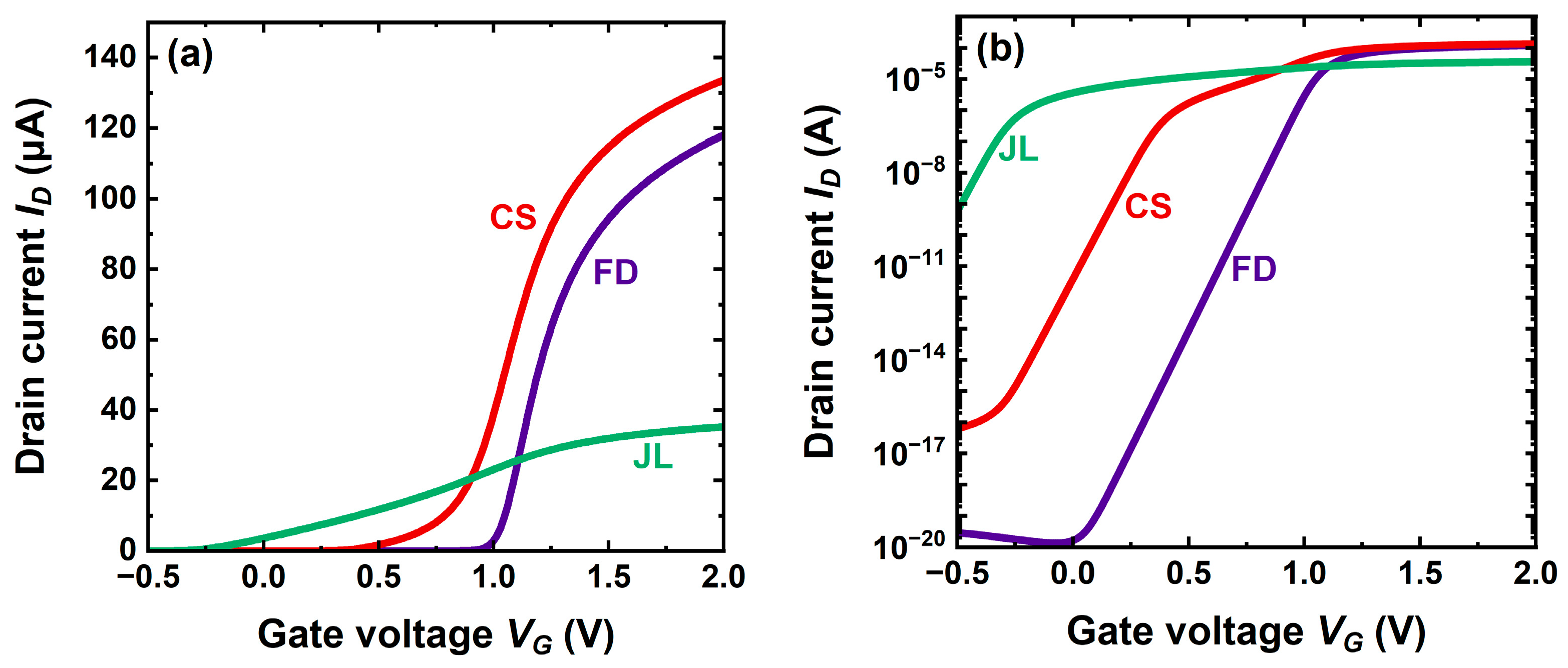

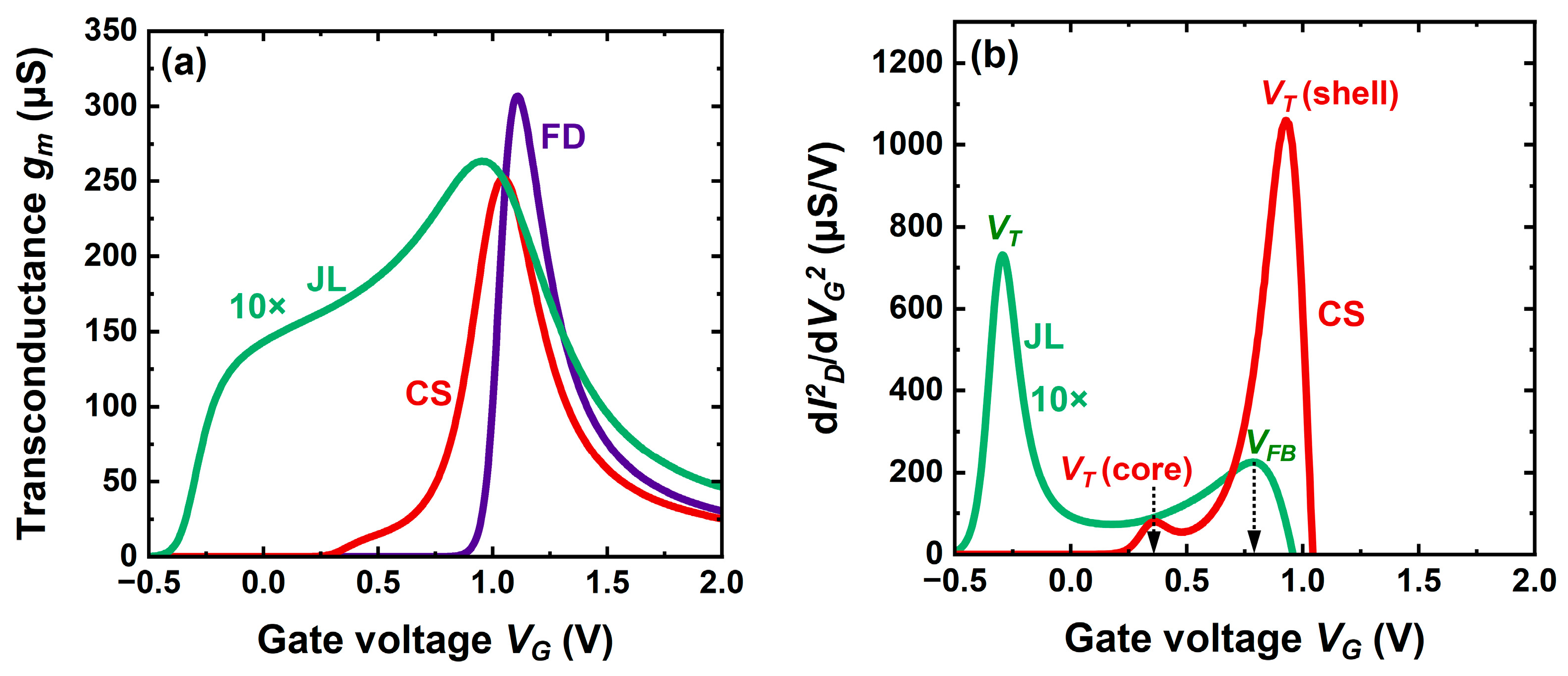

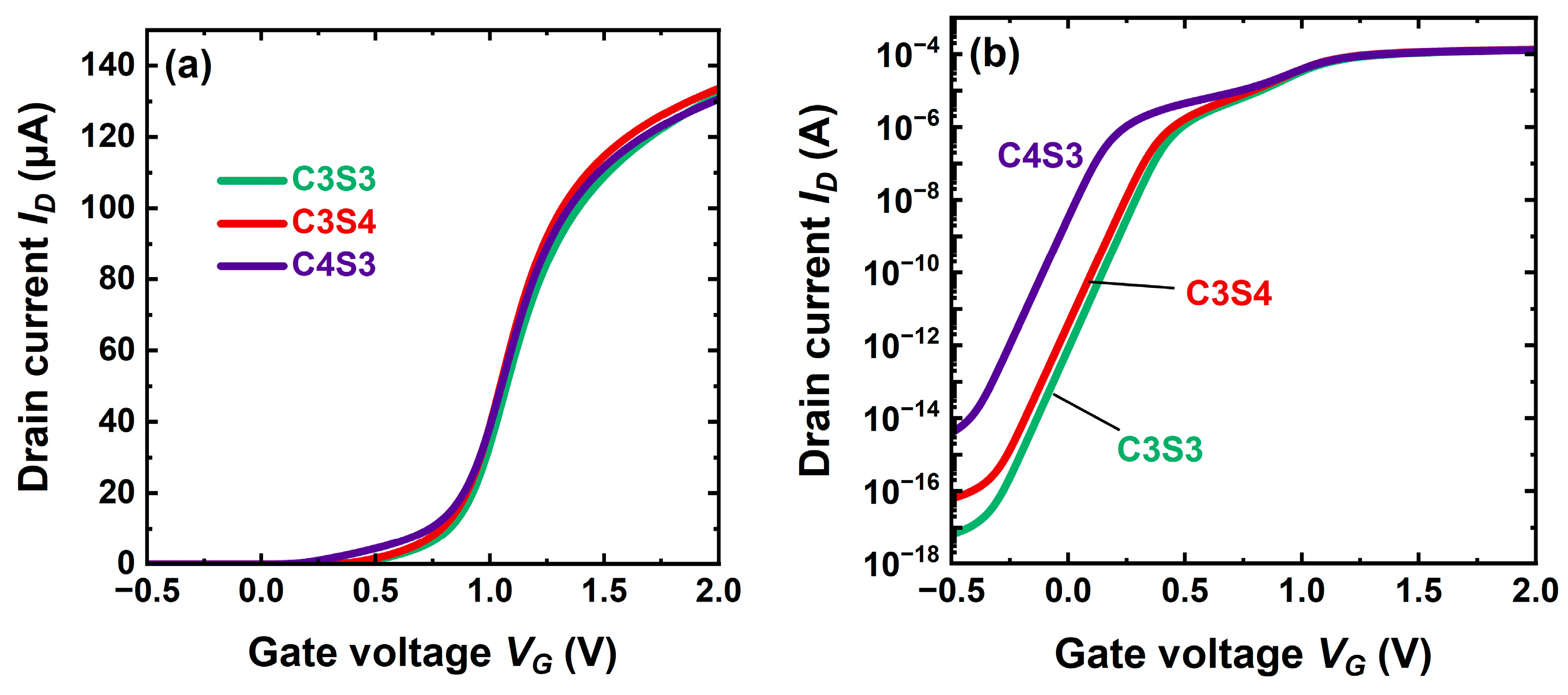

5.1. Transfer Characteristics

- (i)

- In conventional JL, the threshold voltage is definitely negative. CS-JL architecture succeeds in shifting VT from the unsuitable negative value (normally-on) to a positive value (normally-off).

- (ii)

- The drive current is significantly improved (Figure 6a).

5.2. Carrier Mobility

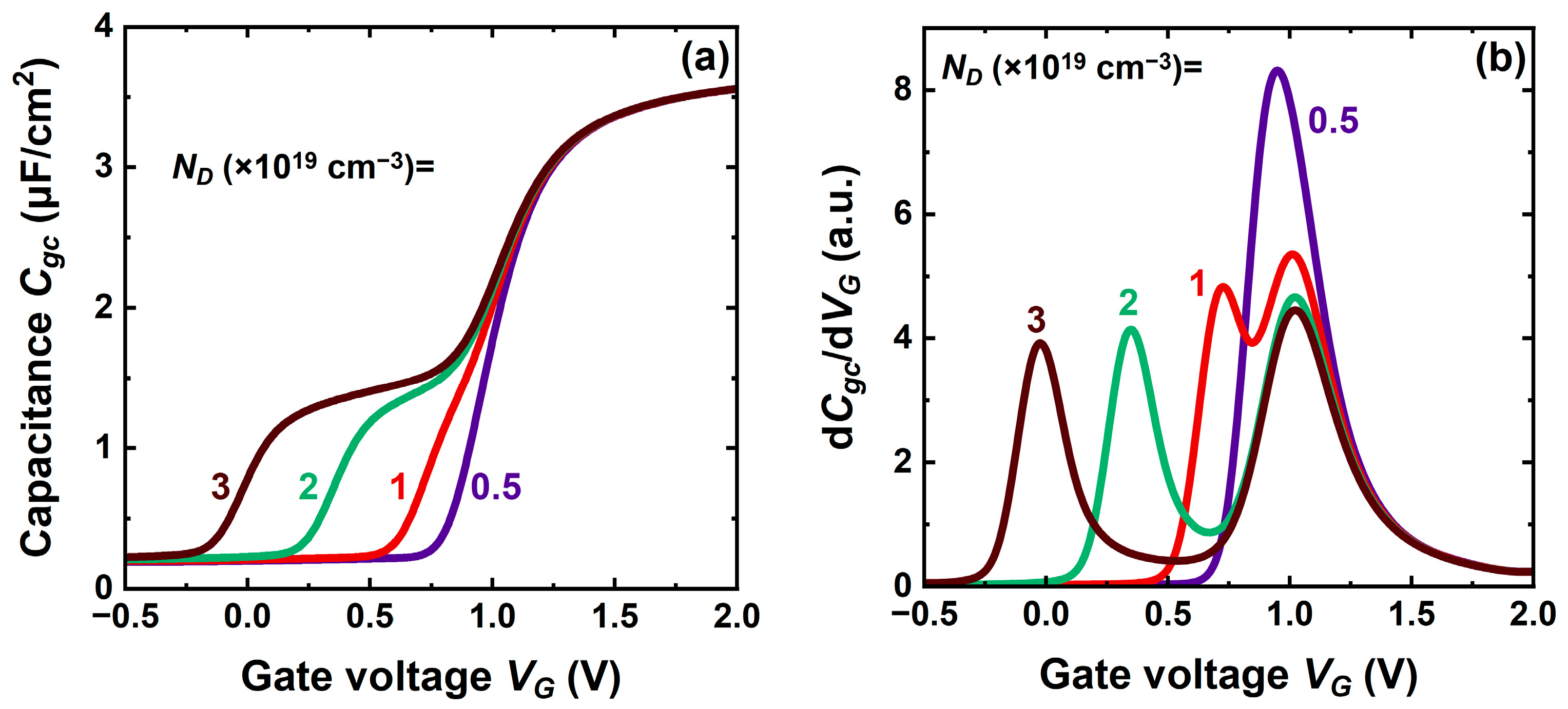

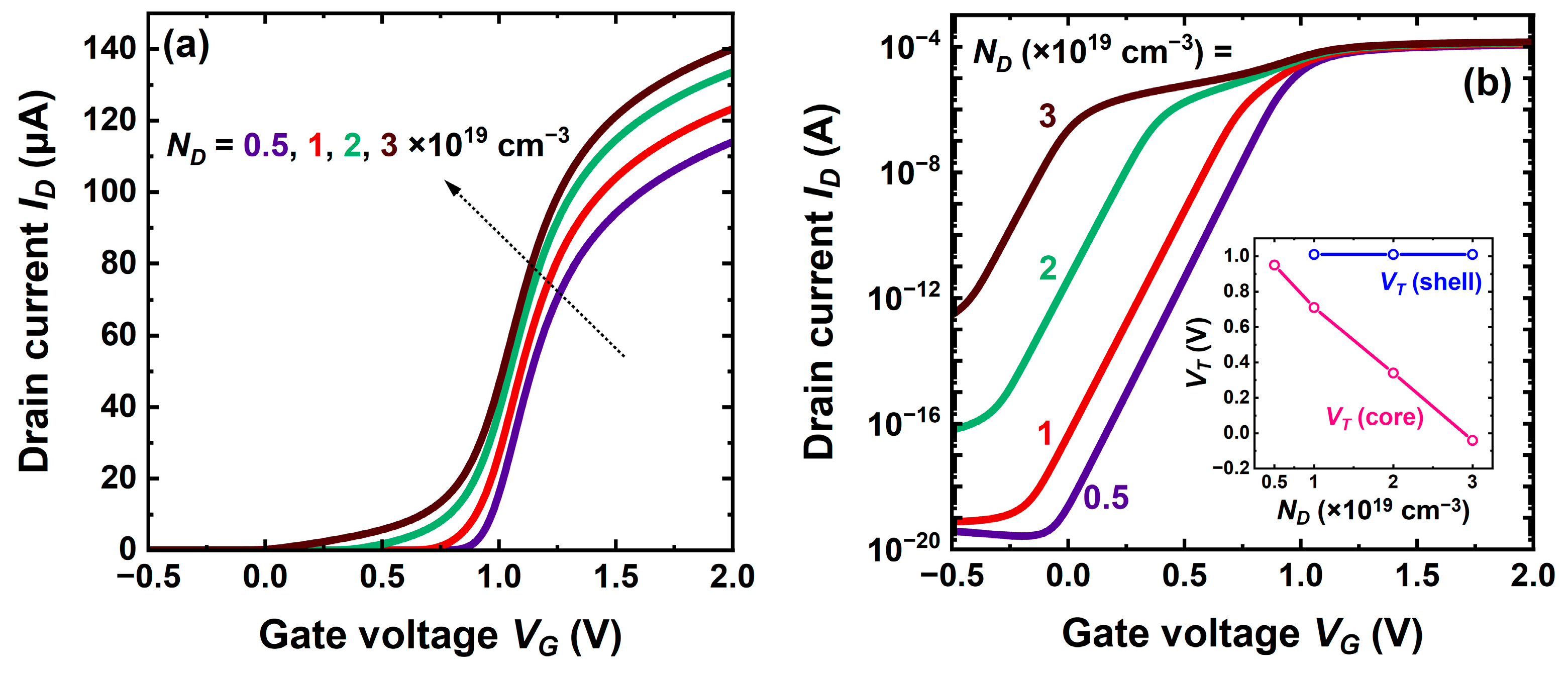

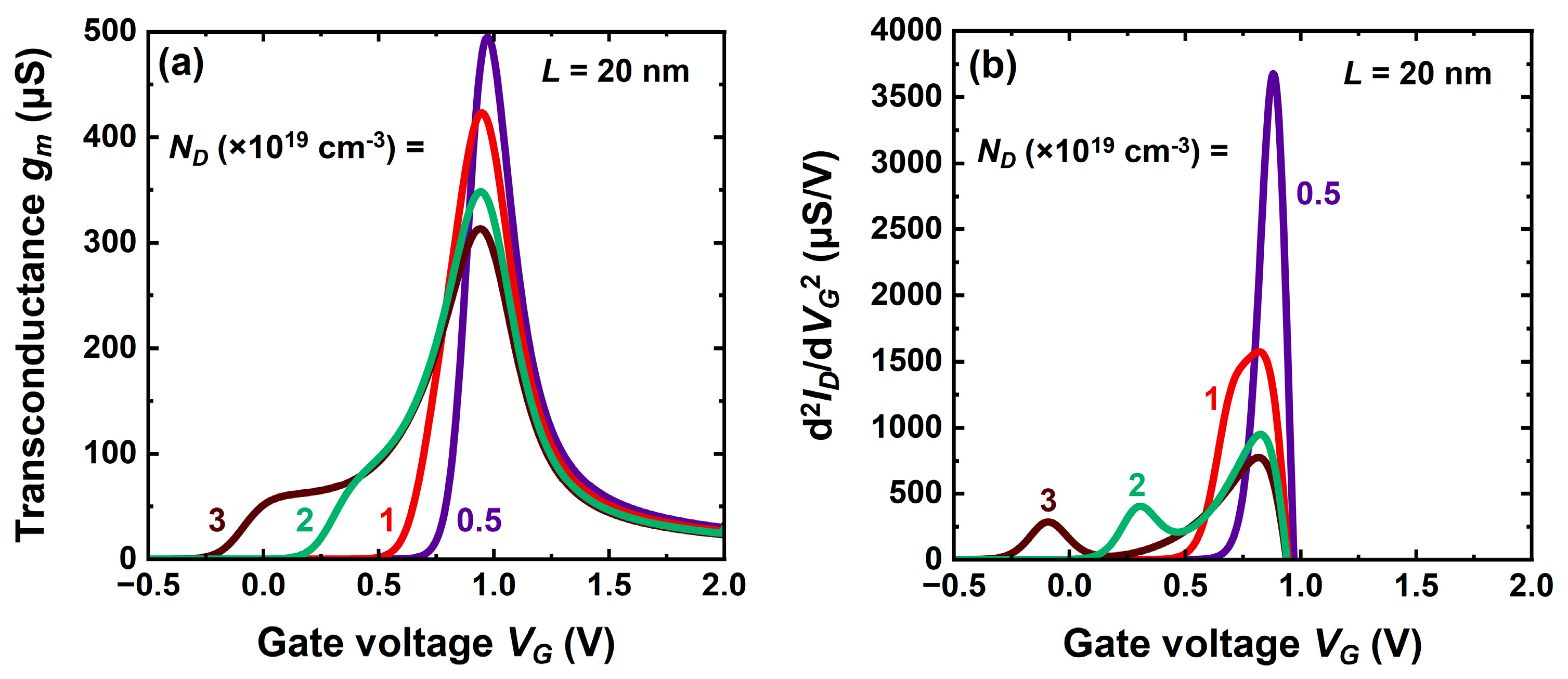

5.3. Impact of Core Doping

5.4. Impact of Thickness

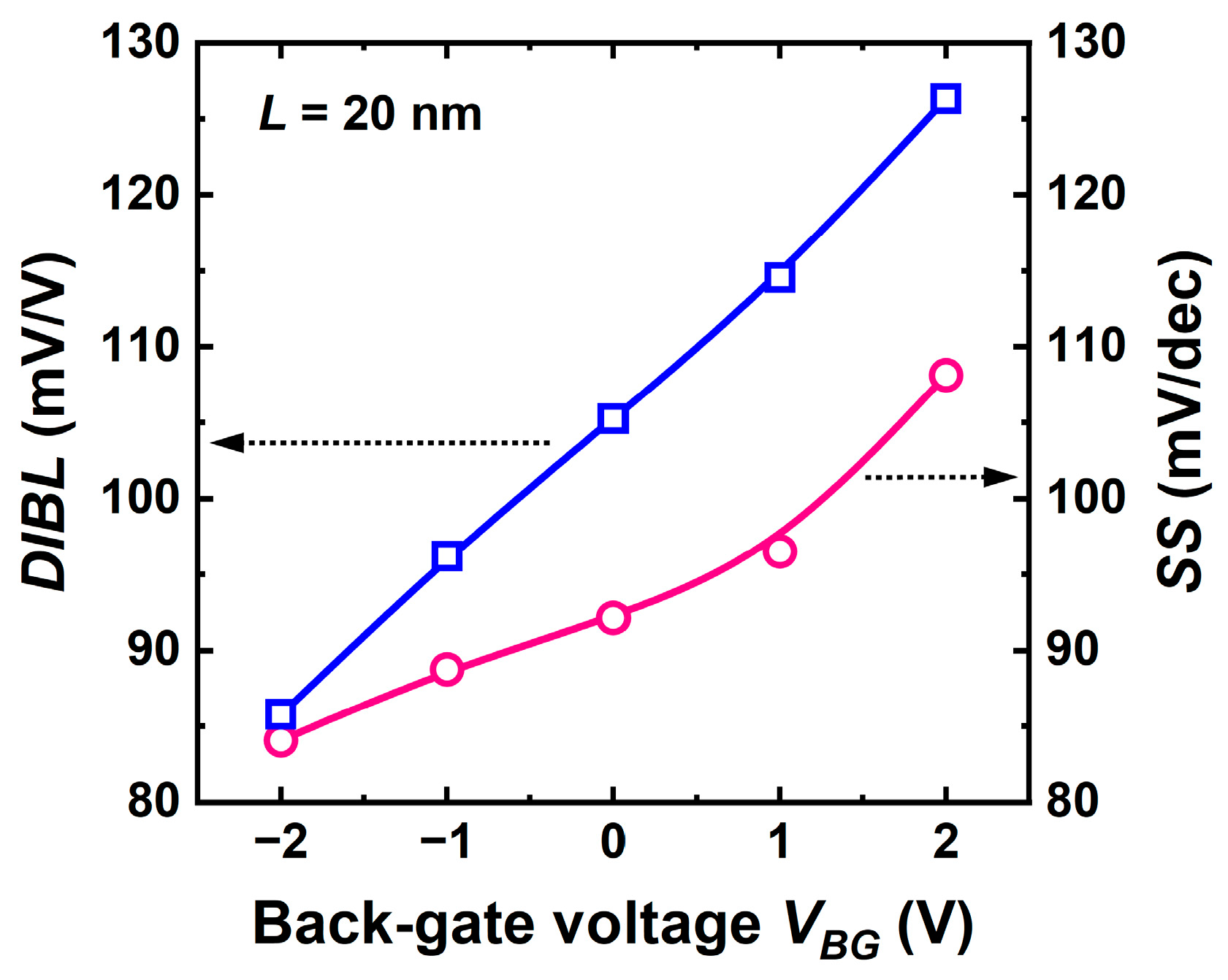

6. Short-Channel Effects

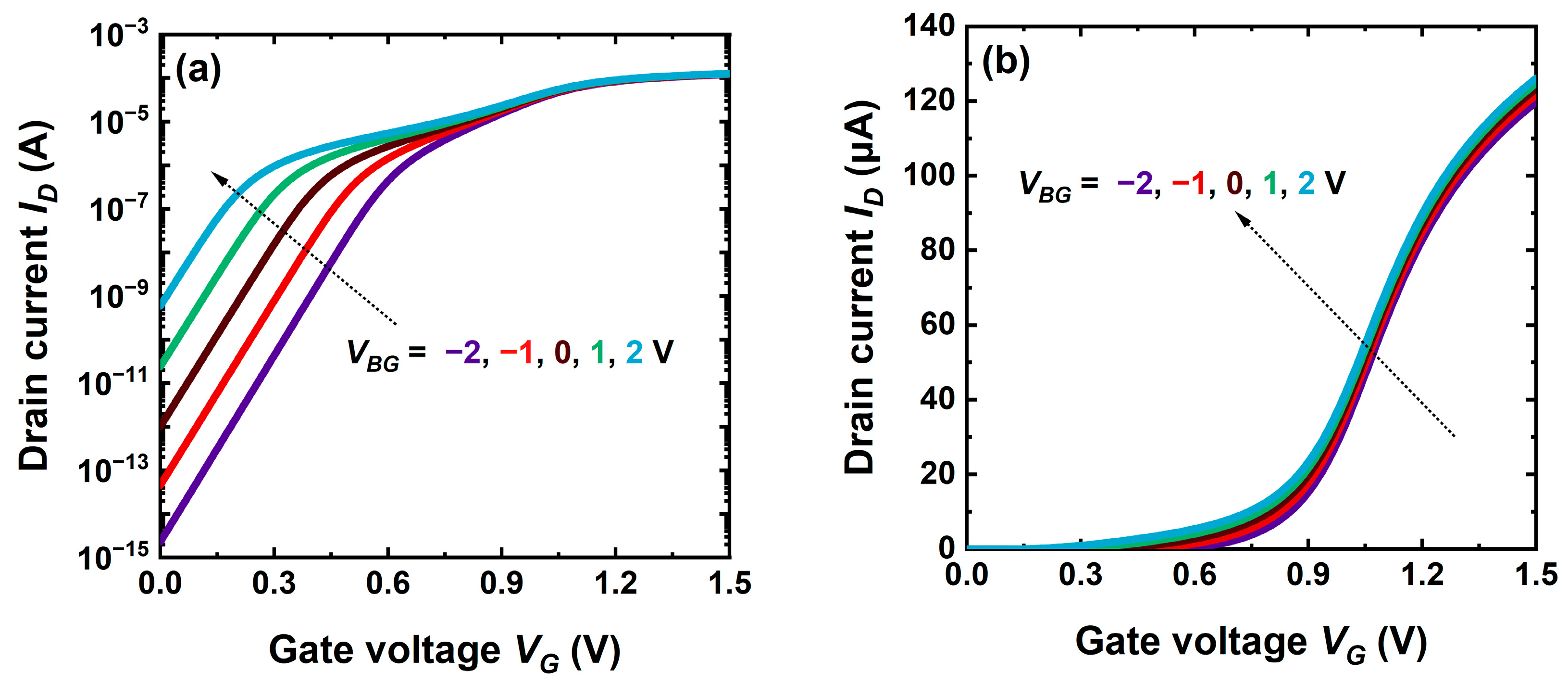

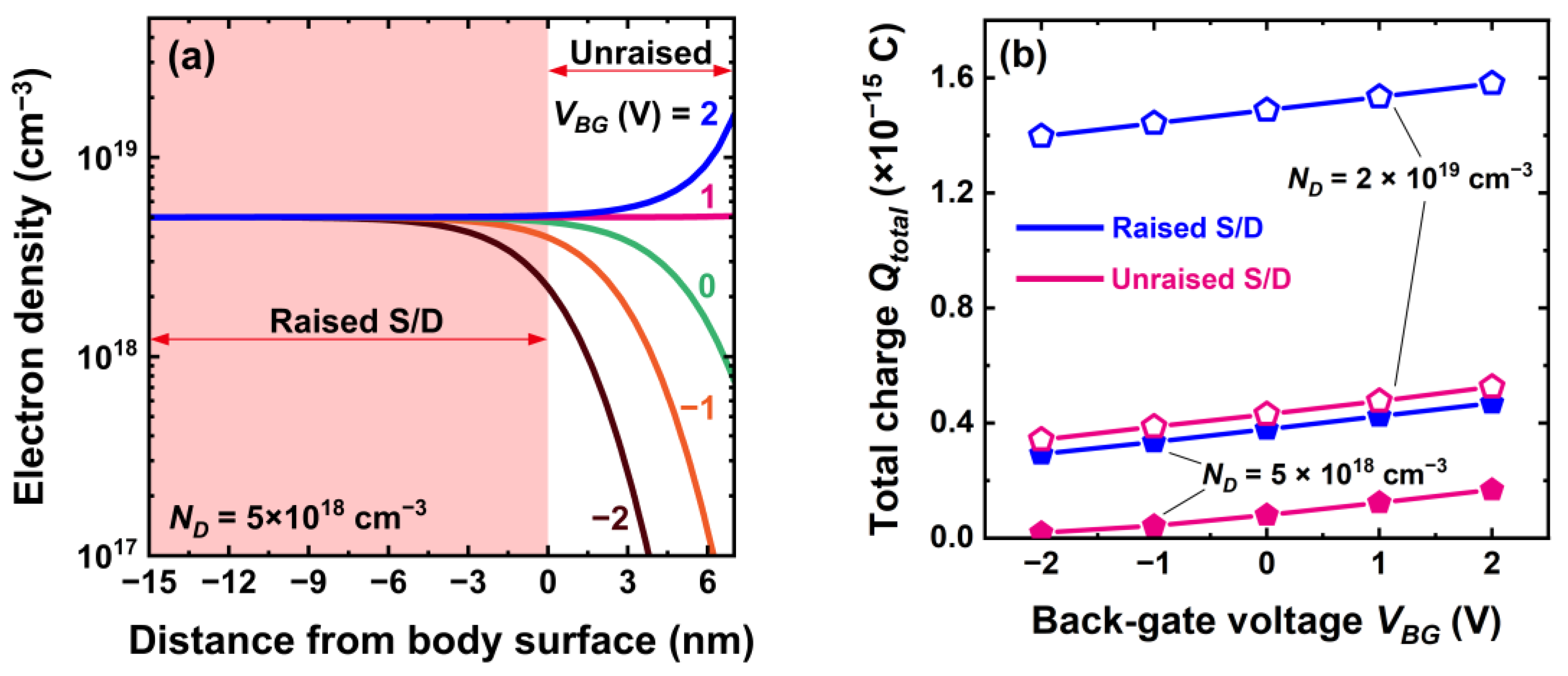

7. Back-Biasing

8. Conclusions

- (i)

- Keep ultrathin body (6−10 nm) as a safe protection against short-channel effects; this implies that both the core and the shell are 3−5 nm thick.

- (ii)

- Use as much core doping as possible to sustain low series resistance.

- (iii)

- Adjust core thickness to match the target threshold voltage.

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Taur, Y.; Ning, T.H. Fundamentals of Modern VLSI Devices, 3rd ed.; Cambridge University Press: New York, NY, USA, 2021. [Google Scholar] [CrossRef]

- Fossum, J.G.; Trivedi, V.P. Fundamentals of Ultra-Thin-Body MOSFETs and FinFETs; Cambridge University Press: New York, NY, USA, 2013. [Google Scholar]

- Cristoloveanu, S. Fully Depleted Silicon–On–Insulator; Elsevier: Amsterdam, The Netherlands, 2021; ISBN 978-0-12-819643-4. [Google Scholar] [CrossRef]

- Batude, P.; Ernst, T.; Arcamone, J.; Arndt, G.; Coudrain, P.; Gaillardon, P.-E. 3-D sequential integration: A key enabling technology for heterogeneous Co-integration of new function with CMOS. IEEE J. Emerg. Sel. Top. Circuits Syst. 2012, 2, 714–722. [Google Scholar] [CrossRef]

- Colinge, J.-P.; Lee, C.-W.; Afzalian, A.; Akhavan, N.D.; Yan, R.; Ferain, I.; Razavi, P.; O’Neill, B.; Blake, A.; White, M.; et al. Nanowire transistors without junctions. Nat. Nanotechnol. 2010, 5, 225–229. [Google Scholar] [CrossRef] [PubMed]

- Colinge, J.-P. Silicon-on-insulator (SOI) junctionless transistors. In Silicon-On-Insulator (SOI) Technology: Manufacture and Applications; Woodhead Publishing: Sawston, UK, 2014; pp. 167–194. [Google Scholar] [CrossRef]

- Colinge, J.-P. The junctionless transistor. In Emerging Devices for Low-Power and High-Performance Nanosystems: Physics, Novel Functions, and Data Processing; Deleonibus, S., Ed.; Pan Stanford Publishing: Singapore, 2018. [Google Scholar] [CrossRef]

- Cristoloveanu, S.; Ghibaudo, G. Superiority of Core-Shell Junctionless FETs. Solid-State Electron. 2022, 194, 108313. [Google Scholar] [CrossRef]

- Cristoloveanu, S.; Ghibaudo, G. The core-shell junctionless MOSFET. Solid-State Electron. 2023, 200, 108567. [Google Scholar] [CrossRef]

- Rodriguez, N.; Cristoloveanu, S.; Gamiz, F. Novel capacitorless 1T-DRAM cell for 22-nm node compatible with bulk and SOI substrates. IEEE Trans. Electron. Devices 2011, 58, 2371–2377. [Google Scholar] [CrossRef]

- Gamiz, F.; Rodriguez, N.; Cristoloveanu, S. Advanced concepts for floating-body memories. Int. J. High Speed Electron. Syst. 2012, 21, 1250002. [Google Scholar] [CrossRef]

- Bawedin, M.; Cristoloveanu, S.; Hubert, A.; Park, K.-H.; Martinez, F. Floating body SOI memory: The scaling tournament. In Semiconductor-On-Insulator Materials for Nanoelectronics Applications; Nazarov, A., Colinge, J.-P., Balestra, F., Raskin, J.-P., Gamiz, F., Lysenko, V., Eds.; Springer: Berlink/Herdelberg, Germany, 2011; pp. 393–421. ISBN 978-3-642-15868-1. [Google Scholar]

- Gamiz, F.; Rodriguez, N.; Cristoloveanu, S. A-RAM family: Novel capacitorless 1T-DRAM cells for 22 nm nodes and beyond. In Nanoscale Semiconductor Memories: Technology and Applications; Kurinek, S.K., Iniewski, K., Eds.; CRC Press: New York, NY, USA, 2013; pp. 157–179. ISBN 9781466560604. [Google Scholar]

- Gamiz, F.; Rodriguez, N.; Navarro, C.; Marquez, C.; Cristoloveanu, S. Tri-Dimensional A2-RAM Cell: Entering the Third Di-mension. In Engineering Materials; Springer: Cham, Switzerland, 2014; pp. 105–124. [Google Scholar] [CrossRef]

- Rodríguez, N.; Navarro, C.; Gamiz, F.; Andrieu, F.; Faynot, O.; Cristoloveanu, S. Experimental Demonstration of Capacitorless A2RAM Cells on Silicon-on-Insulator. Electron. Device Lett. 2012, 33, 1717–1719. [Google Scholar] [CrossRef]

- Rodriguez, N.; Gamiz, F.; Navarro, C.; Marquez, C.; Andrieu, F.; Faynot, O.; Cristoloveanu, S. Experimental developments of A2RAM memory cells on SOI and bulk substrates. Solid-State Electron. 2015, 103, 7–14. [Google Scholar] [CrossRef]

- Lacord, J.; Wakam, F.T.; Chalupa, Z.; Hartmann, J.-M.; Besson, P.; Loup, V.; Vizioz, C.; Brevard, L.; Aussenac, F.; Mescot, X.; et al. Si/Si0.7Ge0.3 A2RAM nanowires fabrication and characterization for 1T-DRAM applications. Solid-State Electron. 2022, 193, 108294. [Google Scholar] [CrossRef]

- Wakam, F.T.; Lacord, J.; Bawedin, M.; Martinie, S.; Cristoloveanu, S.; Barbe, J.-C. Optimization guidelines of A2RAM cell performance through TCAD simulations. In Proceedings of the 2017 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Kamakura, Japan, 7–9 September 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 329–332. [Google Scholar] [CrossRef]

- Wakam, F.T.; Lacord, J.; Bawedin, M.; Martinie, S.; Cristoloveanu, S.; Poiroux, T. Pure boron monolayer to boost A2RAM performance. In Proceedings of the 2019 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), Grenoble, France, 1–3 April 2019; IEEE: Piscataway, NJ, USA, 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Wakam, F.T.; Lacord, J.; Bawedin, M.; Martinie, S.; Cristoloveanu, S.; Ghibaudo, G.; Barbe, J.-C. Doping profile extraction in thin SOI films: Application to A2RAM. Solid-State Electron. 2019, 159, 3–11. [Google Scholar] [CrossRef]

- Wakam, F.T.; Lacord, J.; Bawedin, M.; Martinie, S.; Cristoloveanu, S.; Ghibaudo, G.; Barbe, J.-C. A2RAM compact modeling: From DC to 1T-DRAM memory operation. Solid-State Electron. 2020, 168, 107731. [Google Scholar] [CrossRef]

- Yan, Y.; Song, W.; Dou, C.; Zhao, X.; Li, B.; Xu, Y.; Cristoloveanu, S. A Planar Core-Shell Junctionless Transistor Compatible with FD-SOI Technology. Solid-State Electron. 2025, 225, 109079. [Google Scholar] [CrossRef]

- Gamiz, F.; Lopez-Villanueva, J.-A.; Jimenez-Tejada, J.-A.; Melchor, I.; Palma, A.-A. A comprehensive model for Coulomb scattering in inversion layers. J. Appl. Phys. 1994, 75, 924–934. [Google Scholar] [CrossRef]

- Esseni, D.; Abramo, A.; Selmi, L.; Sangiorgi, E. Physically-based modeling of low field electron mobility in ultrathin single- and double-gate SOI nMOSFETs. IEEE Trans. Electron. Devices 2003, 50, 2445–2455. [Google Scholar] [CrossRef]

- Pananakakis, G.; Ghibaudo, G.; Cristoloveanu, S. Detailed comparison of threshold voltage extraction methods in FD-SOI MOSFETs. Solid-State Electron. 2023, 209, 108764. [Google Scholar] [CrossRef]

- Ghibaudo, G. New method for the extraction of MOSFET parameters. Electron. Lett. 1988, 24, 543–545. [Google Scholar] [CrossRef]

- Cristoloveanu, S.; Ghibaudo, G. Intrinsic mechanism of mobility collapse in short MOSFETs. IEEE Trans. Electron. Devices 2021, 68, 5090–5094. [Google Scholar] [CrossRef]

- Ernst, T.; Tinella, C.; Raynaud, C.; Cristoloveanu, S. Fringing fields in sub-0.1 μm fully depleted SOI MOSFETs: Optimization of the device architecture. Solid-State Electron. 2002, 46, 373–378. [Google Scholar] [CrossRef]

- Lim, H.-K.; Fossum, J.G. Threshold voltage of thin-film silicon-on-insulator (SOI) MOSFETs. IEEE Trans. Electron. Devices 1983, ED–30, 1244. [Google Scholar]

- Han, H.-C.; Jazaeri, F.; Zhao, Z.; Lehmann, S.; Enz, C. An improved subthreshold swing expression accounting for back-gate bias in FDSOI FETs. Solid-State Electron. 2023, 202, 108608. [Google Scholar] [CrossRef]

- Schroder, D.K. Semiconductor Material and Device Characterization, 3rd ed.; John Wiley & Sons: Hoboken, NJ, USA, 2006. [Google Scholar]

| CS-JL | JL | FDSOI | |

|---|---|---|---|

| Peak mobility (cm2/Vs) | 640 | 50 | 700 |

| Transconductance | high | poor | high |

| Drive current | high | poor | high |

| Threshold voltage | positive | negative | positive |

| S/D engineering | none | none | complex |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Dou, C.; Song, W.; Yan, Y.; Zhang, X.; Tang, Z.; Zhao, X.; Liu, F.; Xue, S.; Sun, H.; Wan, J.; et al. The Planar Core–Shell Junctionless MOSFET. Micromachines 2025, 16, 418. https://doi.org/10.3390/mi16040418

Dou C, Song W, Yan Y, Zhang X, Tang Z, Zhao X, Liu F, Xue S, Sun H, Wan J, et al. The Planar Core–Shell Junctionless MOSFET. Micromachines. 2025; 16(4):418. https://doi.org/10.3390/mi16040418

Chicago/Turabian StyleDou, Cunhua, Weijia Song, Yu Yan, Xuan Zhang, Zhiyu Tang, Xing Zhao, Fanyu Liu, Shujian Xue, Huabin Sun, Jing Wan, and et al. 2025. "The Planar Core–Shell Junctionless MOSFET" Micromachines 16, no. 4: 418. https://doi.org/10.3390/mi16040418

APA StyleDou, C., Song, W., Yan, Y., Zhang, X., Tang, Z., Zhao, X., Liu, F., Xue, S., Sun, H., Wan, J., Li, B., Wang, Y., Ye, T., Xu, Y., & Cristoloveanu, S. (2025). The Planar Core–Shell Junctionless MOSFET. Micromachines, 16(4), 418. https://doi.org/10.3390/mi16040418