Abstract

The body diode degradation in SiC power MOSFETs has been demonstrated to be caused by basal plane dislocation (BPD)-induced stacking faults (SFs) in the drift region. To enhance the reliability of the body diode, many process and structural improvements have been proposed to eliminate BPDs in the drift region, ensuring that commercial SiC wafers for 1.2 kV devices are of high quality. Thus, investigating the body diode reliability in commercial planar and trench SiC power MOSFETs made from SiC wafers with similar quality has attracted attention in the industry. In this work, current stress is applied on the body diodes of 1.2 kV commercial planar and trench SiC power MOSFETs under the off-state. The results show that the body diodes of planar and trench devices with a shallow P+ depth are highly reliable, while those of the trench devices with the deep P+ implantation exhibit significant degradation. In conclusion, the body diode degradation in trench devices is mainly influenced by P+ implantation-induced BPDs. Therefore, a trade-off design by controlling the implantation depth/dose and maximizing the device performance is crucial. Moreover, the deep JFET design is confirmed to further improve the body diode reliability in planar devices.

Keywords:

SiC; MOSFET; body diode; reliability; basal plane dislocation; planar; trench; P+ implantation; deep JFET 1. Introduction

Compared to silicon, silicon carbide (SiC) power MOSFETs are favored in the power electronics market, especially in electric vehicles (EVs), due to their lower switching loss, higher temperature capability, and higher switching frequency [1]. The initial and still most widely used commercial SiC power MOSFETs are conventional planar MOSFETs [2]. However, the SiC/SiO2 interface is more complex than the Si/SiO2 interface, causing the gate oxide to have a higher density of interface states and near-interface traps during thermal growth [3,4]. Additionally, a high density of crystallographic and surface defects in the SiC substrate and the epitaxial layer during high-temperature growth negatively affects the reliability of SiC power MOSFETs [5,6]. Thus, the commercialization of SiC power MOSFETs presents significant challenges. As the thermal growth technology of the gate oxide layer and the epitaxial layer has gradually matured, the reliability of planar SiC power MOSFETs has significantly improved [7,8,9,10,11,12]. The degradation of the body diode has become negligible for voltage ratings below 1.2 kV, and some vendors have even eliminated the impact of body diode degradation at the voltage rating of 3.3 kV [13,14]. This allows the parasitic body diode to be directly used as a free-wheeling diode, replacing the external Schottky diode and thus significantly reducing the production cost [15]. With the relative simplicity and maturity of the manufacturing process for planar SiC power MOSFETs, more electric vehicle OEMs and tier-one suppliers are adopting them in their onboard chargers and drivetrain inverters [16].

Currently, in the electric vehicle market, battery voltages are mainly around 400 V, causing 650 V SiC power MOSFETs to occupy a large market share [17,18]. However, for a higher driving range, faster charging efficiency, and better performance, more and more electric vehicle OEMs are considering upgrading from 400 V systems to 800–900 V systems, shifting the market’s focus to 1.2 kV products [19,20,21]. Due to reliability and cost, design trends for power modules favor reducing the number of discrete devices while maintaining or even increasing the current rating [22]. This sets higher demands on the on-resistance () of SiC power MOSFETs. Furthermore, with the rapid expansion of electric vehicles in the automotive market, the demand for SiC power MOSFETs production capacity is increasing; meanwhile, the performance and structural limitations of planar SiC power MOSFETs are becoming apparent [23]. Therefore, trench SiC power MOSFETs, with their higher channel electron mobility, elimination of the JFET resistance, and smaller cell pitch, are gaining attention in the market [24,25,26]. These features make achieving higher current ratings and production capacity for trench SiC power MOSFETs possible.

However, unlike conventional planar SiC power MOSFETs, under the blocking state, trench SiC power MOSFETs experience a high electric-field crowding at the bottom corners of the trench gate oxide, subjecting the gate oxide to higher stress [26,27]. This may require the derating of the drift region, which offsets the gains of the trench structure, and even lead to premature breakdown, affecting the reliability of trench SiC power MOSFETs [25,28,29]. To protect the trench gate oxide, P-type implants for shielding the gate trench corners have become a consensus in the design of trench SiC power MOSFETs [30]. However, for adequate protection, P-type implants in trench SiC power MOSFETs usually require deeper implantation and higher doses than the P-body in planar SiC power MOSFETs [28]. This may sacrifice the reliability of the parasitic body diode, necessitating a reassessment of whether to use an external Schottky diode as a free-wheeling diode. Trench SiC power MOSFETs, due to their relatively complex process, may not have the cost advantage of planar SiC power MOSFETs [31]. Integrating an external Schottky diode may exacerbate this cost disadvantage, eroding the benefits provided by the smaller cell pitch of trench SiC power MOSFETs [32]. Furthermore, there are variations in the characteristics of P-type implants among different vendors and even different generations of trench SiC power MOSFETs from the same vendor, making the research on the reliability of the body diode in SiC power MOSFETs essential. This work investigates and compares the body diode reliability of 1.2 kV commercial products from the mainstream vendors of SiC power MOSFETs with both planar and trench structures and proposes methods to enhance the reliability of the parasitic body diode.

2. Materials and Methods

2.1. Devices under Test (DUTs)

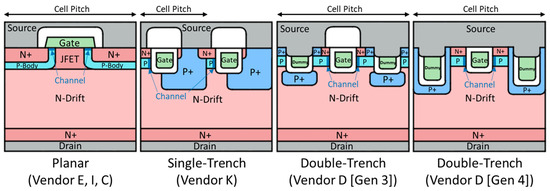

The devices under test (DUTs) used in this work are all 3-pin TO-247 packaged commercial 1.2 kV SiC power MOSFETs, without integrated Schottky diodes, as shown in Table 1. Among them, devices from Vendors E, I, and C are all planar SiC power MOSFETs, while those from Vendors K and D are trench SiC power MOSFETs. The planar structures of the devices from Vendors E, I, and C show the same structure. However, the trench structures of the devices from Vendors K and D differ, reflected in the number and depth of trenches within the cell pitch. Vendor K uses a single-trench structure (gate trench only), whereas Vendor D utilizes a double-trench structure (gate trench and source dummy trench), with slight differences between the third and fourth generations.

Table 1.

General information on the commercial DUTs in this work.

Figure 1 depicts the conventional planar structure of the devices from Vendors E, I, and C, and the trench structures of the devices from Vendors K, D (Gen 3), and D (Gen 4). It can be observed that the single-trench structure of Vendor K’s devices boasts a significant advantage in the cell pitch. However, each single gate trench has a channel on only one side, with the other side covered by a deep P+ implant to protect the trench corners. This means that every channel in devices from Vendor K has to work harder. For devices from Vendor D (Gen 3) with their gate trench plus source trench to form the double-trench configuration, as shown in the cross-sectional SEM images of their bare dies, their structure may have no obvious advantages of the cell pitch over the planar structure, because each cell has its own source trenches which are not shared with adjacent cells [28]. Differing from Vendor K’s deep P+ implants, the P+ implantation in devices from Vendor D (Gen 3) is carried out within the trenches after their formation. This suggests a shallower P+ depth in devices from Vendor D (Gen 3) compared to those from Vendor K, possibly sacrificing some gate oxide protection. However, having source trenches and corresponding P+ implants on both sides of each gate trench ensures channels on both sides, alleviating the channel stress. Therefore, in the structure of the devices from Vendor D (Gen 4), the double trench is retained. Also, the cross-sectional SEM images of their bare dies indicate that adjacent cells begin to share a source trench, improving the cell pitch [28]. Simultaneously, the P+ implants are modified to match Vendor K’s deep P+ implants, and the sequence of source trench etching and P+ implantation is swapped. The etching depth of the source trench wrapped in deep P+ in Gen 4 devices is doubled, offering better protection to the gate oxide than Gen 3 devices.

Figure 1.

The cross-sectional schematics of the planar structure, single-trench structure, and double-trench structure of two generations from left to right.

2.2. Experimental Methods

In this work, the reliability of the body diodes of DUTs was evaluated through the long-term constant current stress test. The sample size for each vendor’s devices was ten. These ten DUTs were connected in series and subjected to a constant current stress that matched their current rating. Meanwhile, a −5 V bias was uniformly applied to the gate of all the DUTs, as this is the recommended operational voltage for the body diode on device datasheets. To determine whether the body diode had a degradation trend that exceeded the industrial degradation criterion (to be introduced in Section 3) and determine the test efficiency, the body diode stress time for all the DUTs was set to 100 h. Electrical measurements were conducted before the stress, 20 h after, 50 h after, and 100 h after, respectively, to observe the changes in body diode characteristics and their impact on device performance. The electrical measurements included the third-quadrant body diode characteristics (with a gate bias of −5 V) to extract the body diode’s forward voltage drop () @ = −20 A; the first-quadrant output characteristics (with a gate bias of 20 V) to determine at = 0.5 V; and the first-quadrant forward blocking characteristics (with a gate bias of 0 V) to observe the forward leakage current and drain-to-source breakdown voltage. The degradation of the body diode manifested in the change rate of (, the percentage change in compared to its pre-stress value), the change rate of (, the percentage change in compared to its pre-stress value), and changes in the blocking characteristic curves. Throughout the constant current stress process, the ten DUTs connected in series were mounted on a cold plate. An electrically insulating thermal pad separated the metal plate in the TO-247 package (connected to the drain) of all the DUTs from the metal cold plate. The cold plate was then connected to an industrial-grade water chiller to effectively dissipate the heat generated inside the device package during the stress, thereby stabilizing the junction temperature.

3. Results

In this section, the results of the 100 h body diode stress tests conducted on the selected commercial SiC MOSFETs are presented. Ideally, SiC power MOSFETs would exhibit no rate of change (ROC) in their body diode characteristics after undergoing stress. However, in reality, devices display varying degrees of ROCs after the same stress. To differentiate between devices whose ROCs remain within and outside the acceptable limits for their application scenarios after stress, a widely used industrial degradation criterion is necessary. Currently, there is no official criterion, but a commonly used one that involves changes in or exceeding about +5% from their initial values has been extensively employed in previous research on body diode degradation [33,34,35]. In this work, we continued to use this industrial degradation criterion for analysis. All ROCs over different time points were based on the average levels of ROCs of all the surviving devices at these time points. Due to the randomness of measurement errors, some ROCs appeared as negative values but were within acceptable limits. For easy observation, changes in the blocking characteristic curves were compared only between the start of the stress and the end of the 100 h stress, based on the most representative device among those that survived until the end. The dotted lines represent the blocking characteristic curves before the stress, and the solid lines represent them after 100 h of stress.

3.1. Body Diode Stress Test Results of Commercial Planar SiC Power MOSFETs

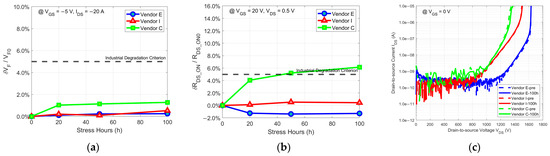

Figure 2 displays the 100 h body diode stress test results for commercial planar SiC power MOSFETs from the three selected vendors. Compared to the industrial criterion for body diode degradation, it can be observed that, regardless of the ROC in or ROC in of the body diode, the DUTs from two of the three vendors remain far away from the industrial degradation criterion and very close to the ideal conditions throughout the stress. Only the DUTs from Vendor C slightly exceed the industrial degradation criterion. Moreover, their blocking characteristic curves demonstrate high stability, with no significant changes in the forward leakage current or drain-to-source breakdown voltage before and after the stress. As a result, body diode degradation is no longer a significant issue for 1.2 kV planar SiC power MOSFETs, suggesting that the parasitic body diode of planar SiC power MOSFETs at this voltage rating can be considered for application as a free-wheeling diode, reducing the production cost and increasing the production capacity. Regarding the DUTs from Vendor C with body diode degradation slightly exceeding the industrial degradation criterion compared to the DUTs from the other two vendors, the possible reasons require further analysis of the stacking faults (SFs) that lead to degradation. By examining the location and propagation trends of SFs, it is possible to determine the initial positions of basal plane dislocations (BPDs) and thus analyze the sources of BPDs. The sources of BPDs will be introduced in Section 4. According to the sources of BPDs, the causes of degradation can be deduced in the corresponding manufacturing process. Thus, if Vendor C wants to further enhance the reliability of their body diodes to match the leading products on the market, they may need to make improvements in the device structure or process, which will be discussed in Section 4.3.1.

Figure 2.

The body diode stress test results of (a) , (b) , and (c) the changes in blocking characteristic curves for commercial planar SiC power MOSFETs from Vendors E, I, and C.

3.2. Body Diode Stress Test Results of Commercial Trench SiC Power MOSFETs

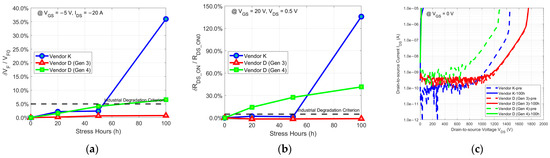

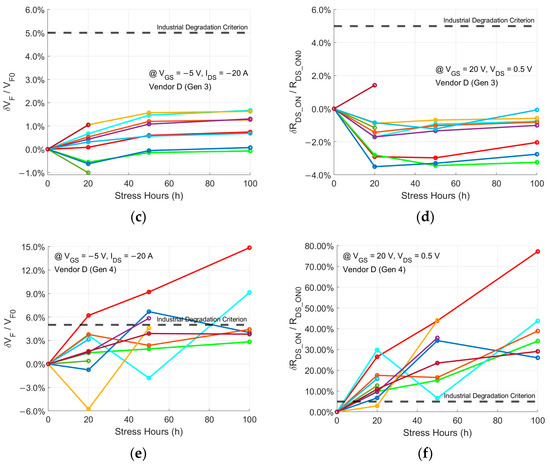

Figure 3 shows the 100 h body diode stress test results for three types of commercial trench SiC power MOSFETs from the two selected vendors. Unlike the commercial planar SiC power MOSFETs, when comparing their characteristics against the industrial criterion for body diode degradation, the devices from both Vendor K and Vendor D (Gen 4) exhibit ROCs in and of the body diode that exceed the industrial degradation criterion. The ROCs for devices from Vendor K exceed the industrial degradation criterion after 20 h of stress and exhibit more severe degradation after 50 h. Only the devices from Vendor D (Gen 3) maintain ROCs far below the industrial degradation criterion throughout the stress, demonstrating reliability similar to that of advanced commercial planar SiC power MOSFETs. Concurrently, changes in their blocking characteristic curves also mirror the level of their body diode degradation. The devices from Vendor K and Vendor D (Gen 4) exhibit very “leaky” characteristics in their blocking characteristic curves after 100 h of stress, with the forward leakage current reaching the device breakdown level at a very low drain-to-source voltage. Only the devices from Vendor D (Gen 3), due to the high reliability of their body diodes, display the same high stability in their blocking characteristics as the commercial planar SiC power MOSFETs. Therefore, body diode degradation remains a challenge for 1.2 kV trench SiC power MOSFETs. Although some trench structures, like those of the devices from Vendor D (Gen 3), offer relatively stable body diodes that could be directly used as free-wheeling diodes, this may be achieved at the expense of sacrificing the device performance to a certain extent. Hence, for most trench SiC power MOSFETs with high performance, integrating external Schottky diodes as free-wheeling diodes may still be needed, which negatively impacts the production cost and capacity.

Figure 3.

The body diode stress test results of (a) , (b) , and (c) the changes in blocking characteristic curves for three types of commercial trench SiC power MOSFETs from Vendors K and D.

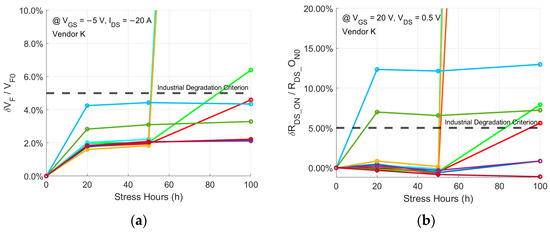

Figure 4 depicts the 100 h body diode stress test results for all the DUTs of the three types of commercial trench SiC power MOSFETs. As shown in Figure 4a,b, all ten DUTs from Vendor K survive the 100 h stress, with seven exceeding the industrial degradation criterion after the stress and three exhibiting very severe degradation. Figure 4c,d indicate that two out of the ten DUTs from Vendor D (Gen 3) fail during the 100 h stress, yet all the DUTs remain below the industrial degradation criterion throughout the stress. Figure 4e,f reveal that four out of the ten DUTs from Vendor D (Gen 4) fail during the stress, with all the DUTs exceeding the industrial degradation criterion after the stress. The yields of qualified body diodes after the stress for all the vendors of the aforementioned commercial trench SiC power MOSFETs are summarized in Table 2. The bad yields further prove that integrating external Schottky diodes as free-wheeling diodes is still necessary for most trench SiC power MOSFETs. For comparison, the body diodes of the devices from all the vendors of commercial planar SiC power MOSFETs survive the 100 h stress and remain below the industrial degradation criterion during the stress.

Figure 4.

The 100 h body diode stress test results of (a) and (b) for ten trench DUTs from Vendor K; (c) and (d) for ten trench DUTs from Vendor D (Gen 3); (e) and (f) for ten trench DUTs from Vendor D (Gen 4). Each color line represents one discrete DUT from ten.

Table 2.

The yields of qualified body diodes after the stress for all the vendors of commercial trench SiC power MOSFETs.

4. Discussion

This section involves the analysis of the body diode stress test results of commercial SiC power MOSFETs with different structures. The results confirm that the mechanism causing the body diode degradation in SiC MOSFETs is the expansion of BPD-induced SFs by absorbing the activation energy from the recombination of injected holes and electrons in the drift region [36]. Hence, the key to analyzing the body diode stress test results in this work lies in the source of the BPDs. The primary sources of BPDs include (1) BPDs originating from the substrate that propagate into the drift region; (2) BPDs formed in the epitaxial layer (i.e., the drift region) during epitaxial growth; (3) BPD clusters formed due to inclusions (SiC down-fall); (4) small and tight BPD clusters formed around micropipes; (5) BPDs formed near the implanted region after P-type implantation and activation annealing [34]. A series of process improvements have been made, such as introducing a recombination-enhanced buffer layer between the substrate and the drift region, a KOH etching process before the conventional epitaxial growth to create BPD etch pits for enhancing the conversion of BPDs to threading edge dislocations (TEDs), and using ultraviolet photoluminescence (UVPL) on wafers to screen out dies with BPDs [37,38,39,40]. Stahlbush et al. have demonstrated the high quality of commercial SiC wafers with an epi-layer thickness of 10 µm suitable for the 1.2 kV rating, and some vendors have achieved a near-equivalent quality of SiC wafers for the 3.3 kV rating with a 30 µm epi-layer thickness [34]. Thus, the body diode degradation phenomenon observed in this work is believed to be caused by the BPDs formed near the implanted region after P-type implantation and activation annealing [38].

4.1. Analysis of Body Diode Stress Test Results of Commercial Planar SiC Power MOSFETs

The devices from Vendors E, I, and C share the same planar structure, as shown in Figure 1. In this planar structure, P-type implantation is of low dose and energy, used to form the shallow P-body. Stahlbush et al. have shown that the low-dose P-type implantation in SiC, even after activation annealing, does not create significant BPDs near the implanted region [41]. Thus, the commercial 1.2 kV planar SiC power MOSFETs tested in this work, based on the inherently low BPD density in the SiC epi-layer, do not introduce new implantation-induced BPDs with the low-dose and low-energy P-type implantation. As a result, they exhibit high reliability and almost no degradation during the long-term constant current stress. Considering that devices from Vendor C exhibit more pronounced degradation, slightly exceeding the industrial degradation criterion compared to those from Vendors E and I, there is one possible reason that the P-type implantation for devices from Vendor C is conducted at room temperature. This could be a strategy to reduce the production cost, but as a trade-off, P-type implantation at room temperature may have a higher probability of introducing new BPDs post-activation annealing than heated implantation. Qian et al. have previously shown that SiC power MOSFETs with P-type implantation at 500 °C, compared to those with P-type implantation at room temperature, exhibit almost negligible body diode degradation [14]. The difference in body diode degradation at these two temperatures aligns with the observed difference in this work between devices from Vendor C and those from Vendors E and I, leading to the belief that this variation is possibly due to different implantation temperatures and/or different annealing conditions.

4.2. Analysis of Body Diode Stress Test Results for Commercial Trench SiC Power MOSFETs

Devices from Vendor K, Vendor D (Gen 3), and Vendor D (Gen 4) possess distinct trench structures, as depicted in Figure 1. Compared to devices from Vendor K and Vendor D (Gen 4), despite undergoing a high-dose P+ implantation process, the P+ implants in Vendor D (Gen 3) devices are shallower, thus requiring less implantation energy. This significantly reduces the likelihood of BPD formation after activation annealing. When controlling the implantation depth and performing high-temperature implantation, the reliability of the parasitic body diode can reach the levels observed in advanced commercial planar SiC power MOSFETs. However, the shielding function that the P+ implants provide to the gate trench corners also becomes diminished. This necessitates the derating of the drift region by increasing its thickness, resulting in an increase in . Figure 3c confirms this, as the drain-to-source breakdown voltage of the devices from Vendor D (Gen 3), nearing 1.8 kV, surpasses that of Vendor K and Vendor D (Gen 4). By contrast, devices from both Vendor K and Vendor D (Gen 4) may have introduced a large number of implantation-induced BPDs, due to the high-dose and high-energy deep P+ implantation for fully protecting the gate trench corners, thereby significantly sacrificing the reliability of the parasitic body diode. Stahbush et al. suggest that, although the formation of BPDs would be enhanced at the corners of the reactive ion etching (RIE) region, oxidation eliminates surface damage at the corners and suppresses the formation of BPDs [42]. Therefore, the trench structure formed by RIE is influenced by oxidation, which inhibits the formation of RIE-induced BPDs, meaning that the main source of BPDs causing the body diode degradation in this work is still P-type implantation. Devices from Vendor D (Gen 3) with the RIE-formed trench structure, yet still possessing highly reliable body diodes, provide strong proof for this. It is worth noting that since the deep P+ implants of the devices from Vendor K occupy a larger proportion in their cell pitch compared to those of the devices from Vendor D (Gen 4), the density of implantation-induced BPDs in devices from Vendor K may be higher than that in devices from Vendor D (Gen 4). As a result, under constant current stress and upon absorbing sufficient activation energy, devices from Vendor K exhibit more severe body diode degradation than those from Vendor D (Gen 4). Also, SFs causing severe body diode degradation in both cases become generation centers when these devices are under the blocking state, leading to a significant increase in the forward leakage current, resulting in a very ‘leaky’ state.

4.3. Structural Improvements to Enhance the Body Diode Reliability

4.3.1. Structural Improvements for Commercial Planar SiC Power MOSFETs

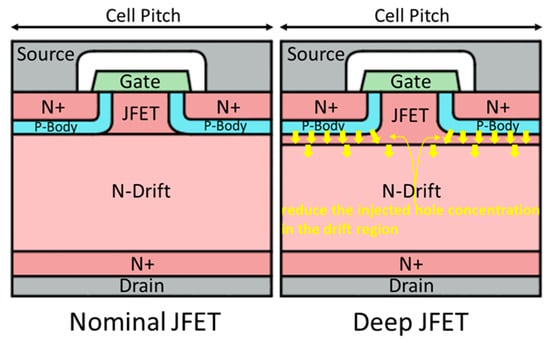

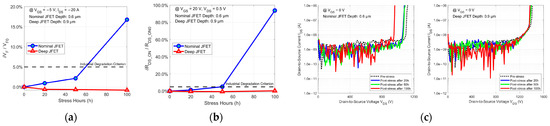

Experimental results in this work indicate that most commercial planar SiC power MOSFETs exhibit excellent reliability in their body diodes. These high-reliability body diodes meet the requirements of some specific application scenarios as free-wheeling diodes. However, some vendors’ devices exhibit body diode degradation still slightly beyond the industrial degradation criterion after the prolonged constant current stress, and therefore they may not be as competitive in harsher environments compared to devices from other vendors with superior body diodes. Considering the high cost of heated ion implantation systems and the limited capacity of fabs running them, some structural improvements can also help enhance the body diode reliability. Previous analysis revealed that the SFs causing body diode degradation expand due to the absorption of the activation energy from the recombination of injected holes and electrons in the drift region, suggesting a strategy to suppress the degradation by reducing this recombination in the drift region. Figure 5 shows a design with a deep N-type-doped JFET in the conventional planar structure to reduce the injected hole concentration in the drift region, thus reducing the recombination in the drift region. Five 1.2 kV planar SiC power MOSFETs based on this deep JFET design were fabricated, and as a control group, another five with a nominal JFET were also fabricated. The general information on these fabricated DUTs is summarized in Table 3. Knowing the die dimensions of the fabricated devices for a die area of ~0.045 cm2, both sets of devices underwent stress at the same current density of ~467 A/cm2 for 100 h. The results of this 100 h stress test are shown in Figure 6. As illustrated in Figure 6a,b, even though they are planar SiC power MOSFETs, the body diode degradation of these lab-grade devices with a nominal JFET still exceeds the industrial degradation criterion. In contrast, degradation in devices with a deep JFET is significantly suppressed, achieving reliability similar to the body diodes of advanced commercial planar SiC power MOSFETs. Moreover, the variations in the representative blocking characteristics in Figure 6c also demonstrate that the deep JFET structure suppresses body diode degradation, achieving very stable blocking characteristics, unlike the noticeable degradation observed in devices with the nominal JFET structure. Thus, the deep JFET design can be considered an effective structural improvement for enhancing the body diode’s reliability.

Figure 5.

The cross-sectional schematics of the planar structure with a nominal JFET and deep JFET from left to right.

Table 3.

General information on the fabricated DUTs with nominal and deep JFET in this work.

Figure 6.

The 100 h body diode stress test results of (a) , (b) , and (c) the changes in blocking characteristic curves for the fabricated planar SiC power MOSFETs with the nominal and deep JFET.

4.3.2. Structural Improvements for Commercial Trench SiC Power MOSFETs

For commercial trench SiC power MOSFETs, due to their unique structure, the deep P+ implantation is crucial for adequately protecting the gate trench corners. However, the excessive P+ implantation depths and doses often come at the expense of body diode reliability. Devices from Vendor D (Gen 3) offer insights into maintaining the body diode reliability in a trench structure. Since mainly the bottom corners of the gate trench require deep P+ protection, the direct deep P+ implantation from the device surface can be replaced by first performing RIE to approach the gate trench corners at both sides, followed by a shallower P+ implantation process. This approach ensures protection for the gate trench corners to a certain extent while minimizing the energy of the P+ implantation, reducing the introduction of implantation-induced BPDs. However, compared to the deep P+ implantation, there may be slightly sacrificed protection for the gate trench corners. This could necessitate the derating of the drift region, eroding the benefits of the trench design. Therefore, the structural improvements in commercial trench SiC power MOSFETs will be a trade-off. While ensuring that the dose and energy of the P+ implantation cause body diode degradation below the industrial degradation criterion, the depth of the pre-implantation RIE should be adjusted to ensure that the position of P+ can provide maximum protection for the gate trench corners, thus minimizing the derating of the drift region and maximizing the device performance.

5. Conclusions

This work explores the reliability of the parasitic body diodes in 1.2 kV commercial SiC power MOSFETs with both planar and trench structures. Through a sufficient sample size, the degradation of the body diode for each DUT was studied with the yields of qualified body diodes after the stress, for investigating the possibility of using the body diode as a free-wheeling diode. Due to the structural advantage and mature process, the parasitic body diode of 1.2 kV commercial planar SiC power MOSFETs presents high reliability, demonstrating or having realized the potential of direct application as a free-wheeling diode. Furthermore, structural improvements, such as a deep JFET design, can further enhance the reliability of the body diode to meet more stringent application scenarios. This helps reduce the production cost and improve the production capacity of 1.2 kV commercial planar SiC power MOSFETs. However, for 1.2 kV commercial trench SiC power MOSFETs, the high electric field crowding at the gate trench corners under the blocking state suggests that the shielding role of the deep P+ implants is required, adversely affecting the reliability of the body diode due to implantation-induced BPDs. Therefore, 1.2 kV commercial trench SiC power MOSFETs may still need to be integrated with external Schottky diodes as stable free-wheeling diodes for switching applications, negatively impacting their production cost and capacity. Some vendors of 1.2 kV commercial trench SiC power MOSFETs have achieved highly reliable body diodes by sacrificing some of the shielding function from the P+ implants on the gate trench corners, thereby eroding some of the device performance gains achieved by the trench structure. However, the trade-off design based on the P+ implantation depth, dose, and position will continue to be the research focus for 1.2 kV commercial trench SiC power MOSFETs aiming to use parasitic body diodes as free-wheeling diodes.

Author Contributions

Conceptualization, J.Q., M.H.W. and A.K.A.; methodology, J.Q. and M.J.; software, J.Q. and L.S.; validation, J.Q., L.S., M.J. and M.B.; formal analysis, J.Q., L.S., M.J., M.B., A.S., H.Y., S.H., M.H.W. and A.K.A.; investigation, J.Q., L.S., M.J., M.B. and H.Y.; resources, J.Q.; data curation, J.Q. and L.S.; writing—original draft preparation, J.Q.; writing—review and editing, J.Q., A.S. and A.K.A.; visualization, J.Q.; supervision, A.K.A.; project administration, A.S.; funding acquisition, A.S. All authors have read and agreed to the published version of the manuscript.

Funding

This research was funded by Ford Auto Co., grant number GR123387.

Data Availability Statement

Data are contained within the article.

Acknowledgments

This research is supported by Ford Motor Co. under the Ford-OSU Alliance Project-Phase II to The Ohio State University. The authors would like to thank the team members from Ford Motor Co. under the project for the helpful discussion.

Conflicts of Interest

Author Atsushi Shimbori was employed by the company Ford Motor Co. The remaining authors declare that the research was conducted in the absence of any commercial or financial relationships that could be construed as a potential conflict of interest. The authors declare that this study received funding from Ford Auto Co. The funders had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript; or in the decision to publish the results.

References

- Choi, H. Overview of Silicon Carbide Power Devices; Fairchild Semiconductor: San Jose, CA, USA, 2016. [Google Scholar]

- Siemieniec, R.; Peters, D.; Esteve, R.; Bergner, W.; Kück, D.; Aichinger, T.; Basler, T.; Zippelius, B. A SiC Trench MOSFET concept offering improved channel mobility and high reliability. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017. [Google Scholar]

- Anders, M.A.; Lenahan, P.M.; Cochrane, C.J.; Lelis, A.J. Relationship Between the 4H-SiC/SiO2 Interface Structure and Electronic Properties Explored by Electrically Detected Magnetic Resonance. IEEE Trans. Electron Devices 2015, 62, 301–308. [Google Scholar] [CrossRef]

- Wan, C.; Xu, H.; Xia, J.; Ao, J. Ultrahigh-temperature oxidation of 4H-SiC (0 0 0 1) and gate oxide reliability dependence on oxidation temperature. J. Cryst. Growth 2020, 530, 125250. [Google Scholar] [CrossRef]

- Chen, P.; Miao, W.; Ahmed, T.; Pan, Y.; Lin, C.; Chen, S.; Kuo, H.; Tsui, B.; Lien, D. Defect Inspection Techniques in SiC. Nanoscale Res. Lett. 2022, 17, 30. [Google Scholar] [CrossRef] [PubMed]

- Langpoklakpam, C.; Liu, A.-C.; Chu, K.-H.; Hsu, L.-H.; Lee, W.-C.; Chen, S.-C.; Sun, C.-W.; Shih, M.-H.; Lee, K.-Y.; Kuo, H.-C. Review of Silicon Carbide Processing for Power MOSFET. Crystals 2022, 12, 245. [Google Scholar] [CrossRef]

- Fukuda, K.; Suzuki, S.; Tanaka, T.; Arai, K. Reduction of interface-state density in 4H–SiC n-type metal–oxide–semiconductor structures using high-temperature hydrogen annealing. Appl. Phys. Lett. 2000, 76, 1585–1587. [Google Scholar] [CrossRef]

- Li, H.F.; Dimitrijev, S.; Harrison, H.B.; Sweatman, D. Interfacial characteristics of N2O and NO nitrided SiO2 grown on SiC by rapid thermal processing. Appl. Phys. Lett. 1997, 70, 2028–2030. [Google Scholar] [CrossRef]

- Li, H.; Dimitrijev, S.; Harrison, H.B. Improved reliability of NO-nitrided SiO2 grown on p-type 4H-SiC. IEEE Electron Device Lett. 1998, 19, 279–281. [Google Scholar]

- Chung, G.Y.; Tin, C.C.; Williams, J.R.; McDonald, K.; Di Ventra, M.; Pantelides, S.T.; Feldman, L.C.; Weller, R.A. Effect of nitric oxide annealing on the interface trap densities near the band edges in the 4H polytype of silicon carbide. Appl. Phys. Lett. 2000, 76, 1713–1715. [Google Scholar] [CrossRef]

- Zhao, Z.; Li, Y.; Xia, X.; Wang, Y.; Zhou, P.; Li, Z. Growth of high-quality 4H-SiC epitaxial layers on 4° off-axis C-face 4H-SiC substrates. J. Cryst. Growth 2020, 531, 125355. [Google Scholar] [CrossRef]

- Itoh, H.; Enokizono, T.; Miyase, T.; Hori, T.; Wada, K.; Furumai, M. High-Quality SiC Epitaxial Wafer “EpiEra” Realizing High-Reliability Large-Current Power Devices. SEI Tech. Rev. 2020, 91, 49. [Google Scholar]

- Qian, J.; Kim, D.; Jin, M.; Zhu, S.; Shi, L.; Shimbori, A.; Sung, W.; Agarwal, A.K. A Comparison of Body Diode Degradation in Commercial 1.2 kV SiC Power MOSFETs with the Planar and Trench Structure. In Proceedings of the 2023 65th Electronic Materials Conference, Santa Barbara, CA, USA, 28–30 June 2023. [Google Scholar]

- Qian, J.; Liu, T.; Soto, J.; Al-Jassim, M.M.; Stahlbush, R.; Mahadik, N.; Shi, L.; Jin, M.; Agarwal, A.K. A Comparison of Ion Implantation at Room Temperature and Heated Ion Implantation on the Body Diode Degradation of Commercial 3.3 kV 4H-SiC Power MOSFETs. In Proceedings of the 2022 IEEE 9th Workshop on Wide Bandgap Power Devices & Applications (WiPDA), Redondo Beach, CA, USA, 7–9 November 2022. [Google Scholar]

- Zhang, X.; Gant, L. Selecting A Freewheeling Diode Solution for Lowest Losses with SiC MOSFETs. Available online: https://www.how2power.com/pdf_view.php?url=/newsletters/1806/articles/H2PToday1806_design_Littelfuse.pdf (accessed on 31 June 2018).

- Telford, M. SiC making further inroads into silicon for EV powertrains. Semicond. Today 2023, 18, 3. Available online: https://www.semiconductor-today.com/news_items/backissues/semiconductor-today-april-2023.pdf (accessed on 17 April 2023).

- Sarnago, H.; Lucía, Ó.; Jiménez, R.; Gaona, P. Differential-Power-Processing On-Board-Charger for 400/800-V Battery Architectures using 650-V Super Junction MOSFETs. In Proceedings of the 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), Phoenix, AZ, USA, 14–17 June 2021. [Google Scholar]

- SiC Is Replacing Si in Electric Vehicles. Available online: https://fastsic.com/2020/06/24/sic-is-replacing-si-in-electric-vehicles/ (accessed on 24 June 2020).

- Jung, C. Power Up with 800-V Systems: The benefits of upgrading voltage power for battery-electric passenger vehicles. IEEE Electrif. Mag. 2017, 5, 53–58. [Google Scholar] [CrossRef]

- Lucid Air to be the Fastest Charging EV, Featuring a 900 V+ Architecture Delivering a Charging Rate of up to 20 Miles Per Minute. Available online: https://lucidmotors.com/media-room/lucid-air-fastest-charging-ev (accessed on 19 August 2020).

- Goldberg, L. Exploiting SiC MOSFETs to Power EV Innovation. Available online: https://www.electronicdesign.com/markets/automotive/article/21262547/electronic-design-exploiting-sic-mosfets-to-power-ev-innovation (accessed on 23 March 2023).

- Johnstone, C. Power Electronics Cooling: How to Reduce the Cost of Inverter Modules by Reducing SiC Area. Available online: https://jetcool.com/post/power-electronics-cooling-how-to-reduce-the-cost-of-inverter-modules-by-reducing-sic-area/ (accessed on 8 October 2020).

- Roccaforte, F.; Greco, G.; Fiorenza, P. Processing Issues in SiC and GaN Power Devices Technology: The Cases of 4H-SiC Planar MOSFET and Recessed Hybrid GaN MISHEMT. In Proceedings of the 2018 International Semiconductor Conference (CAS), Sinaia, Romania, 10–12 October 2018. [Google Scholar]

- Chaturvedi, M.; Dimitrijev, S.; Haasmann, D.; Moghadam, H.A.; Pande, P.; Jadli, U. Comparison of Commercial Planar and Trench SiC MOSFETs by Electrical Characterization of Performance-Degrading Near-Interface Traps. IEEE Trans. Electron Devices 2022, 69, 6225–6230. [Google Scholar] [CrossRef]

- Kim, J.; Kim, K. 4H-SiC Double-Trench MOSFET with Side Wall Heterojunction Diode for Enhanced Reverse Recovery Performance. Energies 2020, 13, 4602. [Google Scholar] [CrossRef]

- Seok, O.; Kang, I.; Moon, J.; Kim, H.; Ha, M.; Bahng, W. Double p-base structure for 1.2-kV SiC trench MOSFETs with the suppression of electric-field crowding at gate oxide. Microelectron. Eng. 2020, 225, 111280. [Google Scholar] [CrossRef]

- Park, Y.; Yoon, H.; Kim, C.; Kim, G.; Kang, G.; Seok, O.; Ha, M. Design and Optimization of 1.2 kV SiC Trench MOSFETs Using a Tilted Ion Implantation Process for High Breakdown Voltage. Jpn. J. Appl. Phys. 2023, 62, 011001. [Google Scholar] [CrossRef]

- Russell, S.; Gammon, P. ROHM Gen 4: A Technical Review. Available online: https://www.techinsights.com/blog/rohm-gen-4-technical-review (accessed on 2 August 2022).

- Yang, T.; Wang, Y.; Yue, R. SiC Trench MOSFET with Reduced Switching Loss and Increased Short-Circuit Capability. IEEE Trans. Electron Devices 2020, 67, 3685–3690. [Google Scholar] [CrossRef]

- Williams, R.K.; Darwish, M.N.; Blanchard, R.A.; Siemieniec, R.; Rutter, P.; Kawaguchi, Y. The Trench Power MOSFET: Part I—History, Technology, and Prospects. IEEE Trans. Electron Devices 2017, 64, 674–691. [Google Scholar] [CrossRef]

- Allouche, A.; Barbarini, E. Power Electronics: SiC Is on a Roll—The Chronicles by Yole SystemPlus. Available online: https://www.yolegroup.com/technology-outlook/power-electronics-sic-is-on-a-roll-the-chronicles-by-yole-systemplus/ (accessed on 16 March 2023).

- Yi, B.; Hu, H.; Lin, J.; Cheng, J.; Huang, H.; Kong, M. SiC trench MOSFET with integrated side-wall Schottky barrier diode having P+ electric field shield. IEICE Electron. Express 2019, 16, 1–10. [Google Scholar] [CrossRef]

- Chen, Y.; Huang, H.; Rao, Y.; He, Z.; Lai, P.; Chen, Y.; Xu, X.; Liu, C. Degradation assessment of 1.2-kV SiC MOSFETs and comparative study with 1.2-kV Si IGBTs under power cycling. Microelectron. Reliab. 2022, 132, 114528. [Google Scholar] [CrossRef]

- Ni, Z.; Lyu, X.; Yadav, O.P.; Singh, B.N.; Zheng, S.; Cao, D. Overview of Real-Time Lifetime Prediction and Extension for SiC Power Converters. IEEE Trans. Power Electron. 2020, 35, 7765–7794. [Google Scholar] [CrossRef]

- Volke, A.; Hornkamp, M. Type tests and routine tests. In IGBT Modules: Technologies, Driver and Application, 2nd ed.; Infineon Technologies AG: Richardson, TX, USA, 2012; p. 509. [Google Scholar]

- Galeckas, A.; Linnros, J.; Pirouz, P. Recombination-enhanced Extension of Stacking Faults in 4H-SiC p-i-n Diodes under Forward Bias. Appl. Phys. Lett. 2002, 81, 883–885. [Google Scholar] [CrossRef]

- Stahlbush, R.; Mahadik, N.; Bonanno, P.; Soto, J. Defects in 4H-SiC epilayers affecting device yield and reliability. In Proceedings of the 2022 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 27–31 March 2022. [Google Scholar]

- Tawara, T.; Miyazawa, T.; Ryo, M.; Miyazato, M.; Fujimoto, T.; Takenaka, K.; Matsunaga, S.; Miyajima, M.; Otsuki, A.; Yonezawa, Y.; et al. Suppression of the Forward Degradation in 4H-SiC PiN Diodes by Employing a Recombination-Enhanced Buffer Layer. Mater. Sci. Forum 2017, 897, 419–422. [Google Scholar] [CrossRef]

- Zhang, Z.; Sudarshan, T. Basal Plane Dislocation-free Epitaxy of Silicon Carbide. Appl. Phys. Lett. 2005, 87, 151913. [Google Scholar] [CrossRef]

- Zhang, Z.; Moulton, E.; Sudarshan, T. Mechanism of Eliminating Basal Plane Dislocations in SiC Thin Films by Epitaxy on an Etched Substrate. Appl. Phys. Lett. 2006, 89, 081910. [Google Scholar] [CrossRef]

- Stahlbush, R.; Mahakik, K.; Lelis, A.; Green, R. Effects of Basal Plane Dislocations on SiC Power Device Reliability. In Proceedings of the 2018 IEEE 64th International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018. [Google Scholar]

- Stahlbush, R.; Mahadik, N. Defects Affecting SiC Power Device Reliability. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).