On-Chip Temperature Compensation for Small-Signal Gain Variation Reduction

Abstract

:1. Introduction

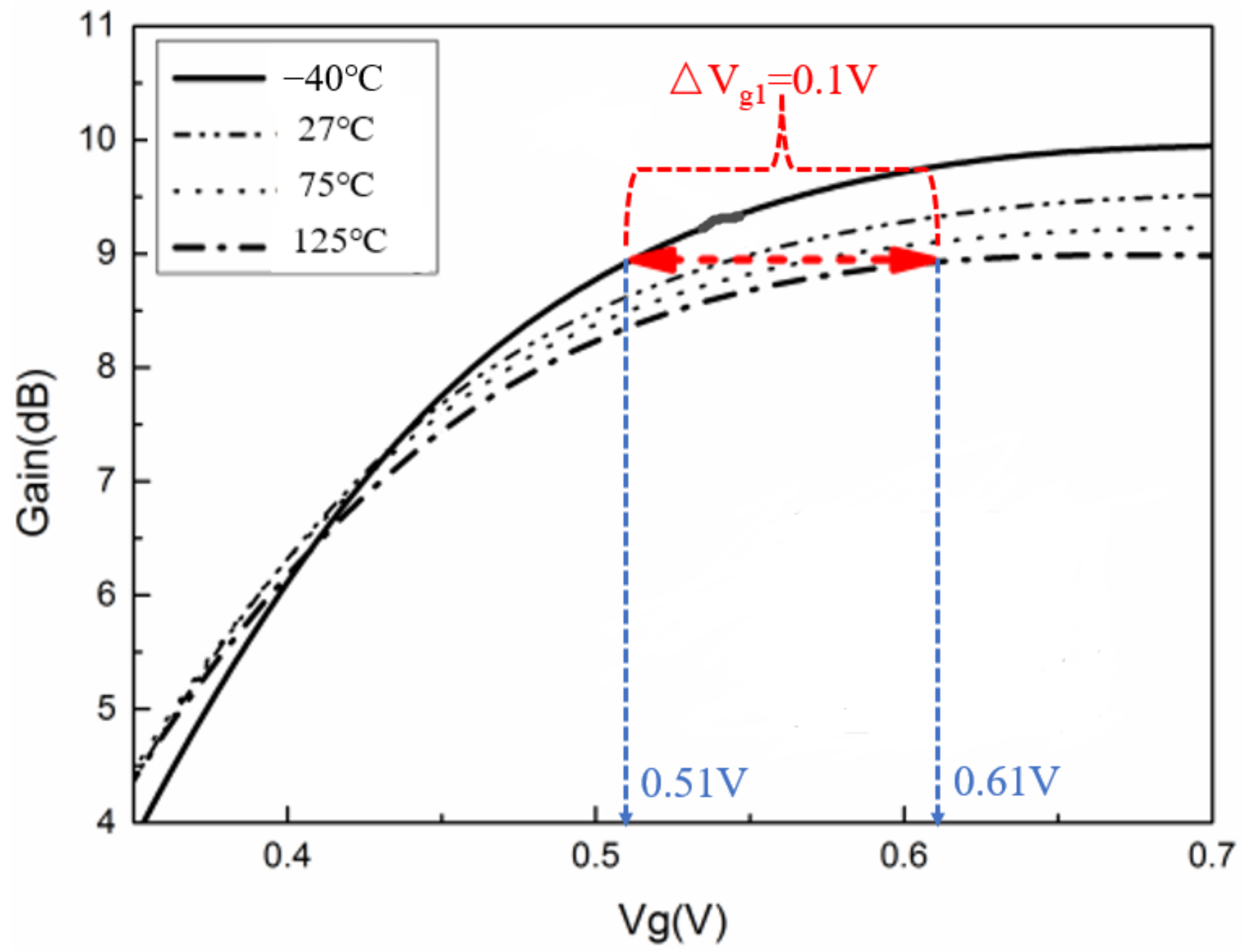

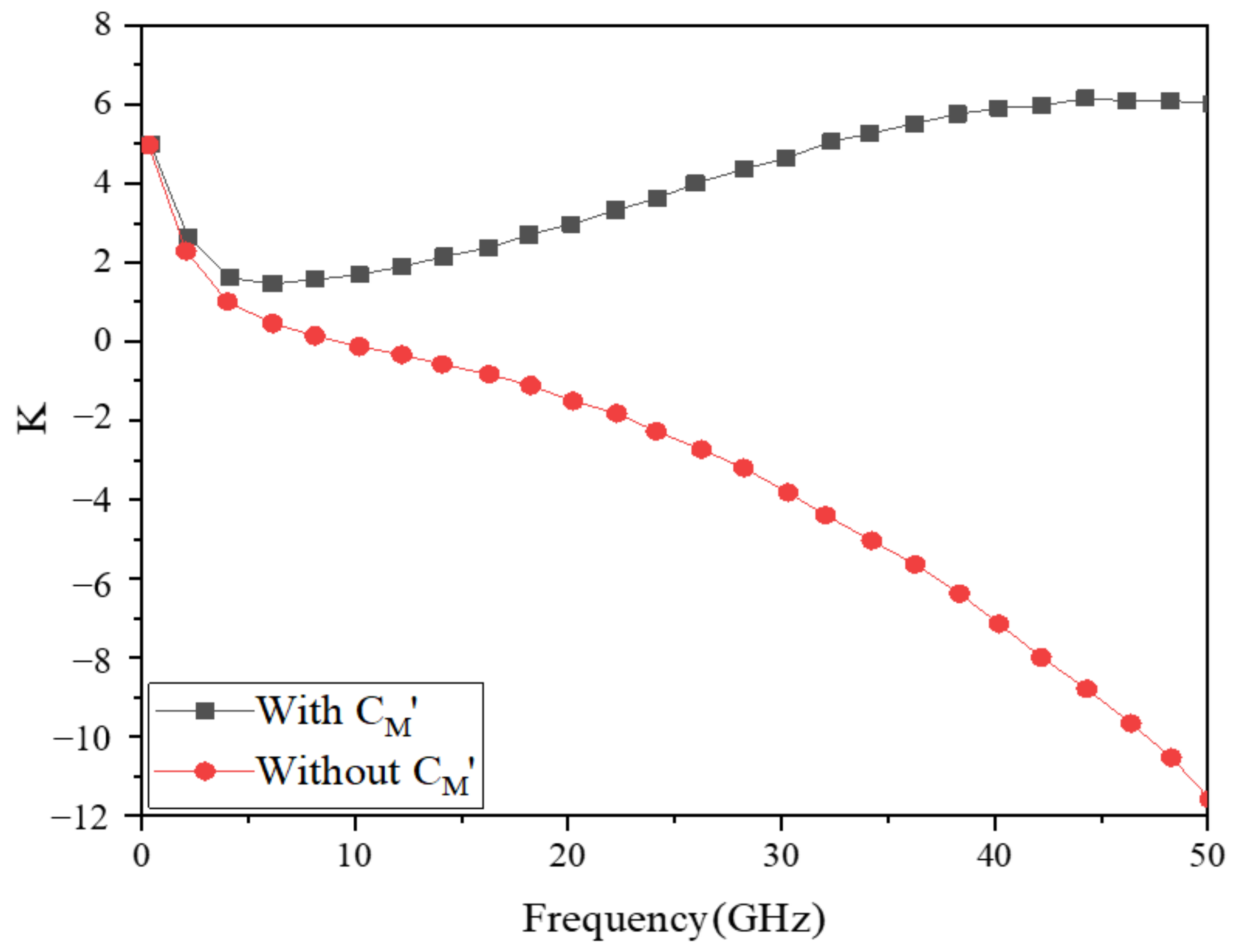

2. Temperature Characteristics of Single-Stage Amplifier Gain

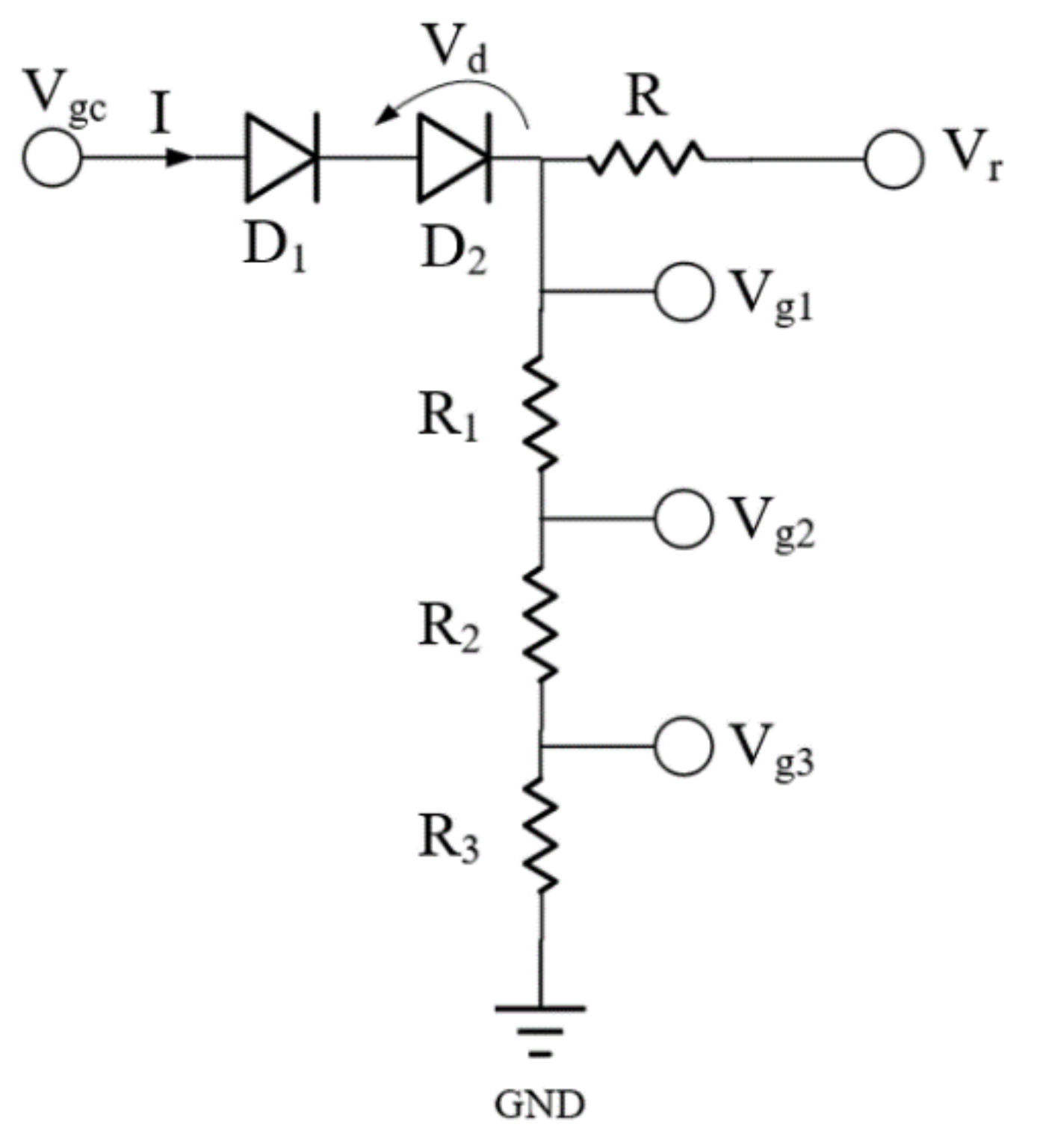

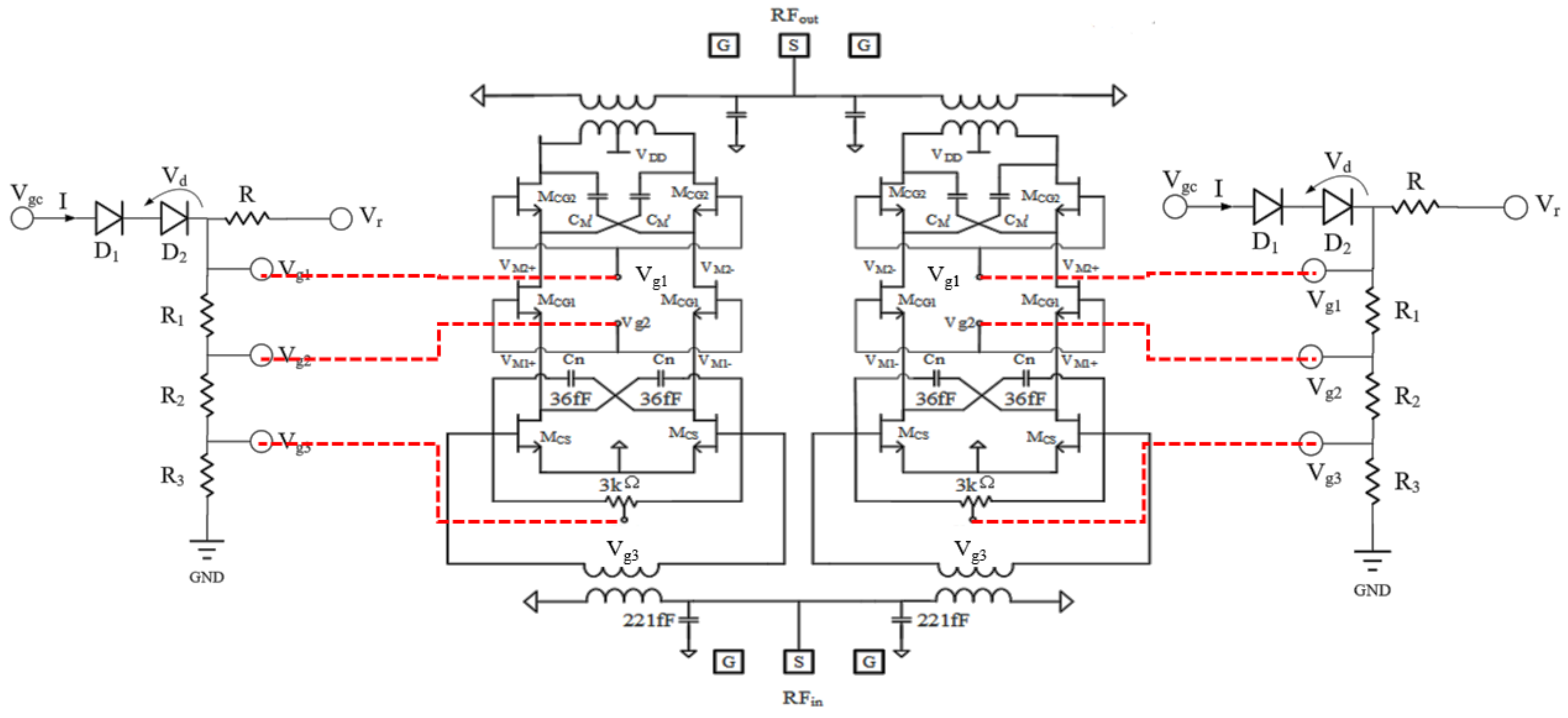

3. Principle and Design of Temperature Compensation Circuit

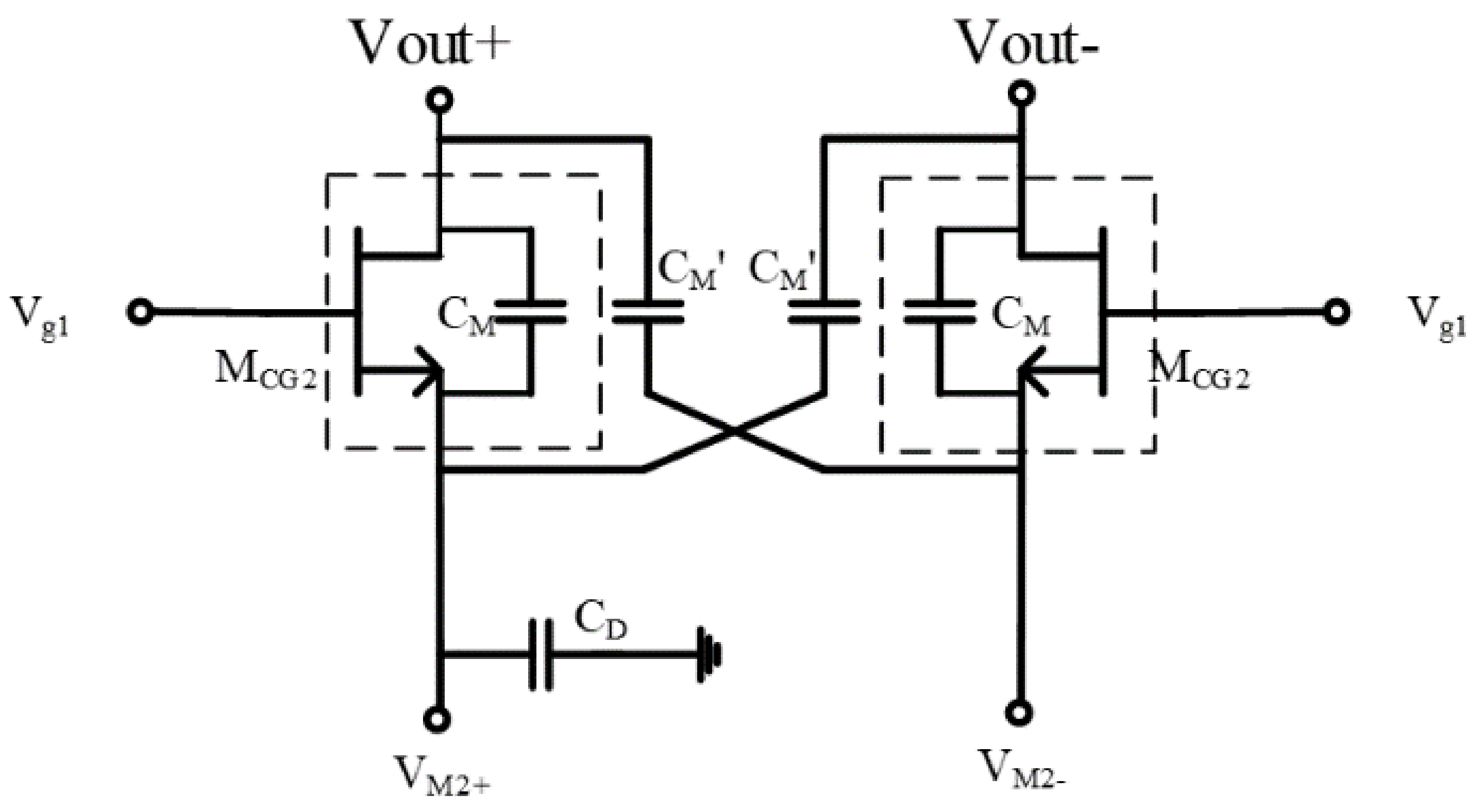

4. Differential Stacked Millimeter-Wave Broadband PA

5. Results and Discussion

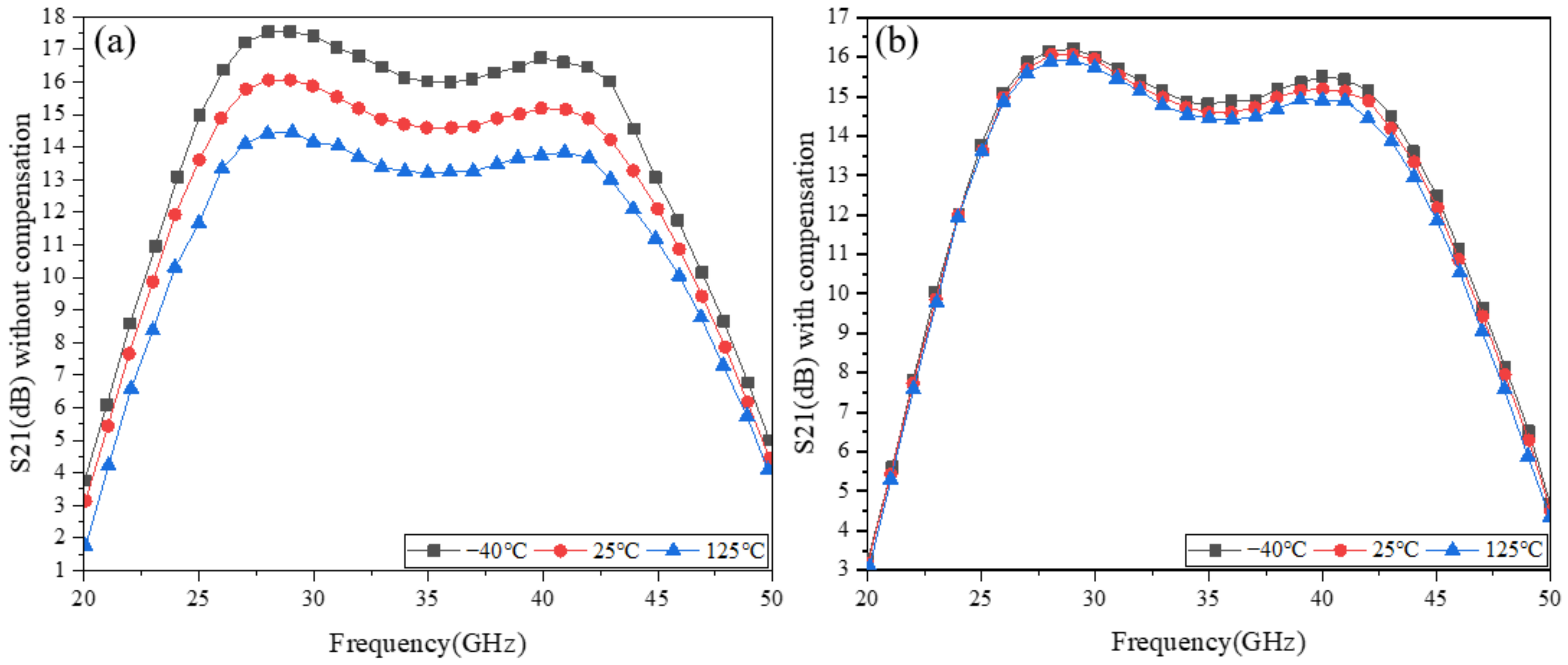

5.1. Small-Signal Gain at Different Temperatures

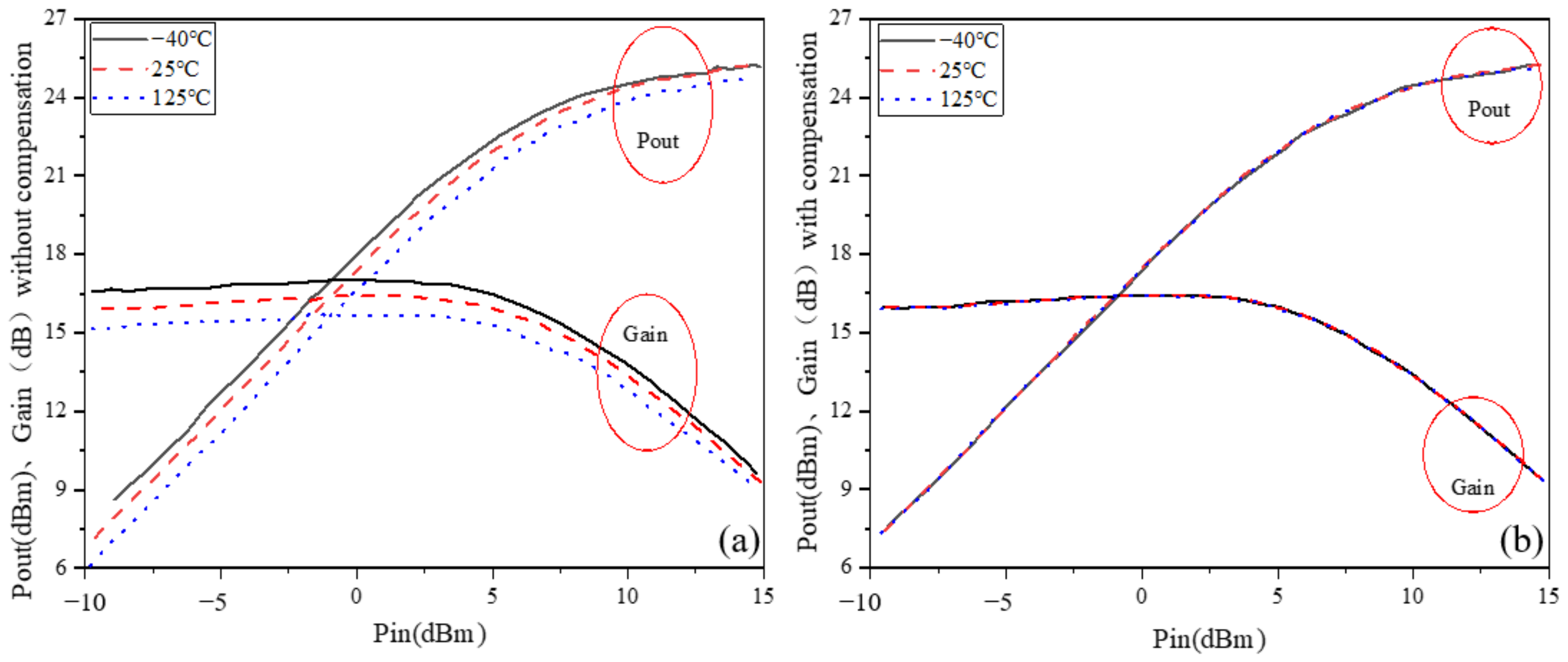

5.2. Output Power and PAE at Different Temperatures

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Wang, X.D.; Lv, X.; Guo, D.L.; Li, M.X.; Cheng, G.; Liu, J.S.; Yu, W.H. Terahertz power amplifier integrated with on-chip antenna using GaN TMIC technology. J. Infrared Millim. Waves 2019, 38, 683–689. [Google Scholar]

- Zhu, H.B.; Wei, H.; Tian, L.; Hong-Jun, T.; Ji-Xin, C.; Fan-Fan, H. Design and fabrication of Ka-band broadband combined power amplifier based on flexible substrate integrated waveguide technology. J. Infrared Millim. Waves 2010, 29, 180–184. [Google Scholar] [CrossRef]

- Huang, Z.Y.; Jun, X.U.; Ran, D.; Qi, Y.F. Design of a W-band power amplifier/combiner based on spatial power-combining technique. J. Infrared Millim. Waves 2018, 37, 454–458. [Google Scholar]

- Cao, Y.X.; Su, Y.B.; Wu, D.Y.; Jin, Z.; Wang, X.T.; Liu, X.Y. A 75 GHz 13.92 dBm InP DHBT cascode power amplifier. J. Infrared Millim. Waves 2012, 31, 294–297. [Google Scholar] [CrossRef]

- Yang, F.; Zhao, H.F.; Liu, J.T.; Liu, R.Z.; Liu, Y.P.; Hu, F.J.; Sun, S.; Feng, Y.U.; Zhou, Y. Solid-state power amplifiers for space: Going to extremely high frequency. J. Infrared Millim. Waves 2021, 40, 25–32. [Google Scholar]

- Karra, A.; Kondi, B.; Jayaraman, R. Implementation of wireless communication to transfer temperature and humidity monitoring data using Arduino Uno. In Proceedings of the 2020 International Conference on Communication and Signal Processing (ICCSP), Chennai, India, 28–30 July 2020; pp. 1101–1105. [Google Scholar]

- Chiang, C.Y.; Hsu, H.T.; Chang, E.Y. Monolithic wideband linear power amplifier with 45% power bandwidth using pseudomorphic high-electron-mobility transistors for long-term evolution application. Jpn. J. Appl. Phys. 2014, 53, 110311. [Google Scholar] [CrossRef]

- Giammello, V.; Ragonese, E.; Palmisano, G. A 15-dBm SiGe BiCMOS PA for 77-GHz Automotive Radar. IEEE Trans. Microw. Theory Tech. 2011, 59, 2910–2918. [Google Scholar] [CrossRef]

- Chen, B.; Lou, L.; Tang, K.; Wang, Y.; Gao, J.; Zheng, Y. A 13.5–19 GHz 20.6-dB Gain CMOS Power Amplifier for FMCW Radar Application. IEEE Microw. Wirel. Compon. Lett. 2017, 27, 377–379. [Google Scholar] [CrossRef]

- Ge, Q.; Liu, W.; Xu, B.; Qian, F.; Yao, C. A 77–100 GHz power amplifier using 0.1-μm GaAs PHEMT technology. J. Semicond. 2017, 38, 120–123. [Google Scholar] [CrossRef]

- Rautschke, F.; Maassen, D.; Ohnimus, F.; Schenk, L.; Dalisda, U.; Boeck, G. A hybrid 50-W GaN-HEMT Ku-band power amplifier. In Proceedings of the 2016 46th European Microwave Conference (EuMC), London, UK, 3–7 October 2016; pp. 1079–1082. [Google Scholar]

- Maassen, D.; Rautschke, F.; Boeck, G. Design and comparison of various coupled line Tx-filters for a Ku-band block upconverter. In Proceedings of the 2016 German Microwave Conference (GeMiC), Bochum, Germany, 14–16 March 2016; pp. 225–228. [Google Scholar]

- Wang, K.; Cheng, Z.; Fan, K.; Chen, S.; Liu, G.; Wang, H. High-efficiency power amplifier for Beidou satellite navigation system. In Proceedings of the 2015 IEEE 16th International Conference on Communication Technology (ICCT), Hangzhou, China, 18–20 October 2015; pp. 655–657. [Google Scholar]

- China Talking about the “Shelf Life” of Missiles. Military. Available online: http://www.81.cn/jfjbmap/content/2018-03/09/content_201251.htm (accessed on 9 March 2018).

- Wu, S.B.; Gao, J.F.; Wang, W.B.; Zhang, J.Y. W-Band MMIC PA With Ultrahigh Power Density in 100-nm AlGaN/GaN Technology. IEEE Trans. Electron Devices 2016, 63, 3882–3886. [Google Scholar]

- Qi, T.; He, S.; Shi, W. Third-octave power amplifier using ring-based matching network with high efficiency. Electron. Lett. 2016, 52, 883–885. [Google Scholar] [CrossRef]

- Zhou, S.; Fu, H.; Ma, J.; Zhang, Q. A neural network modeling approach to power amplifiers taking into account temperature effects. In Proceedings of the 2018 IEEE/MTT-S International Microwave Symposium, Philadelphia, PA, USA, 10–15 June 2018; pp. 1028–1031. [Google Scholar]

- Ma, X.; Duan, B.; Yang, Y. A 500–600 MHz GaN power amplifier with RC-LC stability network. J. Semicond. 2017, 38, 085003. [Google Scholar] [CrossRef]

- Yu, C.; Yuan, J.S. Electrical and Temperature Stress Effects on Class-AB Power Amplifier Performances. IEEE Trans. Electron Devices 2007, 54, 1346–1350. [Google Scholar]

- Cheng, J.H.; Wu, M.H.; Huang, H.T.; Wu, Y.M.; Tsai, J.H.; Huang, T.W. A K-band phase-locked loop in 0.18 μm CMOS technology for vital sign detection radar. In Proceedings of the 2014 IEEE MTT-S International Microwave Workshop Series on RF and Wireless Technologies for Biomedical and Healthcare Applications (IMWS-Bio2014), London, UK, 1–3 December 2014. [Google Scholar]

- Gs, J.; Banerj, E.G.; Raja, I. On-chip non-intrusive temperature detection and compensation of a fully integrated CMOS RF power amplifier. In Proceedings of the 2017 30th International Conference on VLSI Design and 2017 16th International Conference on Embedded Systems (VLSID), Hyderabad, India, 21–26 January 2017. [Google Scholar]

- Wenger, Y.; Meinerzhagen, B.; Ghazinour, A. Current-mode temperature compensation for a differential logarithmic amplifier in 180 nm BiCMOS. In Proceedings of the 2018 25th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Bordeaux, France, 9–12 December 2018; pp. 509–512. [Google Scholar]

- Qi, Q.; Chen, Z. A K-Band CMOS Amplifier with Temperature Compensation for Gain Variation Reduction. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 150–152. [Google Scholar] [CrossRef]

- Pour, F.L.; Ha, D.S. A Temperature compensated 5 GHz GaN on SiC power amplifier. In Proceedings of the 2020 IEEE 63rd International Midwest Symposium on Circuits and Systems (MWSCAS), Springfield, MA, USA, 9–12 August 2020; pp. 549–553. [Google Scholar]

- Li, S.; Fritsche, D.; Carta, C.; Ellinger, F. Design and characterization of a 12–40 GHz power amplifier in SiGe technology. In Proceedings of the 2018 IEEE Topical Conference on RF/Microwave Power Amplifiers for Radio and Wireless Applications (PAWR), Anaheim, CA, USA, 23–25 January 2018. [Google Scholar]

- Pascht, A.; Grozing, M.; Wiegner, D.; Berroth, M. Small-Signal and Temperature Noise Model for MOSFETs. IEEE Trans. Microw. Theory Tech. 2002, 50, 1927–1934. [Google Scholar] [CrossRef]

- Zhao, D.; Reynaert, P. A 40-nm CMOS E-Band 4-Way Power Amplifier with Neutralized Bootstrapped Cascode Amplifier and Optimum Passive Circuits. IEEE Trans. Microw. Theory Tech. 2015, 63, 4083–4089. [Google Scholar] [CrossRef]

- Razavi, B. Design of Analog CMOS Integrated Circuits; McGraw Hill Higher Education: New York, NY, USA, 2003; pp. 17–21. [Google Scholar]

- Neamen, D.A. Semiconductor Physics and Devices: Basic Principles; McGraw Hill Higher Education: New York, NY, USA, 2012; pp. 395–419. [Google Scholar]

- Lee, T.H. The Design of CMOS Radio-Frequency Integrated Circuits; Cambridge University Press: Cambridge, UK, 2012; pp. 172–189. [Google Scholar]

- Yamauchi, K.; Iyama, Y.; Yamaguchi, M.; Ikeda, Y.; Urasaki, S.; Takagi, T. X-band MMIC power amplifier with an on-chip temperature-compensation circuit. IEEE Trans. Microw. Theory Tech. 2001, 49, 2501–2506. [Google Scholar] [CrossRef]

- Wu, K.; Muralidharan, S.; Hella, M. A 104GHz–117GHz power amplifier with 10.4% PAE in thin digital 65 nm low power CMOS technology. In Proceedings of the 2016 IEEE MTT-S International Microwave Symposium (IMS), San Francisco, CA, USA, 1–3 May 2016. [Google Scholar]

- Lin, Y.S.; Gao, J.W.; Wang, C.C.; Lin, Y.W.; Chen, C.C. A wideband power amplifier with 13.2 dBm Psat and 19.5% PAE for 60~94 GHz wireless communication systems in 90 nm CMOS. In Proceedings of the 2016 IEEE Radio and Wireless Symposium (RWS), Austin, TX, USA, 24–27 January 2016; pp. 95–98. [Google Scholar]

- Thome, F.; Leuther, A.; Schlechtweg, M.; Ambacher, O. Broadband high-power W-band amplifier MMICs based on stacked-HEMT unit cells. IEEE Trans. Microw. Theory Tech. 2018, 66, 1312–1318. [Google Scholar] [CrossRef]

- Chen, T.; Tian, T.; Wu, J.H.; Gao, H. Design of a 5.8 GHz Stacked Power Amplifier. J. Microw. 2014, 30, 77–79. [Google Scholar]

- Zhou, S. Experimentally investigating the degradations of small-signal gain for a GaN class-AB dual-band power amplifier under high temperature and humidity conditions. AIP Adv. 2020, 10, 125219. [Google Scholar] [CrossRef]

- He, Z.; Zhou, S.; Nie, M. Experimentally investigating the performance degradations of the CMOS PA at different temperatures. AIP Adv. 2021, 11, 115205. [Google Scholar] [CrossRef]

- Kaamouchi, M.E.; Moussa, M.S.; Raskin, J.P.; Vanhoenacker-Janvier, D. Zero-temperature-coefficient biasing point of 2.4-GHz LNA in PD SOI CMOS technology. In Proceedings of the 2007 European Microwave Conference, Munich, Germany, 9–12 October 2007; pp. 1101–1104. [Google Scholar]

- Chen, W.L.; Chang, S.F.; Chen, K.M.; Huang, G.W.; Chang, J.C. Temperature Effect on Ku-Band Current-Reused Common-Gate LNA in 0.13 μm CMOS Technology. IEEE Trans. Microw. Theory Tech. 2009, 57, 2131–2138. [Google Scholar] [CrossRef]

- Motoyoshi, M.; Takano, K.; Yoshida, T.; Katayama, K.; Amakawa, S.; Minoru, F. 79 GHz CMOS power amplifier using temperature compensation bias. In Proceedings of the 2014 9th European Microwave Integrated Circuit Conference, Rome, Italy, 6–7 October 2014; pp. 49–52. [Google Scholar]

| Reference | Ref. [23] | Ref. [38] | Ref. [39] | Ref. [40] | Ref. [24] | This Work ② |

|---|---|---|---|---|---|---|

| Circuit | PA | LNA | LNA | PA | PA | PA |

| Technology | 90 nm | 130 nm SOI | 130 nm | 40 nm | GaN HEMT | 55 nm |

| Topology | 2-stage | 1-stage | 1-stage | 3-stage | 1-stage | 1-stage |

| Frequency (GHz) | 26.5 | 2.4 | 15.2 | 79 | 4.5–5.5 | 25–40 |

| Small-signal gain variation (dB) | 1.2 (−45~125 °C) | 0.9 (25~200 °C) | 3.1 (−20~120 °C) | 0.6 (10~100 °C) | 0.4 (−40~225 °C) | 0.1 (−40~125 °C) |

| Pout variation (dBm) (center frequency) | N/A | N/A | N/A | N/A | 24.0 (−40~225 °C) | 0.6 (−40~125 °C) |

| PAE variation (center frequency) | N/A | N/A | N/A | N/A | 12% (−40~225 °C) | 7.3% (−40~125 °C) |

| Area (mm2) | 0.5 ① | 0.6 ① | 0.6 ① | 0.11 ① | 6.6 | 0.378 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhou, S.; Wei, S.; Wang, J. On-Chip Temperature Compensation for Small-Signal Gain Variation Reduction. Micromachines 2022, 13, 1101. https://doi.org/10.3390/mi13071101

Zhou S, Wei S, Wang J. On-Chip Temperature Compensation for Small-Signal Gain Variation Reduction. Micromachines. 2022; 13(7):1101. https://doi.org/10.3390/mi13071101

Chicago/Turabian StyleZhou, Shaohua, Shizhe Wei, and Jian Wang. 2022. "On-Chip Temperature Compensation for Small-Signal Gain Variation Reduction" Micromachines 13, no. 7: 1101. https://doi.org/10.3390/mi13071101

APA StyleZhou, S., Wei, S., & Wang, J. (2022). On-Chip Temperature Compensation for Small-Signal Gain Variation Reduction. Micromachines, 13(7), 1101. https://doi.org/10.3390/mi13071101