Understanding the Origin of Metal Gate Work Function Shift and Its Impact on Erase Performance in 3D NAND Flash Memories

Abstract

:1. Introduction

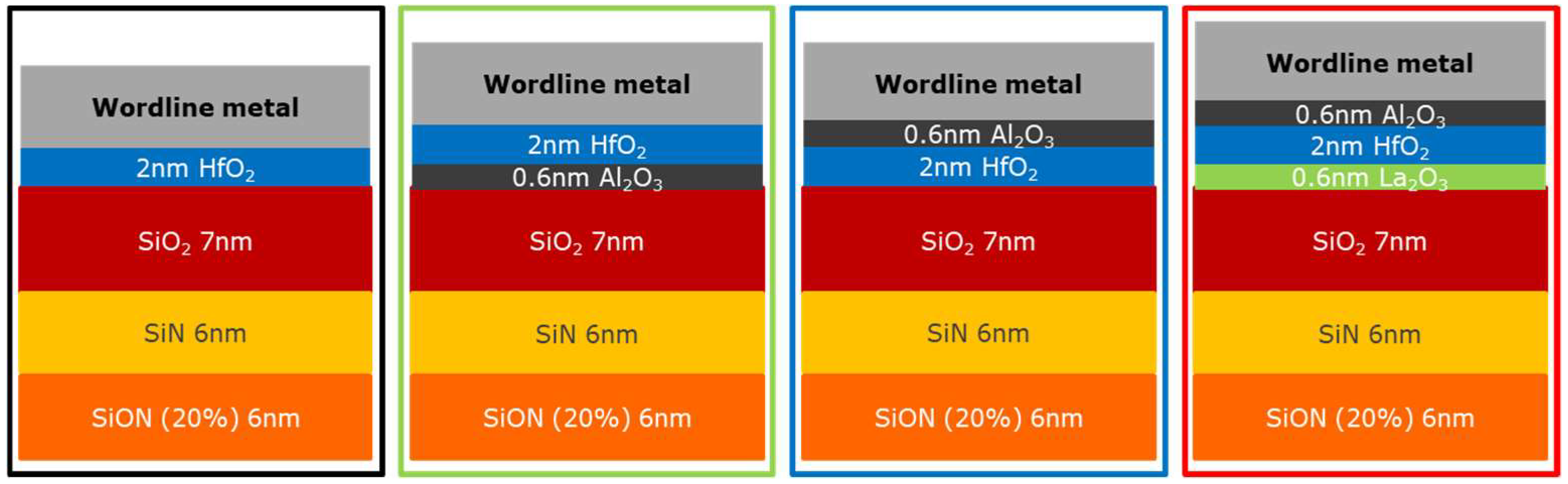

2. Materials and Methods

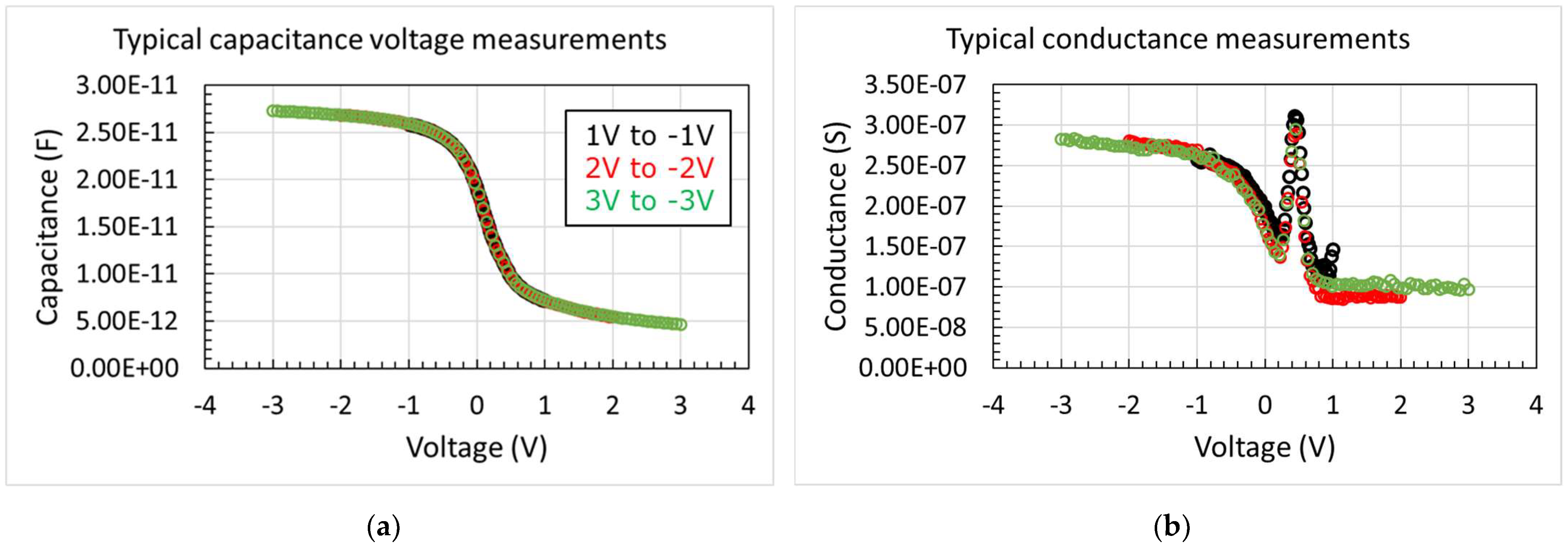

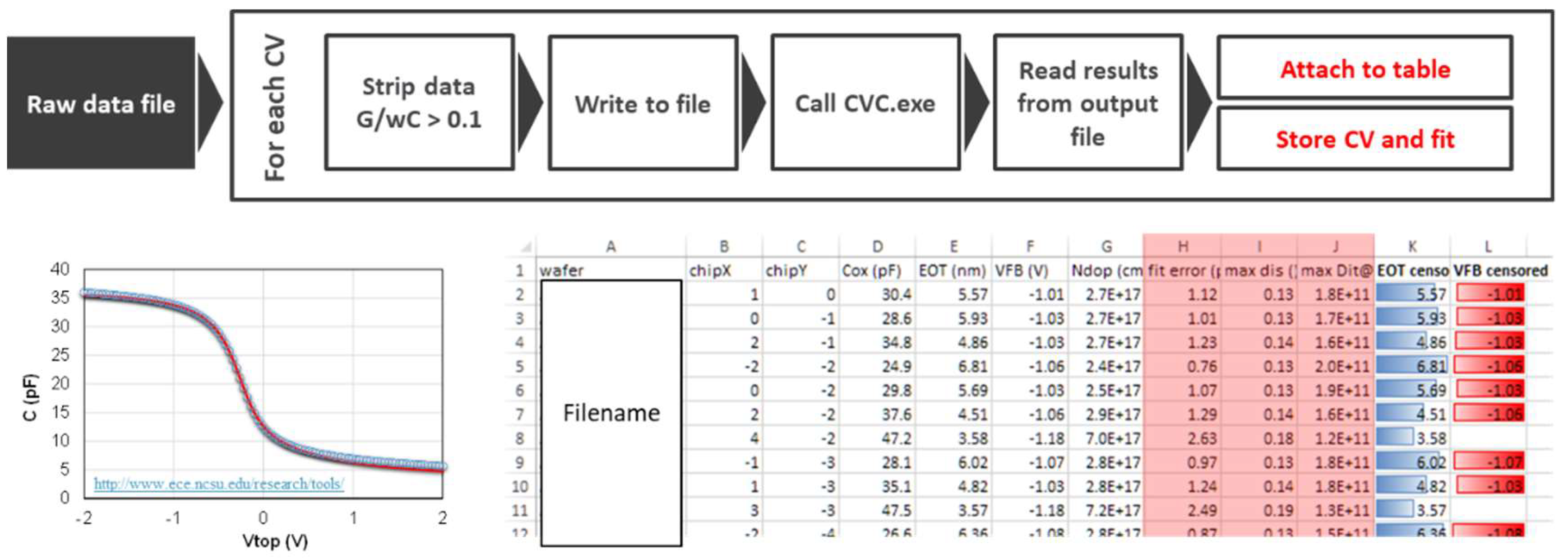

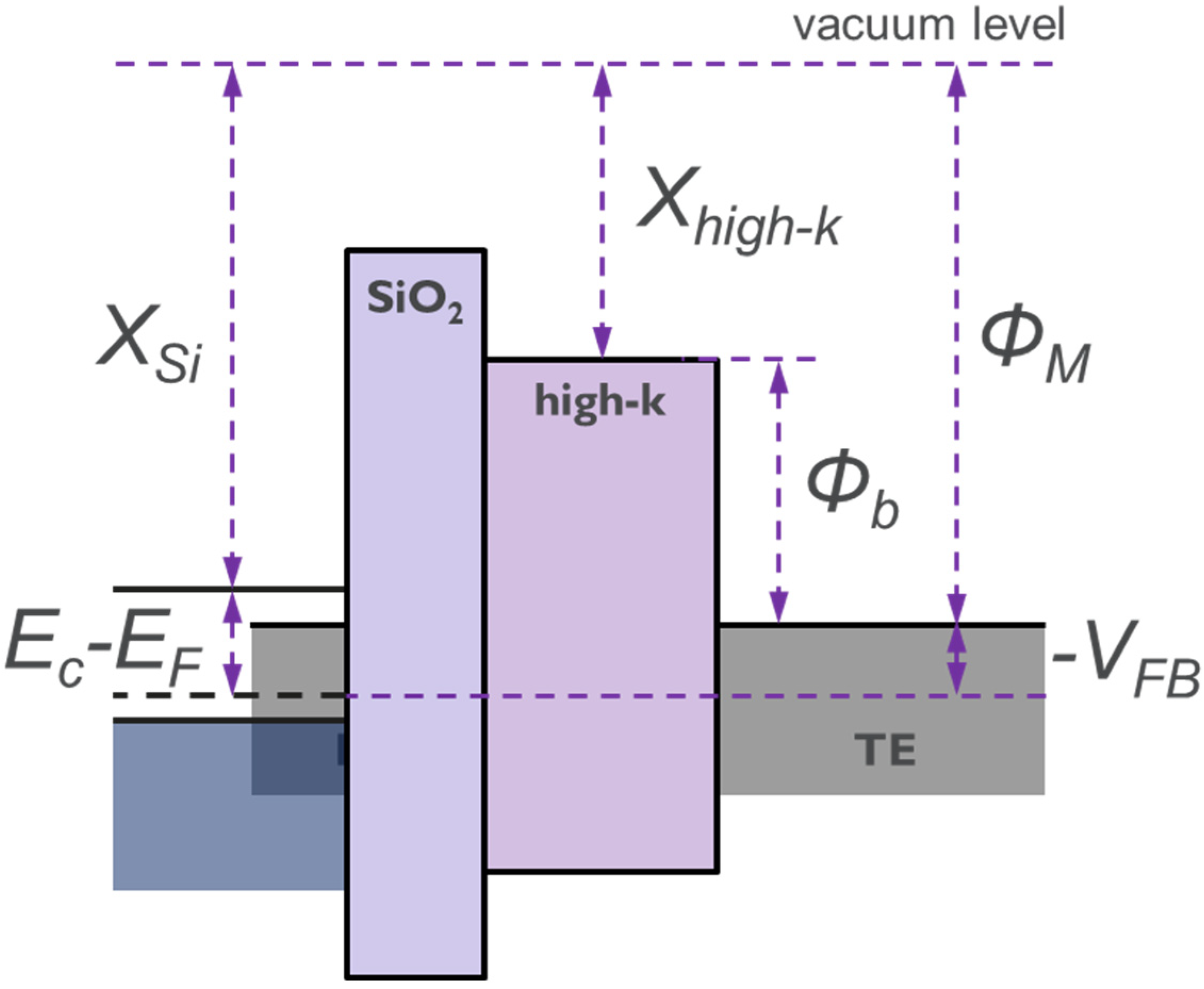

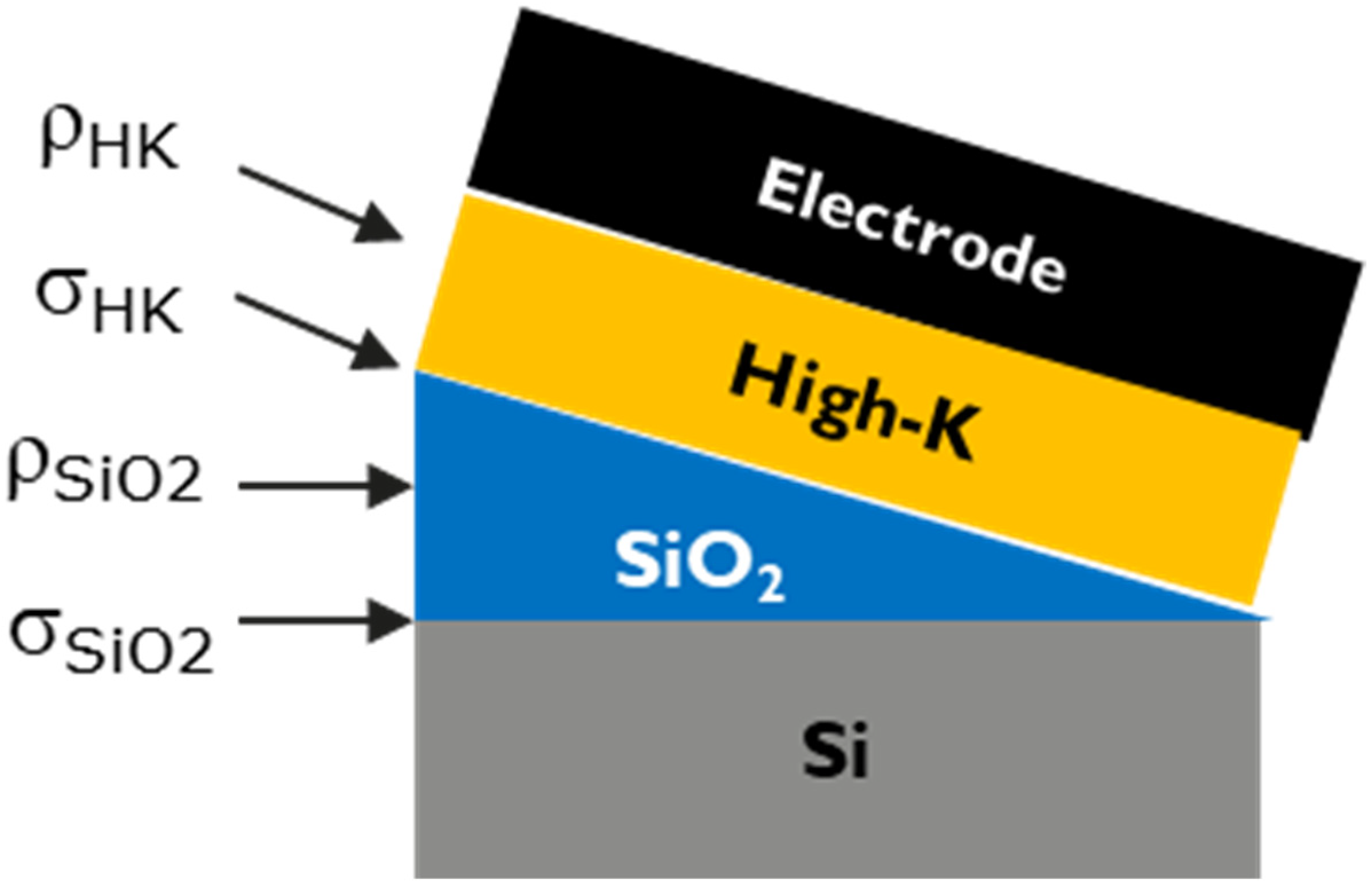

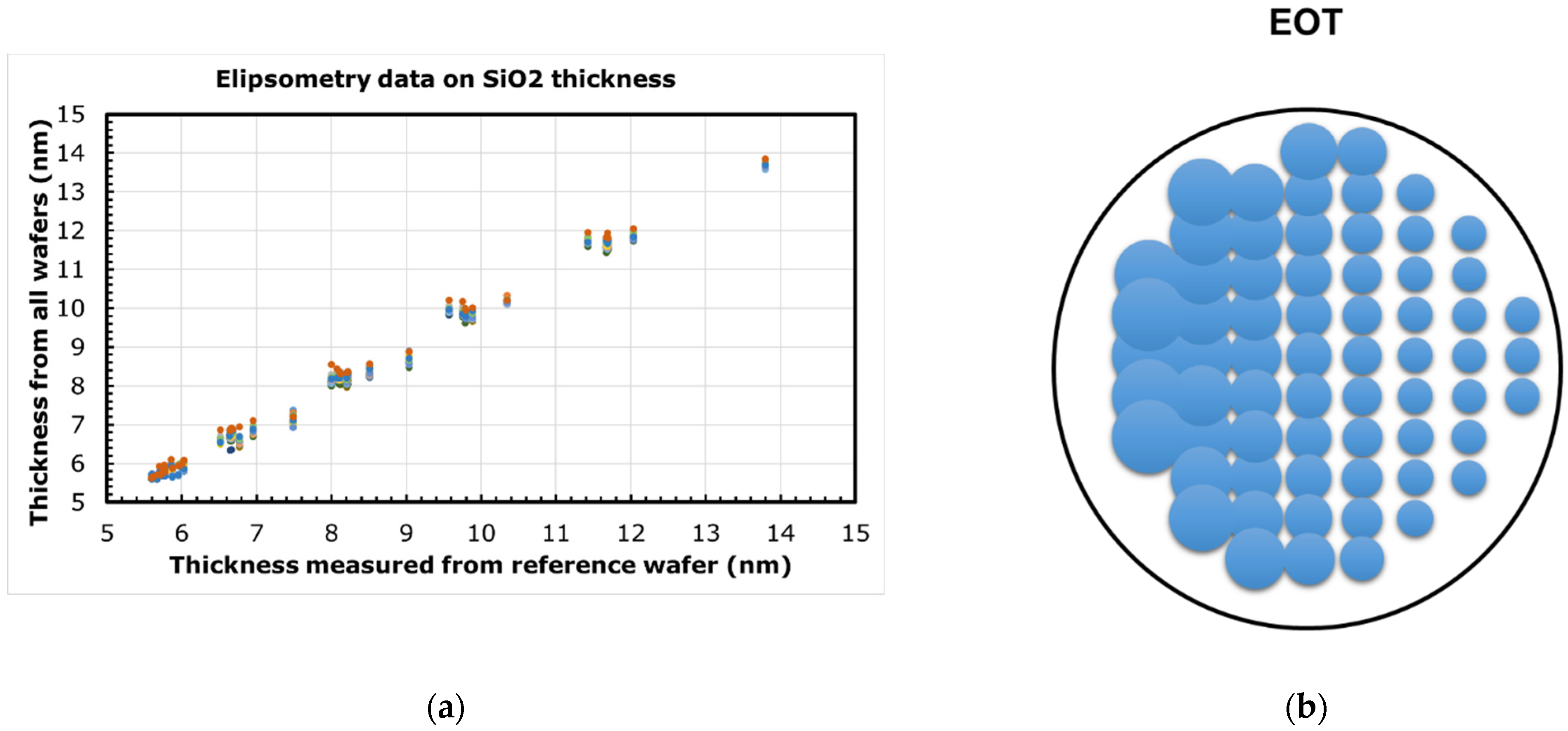

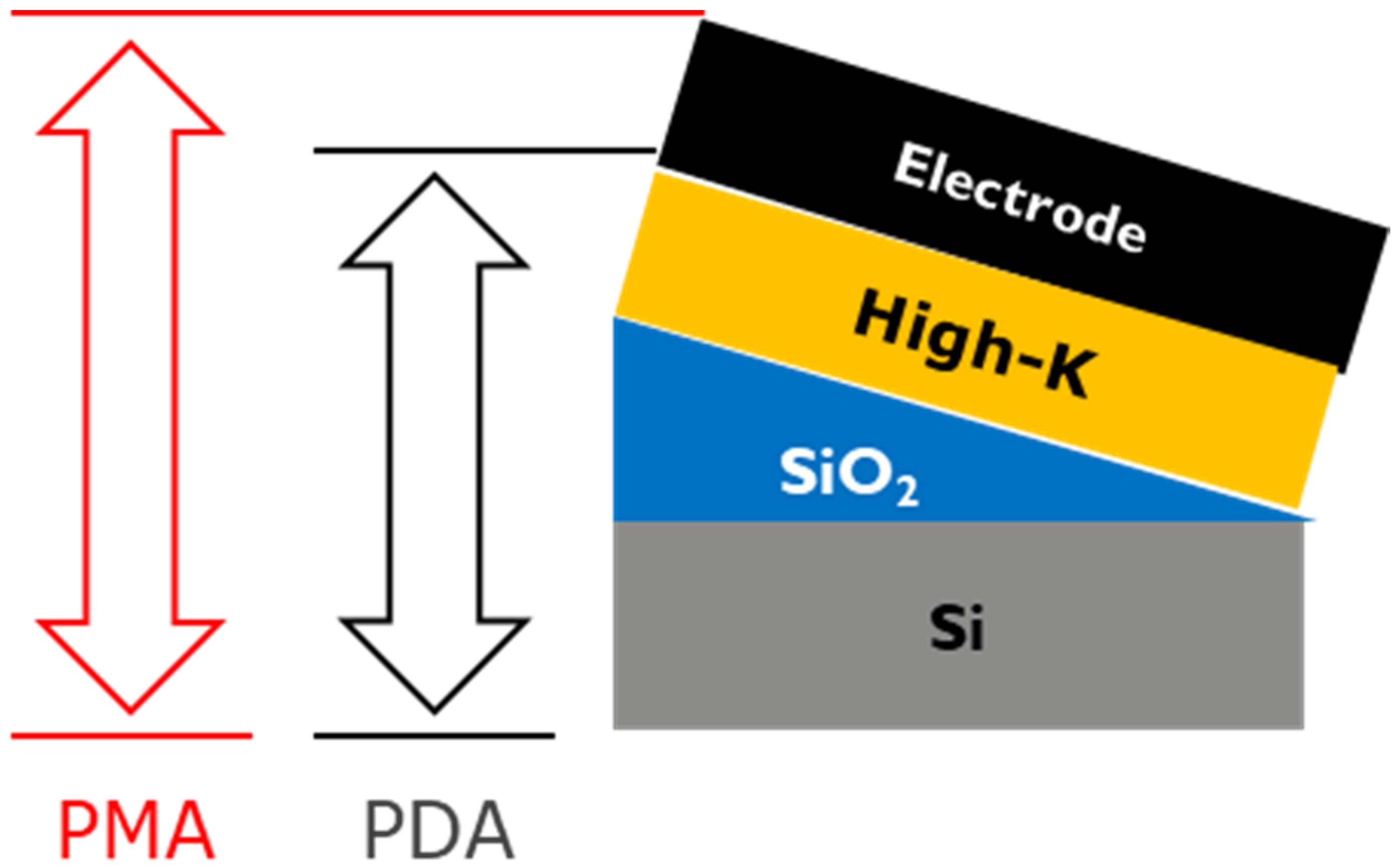

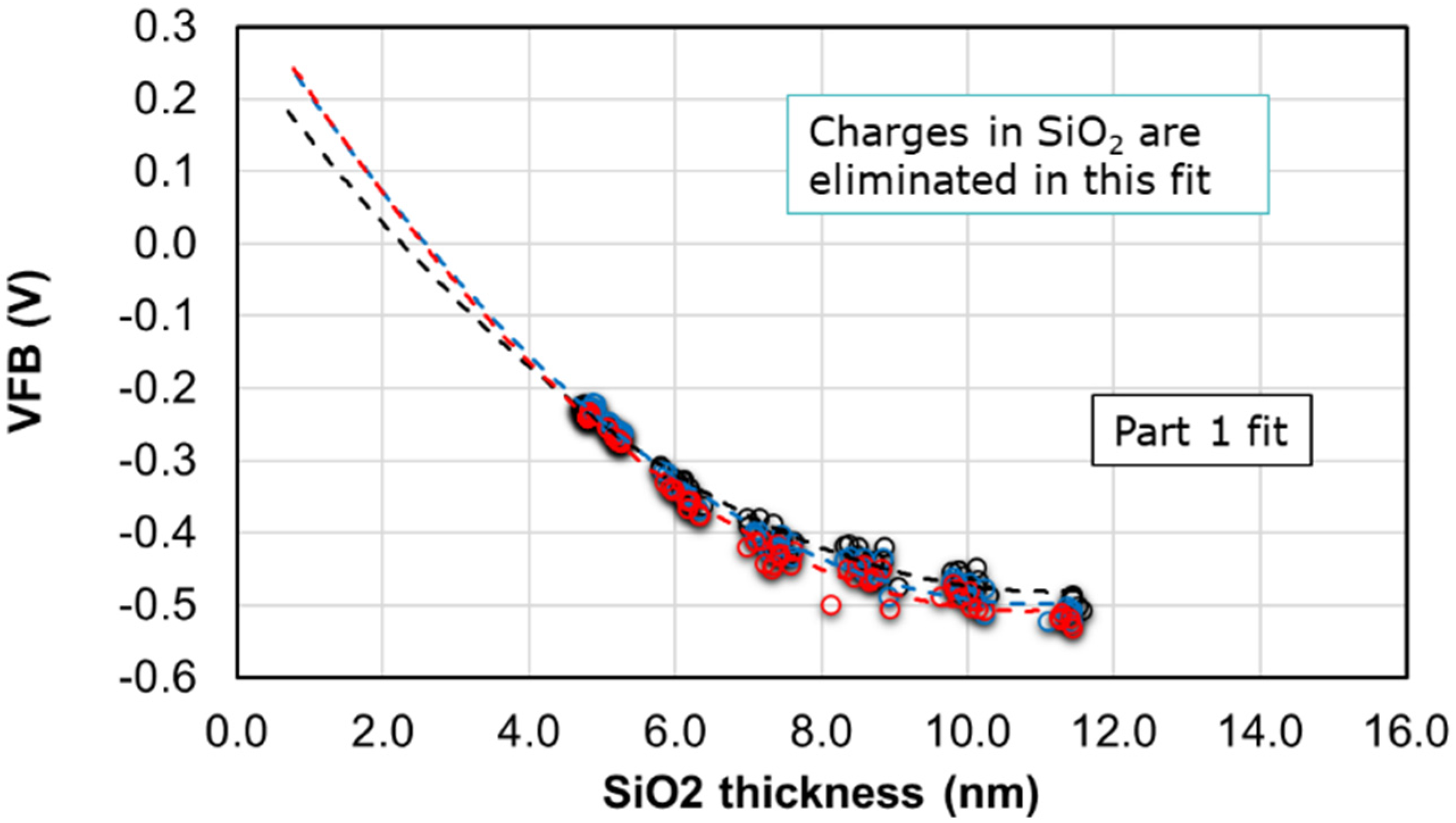

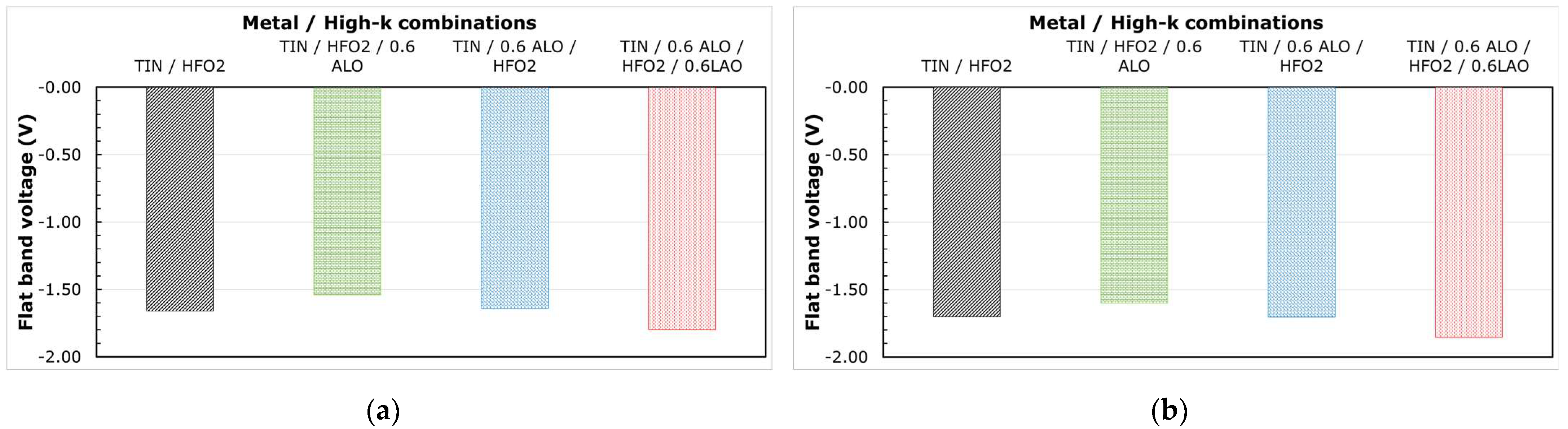

2.1. Work Function Extraction Methodology

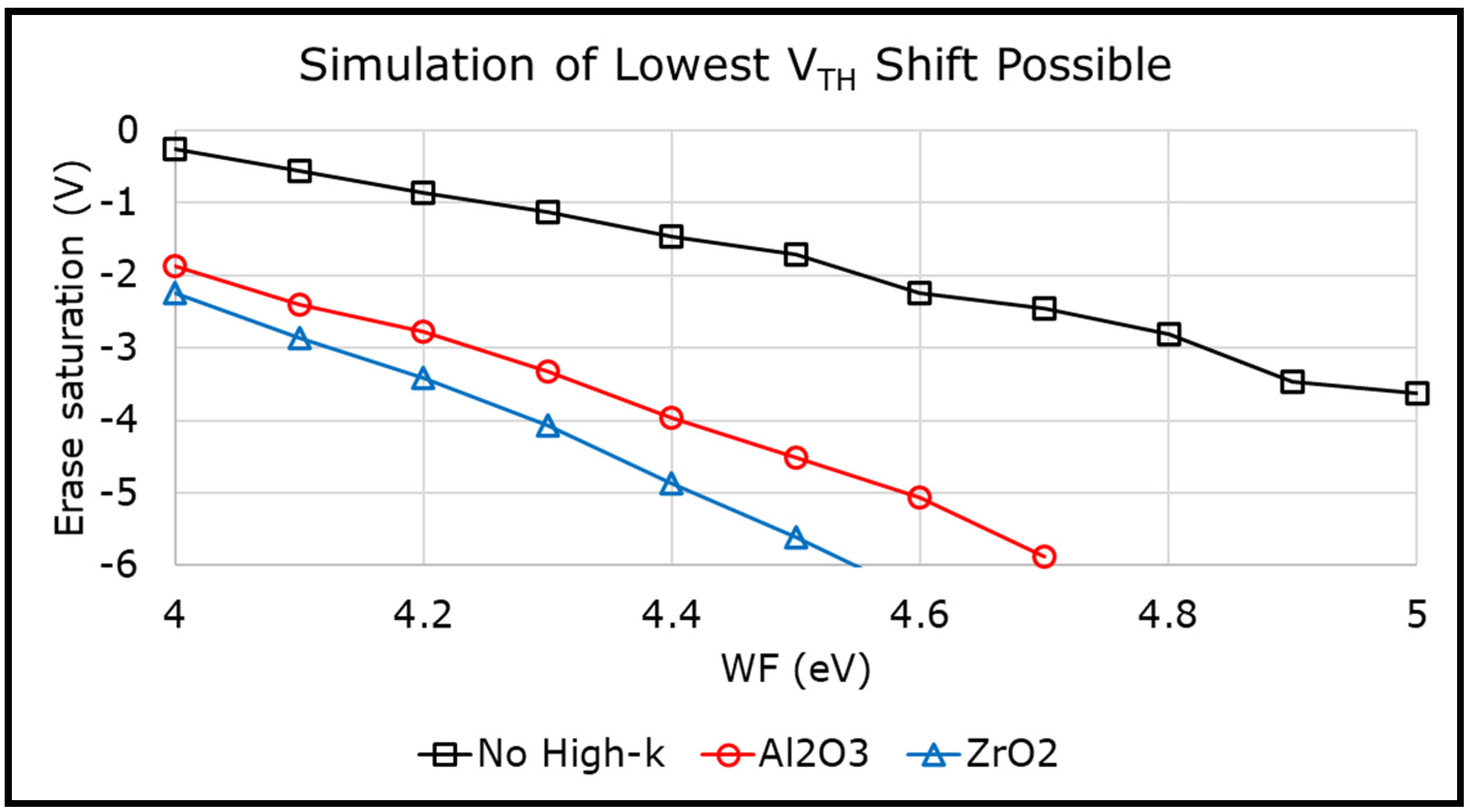

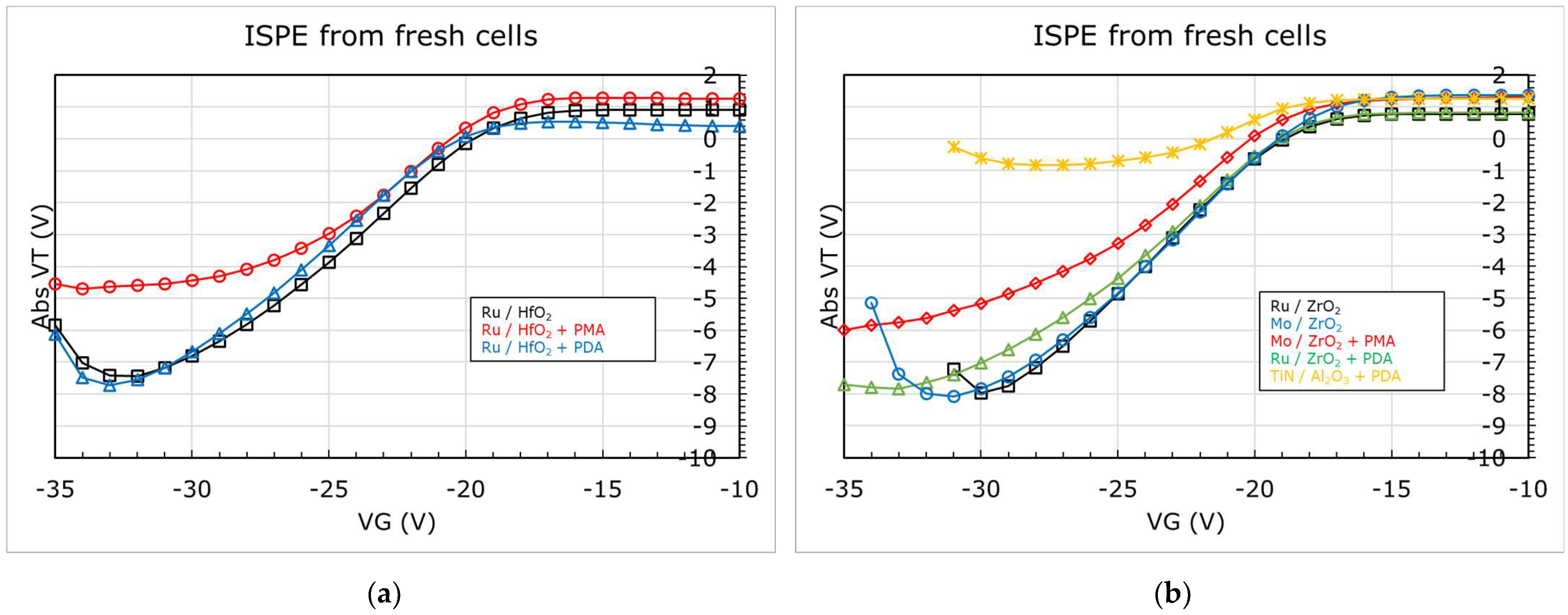

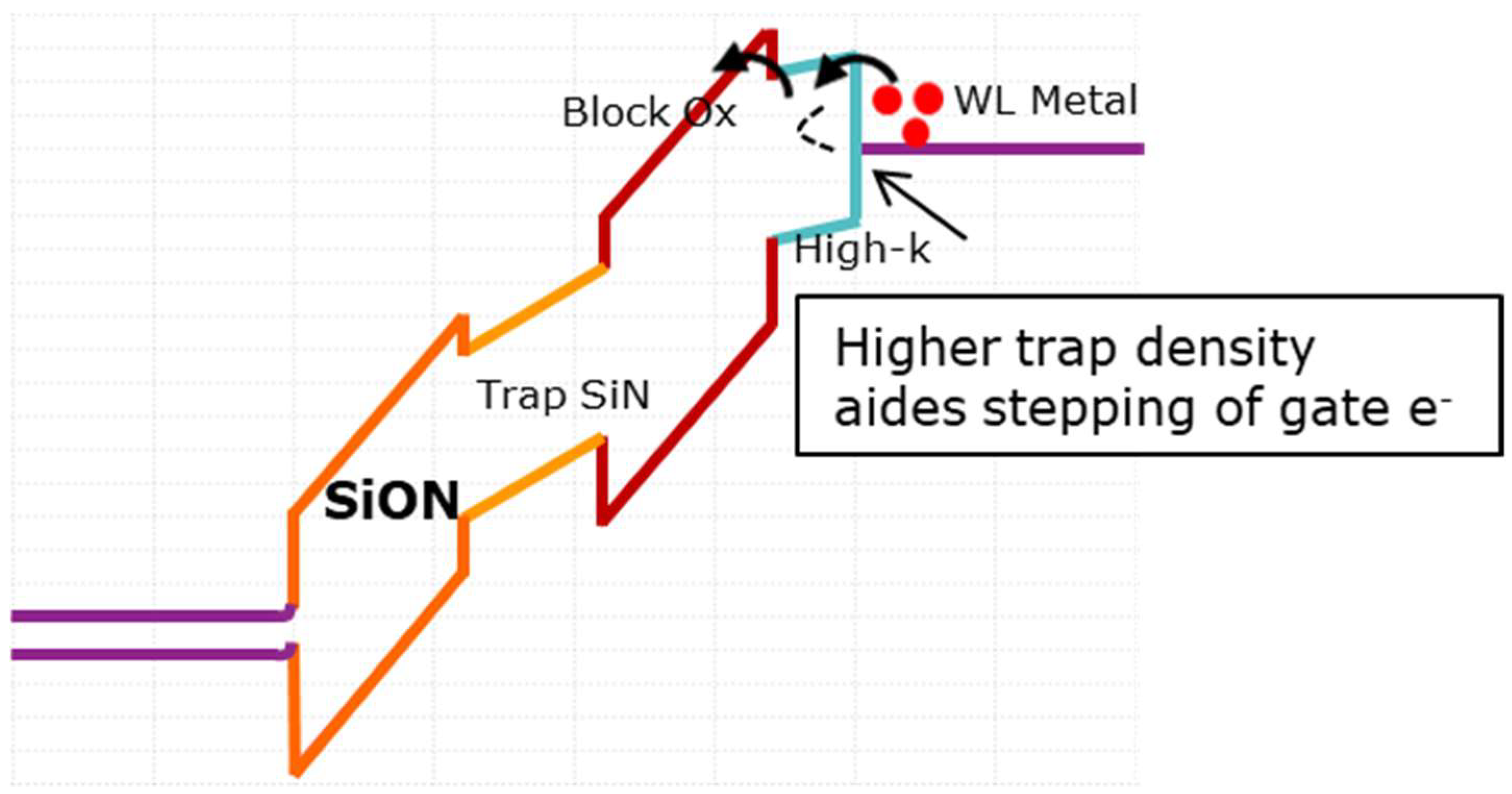

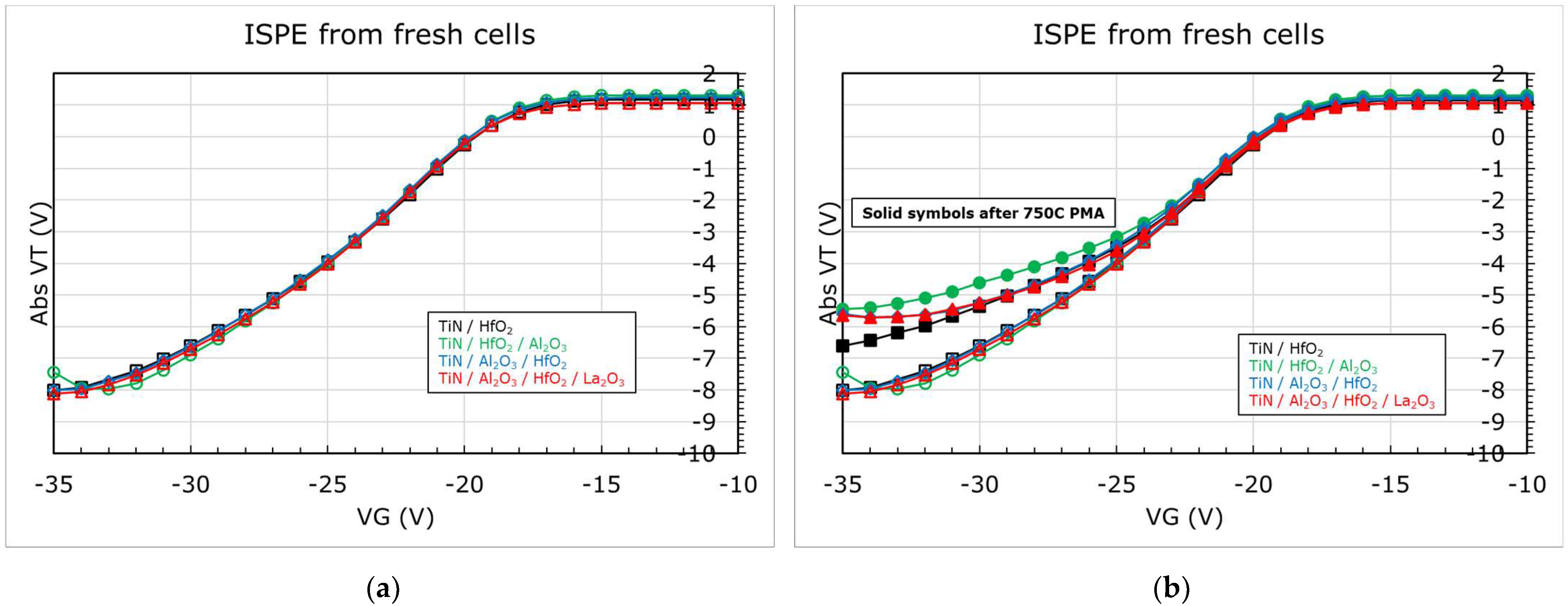

2.2. NAND Flash Erase Analysis

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Appendix A

References

- Parat, K.; Goda, A. Scaling Trends in NAND Flash. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 2.1.1–2.1.4. [Google Scholar] [CrossRef]

- Tanaka, H.; Kido, M.; Yahashi, K.; Oomura, M.; Katsumata, R.; Kito, M.; Fukuzumi, Y.; Sato, M.; Nagata, Y.; Matsuoka, Y.; et al. Bit Cost Scalable Technology with Punch and Plug Process for Ultra High Density Flash Memory. In Proceedings of the IEEE Symposium on VLSI Technology, Kyoto, Japan, 12–14 June 2007; pp. 14–15. [Google Scholar] [CrossRef]

- Breuil, L.; El Hajjam, G.K.; Ramesh, S.; Ajaykumar, A.; Arreghini, A.; Zhang, L.; Sebaai, F.; Nyns, L.; Raymaekers, T.; Rosmeulen, M.; et al. Integration of Ruthenium-based Wordline in a 3-D NAND Memory Devices. In Proceedings of the IEEE International Memory Workshop (IMW), Dresden, Germany, 17–20 May 2020; pp. 1–4. [Google Scholar] [CrossRef]

- Jeon, S.; Han, J.; Lee, J.; Choi, S.; Hwang, H.; Kim, C. High Work-Function Metal Gate and High-kappaDielectrics for Charge Trap Flash Memory Device Applications. IEEE Trans. Electron Devices 2005, 52, 2654–2659. [Google Scholar] [CrossRef]

- Tan, C.-L.; Lavizzari, S.; Blomme, P.; Breuil, L.; Vecchio, G.; Sebaai, F.; Paraschiv, V.; Tao, Z.; Schepers, B.; Nyns, L.; et al. In Depth Analysis of 3D NAND Enablers in Gate Stack Integration and Demonstration in 3D Devices. In Proceedings of the IEEE International Memory Workshop (IMW), Monterey, CA, USA, 14–17 May 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Arreghini, A.; Van den Bosch, G.; Kar, G.S.; Van Houdt, J. Ultimate Scaling Projection of Cylindrical 3D SONOS Devices. In Proceedings of the 2012 4th IEEE International Memory Workshop, Milan, Italy, 20–23 May 2012; pp. 1–4. [Google Scholar] [CrossRef]

- Charbonnier, M.; Mitard, J.; Leroux, C.; Ghibaudo, G.; Cosnier, V.; Besson, P.; Martin, F.; Reimbold, G. Reliable extraction of metal gate work function by combining two electrical characterization methods. In Proceedings of the ESSDERC 2007—37th European Solid State Device Research Conference, Munich, Germany, 11–13 September 2007; pp. 275–278. [Google Scholar] [CrossRef]

- O’Sullivan, B.; Kaushik, V.; Ragnarsson, L.-A.; Onsia, B.; Van Hoornick, N.; Rohr, E.; DeGendt, S.; Heyns, M. Device performance of transistors with high-/spl kappa/ dielectrics using cross-wafer-scaled interface-layer thickness. IEEE Electron Device Lett. 2006, 27, 546–548. [Google Scholar] [CrossRef]

- Akiyama, K.; Wang, W.; Mizubayashi, W.; Ikeda, M.; Ota, H.; Nabatame, T.; Toriumi, A. Roles of oxygen vacancy in HfO2/ultra-thin SiO2 gate stacks—Comprehensive understanding of VFB roll-off -. In Proceedings of the 2008 Symposium on VLSI Technology, Honolulu, HI, USA, 17–19 June 2008; pp. 80–81. [Google Scholar] [CrossRef]

- Kadoshima, M.; Ogawa, A.; Ota, H.; Ikeda, M.; Takahashi, M.; Satake, H.; Nabatame, T.; Toriumi, A. Two Different Mechanisms for Determining Effective Work Function (fm,eff) on High-k—Physical Understanding and Wider Tunability of fm,eff. In Digest of Technical Papers, Proceedings of the 2006 Symposium on VLSI Technology, Honolulu, HI, USA, 13–15 June 2006; IEEE: Piscataway, NJ, USA, 2006; pp. 180–181. [Google Scholar] [CrossRef]

- Kamimuta, Y.; Iwamoto, K.; Nunoshige, Y.; Hirano, A.; Mizubayashi, W.; Watanabe, Y.; Migita, S.; Ogawa, A.; Ota, H.; Nabatame, T.; et al. Comprehensive Study of VFB Shift in High-k CMOS—Dipole Formation, Fermi-level Pinning and Oxygen Vacancy Effect. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; pp. 341–344. [Google Scholar] [CrossRef]

- Kornblum, L.; Rothschild, J.A.; Kauffmann, Y.; Brener, R.; Eizenberg, M. Band offsets and Fermi level pinning at metal-Al2O3 interfaces. Phys. Rev. B 2011, 84, 15. [Google Scholar] [CrossRef]

- Mönch, W. Metal-semiconductor contacts: Electronic properties. Surf. Sci. 1994, 299–300, 928–944. [Google Scholar] [CrossRef]

- Yeo, Y.-C.; King, T.-J.; Hu, C. Metal-dielectric band alignment and its implications for metal gate complementary metal-oxide-semiconductor technology. J. Appl. Phys. 2002, 92, 7266–7271. [Google Scholar] [CrossRef] [Green Version]

- Wen, H.-C.; Majhi, P.; Choi, K.; Park, C.; Alshareef, H.N.; Harris, H.R.; Luan, H.; Niimi, H.; Park, H.-B.; Bersuker, G.; et al. Decoupling the Fermi-level pinning effect and intrinsic limitations on p-type effective work function metal electrodes. Microelectron. Eng. 2008, 85, 2–8. [Google Scholar] [CrossRef]

- Akasaka, Y.; Nakamura, G.; Shiraishi, K.; Umezawa, N.; Yamabe, K.; Ogawa, O.; Lee, M.; Amiaka, T.; Kasuya, T.; Watanabe, H.; et al. Modified Oxygen Vacancy Induced Fermi Level Pinning Model Extendable to P-Metal Pinning. Jpn. J. Appl. Phys. 2006, 45, L1289–L1292. [Google Scholar] [CrossRef]

- Yang, Z.C.; Huang, A.P.; Zheng, X.H.; Xiao, Z.S.; Liu, X.Y.; Zhang, X.W.; Chu, P.K.; Wang, W.W. Fermi-Level Pinning at Metal/High-k Interface Influenced by Electron State Density of Metal Gate. IEEE Electron Device Lett. 2010, 31, 1101–1103. [Google Scholar] [CrossRef]

- Kita, K.; Toriumi, A. Origin of electric dipoles formed at high-k/SiO2 interface. Appl. Phys. Lett. 2009, 94, 132902. [Google Scholar] [CrossRef]

- Bersuker, G.; Park, C.S.; Wen, H.-C.; Choi, K.; Price, J.; Lysaght, P.; Tseng, H.-H.; Sharia, O.; Demkov, A.; Ryan, J.T.; et al. Origin of the Flatband-Voltage Roll-Off Phenomenon in Metal/High- k Gate Stacks. IEEE Trans. Electron Devices 2010, 57, 2047–2056. [Google Scholar] [CrossRef]

- Iwamoto, K.; Ogawa, A.; Kamimuta, Y.; Watanabe, Y.; Mizubayashi, W.; Migita, S.; Morita, Y.; Takahashi, M.; Ito, H.; Ota, H.; et al. Re-examination of Flat-Band Voltage Shift for High-k MOS Devices. In Proceedings of the 2007 IEEE Symposium on VLSI Technology, Kyoto, Japan, 12–14 June 2007; pp. 70–71. [Google Scholar] [CrossRef]

- Charbonnier, M.; Leroux, C.; Cosnier, V.; Besson, P.; Martinez, E.; Benedetto, N.; Licitra, C.; Rochat, N.; Gaumer, C.; Kaja, K.; et al. Measurement of Dipoles/Roll-Off /Work Functions by Coupling CV and IPE and Study of Their Dependence on Fabrication Process. IEEE Trans. Electron Devices 2010, 57, 1809–1819. [Google Scholar] [CrossRef]

- Padovani, A.; Kaczer, B.; Pesic, M.; Belmonte, A.; Popovici, M.; Nyns, L.; Linten, D.; Afanas’Ev, V.V.; Shlyakhov, I.; Lee, Y.; et al. A Sensitivity Map-Based Approach to Profile Defects in MIM Capacitors From I-V, C-V, and G-V Measurements. IEEE Trans. Electron Devices 2019, 66, 1892–1898. [Google Scholar] [CrossRef]

- Kaushik, V.; O’Sullivan, B.; Pourtois, G.; Van Hoornick, N.; Delabie, A.; Van Elshocht, S.; Deweerd, W.; Schram, T.; Pantisano, L.; Rohr, E.; et al. Estimation of fixed charge densities in hafnium-silicate gate dielectrics. IEEE Trans. Electron Devices 2006, 53, 2627–2633. [Google Scholar] [CrossRef]

- Jha, R.; Gurganos, J.; Kim, Y.; Choi, R.; Lee, J.; Misra, V. A Capacitance-Based Methodology for Work Function Extraction of Metals on High-kappa. IEEE Electron Device Lett. 2004, 25, 420–423. [Google Scholar] [CrossRef]

- Hauser, J.R. North Carolina State Umiversity’s CVC. Computer Analysis Software, 1999. [Google Scholar]

- Park, J.-Y.; Yun, D.-H.; Kim, S.-Y.; Choi, Y.-K. Suppression of Self-Heating Effects in 3-D V-NAND Flash Memory Using a Plugged Pillar-Shaped Heat Sink. IEEE Electron Device Lett. 2019, 40, 212–215. [Google Scholar] [CrossRef]

- Calzolari, A.; Catellani, A. Controlling the TiN Electrode Work Function at the Atomistic Level: A First Principles Investigation. IEEE Access 2020, 8, 156308–156313. [Google Scholar] [CrossRef]

- Wen, H.-C.; Choi, R.; Brown, G.; BosckeBoscke, T.; Matthews, K.; Harris, H.; Choi, K.; Alshareef, H.N.; Luan, H.; Bersuker, G.; et al. Comparison of effective work function extraction methods using capacitance and current measurement techniques. IEEE Electron Device Lett. 2006, 27, 598–601. [Google Scholar] [CrossRef]

- Park, K.J.; Doub, J.M.; Gougousi, T.; Parsons, G. Microcontact patterning of ruthenium gate electrodes by selective area atomic layer deposition. Appl. Phys. Lett. 2005, 86, 051903. [Google Scholar] [CrossRef]

- Pantisano, L.; Schram, T.; Li, Z.; Lisoni, J.G.; Pourtois, G.; De Gendt, S.; Brunco, D.P.; Akheyar, A.; Afanas’Ev, V.V.; Shamuilia, S.; et al. Ruthenium gate electrodes on SiO2 and HfO2: Sensitivity to hydrogen and oxygen ambients. Appl. Phys. Lett. 2006, 88, 243514. [Google Scholar] [CrossRef]

- Afanas’Ev, V.V.; Stesmans, A. Internal photoemission at interfaces of high-κ insulators with semiconductors and metals. J. Appl. Phys. 2007, 102, 81301. [Google Scholar] [CrossRef]

- Ramesh, S.; Ajaykumar, A.; Bastos, J.; Breuil, L.; Arreghini, A.; Nyns, L.; Soulié, J.-P.; Ragnarsson, L.-Å.; Schleicher, F.; Jossart, N.; et al. Erase Behavior of Charge Trap Flash Memory Devices using High-k Dielectric as Blocking Oxide Liner. In Proceedings of the IEEE Semiconductor Interface Specialists Conference, San Diego, CA, USA, 6–8 December 2020. [Google Scholar]

- Chou, A.I.; Lai, K.; Kumar, K.; Chowdhury, P.; Lee, J.C. Modeling of stress-induced leakage current in ultrathin oxides with the trap-assisted tunneling mechanism. Appl. Phys. Lett. 1997, 70, 3407–3409. [Google Scholar] [CrossRef]

- Iwamoto, K.; Kamimuta, Y.; Ogawa, A.; Watanabe, Y.; Migita, S.; Mizubayashi, W.; Morita, Y.; Takahashi, M.; Ota, H.; Nabatame, T.; et al. Experimental evidence for the flatband voltage shift of high-k metal-oxide-semiconductor devices due to the dipole formation at the high-k∕SiO2 interface. Appl. Phys. Lett. 2008, 92, 132907. [Google Scholar] [CrossRef]

- Suarez-Segovia, C.; Caubet, P.; Joseph, V.; Gourhant, O.; Romano, G.; Domengie, F.; Ghibaudo, G. Effective Work Function Shift Induced by TiN Sacrificial Metal Gates as a Function of Their Thickness and Composition in 14 nm NMOS devices. In Proceedings of the International Conference on Solid State Devices and Materials, Ibaraki, Japan, 8–11 September 2014. [Google Scholar] [CrossRef] [Green Version]

- Bersch, E.; Di, M.; Consiglio, S.; Clark, R.D.; Leusink, G.J.; Diebold, A.C. Complete band offset characterization of the HfO2/SiO2/Si stack using charge corrected x-ray photoelectron spectroscopy. J. Appl. Phys. 2010, 107, 043702. [Google Scholar] [CrossRef]

- Wang, X.; Han, K.; Wang, W.; Chen, S.; Ma, X.; Chen, D.; Zhang, J.; Du, J.; Xiong, Y.; Huang, A. Physical origin of dipole formation at high-k/SiO2 interface in metal-oxide-semiconductor device with high-k/metal gate structure. Appl. Phys. Lett. 2010, 96, 152907. [Google Scholar] [CrossRef]

- Sivasubramani, P.; Boscke, T.S.; Huang, J.; Young, C.D.; Kirsch, P.D.; Krishnan, S.A.; Quevedo-Lopez, M.A.; Govindarajan, S.; Ju, B.S.; Harris, H.R.; et al. Dipole Moment Model Explaining nFET Vt Tuning Utilizing La, Sc, Er, and Sr Doped HfSiON Dielectrics. In Proceedings of the 2007 IEEE Symposium on VLSI Technology, Kyoto, Japan, 12–14 June 2007; pp. 68–69. [Google Scholar] [CrossRef]

- Zheng, X.H.; Huang, A.P.; Xiao, Z.S.; Yang, Z.C.; Wang, M.; Zhang, X.W.; Wang, W.W.; Chu, P.K. Origin of flat-band voltage sharp roll-off in metal gate/high-k/ultrathin- SiO2/Si p-channel metal-oxide-semiconductor stacks. Appl. Phys. Lett. 2010, 97, 132908. [Google Scholar] [CrossRef]

- Sharia, O.; Demkov, A.A.; Bersuker, G.; Lee, B.H. Theoretical study of the insulator/insulator interface: Band alignment at theSiO2∕HfO2junction. Phys. Rev. B 2007, 75, 035306. [Google Scholar] [CrossRef]

- Franco, J.; Wu, Z.; Rzepa, G.; Vandooren, A.; Arimura, H.; Claes, D.; Horiguchi, N.; Collaert, N.; Linten, D.; Grasser, T.; et al. Low Thermal Budget Dual-Dipole Gate Stacks Engineered for Sufficient BTI Reliability in Novel Integration Schemes. In Proceedings of the 2019 Electron Devices Technology and Manufacturing Conference (EDTM), Singapore, 12–15 March 2019; pp. 215–217. [Google Scholar] [CrossRef]

- Arimura, H.; Sioncke, S.; Cott, D.; Mitard, J.; Conard, T.; Vanherle, W.; Loo, R.; Favia, P.; Bender, H.; Meersschaut, J.; et al. Ge nFET with high electron mobility and superior PBTI reliability enabled by monolayer-Si surface passivation and La-induced interface dipole formation. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 21.6.1–21.6.4. [Google Scholar] [CrossRef]

- Choi, K.; Wen, H.-C.; Bersuker, G.; Harris, R.; Lee, B.H. Mechanism of flatband voltage roll-off studied with Al2O3 film deposited on terraced oxide. Appl. Phys. Lett. 2008, 93, 133506. [Google Scholar] [CrossRef]

- Yamamoto, Y.; Kita, K.; Kyuno, K.; Toriumi, A. Study of La-Induced Flat Band Voltage Shift in Metal/HfLaOx/SiO2/Si Capacitors. Jpn. J. Appl. Phys. 2007, 46, 7251–7255. [Google Scholar] [CrossRef]

- Arimura, H.; Cott, D.; Loo, R.; Vanherle, W.; Xie, Q.; Tang, F.; Jiang, X.; Franco, J.; Sioncke, S.; Ragnarsson, L.-Å.; et al. Si-passivated Ge nMOS gate stack with low Dit and dipole-induced superior PBTI reliability using 3D-compatible ALD caps and high-pressure anneal. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 33.4.1–33.4.4. [Google Scholar] [CrossRef]

- Vais, A.; Franco, J.; Lin, D.; Putcha, V.; Sioncke, S.; Mocuta, A.; Collaert, N.; Thean, A.; De Meyer, K. On the distribution of oxide defect levels in Al2O3 and HfO2 high-k dielectrics deposited on InGaAs metal-oxide-semiconductor devices studied by capacitance-voltage hysteresis. J. Appl. Phys. 2017, 121, 144504. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ramesh, S.; Ajaykumar, A.; Ragnarsson, L.-Å.; Breuil, L.; El Hajjam, G.K.; Kaczer, B.; Belmonte, A.; Nyns, L.; Soulié, J.-P.; Van den bosch, G.; et al. Understanding the Origin of Metal Gate Work Function Shift and Its Impact on Erase Performance in 3D NAND Flash Memories. Micromachines 2021, 12, 1084. https://doi.org/10.3390/mi12091084

Ramesh S, Ajaykumar A, Ragnarsson L-Å, Breuil L, El Hajjam GK, Kaczer B, Belmonte A, Nyns L, Soulié J-P, Van den bosch G, et al. Understanding the Origin of Metal Gate Work Function Shift and Its Impact on Erase Performance in 3D NAND Flash Memories. Micromachines. 2021; 12(9):1084. https://doi.org/10.3390/mi12091084

Chicago/Turabian StyleRamesh, Sivaramakrishnan, Arjun Ajaykumar, Lars-Åke Ragnarsson, Laurent Breuil, Gabriel Khalil El Hajjam, Ben Kaczer, Attilio Belmonte, Laura Nyns, Jean-Philippe Soulié, Geert Van den bosch, and et al. 2021. "Understanding the Origin of Metal Gate Work Function Shift and Its Impact on Erase Performance in 3D NAND Flash Memories" Micromachines 12, no. 9: 1084. https://doi.org/10.3390/mi12091084

APA StyleRamesh, S., Ajaykumar, A., Ragnarsson, L.-Å., Breuil, L., El Hajjam, G. K., Kaczer, B., Belmonte, A., Nyns, L., Soulié, J.-P., Van den bosch, G., & Rosmeulen, M. (2021). Understanding the Origin of Metal Gate Work Function Shift and Its Impact on Erase Performance in 3D NAND Flash Memories. Micromachines, 12(9), 1084. https://doi.org/10.3390/mi12091084