1. Introduction

After a decade of rapid technological developments, 3D NAND flash memory has been widely utilized in various kinds of storage applications, especially in file memory-related products such as laptops and data centers. Due to the fact of its ultra-high bit density, lower bit cost, and better performances as well as reliabilities, 3D NAND flash is substituting its 2D counterpart step by step. For charge-trap (CT) 3D NAND flash memory, the endurance can largely be improved because the effects of the tunneling layer degradations are weak, and the program time can be faster because the effects of inter-cell interference (ICI) are well suppressed with larger cell-to-cell space. Recently, a 3D NAND with more than 170 layers was announced by the NAND flash makers [

1,

2]; more impressively, quadruple-level-cell (QLC, 4 bits/cell), penta-level-cell (PLC, 5 bits/cell), and even hexa-level-cell (HLC, 6 bits/cell) operation modes have been demonstrated [

3,

4]. All these fundamental developments as well as design-technology co-optimizations (DTCO) will drive 3D NAND flash to the mainstream non-volatile memories in the near future [

5].

In NAND flash-based memory systems, a major issue that affects both the performance and reliability is the temperature. In conventional 2D NAND flash with a floating gate (FG) structure, as operation temperature increases, the raw bit error rate (RBER) will increase, and the degradation will become more serious. Therefore, on the one hand, the temperature monitor and controller are necessary in NAND flash-based memory systems with robust reliabilities, and on the other hand, the temperature dependence can be utilized as an accelerator to build a lifetime prediction model in a short-time using the Arrhenius model [

6], which shows high accuracy in 2D FG NAND flash. However, due to the special structures of cells and the arrays in CT 3D NAND flash, the failure mechanisms are much more complex, and the temperature effects are quite different. This can explain why the conventional lifetime prediction model loses accuracy when it is applied to 3D NAND flashes [

7]. Accordingly, comprehensive understandings of the temperature impacts on a 3D NAND flash are strongly required.

In this paper, systematic characterizations of the temperature dependences have been conducted on CT-type 3D TLC NAND flash memories from −30~70 °C, with focus on the RBER modulations in P/E degradations and read disturbs. By using the FPGA-based raw NAND chip tester, it was experimentally observed that the program/erase time and the RBER in the P/E cycling and read disturbs were highly dependent on the temperature. However, temperature had negligible impacts on the cells’ degradation, indicating that the CT 3D NAND is suitable for work at high temperatures with no need to worry about accelerated degradations.

The main contributions of this paper are as follows:

We characterized the P/E cycling in CT 3D NAND flash memory from −30~70 °C using the raw NAND chip tester. An effective TCPT model was proposed to simulate the program time changes by the P/E cycles and the temperature;

We characterized the cross-temperature measurements to study the temperature-dependent degradations, indicating that high-temperature operations will not accelerate the degradation of the memory cells;

We characterized the measurements of temperature-dependent read disturbs. It showed that read disturb degrades at cold temperature, but it helps to recover a part of RBER at high temperatures. The underlying origins are analyzed in detail.

The rest of the paper is organized as follows:

Section 2 introduces the background and related work;

Section 3 presents the evaluation setup;

Section 4 describes the measured results of P/E cycling;

Section 5 shows the temperature-dependent read disturbs; finally,

Section 6 concludes this work.

2. Background and Related Work

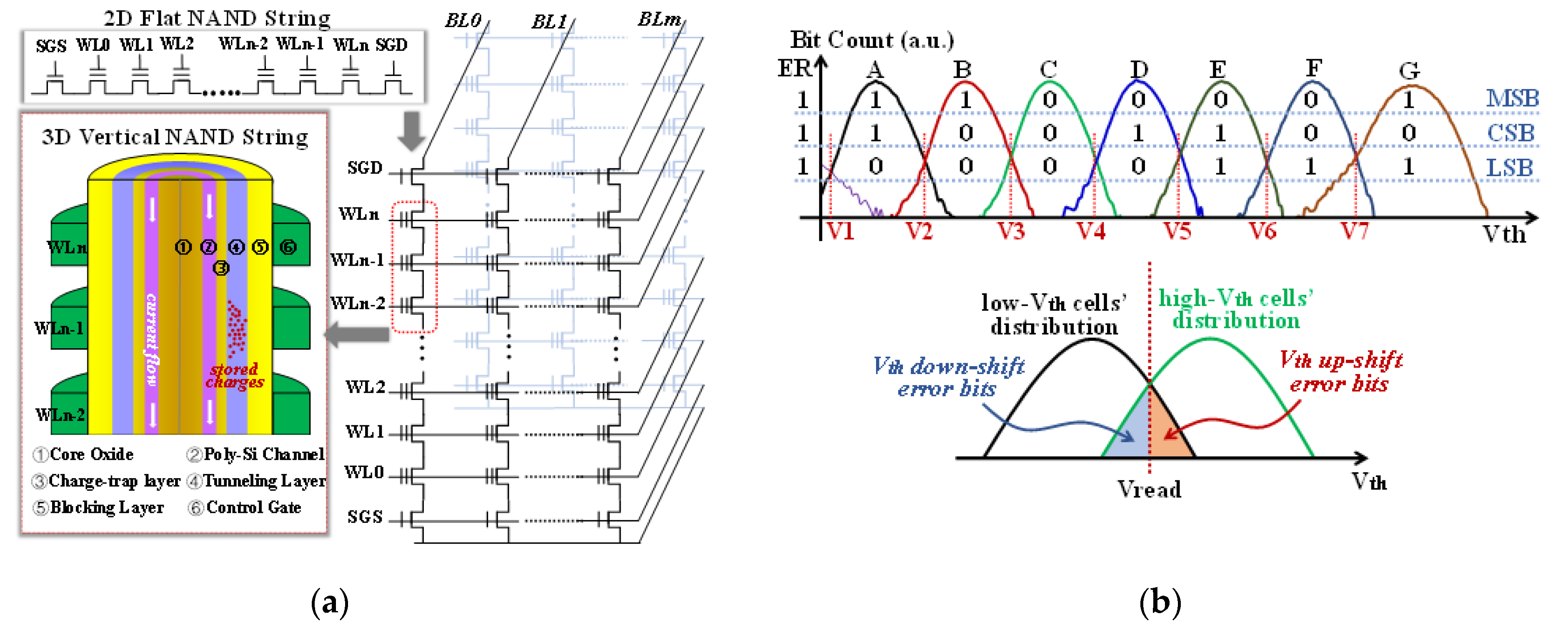

In 2D NAND flash memory, memory cells use FG to store electrons. However, as scaling the cell size to sub-1X nm, serious issues occur from the large cell-to-cell interference and variations in stored charges in FG. It turns out to be extremely difficult to increase the bit density while also guaranteeing the reliability. Different from 2D NAND flash, 3D NAND flash utilizes stacked storage layers to increase the bit density, which settles the problem of flat area scaling and, thus, the key issue turns to be how many layers can be stacked. The comparisons between the two different NAND flash structures are shown in

Figure 1a. In a 3D CT NAND flash cell, besides the core oxide and poly-Si channel, the gate stack contains an oxide tunneling layer, silicon–nitride CT layer, oxide blocking layer, and a control gate (CG).

In NAND flash operations, there includes single-level-cell (SLC, 1 bit/cell), multiple-level-cell (MLC, 2 bits/cell), triple-level-cell (TLC, 3 bits/cell), QLC, PLC, and HLC. For 2D NAND flash, SLC and MLC modes are adopted in accordance with the products’ requirements; while for a 3D NAND flash, TLC mode has been widely used because of the well-tuned reliability and high cost–performance ratio. A typical threshold voltage (

) distribution of TLC in a 3D CT NAND flash is shown in

Figure 1b, wherein seven program states from A to G levels can be well distinguished. Only a part of the erase state (ER) can be observed due to the negative

values. Each word-line (WL) consists of three pages, the most significant bit (MSB) page, the central significant bit (CSB) page, and the least significant bit page (LSB). When reading the data from the chip, error bits occur at the overlapping regions between the neighbor states, such as A(B) to B(A) error bits when reading the CSB page at V2 level. Thus, suppressing overlapping regions or optimizing reading voltages are challenges to designing highly reliable NAND flash memory. In addition, for a 3D CT NAND flash, one special concern is the shared common CT layer between neighboring cells.

This makes the reliability mechanisms more complex because the spatial redistributions of stored charges will seriously affect the data retention and read disturbs [

8]. It was also reported that the P/E cycling stress affects the charge redistributions more seriously [

9]. In other words, in a 2D FG NAND flash, the failure mechanism is simple, and the temperature effects can be monitored, while for a 3D CT NAND flash, the special cell structure makes the failure mechanisms complex and previous temperature-related models are no longer suitable. In the following, several related works are briefly described.

The 3D NAND flash was developed more than ten years ago in 2007 [

10], and the first TLC 3D BiCS flash memory with 32 stacked layers was demonstrated by Toshiba in 2015 [

11]. Currently, 174 staking storage layers [

1,

2] as well as HLC operation mode [

4] have been realized and demonstrated. So far, 3D NAND flash has been utilized in many kinds of storage products, especially in smartphones, personal computers, and data centers. To assure the robust reliability and high performance of those products, environmental temperature effects should be well considered, and the effects should be included in the system design. Cai et al. studied MLC NAND flash memory and noticed that the error bits from read disturb were much more likely to take place in cells with lower

values [

12]. Zambelli et al. studied cross-temperature effects in 2D and 3D NAND flash memories and found that there was a large number of fail-bits when the memory was read at a temperature different from that exercised during the program [

13]. Wu et al. found that cell

values had various offset and velocities for different temperate operations, and it can be reduced by shortening the interval time from erase to program during cross-temperature write–read stages [

14]. Kong et al. studied the read disturbs in a 3D CT NAND flash memory, and observed that read disturbs were strongly correlated to retention time and temperatures, and proposed the schemes of precharge-the-storage-layer (PCSL) and thermally-stabilize-the-storage-layer (TSSL) to suppress read disturbs [

8]. Luo et al. observed that the temperature effects increase retention loss speed at a super-linear rate and increases program variations and concluded that prior models for planer 2D NAND flash were not suitable for 3D NAND flash [

15]. Resnati et al. investigated the temperature dependence of cell

, string currents, and random telegraph noise (RTN) distributions in 3D NAND, showing that

distributions will be tight at high temperatures but widened at low temperatures [

16]. In order to minimize the

distribution widening at low temperature and cross-temperature operations, Venkatesan et al. reviewed the 3D NAND technologies and pointed out that polysilicon channel engineering was necessary [

17]. H. Shin et al. investigated the dominant failure mechanisms in 3D NAND after cycling [

18] and drew their conclusions that failure mechanisms in 3D NAND are complex; it is not reliable to use temperature as an accelerator for burn-in tests on the basis of the Arrhenius model [

7].

As a key factor impacting on NAND flash performance and reliability, temperature effects should be well understood. Thus far, in previous reports, temperature effects have been discussed from material-to-device viewpoints or system-level viewpoints, and most of them focused on data retention. It is necessary to have a comprehensive understanding of the temperature effects to conduct device-to-technology co-optimizations (DTCO) and to provide fundamental information for NAND-based applications in a wide temperature range. In this paper, using a high-performance raw NAND chip tester, temperature-dependent characterizations were performed from −30 to 70 °C by focusing on the RBER in P/E cycling, read disturbs, and cross-temperature degradations.

4. P/E Cycling

The NAND flash memory tested in this experiment was a 3D CT TLC NAND flash chip, and the stored data were divided into eight states according to the

of the storage cell. Ideally, the

between adjacent states has a wide read margin, but the

of adjacent states had overlapping regions in practice, and these overlapping regions were the source of error bits. It should be noted, due to the limited memory window for programming in a high-bit density NAND flash, such as TLC mode, overlapping regions do exist as shown in

Figure 1b. The experimental procedure was as follows: firstly, we raised the temperature to the set value; then, we performed 3000 P/E cycles in randomly selected blocks in the chip, and several blocks were characterized to make sure that our results were reliable and stable; finally, the program/erase times of each P/E cycle was recorded in real-time, and the data were exported for analysis.

| Algorithm 1. The process of experiment. |

| Definitions: |

| 1: : the number of P/E cycles, be initialized to 0; |

| 2: T: the temperature of experiment; |

| 3: : the target temperature of experiment; |

| 4: : the number of read cycles, be initialized to 0; |

| 5: MAX : the maximum number of read cycles; |

| Process: |

| 6: if T < or T > then |

| 7: Raise T to ; |

| 8: else |

| 9: Wait 5 min; |

| 10: for ≤ do |

| 11: Execute erase/program operation; |

| 12: + = 1; |

| 13: Collect program time and erase time; |

| 14: if == 1 || % 200 == 0 then |

| 15: Excute the dump operation; |

| 16: Calculate RBER; |

| 17: end if |

| 18: end for |

| 19: Change NAND block; |

| 20: While ≤ MAX do |

| 21: Excute sequential read operation on NAND block; |

| 22: + = 1; |

| 23: if == 1 || % 100 == 0 then |

| 24: Excute the dump operation; |

| 25: Compare and calculate RBER; |

| 26: Collect error classification; |

| 27: end if |

| 28: end while |

| 29: end if |

Figure 2 shows the program time (

) and the erase time (

) when performing P/E cycling at various temperatures. In the case of

, it had a strong dependence on the temperature, but the effects of P/E cycles were negligible. The higher the temperature, the shorter

. However,

depended on both P/E cycles and the temperature as shown in

Figure 2b. For blocks after a certain number of P/E cycles, the higher ambient temperature of the NAND flash memory, the less time it took to execute the program operation. While at the same ambient temperature,

decreased with P/E cycles. Thereby, we propose a temperature-dependent cycling program time (TCPT) model on the basis of following equation:

T,

, and

are the temperature, P/E cycles, and program time, respectively.

and

are the temperature-related functions with fitting parameters

(

n = 1~4). As shown in

Figure 2b, for blocks with higher than 100 P/E cycles, simulation curves agreed well with the experimental data, indicating that the model was effective at predicting the program latency in a wide temperature range. The values of the fitting parameters are listed in

Table 1.

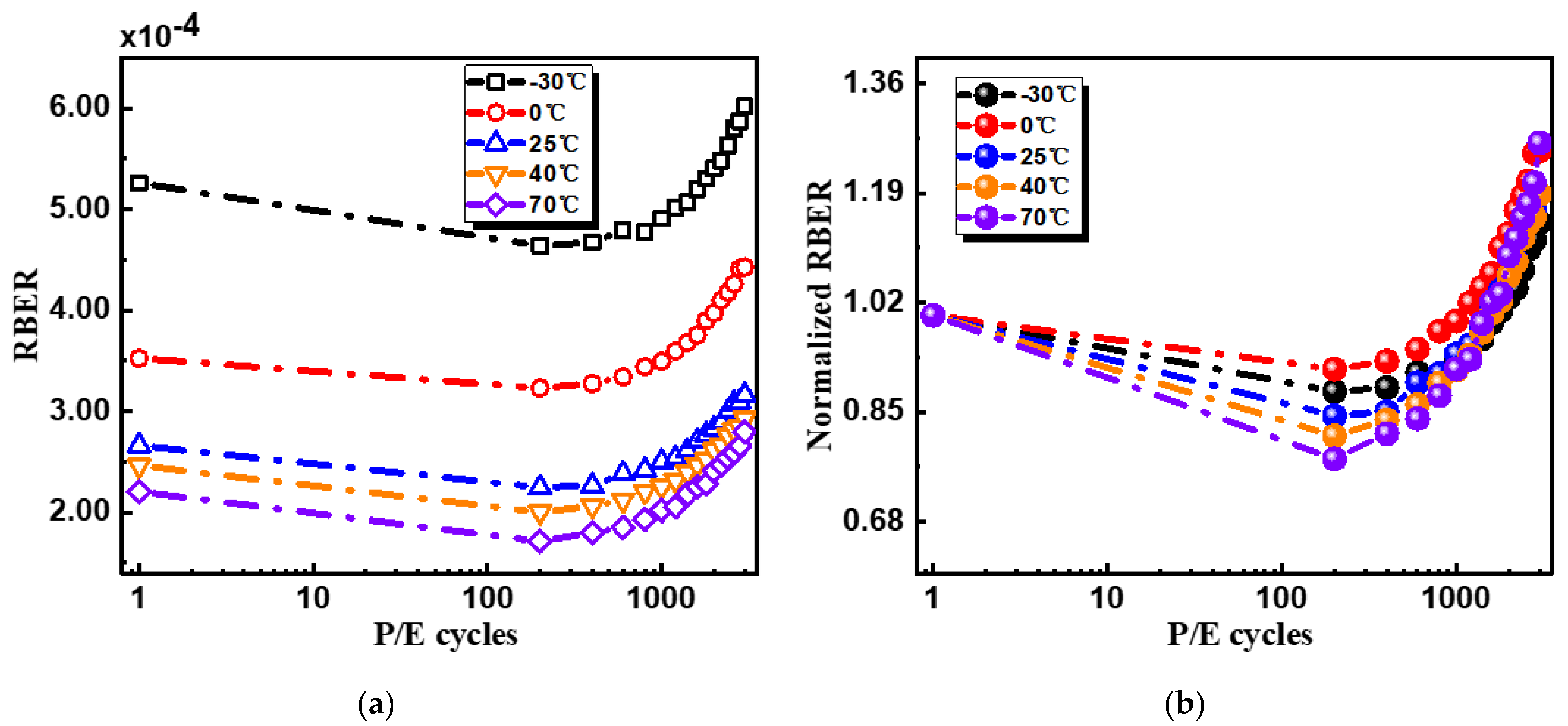

Figure 3 shows the measured RBER when the P/E cycling was performed at different temperatures. No matter what the temperature we choose, RBER has an initially higher value at the fresh state with a decreasing trend in sub-200 P/E cycles, and then it increases during subsequent P/E cycling. Initial higher RBER could possibly come from the unstable initial stage after factory, and the gradually increased RBER can be explained by P/E cycling stress caused cell degradation. During the P/E cycling, defects generated in both the tunneling layer and CT layer and the stability of the NAND cells became worse. The most important thing was that RBER could be suppressed at high temperatures, while it degraded at cold temperatures. These results can be explained by the

distributions’ changes that depended on the temperature. According to the simulated results by Resnati et al. [

16],

distributions are tight at high temperatures (narrower overlap regions cause fewer error bits) but widened at cold temperatures (wider overlap regions cause more error bits). Furthermore, by normalizing the RBER, it was observed that, although RBER increasing at a rate of 70 °C was greater than that at 0 °C, the degradation tendencies did not show a clear temperature dependence in the whole temperature range as shown in

Figure 3b. Considering that different V

th distributions had different sensitivities to the cells’ degradations, it was necessary to use a unified criterion to study the cells’ degradations by cycling stress at different temperatures.

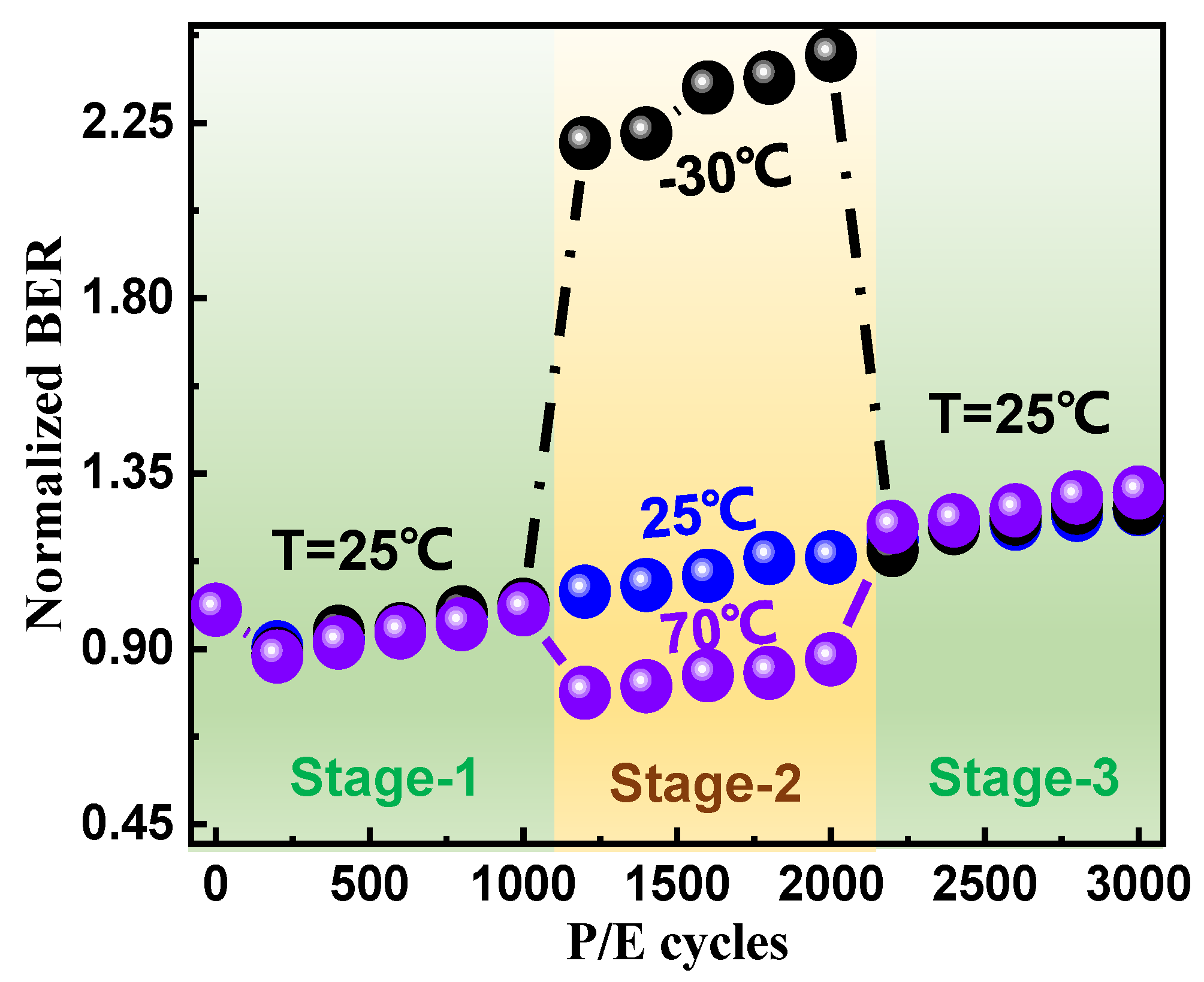

Next, for further evidence, cross-temperature characterizations were conducted to study the temperature effects on P/E cycling stress-related cell degradations. As shown in

Figure 4, we designed the following experiment: firstly, we selected three groups of blocks, and all groups performed 1000 P/E cycles at 25 °C (Stage-1); secondly, 1000 P/E cycles were executed in three groups, −30, 25, and 70 °C (Stage-2); then, the temperatures were lowered to 25 °C, and 1000 P/E cycles were subsequently performed on all groups (Stage-3). Finally, each group operated 3000 read cycles at 25 °C. It can be observed that, no matter what the temperature we chose in stage-2, the RBER degradation tendency trends were almost the same in stage-3 and read cycles after cross-temperature P/E cycles. On the one hand, it can be concluded that thermal experiences (up to 70 °C) have negligible impacts on RBER degradation; on the other hand, the 3D NAND is suitable for high-temperature operations because the RBER is lower and the effects of P/E cycling caused damage will not be accelerated at higher temperatures. It should be noted that no matter what the operation mode we adopted, operations at higher temperatures did cause larger degradations to memory cells such as enhanced interface trap generation. Fortunately, these damages do not cause worse error bits degradation using the same criteria (Stage-3) as shown in

Figure 4.

5. Read Disturb

It is known that high temperature can accelerate the speed of lateral charge migration in the storage layer and modulate the threshold voltage distributions of memory cells [

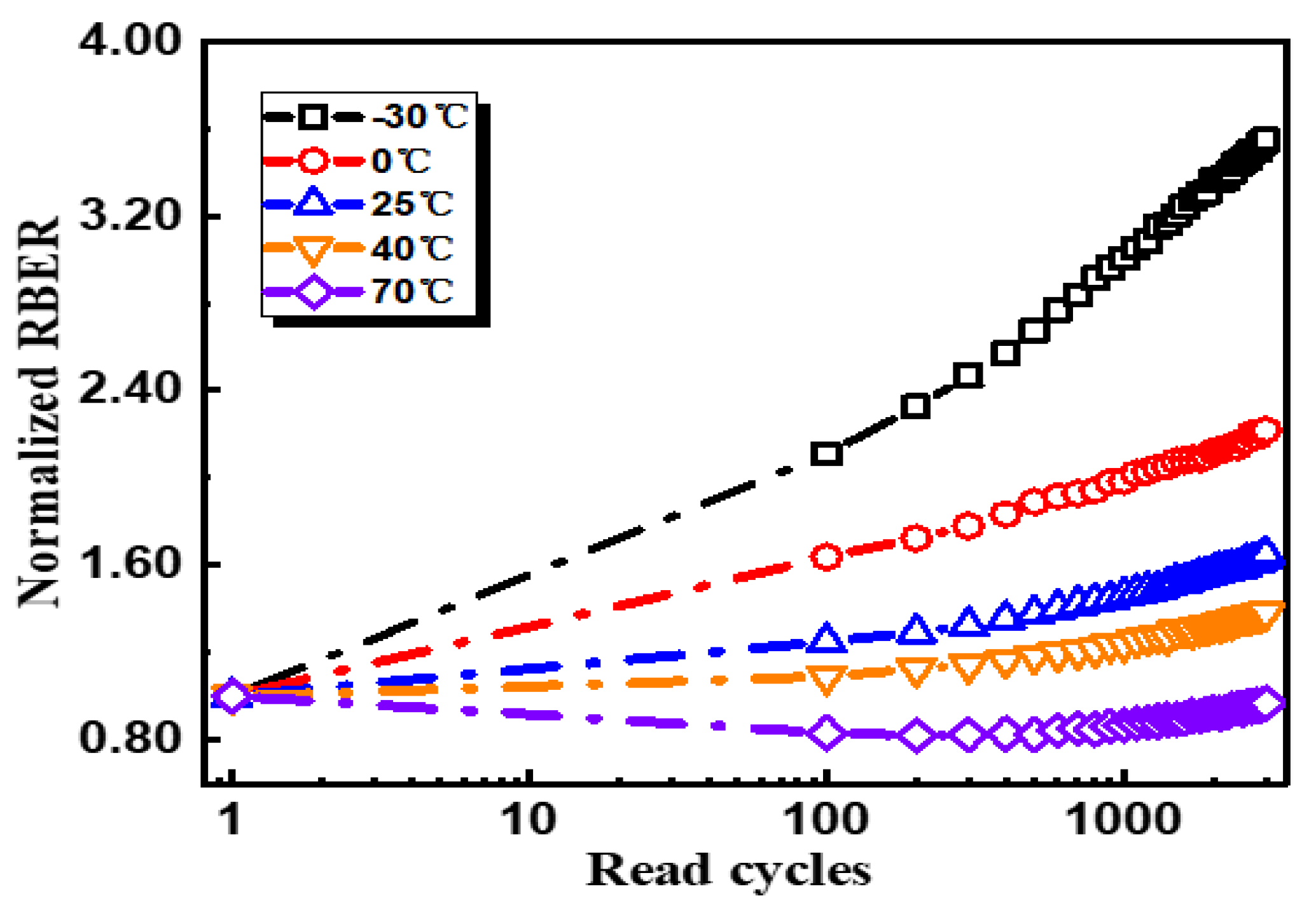

8]. These factors can cause read disturb properties to become more complex at various temperatures. To understand the temperature impacts, we designed the following experiment: firstly, setting the work temperature of the chamber to the target temperature ranging from −30 to 70 °C; then, programming randomized data with subsequent 3000 times read cycling. For detail analysis, data were dumped and recorded every 100 times.

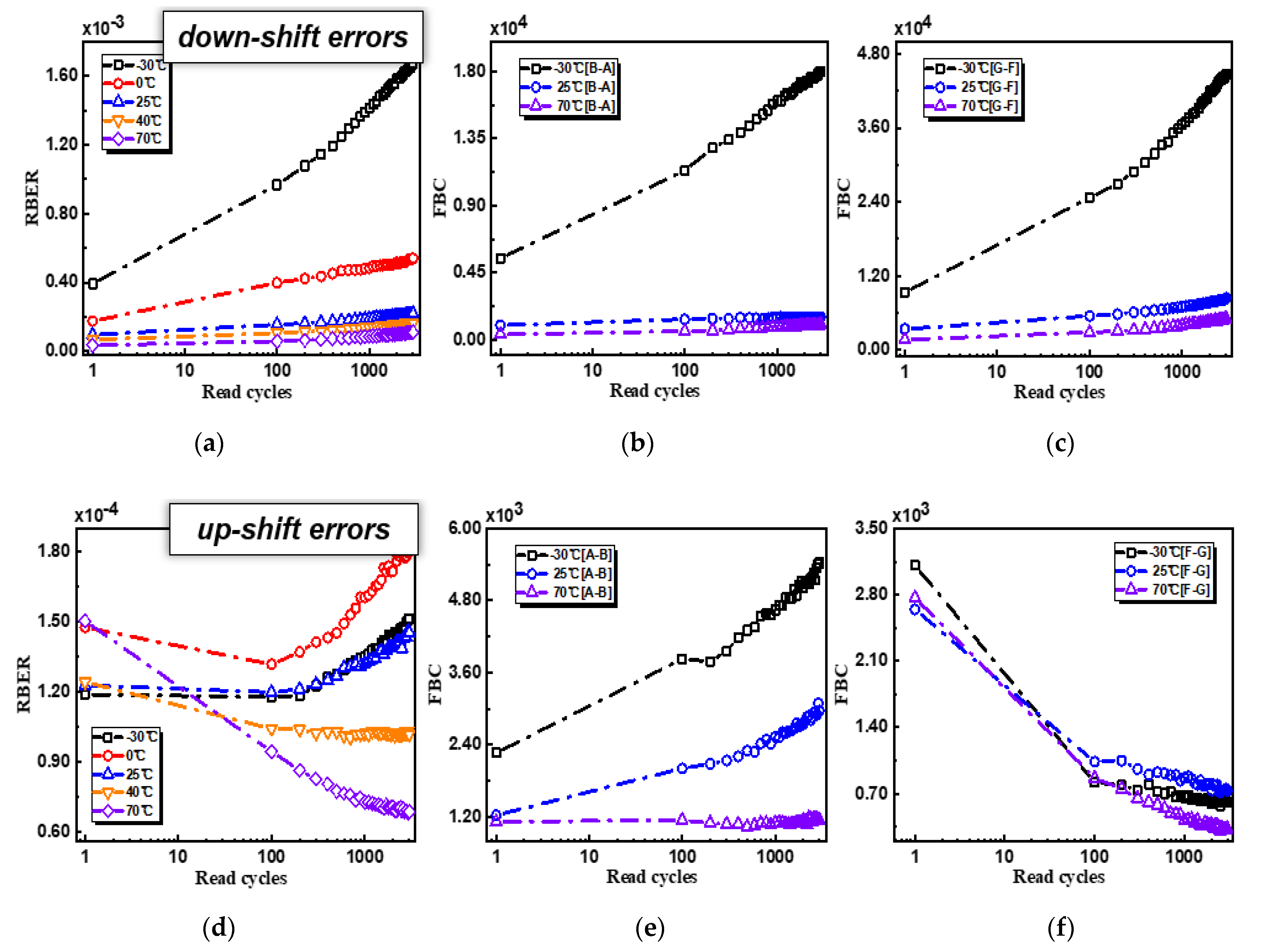

Measured read disturbs are summarized in

Figure 5. Firstly, it was observed that RBER degradation turned out to be much more serious at cold temperatures; secondly, for high-temperature operations at 70 °C, a part of RBER can be recovered after serval times reading. Considering that the total RBER included two parts, down-shift errors from the charge loss and up-shift errors from charge accrual, we divided the total error bits to two groups for in-depth analysis: down-shift errors and up-shift errors. As shown in

Figure 6, for read disturb-related RBER degradations, down-shift errors were the dominant part with clear temperature dependences, indicating that RBER changes mainly originated from the charge loss. Down-shift error degradation was much stronger at sub −25 °C, but it could be well suppressed at high temperatures, which can be explained by the narrower

distributions at high temperatures [

16]. The interesting phenomenon was that read disturbs from up-shift errors showed the opposite tendency while increasing the operating temperature. For read cycling at 70 °C, up-shift error bits can be partly recovered with read cycles. It was noticed that the decreasing error bits were mainly from cells with high program levels, like F-to-G errors in F-level cells. It should be noted that, as shown in

Figure 6f, lower F-to-G error bits can be observed in the whole temperature range from −30 to 70 °C. However, G-to-F up-shift error bits are largely suppressed at 70 °C. Thus, with combined down-shift and up-shift errors, we observed abnormal “recovery” at 70 °C while performing read cycling.

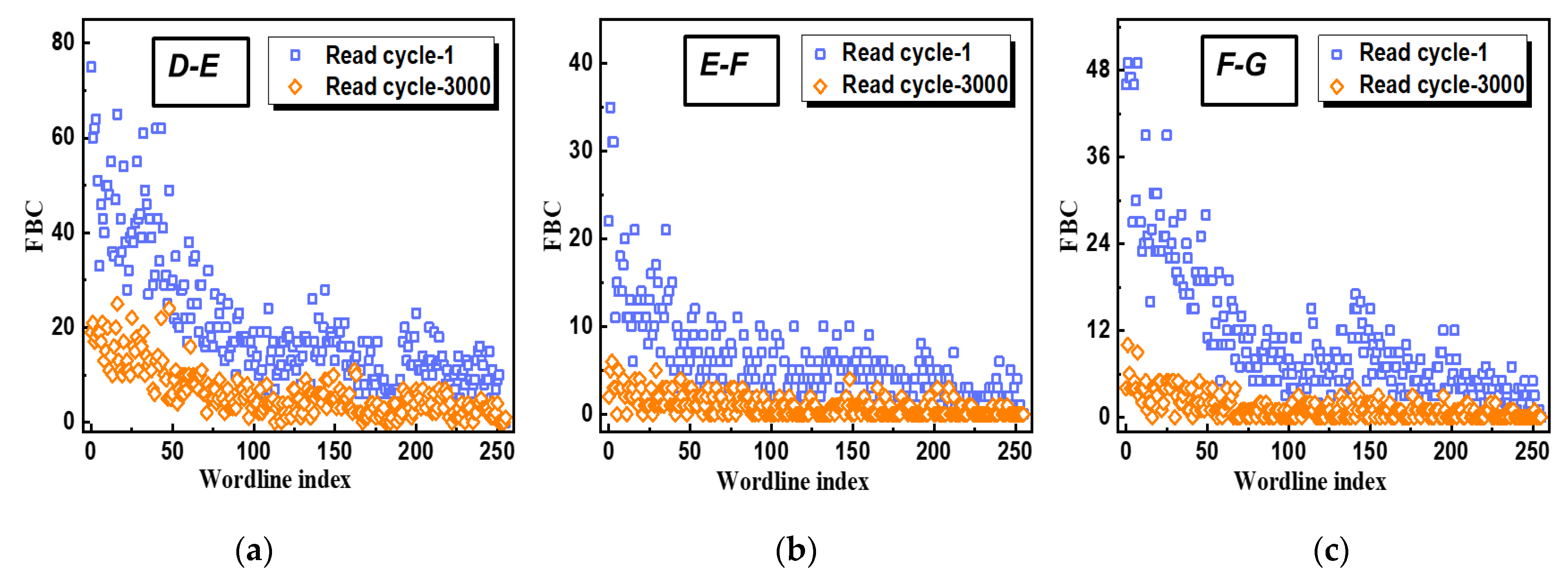

For further understandings, the word-line (WL) dependences of fail bit counts (FBCs) change at 70 °C were studied in detail. By comparing the data from the 1st and 3000th read cycles, it was observed that the dependence of the major state error decreased on the WL index. As shown in

Figure 7, error bits from D-E, E-F, and F-G errors showed obvious decreasing trends in higher WL index, and each read cycle in this experiment followed the same observation. In other words, the WLs of the middle-to-low index were the dominant origins for the lower up-shift errors that were attributed to the observed error bits “recovery” at 70 °C.