A Scalable and Low Stress Post-CMOS Processing Technique for Implantable Microsensors

Abstract

1. Introduction

2. Materials and Methods

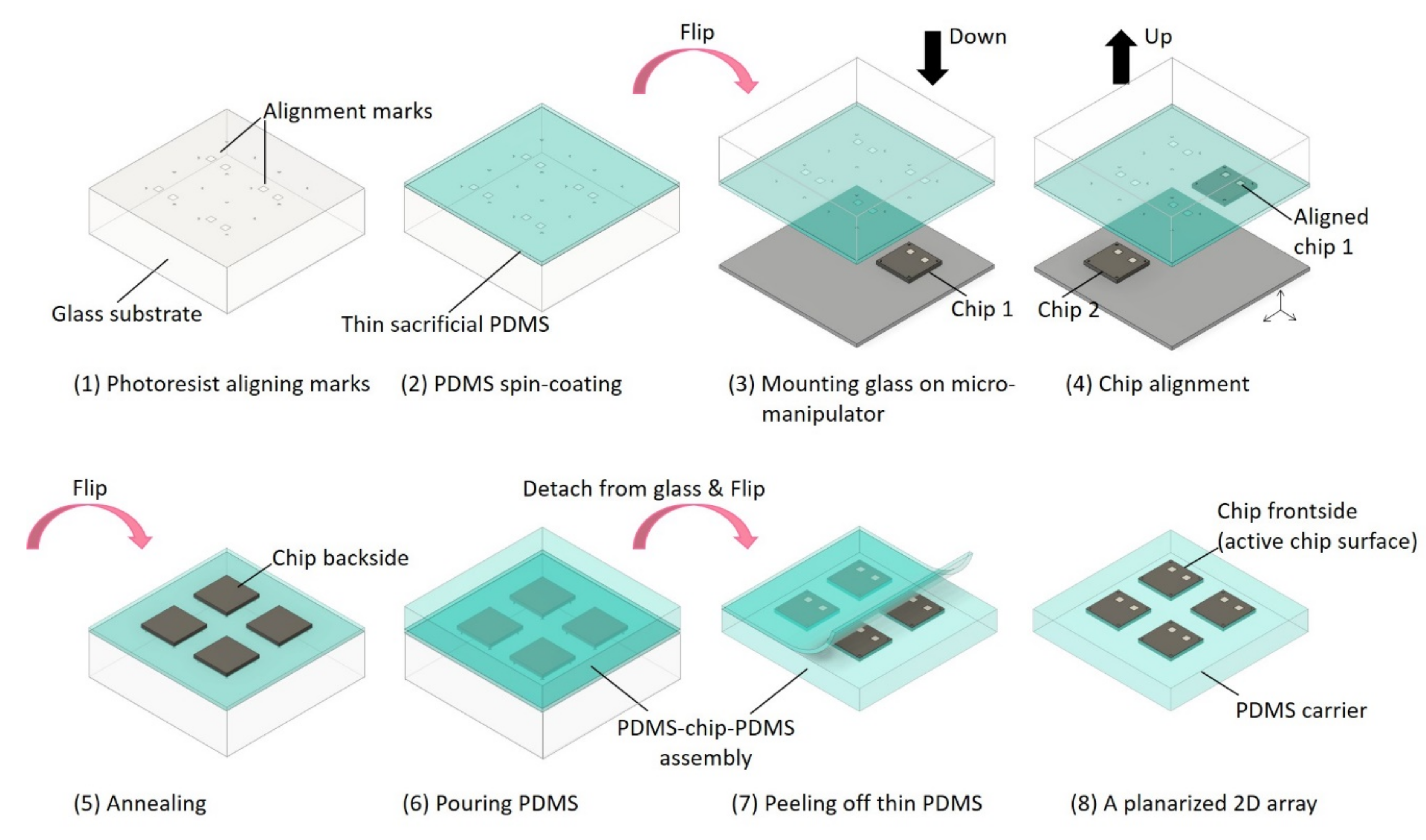

2.1. Planarized 2D Chip Array

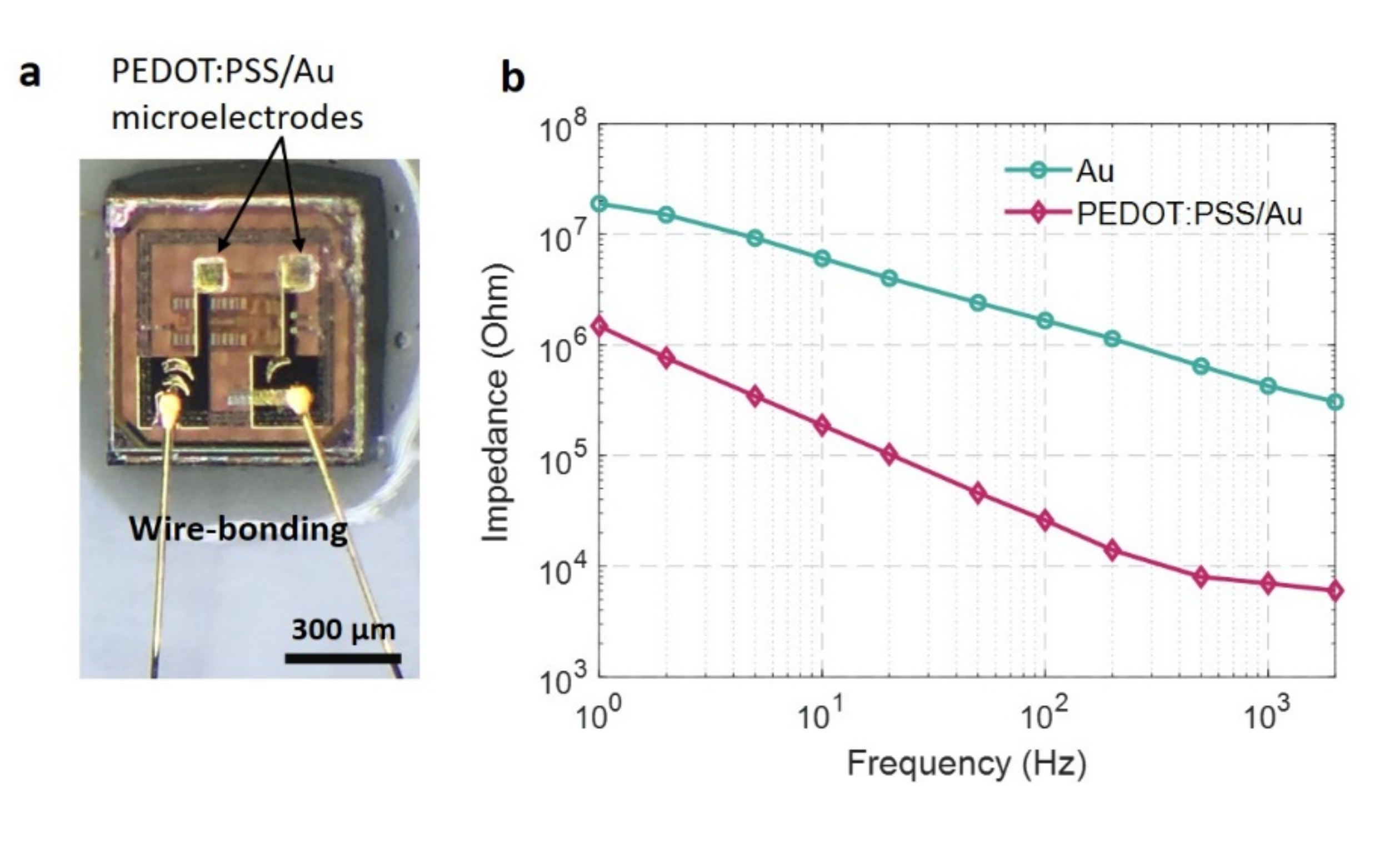

2.2. Fabrication of On-Chip Microelectrodes with Au and PEDOT:PSS

2.3. Characterization of Microelectrode Electrical Impedance

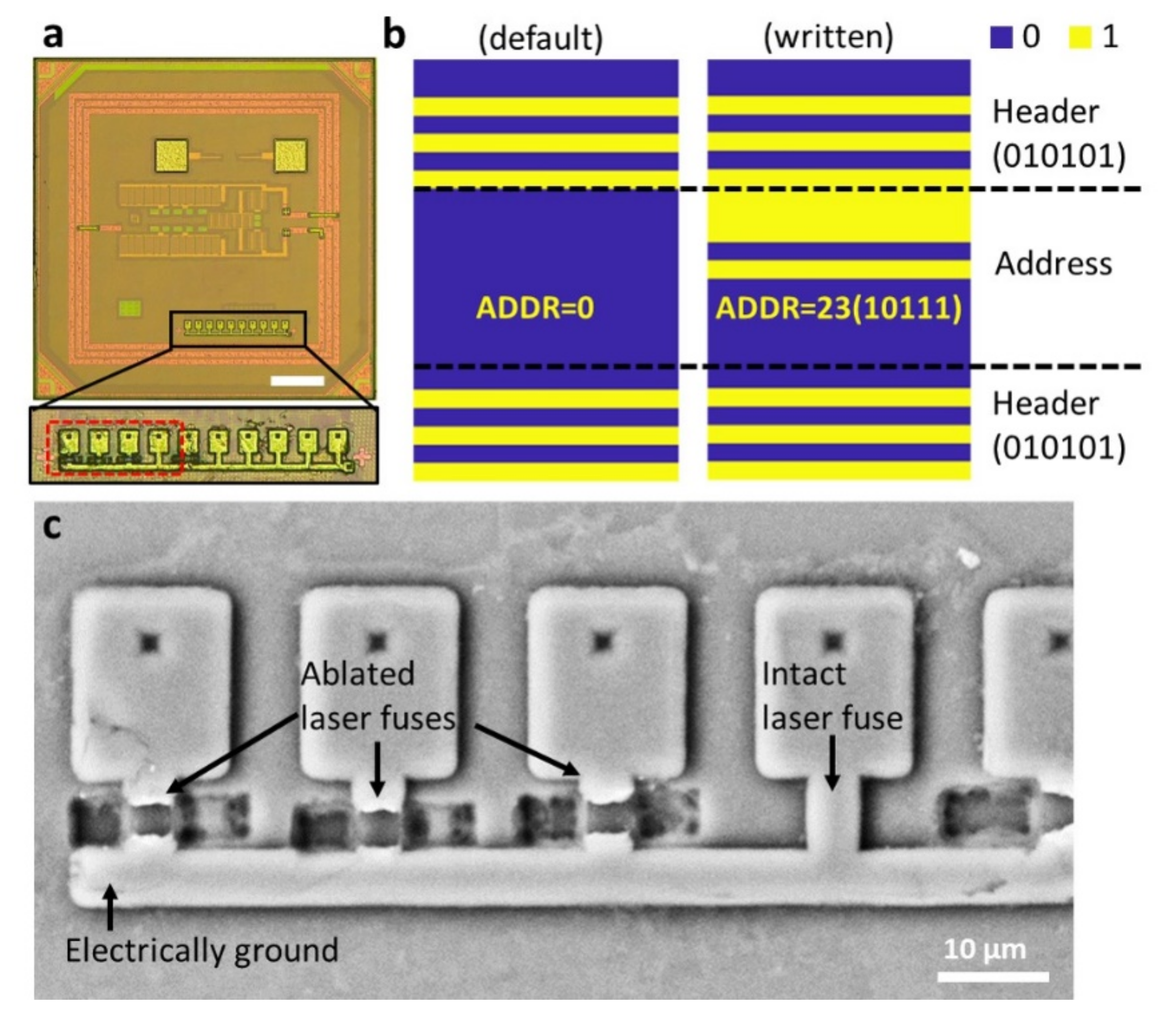

2.4. Post-Processing on-Chip Device Identifiers by Laser Ablation

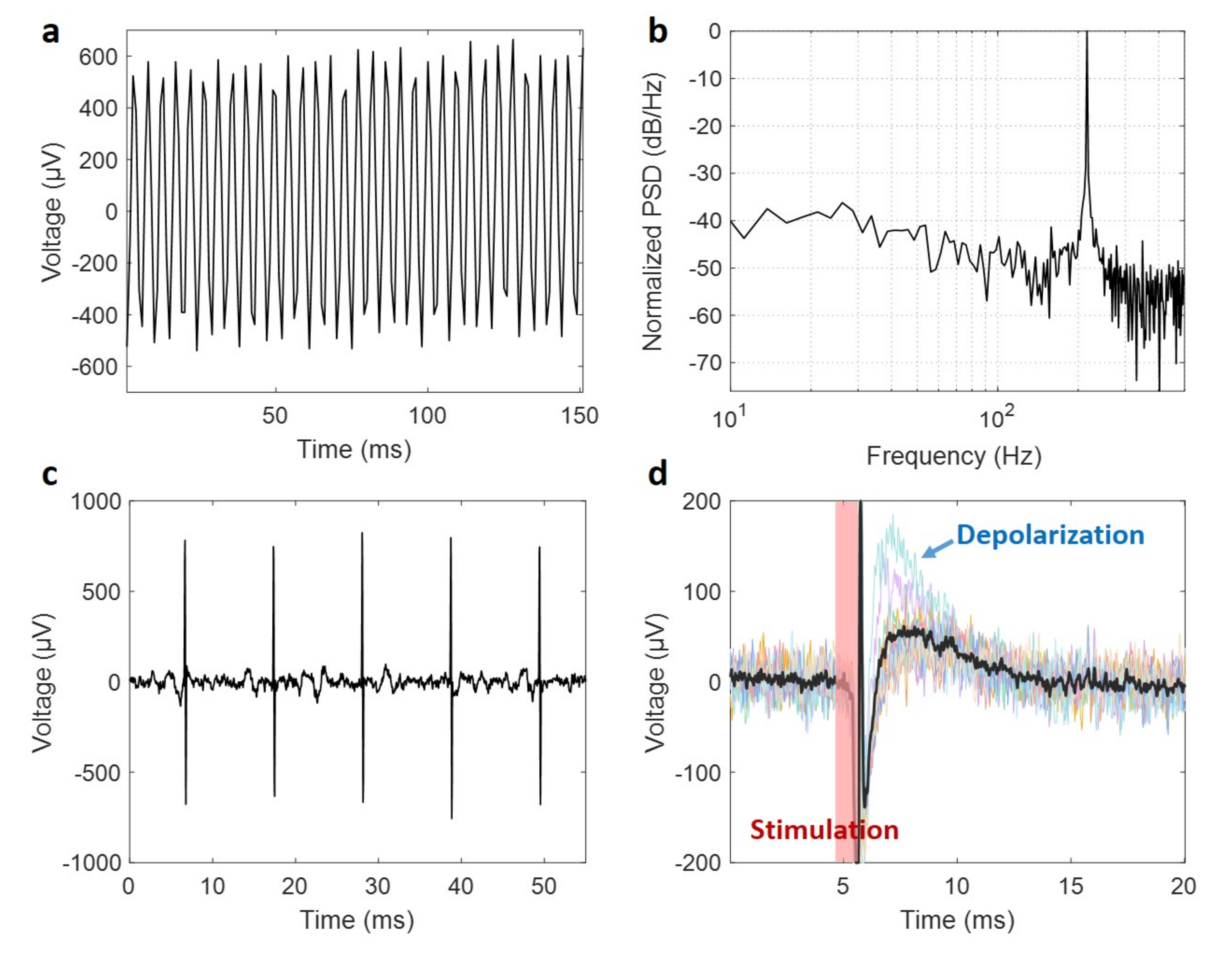

2.5. Assessing the Functionality of Post-Processed Microchips

3. Results and Discussion

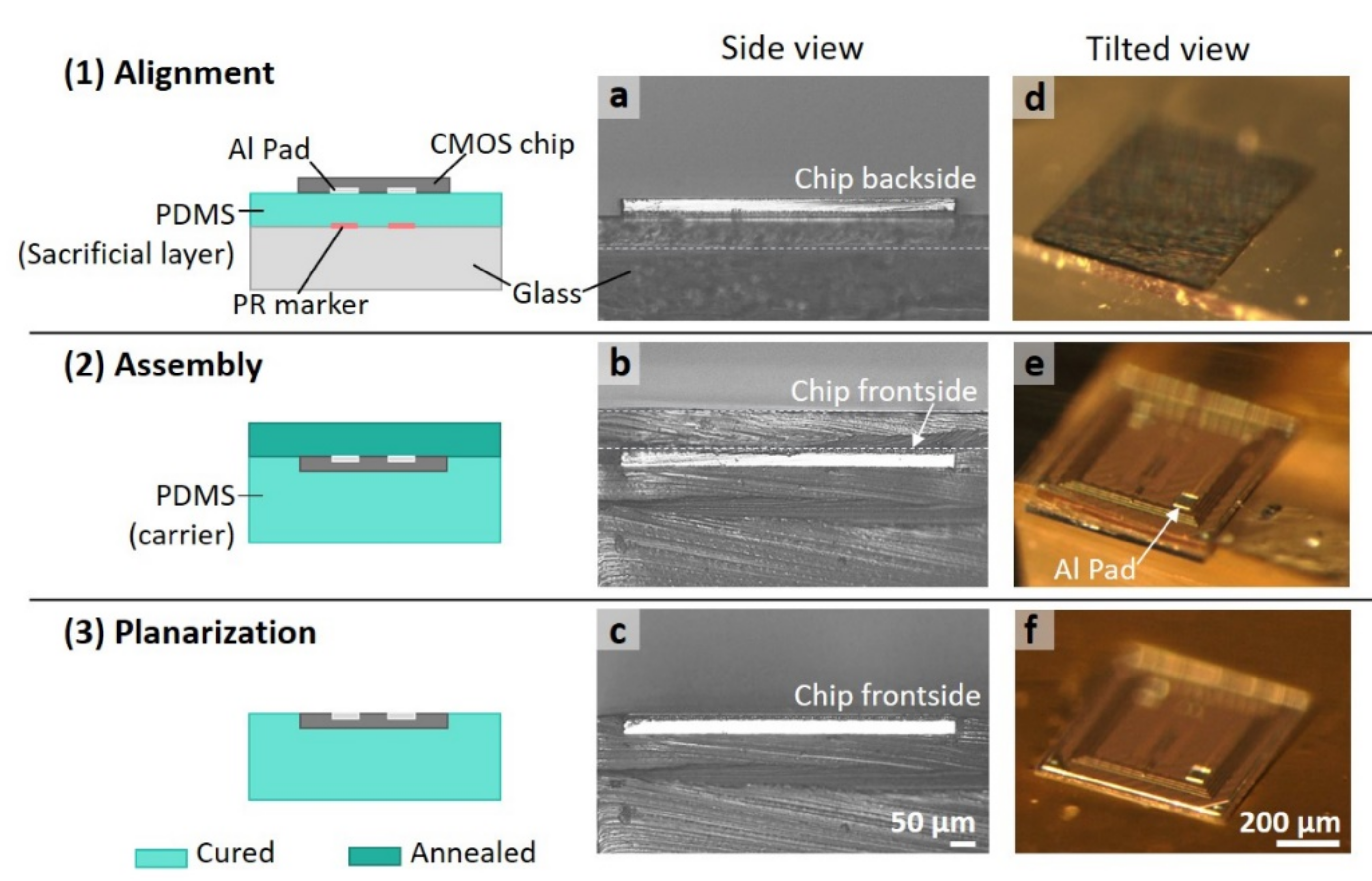

3.1. The Planarized Fabrication Process with a 30 μm Thin Die

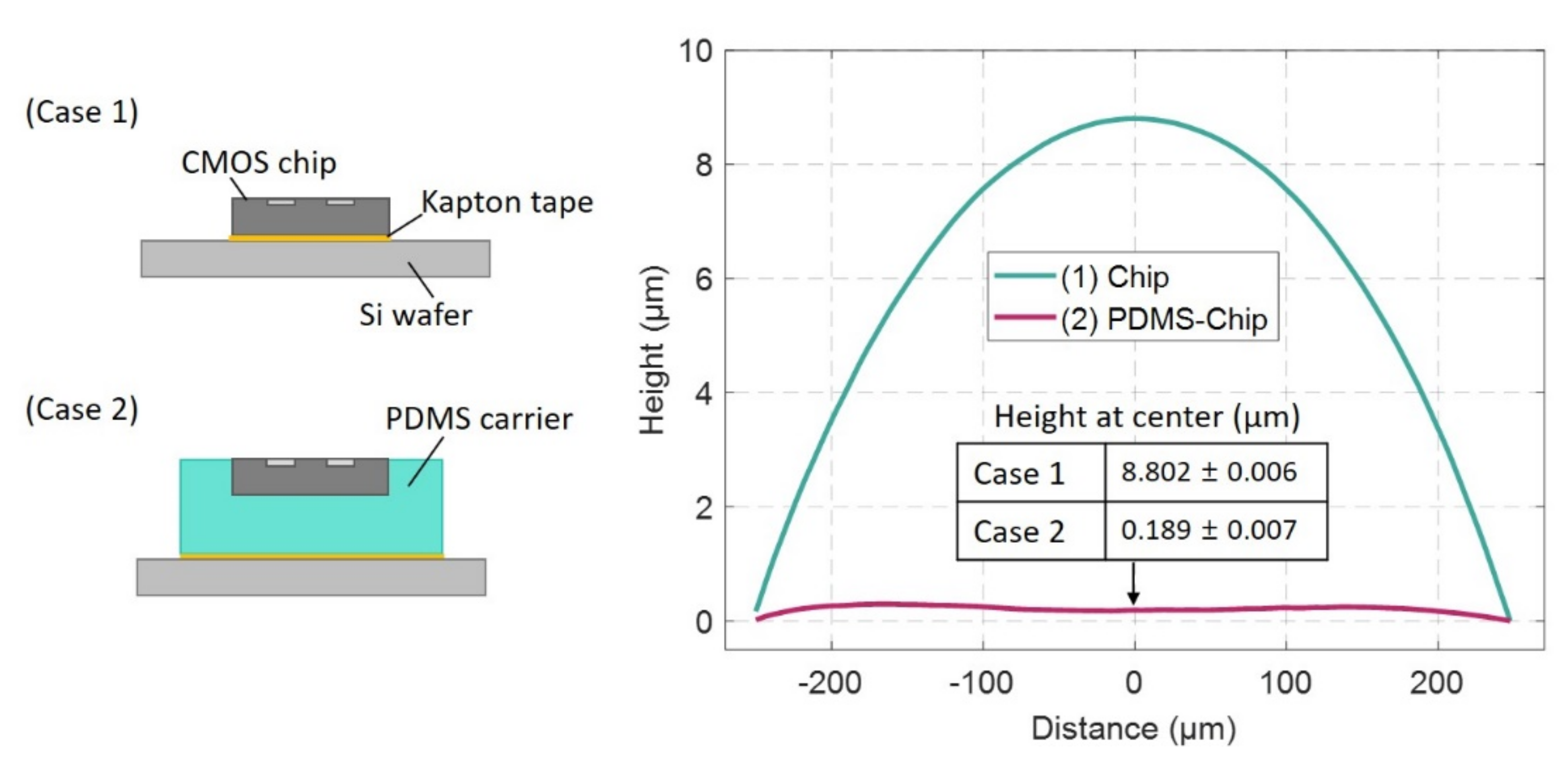

3.2. Surface Profile of the Photoresist Coated Sub-mm Sized Single Die

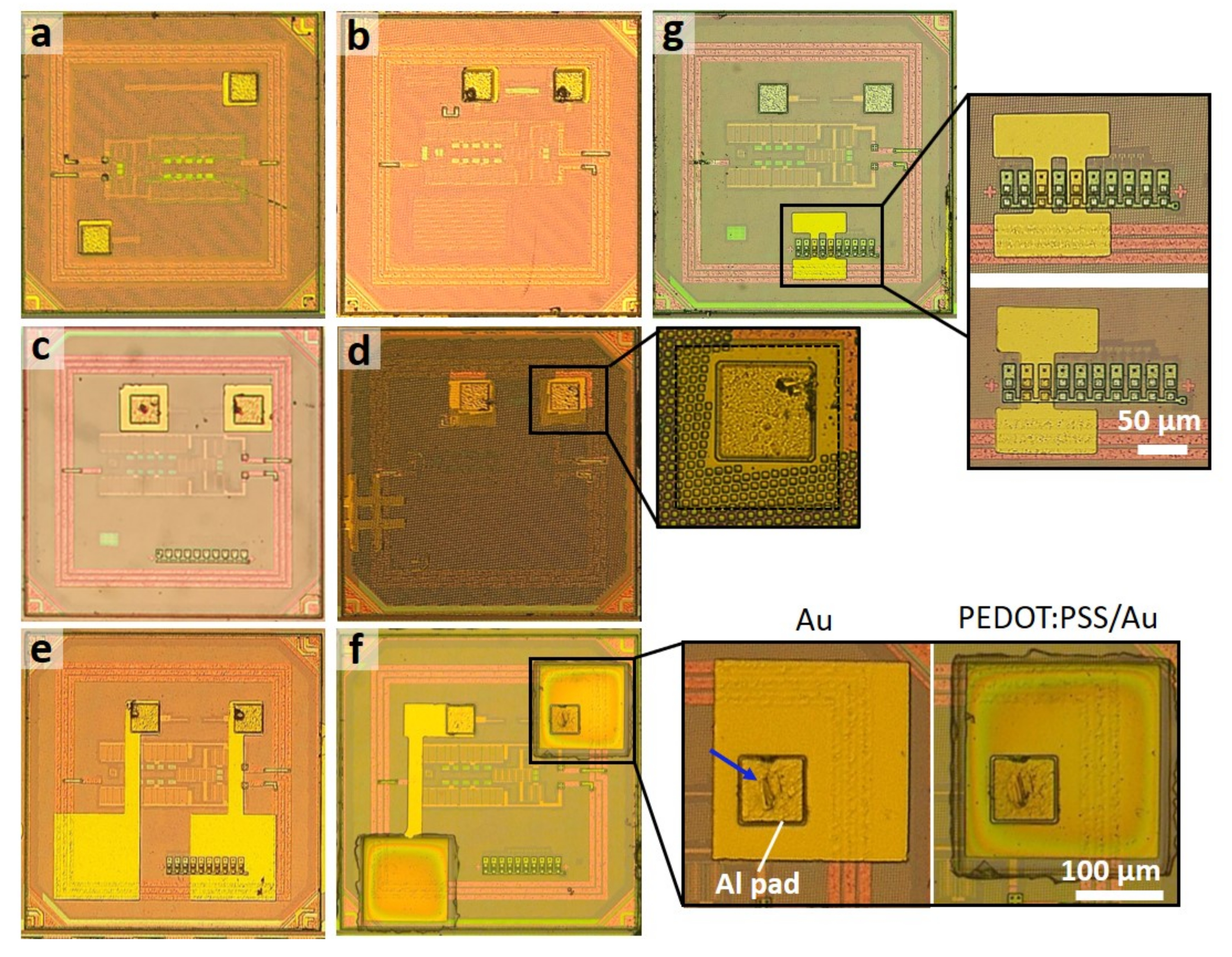

3.3. High Precision Post-Process Micropatterning of Microelectrodes on Chip Ensembles

3.4. On-Chip Device Identifier for RF Telecommunication

3.5. Impedance Measurement of On-Chip Microelectrodes

3.6. Validation of the Post-Processed Microchip Performance as Neural Implants

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Wei, C.L.; Lin, Y.C.; Chen, T.A.; Lin, R.Y.; Liu, T.H. Respiration Detection Chip with Integrated Temperature-Insensitive MEMS Sensors and CMOS Signal Processing Circuits. IEEE Trans. Biomed. Circuits Syst. 2014, 9, 105–112. [Google Scholar] [CrossRef] [PubMed]

- Chow, E.Y.; Chakraborty, S.; Chappell, W.J.; Irazoqui, P.P. Mixed-signal integrated circuits for self-contained sub-cubic millimeter biomedical implants. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 7–11 February 2010; pp. 236–237. [Google Scholar]

- Zhang, B.; Dong, Q.; Korman, C.E.; Li, Z.; Zaghloul, M.E. Flexible packaging of solid-state integrated circuit chips with elastomeric microfluidics. Sci. Rep. 2013, 3, 1098. [Google Scholar] [CrossRef]

- Burdallo, I.; Jiménez, C.; Fernández-Sánchez, C.; Baldi, A. Integration of microelectronic chips in microfluidic systems on printed circuit board. J. Micromech. Microeng. 2012, 22. [Google Scholar] [CrossRef]

- Chien, J.C.; Ameri, A.; Yeh, E.C.; Killilea, A.N.; Anwar, M.; Niknejad, A.M. A high-throughput flow cytometry-on-a-CMOS platform for single-cell dielectric spectroscopy at microwave frequencies. Lab Chip 2018, 18, 2065–2076. [Google Scholar] [CrossRef] [PubMed]

- Lindsay, M.; Bishop, K.; Sengupta, S.; Co, M.; Cumbie, M.; Chen, C.H.; Johnston, M.L. Heterogeneous Integration of CMOS Sensors and Fluidic Networks Using Wafer-Level Molding. IEEE Trans. Biomed. Circuits Syst. 2018, 12, 1046–1055. [Google Scholar] [CrossRef] [PubMed]

- Chang, S.R.; Chang, C.H.; Lin, J.S.; Lu, S.C.; Lee, Y.T.; Yeh, S.R.; Chen, H. Die-level, post-CMOS processes for fabricating open-gate, field-effect biosensor arrays with on-chip circuitry. J. Micromech. Microeng. 2008, 18, 115032. [Google Scholar] [CrossRef]

- Mirzaei, M.; Sawan, M. Microelectronics-Based Biosensors Dedicated to the Detection of Neurotransmitters: A Review. Sensors 2014, 14, 17981–18008. [Google Scholar] [CrossRef]

- Bonanno, A.; Sanginario, A.; Marasso, S.L.; Miccoli, B.; Bejtka, K.; Benetto, S.; Demarchi, D. A Multipurpose CMOS Platform for Nanosensing. Sensors 2016, 16, 2034. [Google Scholar] [CrossRef]

- Li, H.T.; Liu, X.W.; Li, L.; Mu, X.Y.; Genov, R.; Mason, A.J. CMOS Electrochemical Instrumentation for Biosensor Microsystems: A Review. Sensors 2017, 17, 74. [Google Scholar] [CrossRef]

- Park, S.; Borton, D.A.; Kang, M.Y.; Nurmikko, A.V.; Song, Y.K. An Implantable Neural Sensing Microsystem with Fiber-Optic Data Transmission and Power Delivery. Sensors 2013, 13, 6014–6031. [Google Scholar] [CrossRef]

- Lee, J.; Leung, V.; Lee, A.H.; Huang, J.; Asbeck, P.; Mercier, P.P.; Shellhammer, S.; Larson, L.; Laiwalla, F.; Nurmikko, A. Wireless Ensembles of Sub-mm Microimplants Communicating as a Network near 1 GHz in a Neural Application. bioRxiv 2020, arXiv:293829. [Google Scholar]

- Lee, J.; Mok, E.; Huang, J.; Cui, L.; Lee, A.; Leung, V.; Mercier, P.; Shellhammer, S.; Larson, L.; Asbeck, A.; et al. An Implantable Wireless Network of Distributed Microscale Sensors for Neural Applications. In Proceedings of the 9th International IEEE EMBS Conference on Neural Engineering (NER), San Francisco, CA, USA, 20–23 March 2019; pp. 871–874. [Google Scholar]

- Yeon, P.; Mirbozorgi, S.A.; Ash, B.; Eckhardt, H.; Ghovanloo, M. Fabrication and Microassembly of a mm-Sized Floating Probe for a Distributed Wireless Neural Interface. Micromachines 2016, 7, 154. [Google Scholar] [CrossRef] [PubMed]

- Jia, Y.Y.; Mirbozorgi, S.A.; Lee, B.; Khan, W.; Madi, F.; Inan, O.T.; Weber, A.; Li, W.; Ghovanloo, M. A mm-Sized Free-Floating Wirelessly Powered Implantable Optical Stimulation Device. IEEE Trans. Biomed. Circuits Syst. 2019, 13, 608–618. [Google Scholar] [CrossRef] [PubMed]

- Cho, S.H.; Xue, N.; Cauller, L.; Rosellini, W.; Lee, J.B. A SU-8-Based Fully Integrated Biocompatible Inductively Powered Wireless Neurostimulator. J. Microelectromech. S. 2013, 22, 170–176. [Google Scholar] [CrossRef]

- Khalifa, A.; Karimi, Y.; Wang, Q.H.; Garikapati, S.; Montlouis, W.; Stanacevic, M.; Thakor, N.; Etienne-Cummings, R. The Microbead: A Highly Miniaturized Wirelessly Powered Implantable Neural Stimulating System. IEEE Trans. Biomed. Circuits Syst. 2018, 12, 521–531. [Google Scholar] [CrossRef]

- Piech, D.; Johnson, B.C.; Shen, K.; Ghanbari, M.M.; Li, K.Y.; Neely, R.; Kay, J.E.; Carmena, J.M.; Maharbiz, M.M.; Muller, R. A wireless millimetre-scale implantable neural stimulator with ultrasonically powered bidirectional communication. Nat. Biomed. Eng. 2020, 4, 207–222. [Google Scholar] [CrossRef]

- Cogan, S.F. Neural stimulation and recording electrodes. Annu. Rev. Biomed. Eng. 2008, 10, 275–309. [Google Scholar] [CrossRef]

- Wellman, S.M.; Eles, J.R.; Ludwig, K.A.; Seymour, J.P.; Michelson, N.J.; McFadden, W.E.; Vazquez, A.L.; Kozai, T.D.Y. A Materials Roadmap to Functional Neural Interface Design. Adv. Funct. Mater. 2018, 28, 1701269. [Google Scholar] [CrossRef]

- Ganji, M.; Kaestner, E.; Hermiz, J.; Rogers, N.; Tanaka, A.; Cleary, D.; Lee, S.H.; Snider, J.; Halgren, M.; Cosgrove, G.R.; et al. Development and Translation of PEDOT:PSS Microelectrodes for Intraoperative Monitoring. Adv. Funct. Mater. 2018, 28, 1700232. [Google Scholar] [CrossRef]

- Khodagholy, D.; Gelinas, J.N.; Thesen, T.; Doyle, W.; Devinsky, O.; Malliaras, G.G.; Buzsaki, G. NeuroGrid: Recording action potentials from the surface of the brain. Nat. Neurosci. 2015, 18, 310–315. [Google Scholar] [CrossRef]

- Ganji, M.; Elthakeb, A.T.; Tanaka, A.; Gilja, V.; Halgren, E.; Dayeh, S.A. Scaling Effects on the Electrochemical Performance of poly(3,4-ethylenedioxythiophene (PEDOT), Au, and Pt for Electrocorticography Recording. Adv. Funct. Mater. 2017, 27, 1703018. [Google Scholar] [CrossRef]

- Sessolo, M.; Khodagholy, D.; Rivnay, J.; Maddalena, F.; Gleyzes, M.; Steidl, E.; Buisson, B.; Malliaras, G.G. Easy-to-Fabricate Conducting Polymer Microelectrode Arrays. Adv. Mater. 2013, 25, 2135–2139. [Google Scholar] [CrossRef] [PubMed]

- Huang, Y.; Mason, A.J. Lab-on-CMOS integration of microfluidics and electrochemical sensors. Lab Chip 2013, 13, 3929–3934. [Google Scholar] [CrossRef] [PubMed]

- Lopez-Huerta, F.; Herrera-May, A.L.; Estrada-Lopez, J.J.; Zuniga-Islas, C.; Cervantes-Sanchez, B.; Soto, E.; Soto-Cruz, B.S. Alternative Post-Processing on a CMOS Chip to Fabricate a Planar Microelectrode Array. Sensors 2011, 11, 10940–10957. [Google Scholar] [CrossRef] [PubMed]

- Chae, J.; Kulah, H.; Najafi, K. A CMOS-compatible high aspect ratio silicon-on-glass in-plane micro-accelerometer. J. Micromech. Microeng. 2005, 15, 336–345. [Google Scholar] [CrossRef]

- Datta-Chaudhuri, T.; Abshire, P.; Smela, E. Packaging commercial CMOS chips for lab on a chip integration. Lab Chip 2014, 14, 1753–1766. [Google Scholar] [CrossRef]

- Datta-Chaudhuri, T.; Smela, E.; Abshire, P.A. System-on-Chip Considerations for Heterogeneous Integration of CMOS and Fluidic Bio-Interfaces. IEEE Trans. Biomed. Circuits Syst. 2016, 10, 1129–1142. [Google Scholar] [CrossRef]

- Li, L.; Yin, H.; Mason, A.J. Epoxy Chip-in-Carrier Integration and Screen-Printed Metalization for Multichannel Microfluidic Lab-on-CMOS Microsystems. IEEE Trans. Biomed. Circuits Syst. 2018, 12, 416–425. [Google Scholar] [CrossRef]

- Ieong, M.; Doris, B.; Kedzierski, J.; Rim, K.; Yang, M. Silicon device scaling to the sub-10-nm regime. Science 2004, 306, 2057–2060. [Google Scholar] [CrossRef]

- Radamson, H.H.; He, X.B.; Zhang, Q.Z.; Liu, J.B.; Cui, H.S.; Xiang, J.J.; Kong, Z.Z.; Xiong, W.J.; Li, J.J.; Gao, J.F.; et al. Miniaturization of CMOS. Micromachines 2019, 10, 293. [Google Scholar] [CrossRef]

- Charlot, B.; Sassine, G.; Garraud, A.; Sorli, B.; Giani, A.; Combette, P. Micropatterning PEDOT:PSS layers. Microsyst. Technol. 2013, 19, 895–903. [Google Scholar] [CrossRef]

- Ouyang, S.H.; Xie, Y.T.; Wang, D.P.; Zhu, D.L.; Xu, X.; Tan, T.; Fong, H.H. Surface Patterning of PEDOT:PSS by Photolithography for Organic Electronic Devices. J. Nanomater. 2015, 2015. [Google Scholar] [CrossRef]

- Laiwalla, F.; Lee, J.; Lee, A.; Mok, E.; Leung, V.; Shellhammer, S.; Song, Y.; Larson, L.; Nurmikko, A. A Distributed Wireless Network of Implantable Sub-mm Cortical Microstimulators for Brain-Computer Interfaces. In Proceedings of the 41st Annual International Conference of the IEEE Engineering in Medicine & Biology Society (EMBC), Berlin, Germany, 23–27 July 2019; pp. 6876–6879. [Google Scholar]

- Lee, J.; Laiwalla, F.; Jeong, J.; Kilfoyle, C.; Larson, L.; Nurmikko, A.; Li, S.; Yu, S.; Leung, V. Wireless Power and Data Link for Ensembles of Sub-mm scale Implantable Sensors near 1GHz. In Proceedings of the IEEE Biomedical Circuits and Systems Conference (BioCAS), Cleveland, OH, USA, 17–19 October 2018; pp. 1–4. [Google Scholar]

- Huang, J.; Laiwalla, F.; Lee, J.; Cui, L.; Leung, V.; Nurmikko, A.; Mercier, P. A 0.01-mm2 Mostly Digital Capacitor-Less AFE for Distributed Autonomous Neural Sensor Nodes. IEEE Soild State Circuits Lett. 2018, 1, 162–165. [Google Scholar] [CrossRef]

- Leung, V.; Lee, J.; Li, S.; Yu, S.; Kilfovle, C.; Larson, L.; Nurmikko, A.; Laiwalla, F. A CMOS Distributed Sensor System for High-Density Wireless Neural Implants for Brain-Machine Interfaces. In Proceedings of the ESSCIRC IEEE 44th European Soild State Circuits Conference (ESSCIRC), Dresden, Germany, 3–6 September 2018; pp. 230–233. [Google Scholar]

- Leung, V.; Cui, L.; Alluri, S.; Lee, J.; Huang, J.; Mok, E.; Shellhammer, S.; Rao, R.; Asbeck, P.; Mercier, P.; et al. Distributed Microscale Brain Implants with Wireless Power Transfer and Mbps Bi-directional Networked Communications. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 14–17 April 2019; pp. 1–4. [Google Scholar]

- Braun, T.; Becker, K.F.; Hoelck, O.; Voges, S.; Kahle, R.; Dreissigacker, M.; Schneider-Ramelow, M. Fan-Out Wafer and Panel Level Packaging as Packaging Platform for Heterogeneous Integration. Micromachines 2019, 10, 342. [Google Scholar] [CrossRef]

- Jeong, J.; Laiwalla, F.; Lee, J.; Ritasalo, R.; Pudas, M.; Larson, L.; Leung, V.; Nurmikko, A. Conformal Hermetic Sealing of Wireless Microelectronic Implantable Chiplets by Multilayered Atomic Layer Deposition (ALD). Adv. Funct. Mater. 2019, 29, 1806440. [Google Scholar] [CrossRef]

- Ding, K.; Avrutin, V.; Izyumskaya, N.; Özgür, Ü.; Morkoç, H. Micro-LEDs, a Manufacturability Perspective. Appl. Sci. 2019, 9, 1206. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, A.-H.; Lee, J.; Laiwalla, F.; Leung, V.; Huang, J.; Nurmikko, A.; Song, Y.-K. A Scalable and Low Stress Post-CMOS Processing Technique for Implantable Microsensors. Micromachines 2020, 11, 925. https://doi.org/10.3390/mi11100925

Lee A-H, Lee J, Laiwalla F, Leung V, Huang J, Nurmikko A, Song Y-K. A Scalable and Low Stress Post-CMOS Processing Technique for Implantable Microsensors. Micromachines. 2020; 11(10):925. https://doi.org/10.3390/mi11100925

Chicago/Turabian StyleLee, Ah-Hyoung, Jihun Lee, Farah Laiwalla, Vincent Leung, Jiannan Huang, Arto Nurmikko, and Yoon-Kyu Song. 2020. "A Scalable and Low Stress Post-CMOS Processing Technique for Implantable Microsensors" Micromachines 11, no. 10: 925. https://doi.org/10.3390/mi11100925

APA StyleLee, A.-H., Lee, J., Laiwalla, F., Leung, V., Huang, J., Nurmikko, A., & Song, Y.-K. (2020). A Scalable and Low Stress Post-CMOS Processing Technique for Implantable Microsensors. Micromachines, 11(10), 925. https://doi.org/10.3390/mi11100925