Study of Carrier Mobilities in 4H-SiC MOSFETS Using Hall Analysis

Abstract

1. Introduction

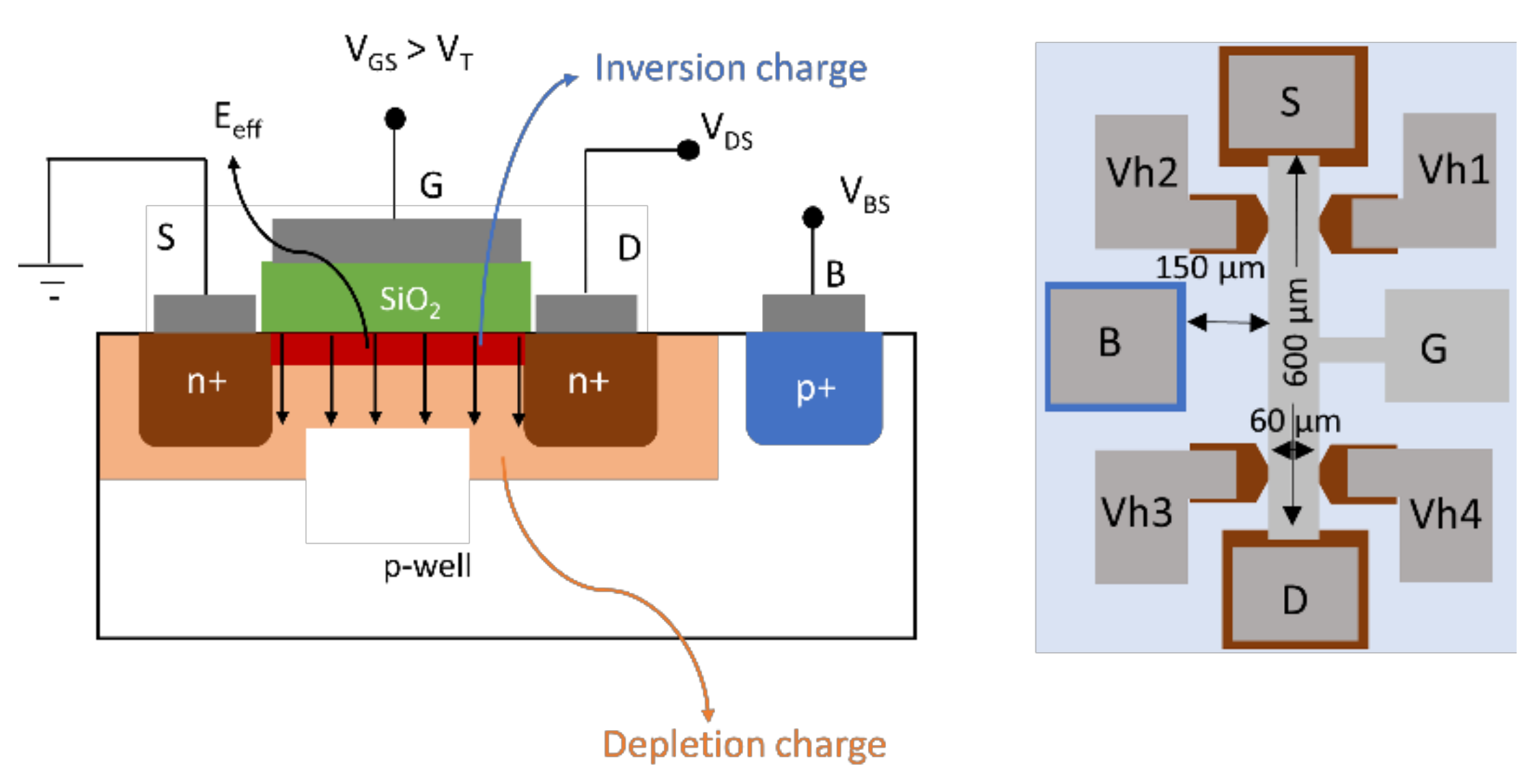

2. Materials and Methods

2.1. Fundamentals on Channel-Transverse Electric Fields and Mobility

2.2. Experimental Methods

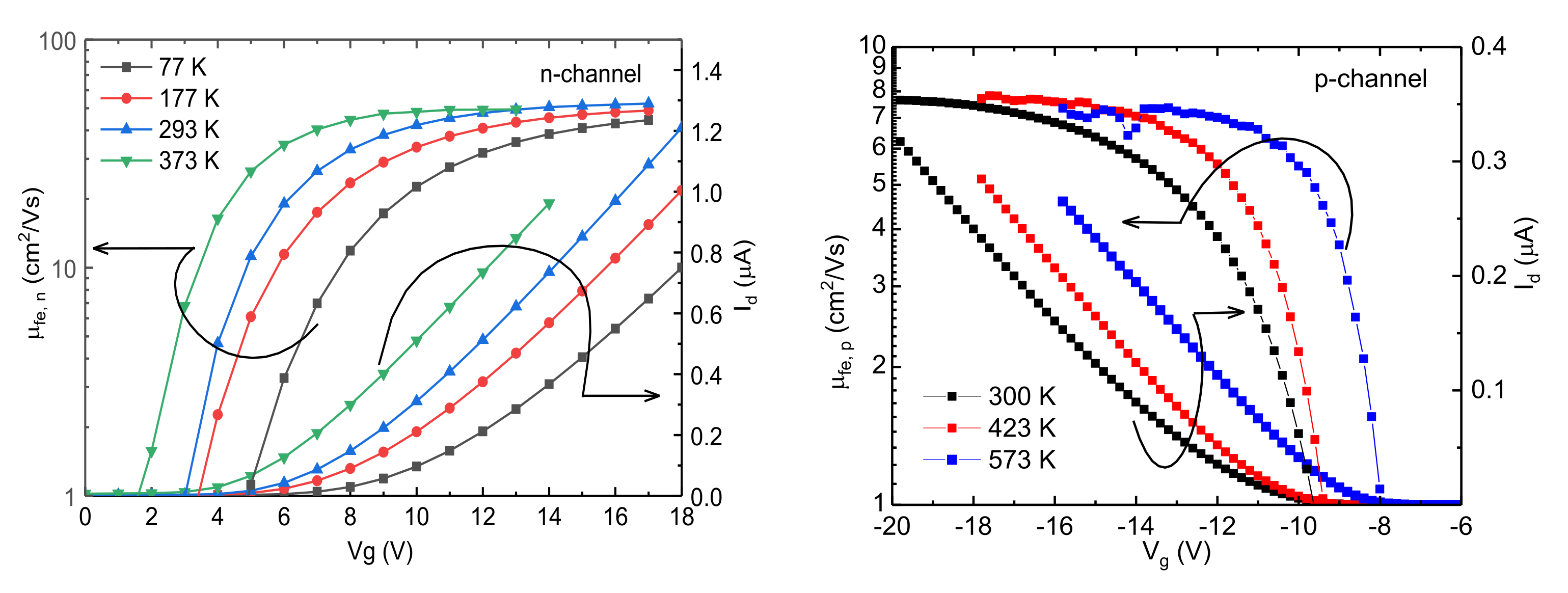

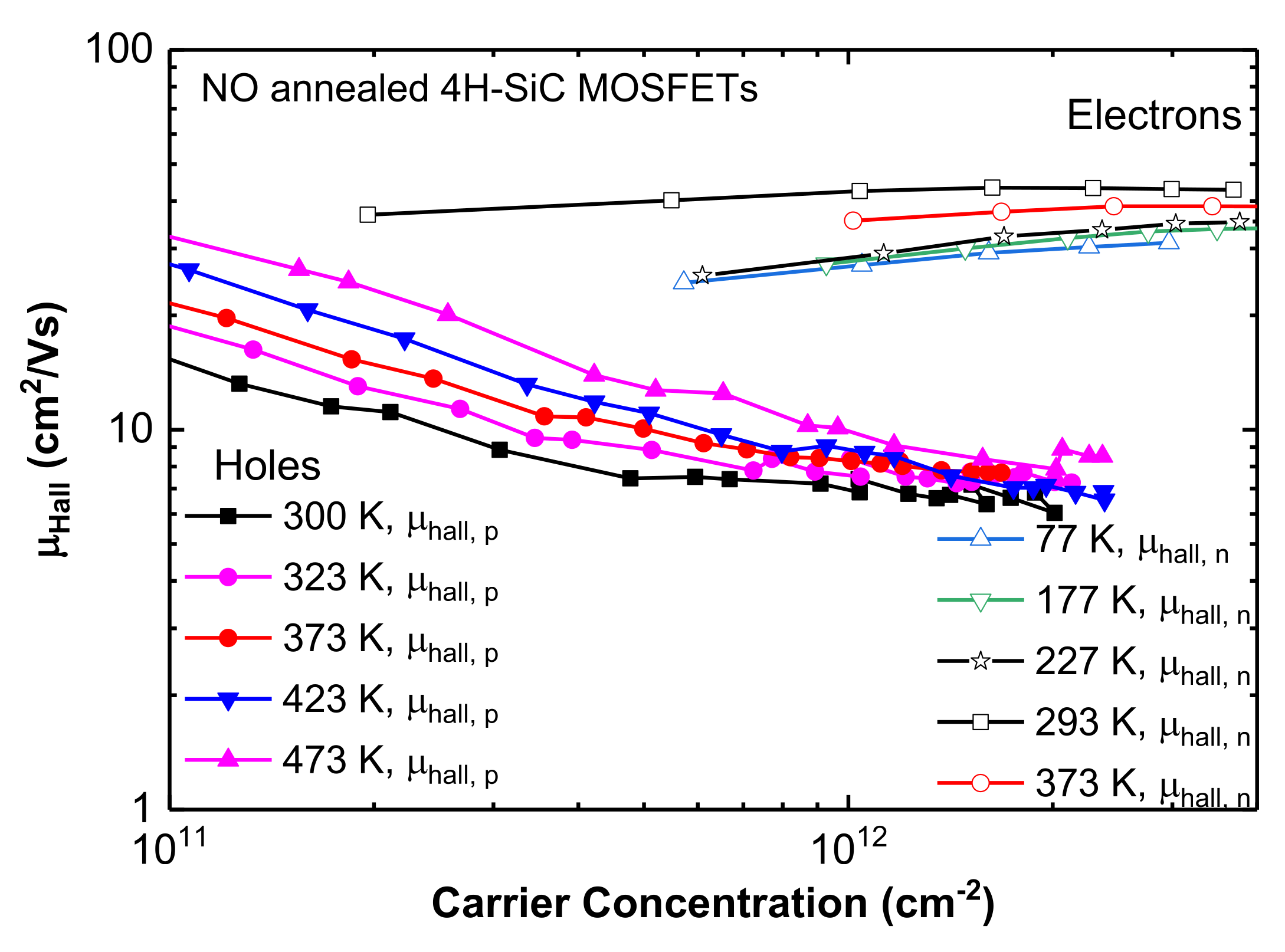

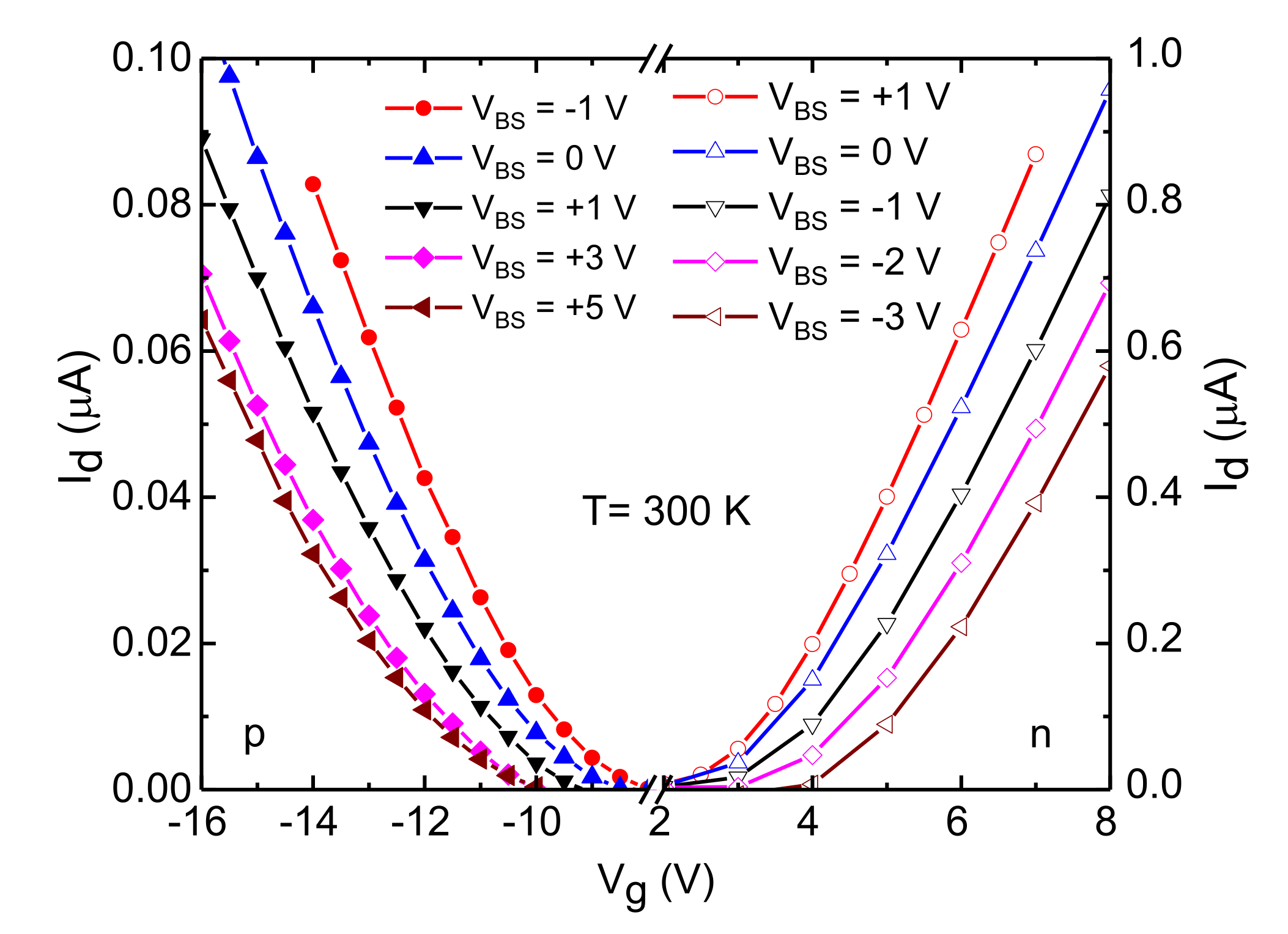

3. Results and Discussions

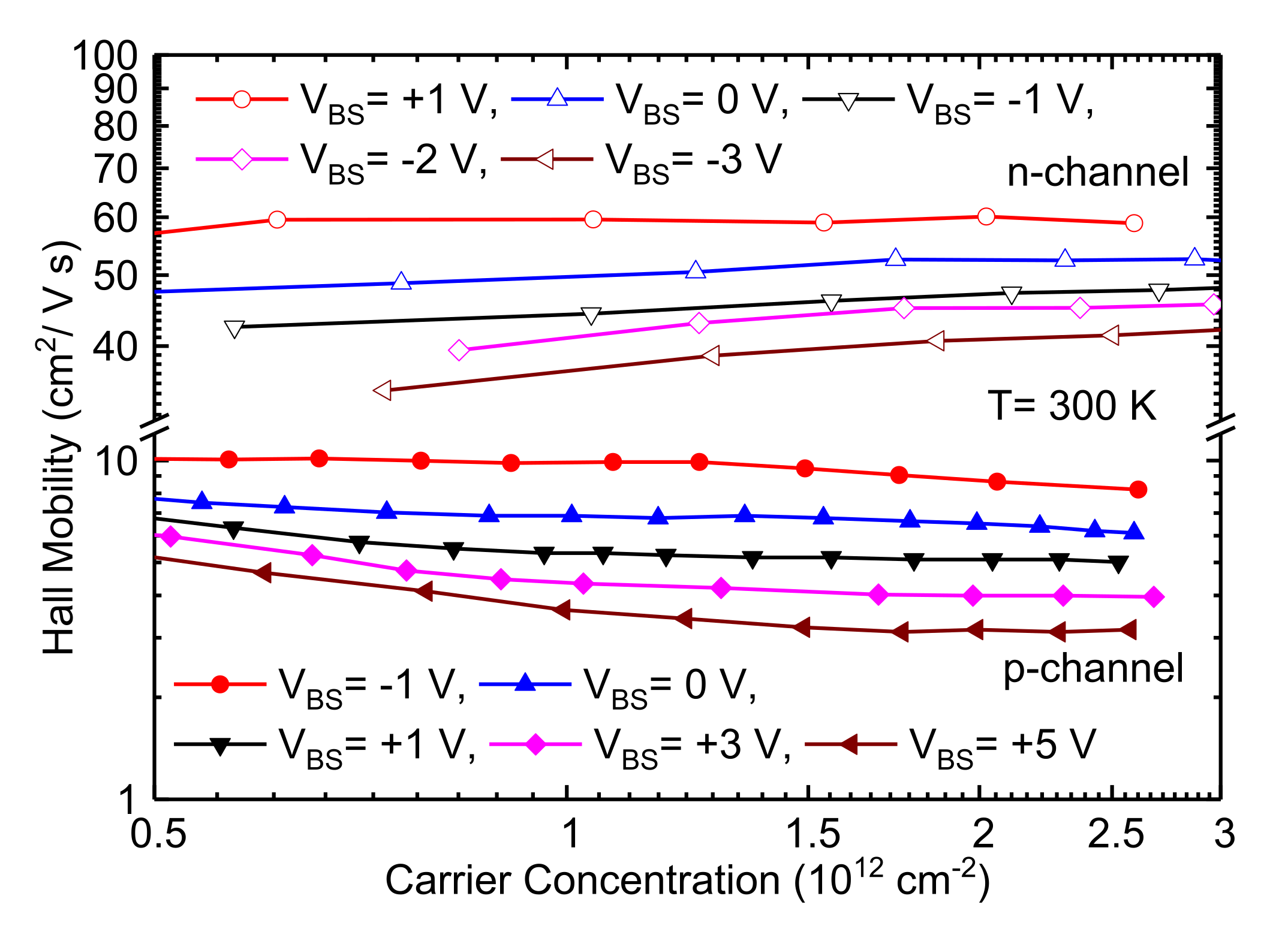

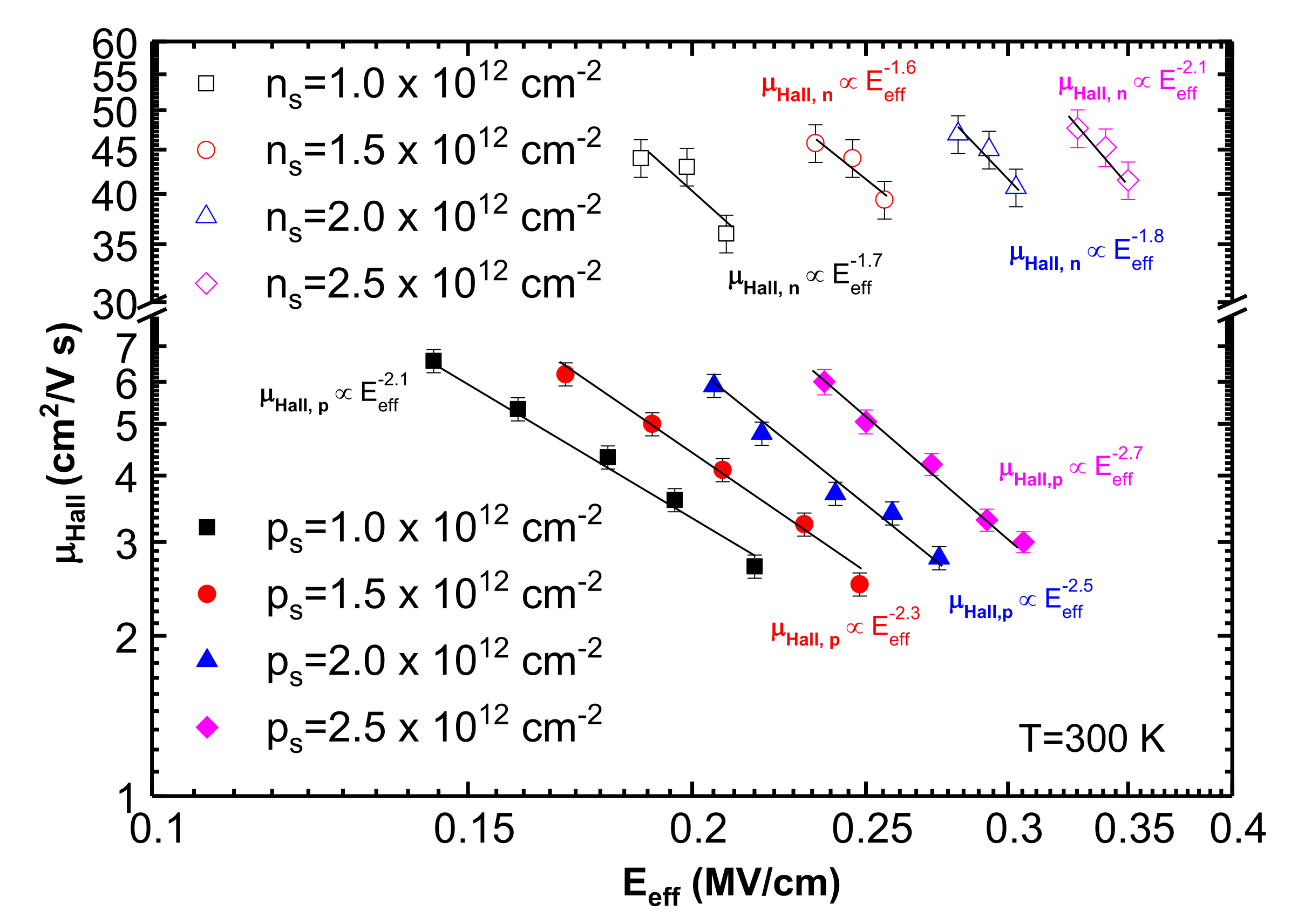

3.1. Classification of the Dominant Scattering Mechanisms

3.2. Analysis of Surface Roughness Scattering Using Body Bias Measurements

3.3. Phonon-Scattering-Limited Mobility

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Baliga, B.J. Fundamentals of Power Semiconductor Devices; Springer Science & Business Media: Berlin, Germany, 2010; ISBN 978-0-387-47314-7. [Google Scholar]

- Agarwal, A.K. An Overview of SiC Power Devices. In Proceedings of the 2010 International Conference on Power, Control and Embedded Systems, Allahabad, India, 29 November–1 December 2010; pp. 1–4. [Google Scholar]

- He, J.; Zhao, T.; Jing, X.; Demerdash, N.A.O. Application of Wide Bandgap Devices in Renewable Energy Systems—Benefits and Challenges. In Proceedings of the 2014 International Conference on Renewable Energy Research and Application (ICRERA), Milwaukee, WI, USA, 19–22 October 2014; pp. 749–754. [Google Scholar]

- Hunter, G.; Neudeck, P.; Xu, J.C.; Lukco, D.; Trunek, A.J.; Artale, M.; Lampard, P.; Androjna, D.; Makel, D.; Ward, B.; et al. Development of SiC-Based Gas Sensors for Aerospace Applications. MRS Online Proc. Libr. 2004, 815. [Google Scholar] [CrossRef]

- Rahman, A.; Roy, S.; Murphree, R.; Kotecha, R.; Addington, K.; Abbasi, A.; Mantooth, H.A.; Francis, A.M.; Holmes, J.; Di, J. High-Temperature SiC CMOS Comparator and Op-Amp for Protection Circuits in Voltage Regulators and Switch-Mode Converters. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 935–945. [Google Scholar] [CrossRef]

- Holmes, J.; Francis, A.M.; Getreu, I.; Barlow, M.; Abbasi, A.; Mantooth, H.A. Extended High-Temperature Operation of Silicon Carbide CMOS Circuits for Venus Surface Application. J. Microelectron. Electron. Packag. 2016, 13, 143–154. [Google Scholar] [CrossRef]

- Kappert, H.; Kordas, N.; Dreiner, S.; Paschen, U.; Kokozinski, R. High Temperature SOI CMOS Technology and Circuit Realization for Applications up to 300 °C. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015. [Google Scholar] [CrossRef]

- Homberger, J.M.; Cilio, E.; Schupbach, R.M.; Lostetter, A.B.; Mantooth, H.A. A High-Temperature Multichip Power Module (MCPM) Inverter Utilizing Silicon Carbide (SiC) and Silicon on Insulator (SOI) Electronics. In Proceedings of the 2006 37th IEEE Power Electronics Specialists Conference, Jeju, Korea, 18–22 June 2006; pp. 1–7. [Google Scholar]

- Liu, D.; Svensson, C. Power Consumption Estimation in CMOS VLSI Chips. IEEE J. Solid-State Circuits 1994, 29, 663–670. [Google Scholar] [CrossRef]

- Tachiki, K.; Kimoto, T. Improvement of Both N- and p-Channel Mobilities in 4H-SiC MOSFETs by High-Temperature N₂ Annealing. IEEE Trans. Electron Devices 2021, 68, 638–644. [Google Scholar] [CrossRef]

- Tachiki, K.; Kaneko, M.; Kimoto, T. Mobility Improvement of 4H-SiC (0001) MOSFETs by a Three-Step Process of H2 Etching, SiO2 Deposition, and Interface Nitridation. Appl. Phys. Express 2021, 14, 031001. [Google Scholar] [CrossRef]

- Tachiki, K.; Mikami, K.; Ito, K.; Kaneko, M.; Kimoto, T. Mobility Enhancement in Heavily Doped 4H-SiC (0001), (), and () MOSFETs via an Oxidation-Minimizing Process. Appl. Phys. Express 2022, 15, 071001. [Google Scholar] [CrossRef]

- Mikami, K.; Tachiki, K.; Ito, K.; Kimoto, T. Body Doping Dependence of Field-Effect Mobility in Both n- and p-Channel 4H-SiC Metal-Oxide-Semiconductor Field-Effect Transistors with Nitrided Gate Oxides. Appl. Phys. Express 2022, 15, 036503. [Google Scholar] [CrossRef]

- Hirai, H.; Hatakeyama, T.; Sometani, M.; Okamoto, M.; Harada, S.; Okumura, H.; Yamaguchi, H. Difference in Electron Mobility at 4H–SiC/SiO2 Interfaces with Various Crystal Faces Originating from Effective-Field-Dependent Scattering. Appl. Phys. Lett. 2020, 117, 042101. [Google Scholar] [CrossRef]

- Yamanaka, T.; Fang, S.J.; Lin, H.-C.; Snyder, J.P.; Helms, C.R. Correlation between Inversion Layer Mobility and Surface Roughness Measured by AFM. IEEE Electron Device Lett. 1996, 17, 178–180. [Google Scholar] [CrossRef]

- Pirovano, A.; Lacaita, A.L.; Ghidini, G.; Tallarida, G. On the Correlation between Surface Roughness and Inversion Layer Mobility in Si-MOSFETs. IEEE Electron Device Lett. 2000, 21, 34–36. [Google Scholar] [CrossRef]

- Matsumoto, Y.; Uemura, Y. Scattering Mechanism and Low Temperature Mobility of MOS Inversion Layers. Jpn. J. Appl. Phys. 1974, 13, 367. [Google Scholar] [CrossRef]

- Sze, S.M.; Ng, K.K. Physics of Semiconductor Devices, 3rd ed.; Wiley-Interscience: Hoboken, NJ, USA, 2007; ISBN 978-0-471-14323-9. [Google Scholar]

- Sun, S.C.; Plummer, J.D. Electron Mobility in Inversion and Accumulation Layers on Thermally Oxidized Silicon Surfaces. IEEE Trans. Electron Devices 1980, 27, 1497–1508. [Google Scholar] [CrossRef]

- Takagi, S.; Toriumi, A.; Iwase, M.; Tango, H. On the Universality of Inversion Layer Mobility in Si MOSFET’s: Part I-Effects of Substrate Impurity Concentration. IEEE Trans. Electron Devices 1994, 41, 2357–2362. [Google Scholar] [CrossRef]

- Arora, N.D.; Gildenblat, G.S. A Semi-Empirical Model of the MOSFET Inversion Layer Mobility for Low-Temperature Operation. IEEE Trans. Electron Devices 1987, 34, 89–93. [Google Scholar] [CrossRef]

- Sabnis, A.G.; Clemens, J.T. Characterization of the Electron Mobility in the Inverted <100> Si Surface. In Proceedings of the 1979 International Electron Devices Meeting, Washington, DC, USA, 3–5 December 1979; pp. 18–21. [Google Scholar]

- Noguchi, M.; Iwamatsu, T.; Amishiro, H.; Watanabe, H.; Miura, N.; Kita, K.; Yamakawa, S. Carrier Transport Properties in Inversion Layer of Si-Face 4H–SiC MOSFET with Nitrided Oxide. Jpn. J. Appl. Phys. 2019, 58, 031004. [Google Scholar] [CrossRef]

- Noguchi, M.; Watanabe, T.; Watanabe, H.; Kita, K.; Miura, N. Comparative Study of Hall Effect Mobility in Inversion Layer of 4H-SiC MOSFETs With Nitrided and Phosphorus-Doped Gate Oxides. IEEE Trans. Electron Devices 2021, 68, 6321–6329. [Google Scholar] [CrossRef]

- Das, S.; Isaacs-Smith, T.; Ahyi, A.; Kuroda, M.A.; Dhar, S. High Temperature Characteristics of Nitric Oxide Annealed P-Channel 4H-SiC Metal Oxide Semiconductor Field Effect Transistors. J. Appl. Phys. 2021, 130, 225701. [Google Scholar] [CrossRef]

- Noguchi, M.; Iwamatsu, T.; Amishiro, H.; Watanabe, H.; Kita, K.; Miura, N. Coulomb-Limited Mobility in 4H-SiC MOS Inversion Layer as a Function of Inversion-Carrier Average Distance from MOS Interface. Jpn. J. Appl. Phys. 2020, 59, 051006. [Google Scholar] [CrossRef]

- Uhnevionak, V.; Burenkov, A.; Strenger, C.; Ortiz, G.; Bedel-Pereira, E.; Mortet, V.; Cristiano, F.; Bauer, A.J.; Pichler, P. Comprehensive Study of the Electron Scattering Mechanisms in 4H-SiC MOSFETs. IEEE Trans. Electron Devices 2015, 62, 2562–2570. [Google Scholar] [CrossRef]

- Potbhare, S.; Goldsman, N.; Lelis, A.; McGarrity, J.M.; McLean, F.B.; Habersat, D. A Physical Model of High Temperature 4H-SiC MOSFETs. IEEE Trans. Electron Devices 2008, 55, 2029–2040. [Google Scholar] [CrossRef]

- Takagi, S.; Toriumi, A.; Iwase, M.; Tango, H. On the Universality of Inversion Layer Mobility in Si MOSFET’s: Part II-Effects of Surface Orientation. IEEE Trans. Electron Devices 1994, 41, 2363–2368. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Das, S.; Zheng, Y.; Ahyi, A.; Kuroda, M.A.; Dhar, S. Study of Carrier Mobilities in 4H-SiC MOSFETS Using Hall Analysis. Materials 2022, 15, 6736. https://doi.org/10.3390/ma15196736

Das S, Zheng Y, Ahyi A, Kuroda MA, Dhar S. Study of Carrier Mobilities in 4H-SiC MOSFETS Using Hall Analysis. Materials. 2022; 15(19):6736. https://doi.org/10.3390/ma15196736

Chicago/Turabian StyleDas, Suman, Yongju Zheng, Ayayi Ahyi, Marcelo A. Kuroda, and Sarit Dhar. 2022. "Study of Carrier Mobilities in 4H-SiC MOSFETS Using Hall Analysis" Materials 15, no. 19: 6736. https://doi.org/10.3390/ma15196736

APA StyleDas, S., Zheng, Y., Ahyi, A., Kuroda, M. A., & Dhar, S. (2022). Study of Carrier Mobilities in 4H-SiC MOSFETS Using Hall Analysis. Materials, 15(19), 6736. https://doi.org/10.3390/ma15196736