A New Cell Topology for 4H-SiC Planar Power MOSFETs for High-Frequency Switching

Abstract

:1. Introduction

2. Device Design and Fabrication

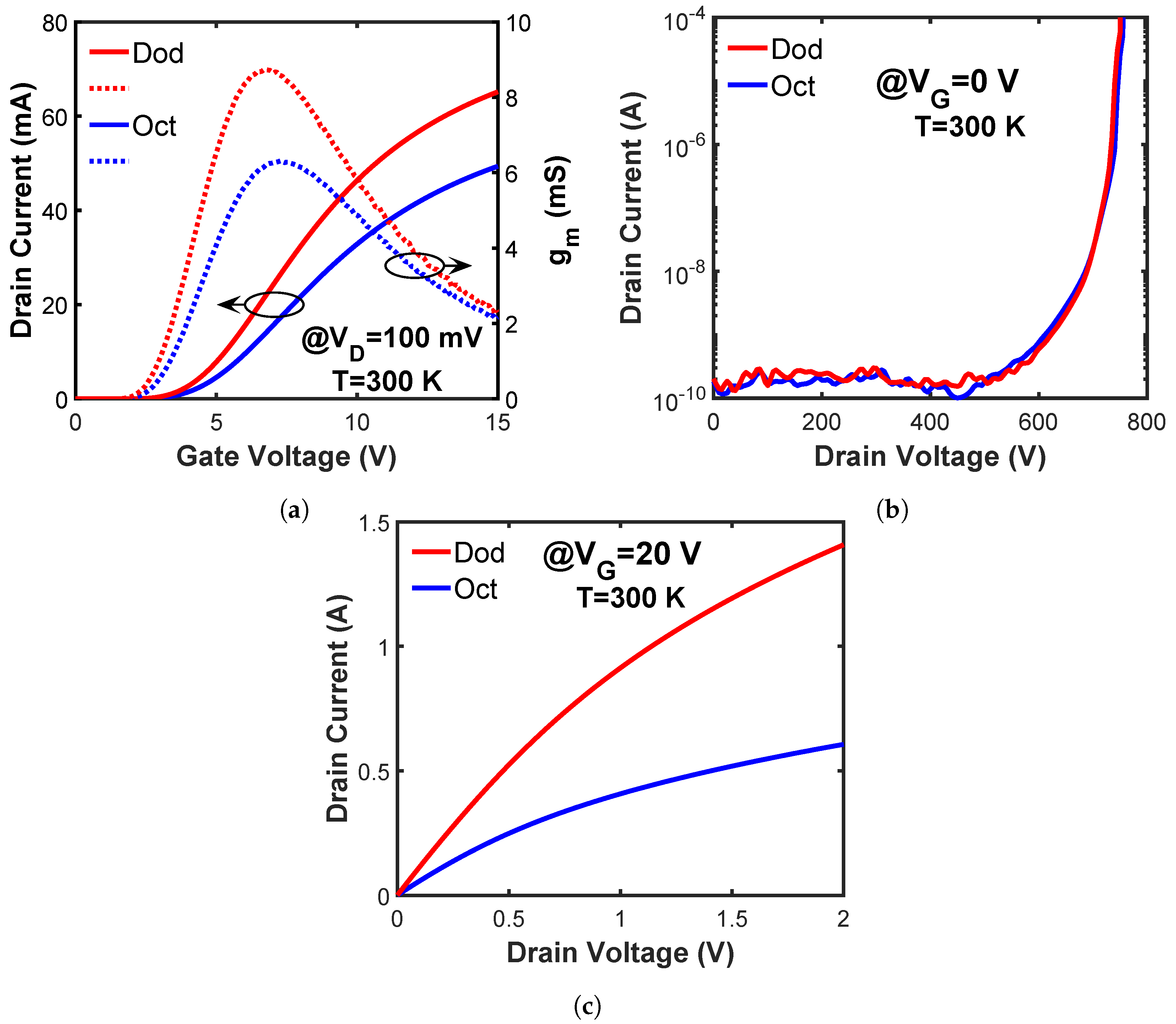

3. Experimental Results and Discussion

3.1. Statistic Performance

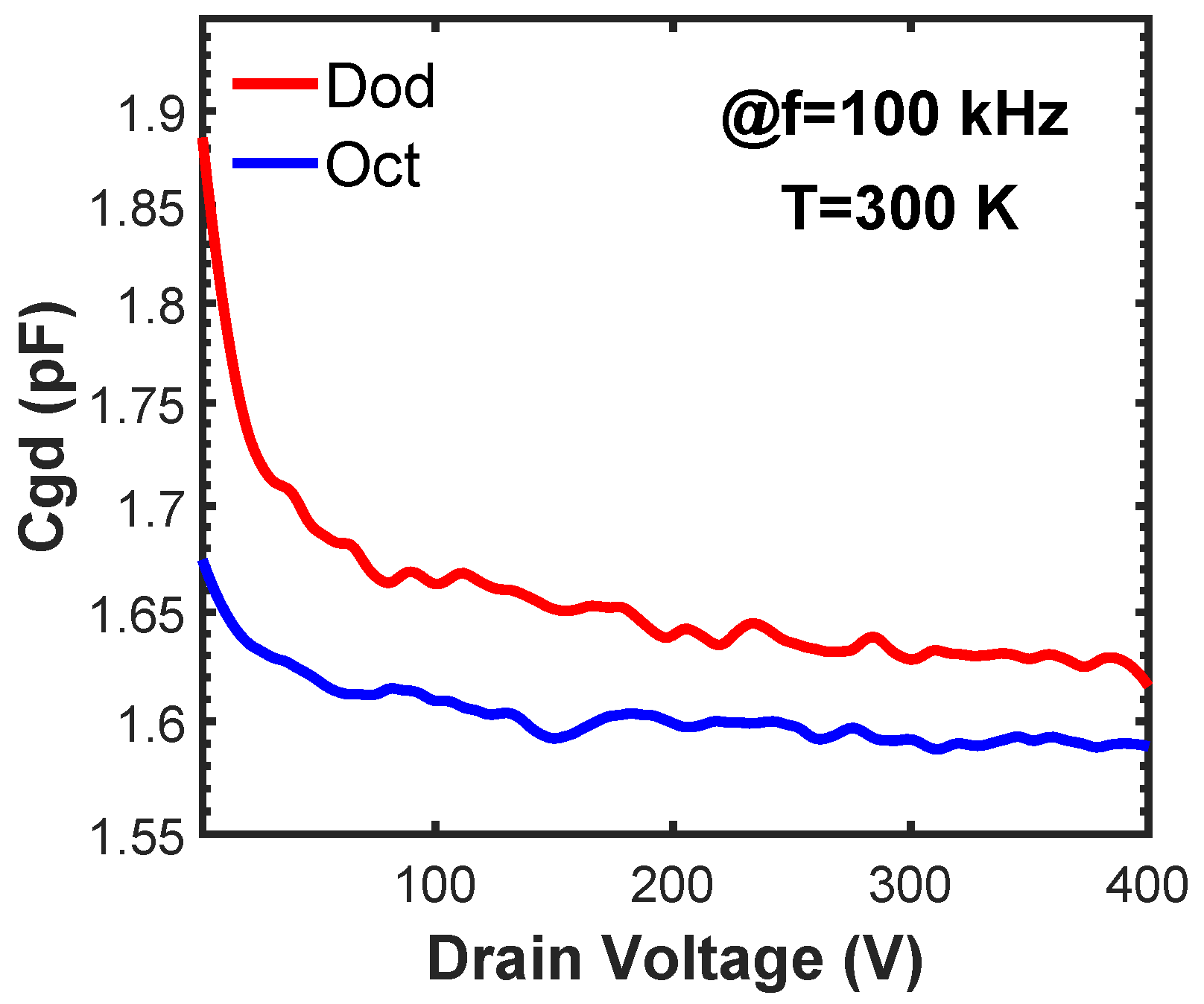

3.2. Dynamic Performance

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| SiC | Silicon Carbide |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor |

| JFET | Junction Field-Effect Transistor |

| JBSFET | Junction Barrier Schottky (JBS) diode-integrated MOSFET |

| HF-FOM | High-Frequency Figure of Merit |

| DPT | Double-Pulse Test |

References

- Camacho, A.P.; Sala, V.; Ghorbani, H.; Martinez, J.L.R. A novel active gate driver for improving SiC MOSFET switching trajectory. IEEE Trans. Ind. Electron. 2017, 64, 9032–9042. [Google Scholar] [CrossRef]

- Hazra, S.; De, A.; Cheng, L.; Palmour, J.; Schupbach, M.; Hull, B.A.; Allen, S.; Bhattacharya, S. High switching performance of 1700-V, 50-A SiC power MOSFET over Si IGBT/BiMOSFET for advanced power conversion applications. IEEE Trans. Power Electron. 2015, 31, 4742–4754. [Google Scholar]

- Kimoto, T. Material science and device physics in SiC technology for high-voltage power devices. Jpn. J. Appl. Phys. 2015, 54, 040103. [Google Scholar] [CrossRef]

- Baliga, B.J. Power semiconductor device figure of merit for high-frequency applications. IEEE Electron Device Lett. 1989, 10, 455–457. [Google Scholar] [CrossRef]

- Wang, H.; Wang, F.; Zhang, J. Power semiconductor device figure of merit for high-power-density converter design applications. IEEE Trans. Electron Devices 2007, 55, 466–470. [Google Scholar] [CrossRef]

- Watanabe, N.; Okino, H.; Shima, A. Impact of Cell Layout on On-state and Dynamic Characteristics of N-channel SiC IGBTs. In Proceedings of the 2022 IEEE 34th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vancouver, BC, Canada, 22–25 May 2022; pp. 85–88. [Google Scholar]

- Agarwal, A.; Han, K.; Baliga, B.J. Impact of cell topology on characteristics of 600V 4H-SiC planar MOSFETs. IEEE Electron Device Lett. 2019, 40, 773–776. [Google Scholar] [CrossRef]

- Agarwal, A.; Han, K.; Baliga, B. Assessment of linear, hexagonal, and octagonal cell topologies for 650 V 4H-SiC inversion-channel planar-gate power JBSFETs fabricated with 27 nm gate oxide thickness. IEEE J. Electron Devices Soc. 2020, 9, 79–88. [Google Scholar] [CrossRef]

- Han, K.; Baliga, B. The 1.2-kV 4H-SiC OCTFET: A new cell topology with improved high-frequency figures-of-merit. IEEE Electron Device Lett. 2018, 40, 299–302. [Google Scholar] [CrossRef]

- Liu, T.; Zhu, S.; Salemi, A.; Sheridan, D.; White, M.H.; Agarwal, A.K. JFET Region Design Trade-Offs of 650 V 4H-SiC Planar Power MOSFETs. Solid State Electron. Lett. 2021, 3, 53–58. [Google Scholar] [CrossRef]

- Mukunoki, Y.; Nakamura, Y.; Konno, K.; Horiguchi, T.; Nakayama, Y.; Nishizawa, A.; Kuzumoto, M.; Akagi, H. Modeling of a silicon-carbide MOSFET with focus on internal stray capacitances and inductances, and its verification. IEEE Trans. Ind. Appl. 2018, 54, 2588–2597. [Google Scholar] [CrossRef]

- Ebihara, Y.; Ichimura, A.; Mitani, S.; Noborio, M.; Takeuchi, Y.; Mizuno, S.; Yamamoto, T.; Tsuruta, K. Deep-P encapsulated 4H-SiC trench MOSFETs with ultra low R on Q gd. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 44–47. [Google Scholar]

- Zhu, S.; Liu, T.; Fan, J.; Maddi, H.L.R.; White, M.H.; Agarwal, A.K. Effects of JFET Region Design and Gate Oxide Thickness on the Static and Dynamic Performance of 650 V SiC Planar Power MOSFETs. Materials 2022, 15, 5995. [Google Scholar] [CrossRef] [PubMed]

- Li, X.; Jiang, J.; Huang, A.Q.; Guo, S.; Deng, X.; Zhang, B.; She, X. A SiC power MOSFET loss model suitable for high-frequency applications. IEEE Trans. Ind. Electron. 2017, 64, 8268–8276. [Google Scholar] [CrossRef]

| Cell Topology | Oct | Dod | |

|---|---|---|---|

| Design parameters | Cell pitch (m) | 8.4 | 8.4 |

| Active area (mm) | 0.643 | 0.634 | |

| Channel density (m) | 0.113 | 0.181 | |

| JFET density | 0.034 | 0.055 | |

| Experimental results | (V) | 4.09 ± 0.09 * | 4.35 ± 0.10 |

| BV (V) @ = 100 A | 756.3 ± 22.6 | 753.4 ± 23.6 | |

| (mcm) @ = 1.5 V | 24.4 ± 7.52 | 10.9 ± 3.06 | |

| (pF) @ = 400 V | 1.59 ± 0.01 | 1.63 ± 0.04 | |

| HF-FOM (mpF) () | 6031 ± 1896 | 2817 ± 749 | |

| dv/dt turn-on () | 6.1 | 12.5 | |

| Switching loss turn-on (J) | 29.4 | 20.1 | |

| dv/dt turn-off () | 8.4 | 10.7 | |

| Switching loss turn-off (J) | 5.7 | 4.7 | |

| Total switching loss (J) | 35.1 | 24.8 | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhu, S.; Liu, T.; Fan, J.; Salemi, A.; White, M.H.; Sheridan, D.; Agarwal, A.K. A New Cell Topology for 4H-SiC Planar Power MOSFETs for High-Frequency Switching. Materials 2022, 15, 6690. https://doi.org/10.3390/ma15196690

Zhu S, Liu T, Fan J, Salemi A, White MH, Sheridan D, Agarwal AK. A New Cell Topology for 4H-SiC Planar Power MOSFETs for High-Frequency Switching. Materials. 2022; 15(19):6690. https://doi.org/10.3390/ma15196690

Chicago/Turabian StyleZhu, Shengnan, Tianshi Liu, Junchong Fan, Arash Salemi, Marvin H. White, David Sheridan, and Anant K. Agarwal. 2022. "A New Cell Topology for 4H-SiC Planar Power MOSFETs for High-Frequency Switching" Materials 15, no. 19: 6690. https://doi.org/10.3390/ma15196690

APA StyleZhu, S., Liu, T., Fan, J., Salemi, A., White, M. H., Sheridan, D., & Agarwal, A. K. (2022). A New Cell Topology for 4H-SiC Planar Power MOSFETs for High-Frequency Switching. Materials, 15(19), 6690. https://doi.org/10.3390/ma15196690