2.1. Experimental Validation Object

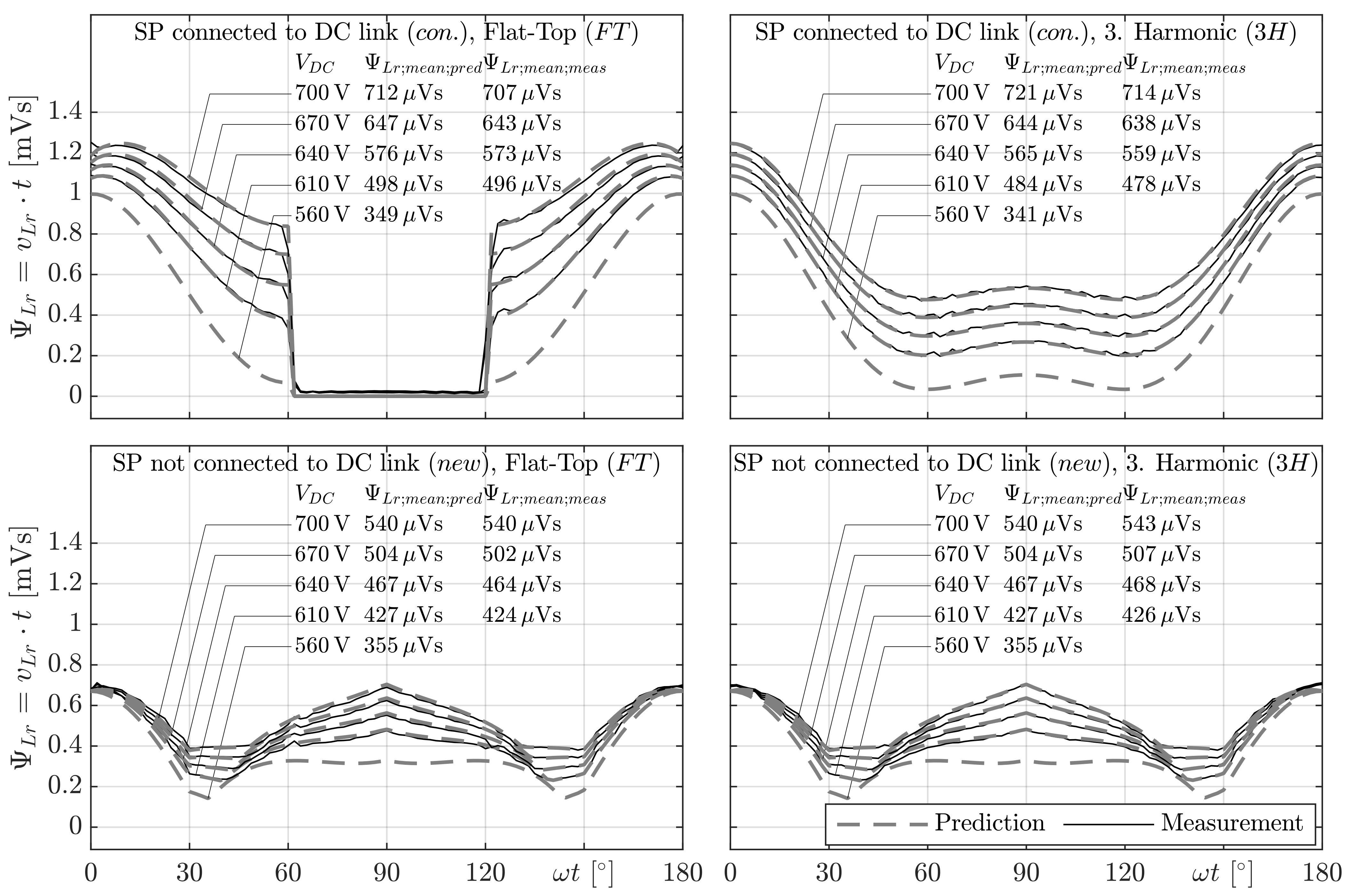

Initially, developed models introduced in [

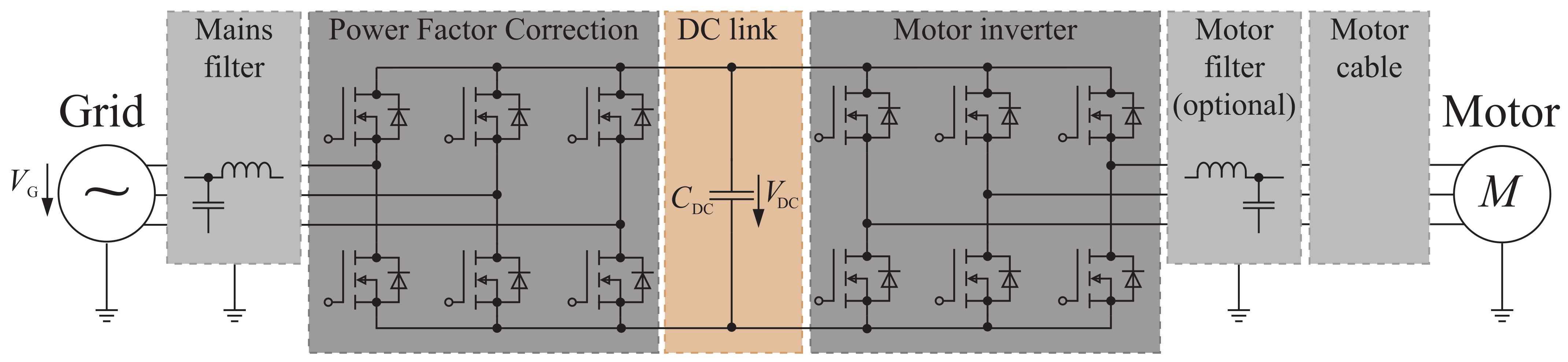

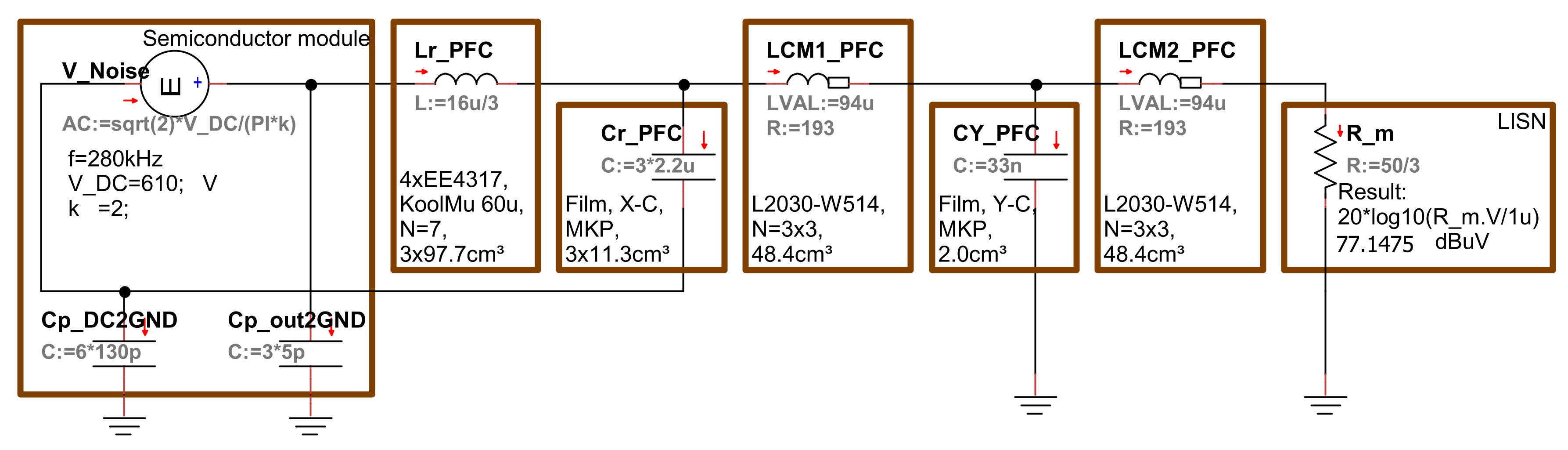

15] are compared with measurements. For the validation of the presented filter concept it is not required to operate a complete drive system as shown in

Figure 1. It is sufficient to perform the measurements on the power electronic system presented in

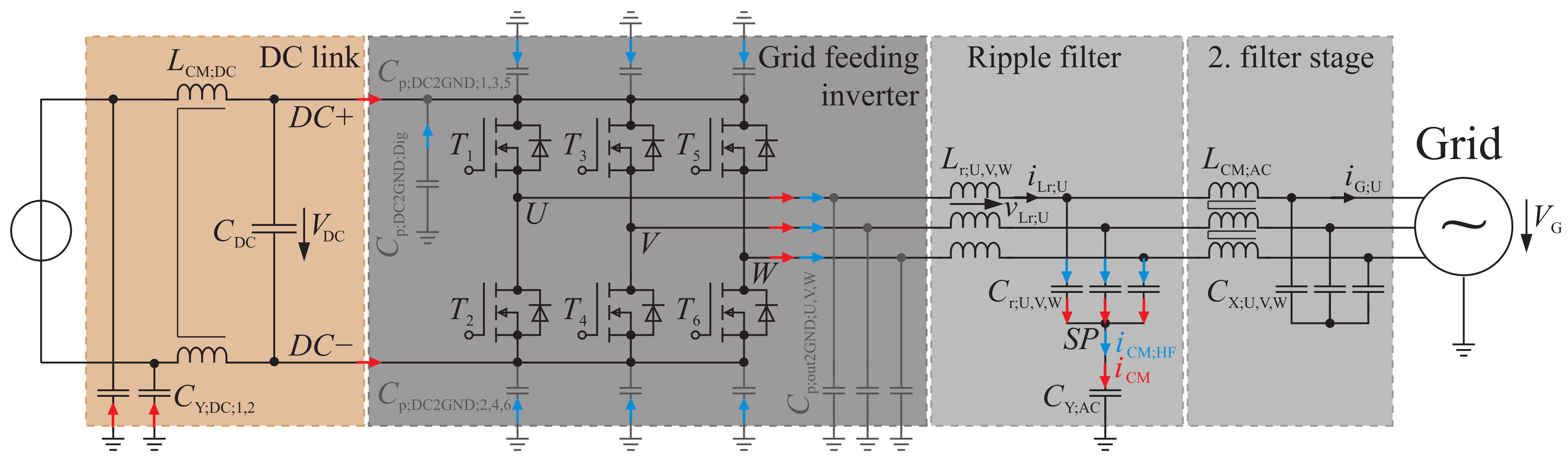

Figure 4. As necessary for the validation, the CM choke in the DC link absorbs almost the entire CM voltage-time area. One difference compared to the complete motor drive is that the load profile of the DC link CM choke regarding the flux linkage differs when the motor inverter is not operated. Consequently, the design results of this choke optimized with respect to losses would differ. Furthermore, without motor and motor cable a CM interference current path is eliminated due to the high capacitive coupling of the motor and cable to ground, which must be considered in the filter design of the complete motor drive system. Despite these differences the validation object is suitable to qualify the approach presented here. The main CM circuit is marked in red in

Figure 4 and runs from the semiconductor modules

–

through the ripple inductors

and capacitors

as well as the mains-side Y capacitor

to ground and closes through the Y capacitor on the DC side

and the CM choke

to the DC link potentials. Note that the CM capacitors in the ripple stage and the DC link are Y capacitors connected to ground. Independently of this, a CM current can also be generated without a Y capacitor via the parasitic ground capacitances, which are shown in gray in the figure, since the electrical distribution network has a ground reference.

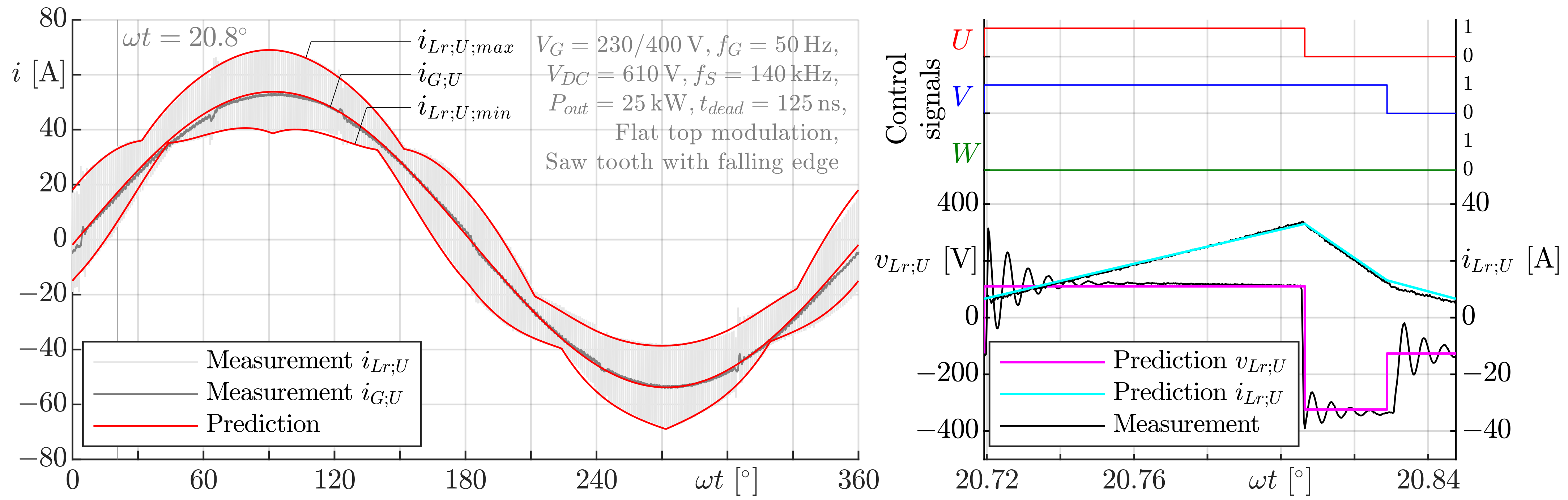

If the predicted voltage and current waveforms, the voltage-time areas of the ripple inductors and the CM choke in the DC link as well as the interference levels at the considered grid feeding inverter correspond to those measured, the methodology can also be applied to the more complex systems considered previously. Once the validity of the models has been demonstrated, a size comparison can be provided between optimized back-to-back converter system using the novel and the conventional filter topology.

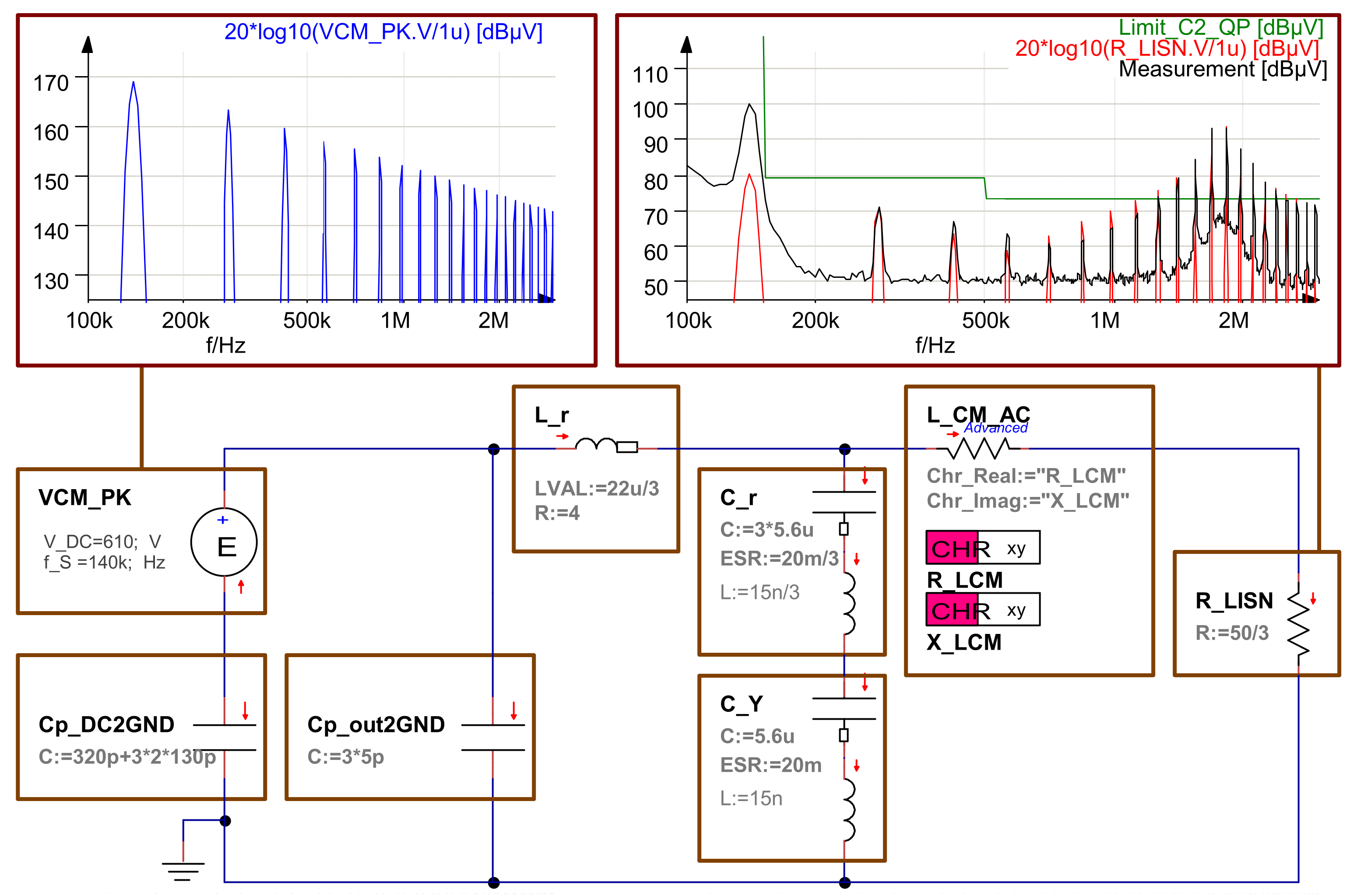

The grid feeding inverter is intended for connection to the public distribution network.

Table 1 summarizes its electrical requirements and operating parameters. The DC link capacitor, the ripple inductors and the EMC filter are designed for a switching frequency of

. As a result, EMC limits need only be met from the second harmonic at a frequency of

, which reduces the size of the filter components.

The prototype inverter used in the measurements is shown in

Figure 5. The filters are designed in such a way that their components can be placed at the bottom of the device on a PCB with the same base area as the heat sink.

Table 2 contains a list of the applied components with the relevant EMC properties. Note that most of the utilized passive components are not volume optimized.

The impedance of the CM choke on the mains side

cannot be described with frequency-independent parameters because the employed nanocrystalline core material has a strong dependence on frequency with respect to the complex permeability due to increasing eddy currents at higher frequencies. The impedance curve used in the simulations was measured with an impedance analyzer (see below) and is shown in the right diagram of

Figure 6.

The frequency dependency of all other specified parameters is not as significant (e.g., , ) or can be neglected for the modeling (e.g., , ), allowing them to be described with frequency-independent values. The parameters were determined by measurements with the impedance analyzer.

The frequency dependence of the ripple inductors’ permeability is neglected, since it drops by only at the maximum frequency used in the EMI simulations () due to the distributed air gaps in the core material. Furthermore, the winding capacitance of the ripple inductors can also be neglected in the simulations because the first parallel resonance only occurs at a frequency above .

However, it must be considered that the inductance value of the ripple inductors is current-dependent due to the utilization of powder core material KoolMu 60u from Magnetics (

https://www.mag-inc.com/Products/Powder-Cores/Kool-Mu-Cores (accessed on 19 July 2019)). On the one hand, their voltage-time area and the CM voltage-time area in the DC link CM choke are affected as a function of the load condition. In the left diagram of

Figure 6, the partially empirical equations and parameters for calculating this dependency are provided and the result is compared with the measurement performed with a power choke tester. The current dependent inductance can be predicted with very high accuracy. On the other hand, the current dependent inductance value is reflected in higher interference emissions with increasing load currents as described in the following. the company and must therefore be written with a capital M: “Magnetics”.

The interference measurements are performed at an output power of approximately and a DC link voltage of . At the operating point with the highest mains current of approximately , their inductance value drops from at zero current to . Due to the shifted phase currents of the three inverter stages the emissions does not increase in a proportional manner. Even when one ripple inductor momentarily carries a high current leading to a strongly reduced inductance, the other two inductors will at the same time carry a lower current and thus, relatively seen, maintain a higher inductance. Analyses show that the PK value increases by a maximum of and the AV value by at full load compared to the low load case.

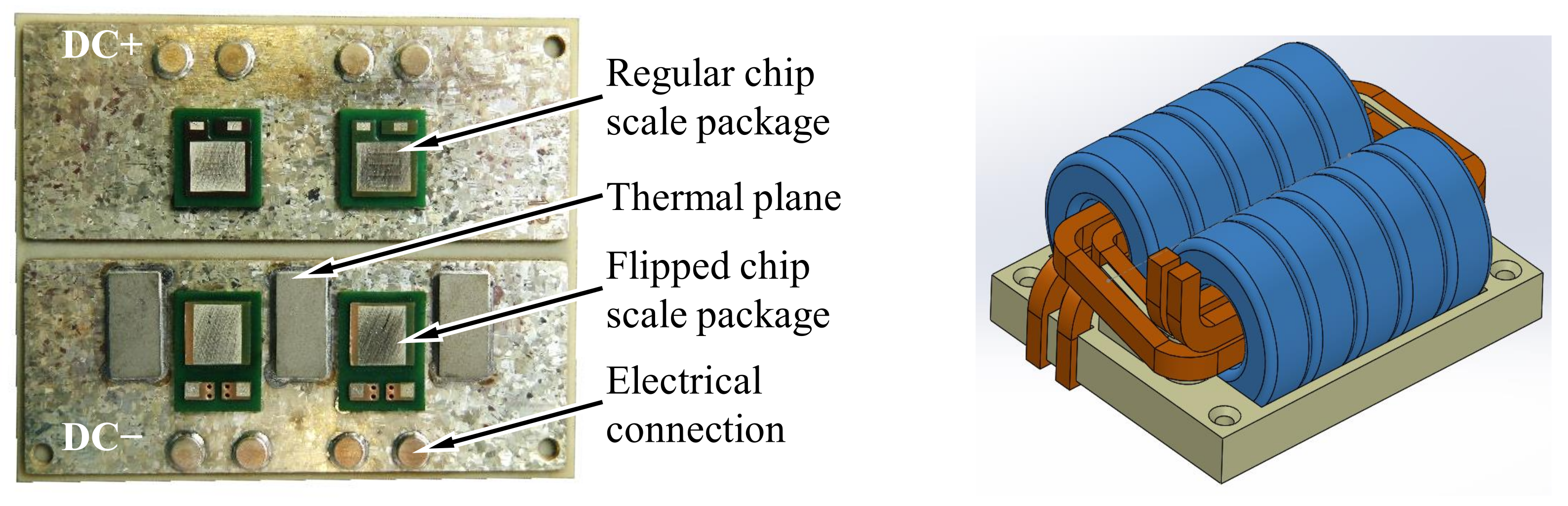

Special attention is paid to the design of the DC link CM choke, which is designed having the complete motor drive system in mind. Since it must absorb the difference in CM voltage-time areas from both converters, which is relatively high in certain operating conditions, it must be ensured that the choke does not saturate at any operating point and that it is designed for a minimum of losses. The selected core material is a loss-optimized MnZn ferrite for the applied switching frequency with a relatively high saturation flux density of

at a temperature of

(N87 from TDK). To keep the leakage inductance as low as possible, two stacks of 5 cores R38.1 × 19.05 × 12.7 are wound with 2 windings of 2 turns each as shown in the right picture of

Figure 7. The resulting low leakage inductance of

per winding including the connections to the two DC links resonates with the DC link capacitors at a frequency of approximately

. Due to the damping caused by the losses in the CM choke and especially in the DC link capacitors, which have a relatively high Equivalent Series Resistance (ESR) at this frequency, the oscillation decayed to below

of its initial amplitude after 5 oscillations following a voltage step in one of the two DC link voltages. Since the controller operates with a frequency of

, no impact on the control is to be expected. However, a load step on the motor side will cause an oscillation with the resonance frequency on the mains side. At this frequency, however, no requirements exist regarding EMC or THD. As the switching frequency is substantially higher than the resonance frequency, no oscillations due to the switching operations of the semiconductors are to be expected. This topic will be subject to further studies in the future.

For the validation object, power modules depicted in

Figure 7 have been EMC-optimized as described in [

16]. The basis for the low-inductive design are Chip-Scale Packages (CSPs) of silicon carbide (SiC) Metal–Oxide–Semiconductor Field-Effect Transistor MOSFET dies, which are also used for the component SCTW100N120G2AG from ST in HiP247 package (

https://www.st.com/en/power-transistors/sctw100n120g2ag.html (accessed on 7 October 2020)). The semiconductor dies are each embedded in a small circuit board. One module features four such SiC switches, two in parallel for both High Side (HS) and Low Side (LS).

In the first assembly step, the drain contact of the chip is sintered onto a copper foil. The contacting of the gate and the source is realized with microvias in PCB technology. The LS switches are flipped with respect to their relative position to the Direct Copper Bond (DCB). This is done in order to reduce the parasitic capacitance between the LS drain i.e., the half bridge output potential and the heat sink . To avoid imbalances with respect to the occurring parasitic capacitances, the copper areas of the and potentials on the top side of the DCB are of equal size. In first approximation the capacitance between top and bottom copper areas can be simply determined using the equation for the capacitance of a plate capacitor and amounts to (area , the ceramic material silicon nitride is a dielectric with and has a thickness of ).

Thermal planes, visible in the picture near the LS switches, are added in order to reduce the thermal resistance between the LS chips and the heat sink: Since the LS switches are flipped, their sinter connection, which have a much better thermal conductivity than the microvias, is not facing the DCB but the inverter PCB. The negative impact this has on the thermal properties is accepted in this case for the benefit of a decreased parasitic capacitance. The additional thermal planes are thermally highly conductive cuboids designed to alleviate thermal problems by transporting heat away from top of the CSPs via copper paths on the inverter PCB back down to the DCB.

The top side of the module is not wire bonded, but soldered onto a PCB. Therefore, the commutation and gate inductances are extraordinarily low allowing for extremely fast switching. Using the loss simulation approach in [

17] the switching losses can be predicted neglecting the parasitic module inductances. Hence, it can be concluded that the switching speed is limited exclusively by the semiconductor properties (internal gate resistance, capacitances and transfer characteristic).

2.3. Filter Design Assumptions

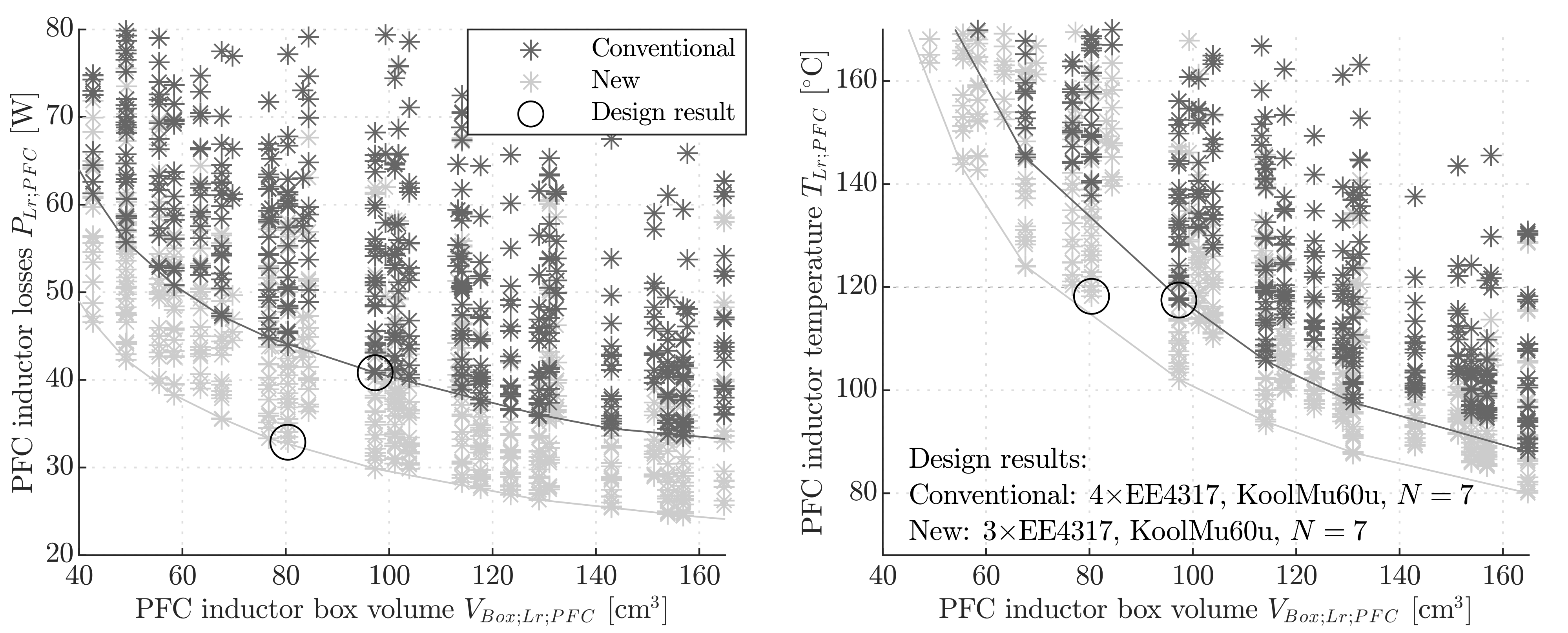

After providing experimental evidence of the accuracy of the existing prediction methodology, conventional and novel filter topologies are compared using computational methods. As already mentioned, the analytical calculation tool presented in [

15] is used for the calculations. It enables a large number of design possibilities to be calculated in a short time.

The models predict the operating behavior of back-to-back converter systems with AFE according to

Figure 2 and

Figure 3 respectively, assumed to have a rated power of

and being connected to the public distribution network. Mains phase Root Mean Square (RMS) voltage is

, mains frequency is

. The maximum DC link voltage is set to

, a switching frequency of

and flat-top modulation is considered.

For thermal modeling it is assumed, that the ambient temperature is maximum and that the winding temperature of the inductors and CM chokes must not exceed . Furthermore, it is assumed that the entire surface of the inductors can dissipate a power of to the environment via forced air cooling.

The ripple inductors on the PFC and motor side as well as the DC link CM choke can be designed independently of all other passive components because they are configured according to the lowest losses and not according to EMC attenuation characteristics. Since PFC ripple inductors always absorb the difference between mains and DC link voltage, losses are maximum at full load. The output voltage on the motor side can be varied over a wide range, resulting in the voltage-time area of the associated ripple inductors being much higher than that of the PFC inductors. It makes sense to analyze and compare designs at the operating point of maximum losses. With the use of the analytical calculation tool mentioned above a motor voltage of and a motor current of is therefore chosen.

With respect to possible core materials, different powder materials are compared, namely the powder material KoolMu from Magnetics with relative permeability of 40, 60 and 90 and the amorphous iron based alloy material 2605SA1 Metglas (

https://metglas.com/magnetic-materials/ (accessed on 20 February 2021)). Their parameters were taken from their respective datasheets and used to calculate the core losses applying the improved generalized Steinmetz equation [

18,

19,

20]. The Steinmetz parameters are listed in

Table 3. The factor for calculation with a sinusoidal excitation

is converted for use in the generalized Steinmetz equation as described in [

20]. The dependence of the core losses on the premagnetization [

21] is neglected for simplicity. The core shapes considered for the design are limited to the standard cores available from the manufacturers. E cores are considered for the KoolMu cores and AMCC cores for the Metglas cores.

Since the permeability of the core materials strongly changes with the magnetic field strength, the dependence of the differential inductance of the inductors on the current is taken into account by the calculation tool (cf. left hand diagram of

Figure 6). To simplify the calculation of the current ripple, the average differential inductance during a switching period corresponding to the instantaneous low-frequency load current is used. The error that occurs is negligible.

A single-layer rectangular winding with wires bent over the thinner edge is used as winding, which ensures a high copper fill factor and low HF copper losses in the components. Such rectangular wires are available in a large geometric variety. Therefore, the width and height of the winding wire are automatically calculated by the calculation tool, taking into account the necessary insulation distances and manufacturability. Those are assumed to be between copper and core where the wire is surrounded by core material, where the winding runs outside the core and from one turn to the next. The frequency-dependent resistance of the winding is calculated with a 2D FEM simulation at an assumed winding temperature of . The results are used to determine the Low Frequency (LF) and HF copper losses. In this process, just the resistance in the winding part enclosed by core material is calculated. Since the HF copper losses are only a small part of the inductor losses, it is assumed that the current density distribution is identical in the winding part outside the core. To account for the copper losses in the winding part that is not enclosed by the core material, the resistance calculated with the FEM is multiplied by the winding factor. This is calculated analytically previously and specifies the ratio of the actual length of the winding wire to the length considered in the simulation.

For the design of the CM choke in the DC link it is important to note that there is no operating point at which all designed chokes have the maximum losses. In the case of motor start-up, core losses occur almost exclusively, because the current in the DC link is very low due to the low output voltage. At this operating point, the core losses are at a maximum. A CM choke optimized for this operating point would have a large number of turns and a winding wire with a low copper cross-section. In contrast to this, however, at maximum output power the copper losses are maximum, but the potential for core losses is not as pronounced. Therefore, several operating points must be considered for the design of the CM choke in the DC link.

Table 4 shows the operating points used for the choke design.

Standard ring cores made of nanocrystalline core material from Vacuumschmelze (

https://vacuumschmelze.com/products/Inductive-Components-and-Cores/Amorphous-and-Nanocrystalline-Cores (accessed on 17 February 2021)) are used in the design. Since the geometric dimensions are not very fine-grained, not as many variants as for the ripple inductor design can be calculated. In the loss modeling, the HF copper losses are neglected because the switching-frequency current is very low due to the high inductance value of the CM choke. The core losses are calculated using the generalized Steinmetz equation with the parameters specified in

Table 3. The low-frequency copper losses result from the determined DC resistance of the flexible copper winding wire at a temperature of

and the DC link current. The latter and the voltage-time area that the CM choke must absorb are determined using the calculation tool presented in [

15]. Furthermore, it must be ensured that the core material is not saturated at any operating point. It is also taken into account that the CM voltages are load dependent due to the current dependence of the differential inductance of the ripple inductors (cf.

Section 3.1 and

Section 3.2).

For the EMC filter design the following assumptions are made. Since the switching frequency is selected with

and EMC limits values exist from a frequency of

, the filters are designed for the interference levels at the second harmonic of the switching frequency. The interference excitation is considered to be a square wave voltage with a voltage step corresponding to the DC link voltage

and the highest possible interference voltage value for the harmonic under consideration. The Fourier transformed value for these assumptions results in the PK interference voltage in the frequency domain

:

where

k is the number of the harmonic which is 2 for the design frequency of

.

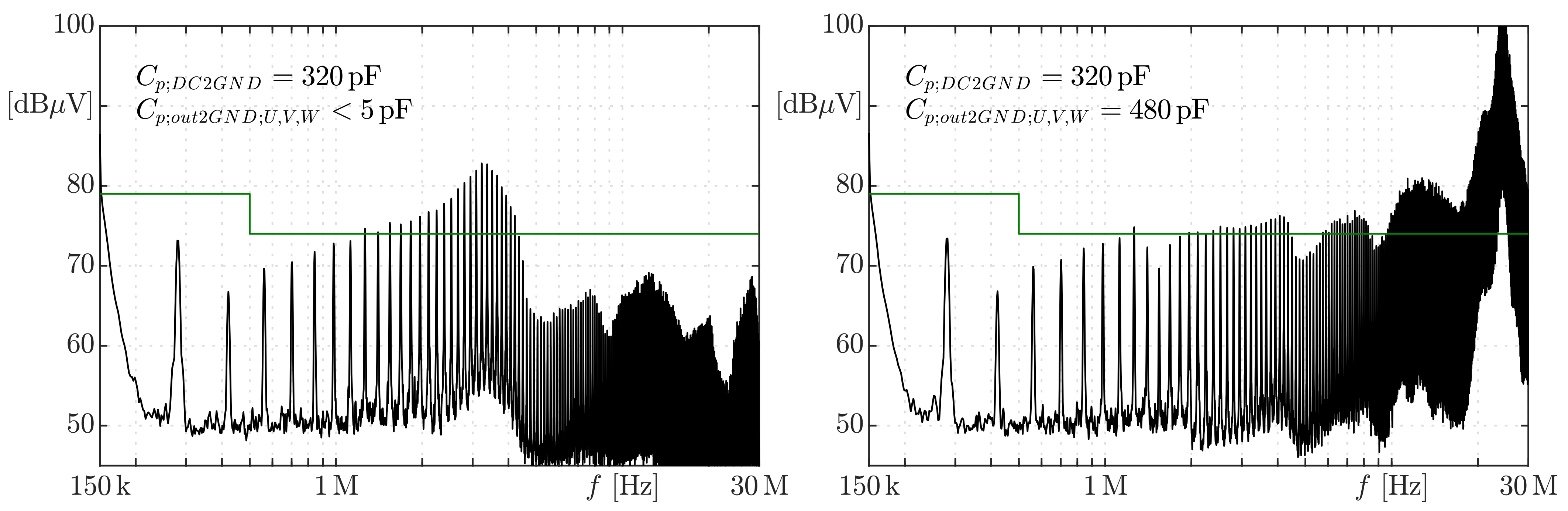

In order to comply with the EMC regulation limit values on the mains side according to IEC 61800-3 Class C2, further filter components are required in addition to the ripple filter. For the frequency of the PK limit value is . To enable the cable shield to be eliminated on the motor side, the PK interference voltage must not exceed in the frequency range 150– in accordance with the CISPR 14 standard. For this purpose, the interference voltage on the motor side is measured at an input impedance of the measuring device of .

The EMC filters are designed according to the PK value. Although the PK and AV values differ by only about

for a LF sinusoidal excitation, the limits according to IEC 61800-3 Class C2 differ by

. However, the AV value of the interference can be reduced to the desired difference to the PK value using frequency dithering according to [

22,

23]. Since the measurement bandwidth of

is much smaller than the average switching frequency, the AV value can be reduced widely by more than

. The PK value cannot be influenced by frequency dithering.

For the size comparison, only the CM filter volume is considered. It is assumed that EMC optimized power modules are utilized. For the conventional topology, this means a minimum ground capacitance of the half-bridge output nodes

according to the design rules in [

16]. In contrast, in the case of using the CM filter concept with the CM choke in the DC link, the parasitic capacitances of the DC link potentials

must be minimized. In the simulations, it is assumed that the module layout is optimized to reduce these capacitances to

per phase. For the other parasitic ground capacitances of the semiconductor module, a total capacitance of

is considered.

As described in [

14] the overall capacitance value of all Y capacitors on the mains side must be limited due to safety requirements to a total value of

. Behind the ripple inductors on the mains and motor side respectively, X capacitors with non-restricted capacitance value can be used for CM filtering because they do not have to be connected to the ground potential. The CM capacitors

and

in

Figure 2 and

Figure 3 can be omitted. The three capacitors

and

, respectively, are used on each side, each connected to one of the three phases. Thus they have an effect for filtering the CM and DM interferences. Their connection between the mains and motor sides when using the new filter topology or to the DC link potential when using the conventional filter topology must be very low inductive. Assuming three X capacitors with a capacitance value of

each and a parasitic inductance of

, the impedance of the CM current path is determined exclusively by the inductance from the fourth harmonic on.

The required size of the DM filter is not influenced by the components of the CM filter in this case. Although leakage inductances of the CM chokes have an influence on the DM attenuation, but in this case they have such a minor influence with values in the range of only 100– that they can be neglected. To minimize the DM filter, additional DM filter chokes are needed to reduce the size of the X capacitors.

The design is done with simple circuit simulation with the simulation program Portunus (

https://www.adapted-solutions.com/en/home-englisch/ (accessed on 28 February 2021)). Due to the limited number of available cores made of nanocrystalline core material from Vacuumschmelze, no calculation with the optimization tool for the CM filter is required.

As almost the entire voltage-time area is absorbed by the CM choke in the DC link or by the ripple inductors, and outside the ripple stages the ripple currents are negligible, only the LF copper losses are considered for further required CM chokes. The inductance and resistance values of the CM chokes are calculated according to the cross-section and path length of the utilized core, the complex permeability of the nanocrystalline core material at the design frequency of , as well as the number of turns.