A Systematic Study on the Harmonic Overlap Effects for DC/AC Converters under Low Switching Frequency Modulation

Abstract

1. Introduction

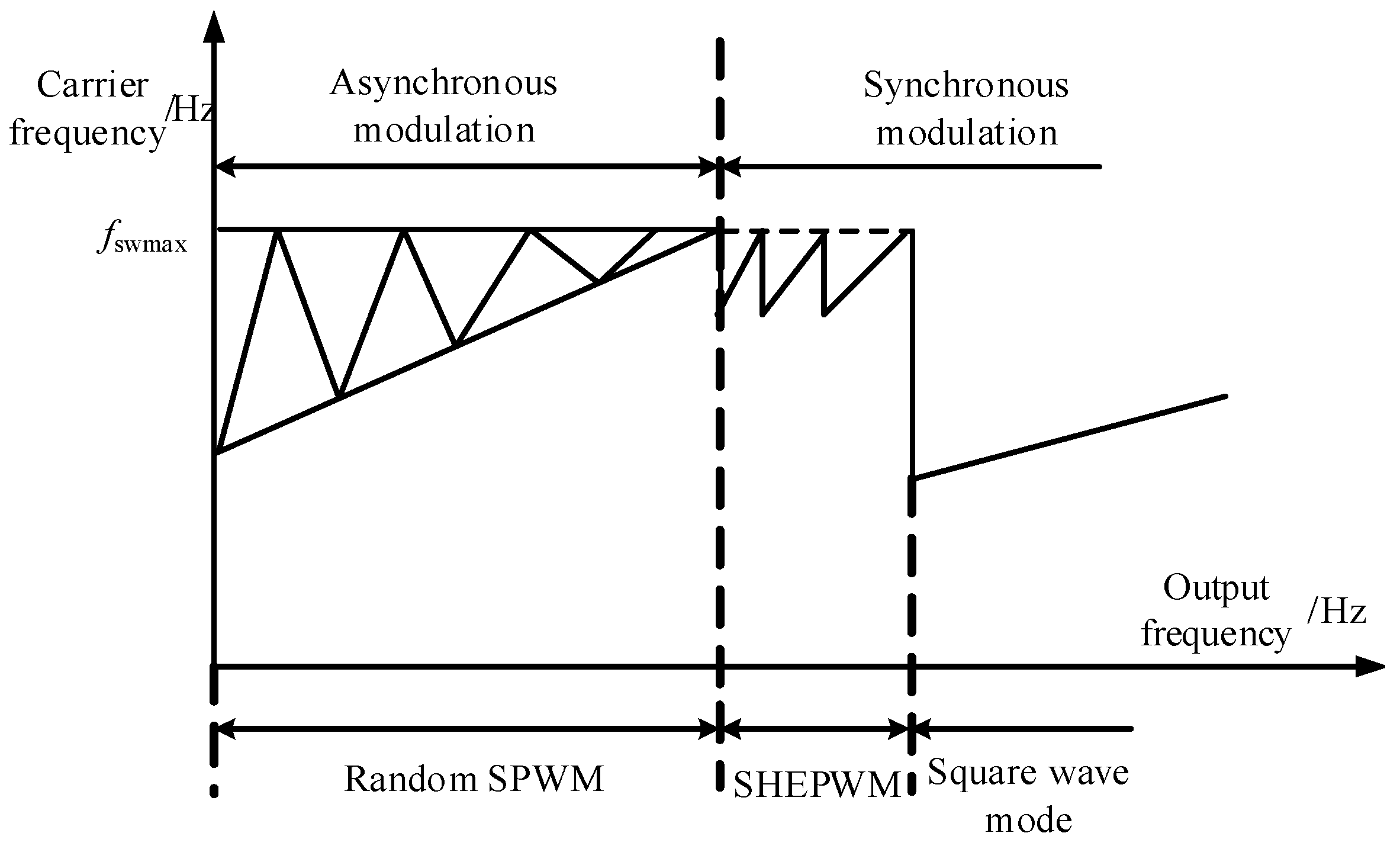

2. Preliminaries on the Classic Two-Level SPWM

- When Cr is an odd number, it can ensure that the pulses are symmetrical around the zero crossing points in one period. The spectrum of the PWM output will be free of dc components and low order even harmonics.

- When Cr is the multiples of three, the sideband of some harmonics in the symmetrical system will be in phase. Thus, the line voltage and current will be free of these harmonics, THD will be improved [28].

- The decimal Cr will cause a subharmonic around the fundamental order [29], which is very harmful to the load. For example, in motor drive applications, it will cause severe low-frequency oscillation, which will cause great damage to the motor bearings.

3. Mechanism One—The Harmonic Overlap in DC and Fundamental Component When Cr ≤ 5

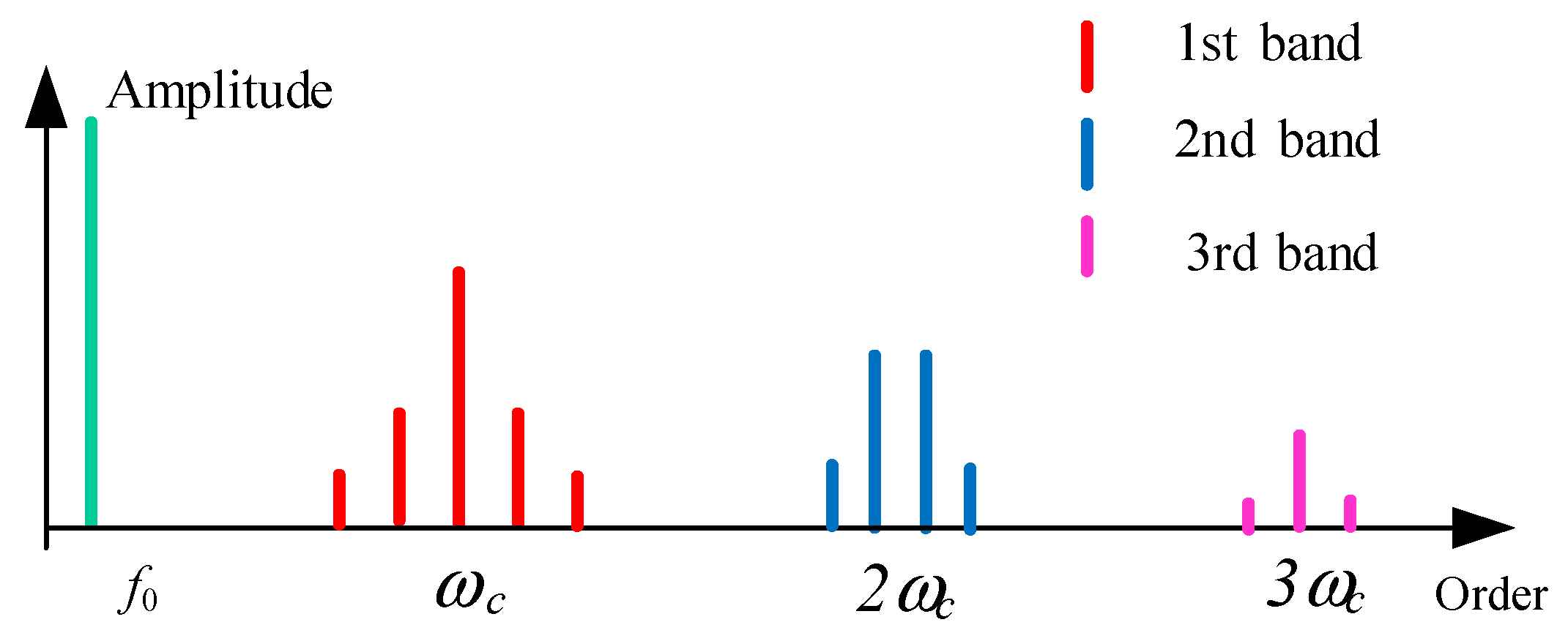

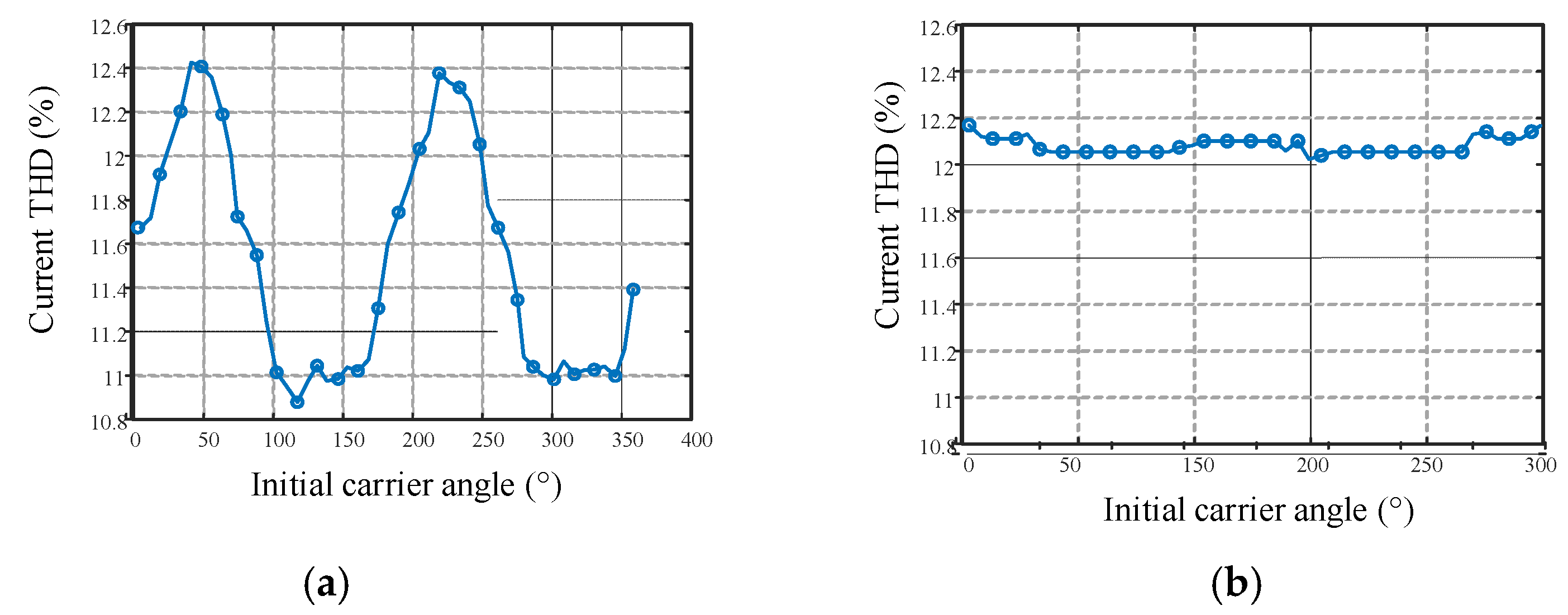

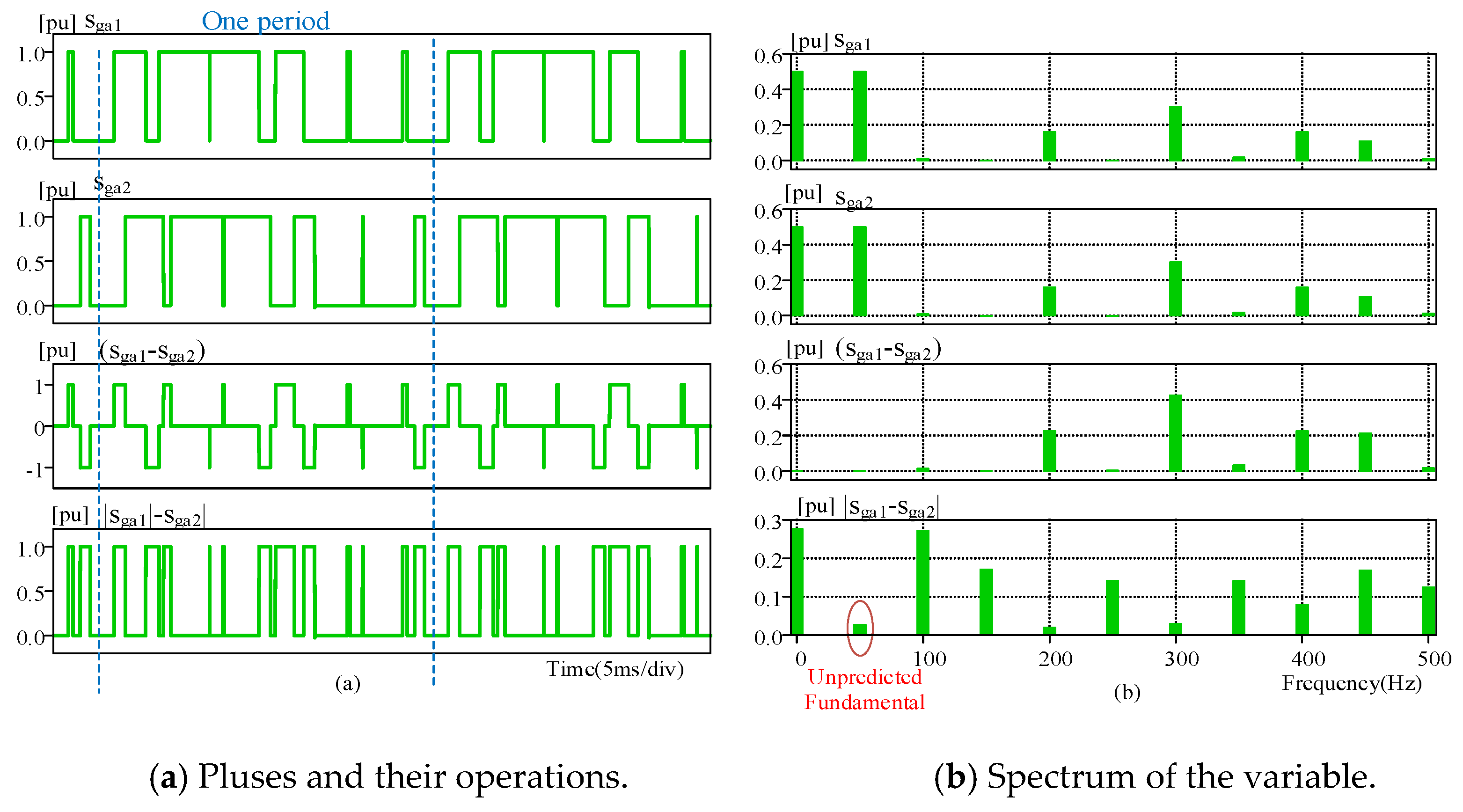

4. Mechanism Two—The Overlap in Sideband Harmonics When Cr ≤ 9

5. Mechanism Three—The Undesired Harmonic Order When Cr Nears an Even Integer

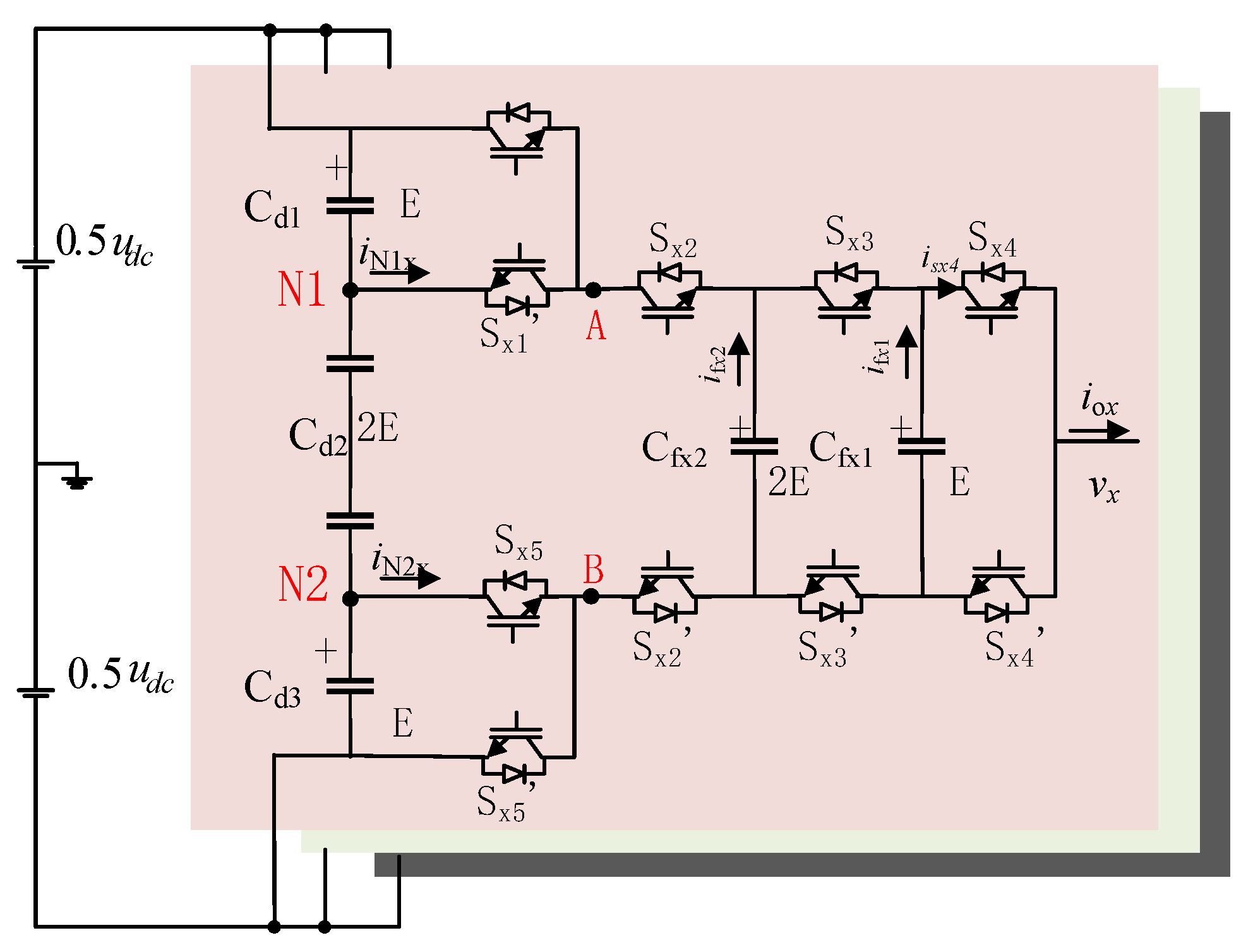

5.1. Operating Principle of the 5L-HC

5.2. Solution for Mechanism Three

5.3. Simulation of Mechanism Three and the Solution

6. Summary of Harmonic Overlap Phenomenon on Different High Power Converters

- The same mechanism on different topologies will exert different influences, so the solutions are different, which should be analyzed individually.

- There will be one or more mechanisms in one converter.

- The mechanisms do not conflict with the existing two-level and multi-level modulation theory. The traditional theory remains valid. For example, the carrier ratio should be odd (avoid even numbers), and better to be odd multiples of three in the three-phase system.

7. Concluding Remarks and Future Works

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Holtz, J.; Oikonomou, N. Fast Dynamic Control of Medium Voltage Drives Operating at Very Low Switching Frequency—An Overview. IEEE Trans. Ind. Electron. 2008, 55, 1005–1013. [Google Scholar] [CrossRef]

- Yang, S.; Wang, Y.; Song, K.; Wu, M.; Konstantinou, G. Stability and Suppression Study for Low-Frequency Oscillations in Network-Train System. IEEE Access 2020, 8, 30575–30590. [Google Scholar] [CrossRef]

- Zhang, Z.; Ge, X.; Tian, Z.; Zhang, X.; Tang, Q.; Feng, X. A PWM for Minimum Current Harmonic Distortion in Metro Traction PMSM With Saliency Ratio and Load Angle Constrains. IEEE Trans. Power Electron. 2018, 33, 4498–4511. [Google Scholar] [CrossRef]

- Fu, X.; Dai, P.; Yuan, Q.; Wu, X. Overview of Low Switching Frequency Control of High Power Three-Level Converters. Electrical Power Systems and Computers; Springer: Berlin/Heidelberg, Germany, 2011; pp. 877–883. [Google Scholar]

- Marzoughi, A.; Burgos, R.; Boroyevich, D.; Xue, Y. Design and Comparison of Cascaded H-Bridge, Modular Multilevel Converter, and 5-L Active Neutral Point Clamped Topologies for Motor Drive Applications. IEEE Trans. Ind. Appl. 2017, 54, 1404–1413. [Google Scholar] [CrossRef]

- Rodriguez, J.; Lai, J.-S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Wang, Z.; Chen, J.; Liao, K.; Xiong, J.; Zhang, K. Review on low-frequency ripple suppression methods for MMCs for medium-voltage drive applications. IET Power Electron. 2018, 11, 2403–2414. [Google Scholar] [CrossRef]

- Ronanki, D.; Williamson, S.S. Modular multilevel converters for transportation electrification: Challenges and opportunities. IEEE Trans. Transp. Electrif. 2018, 4, 399–407. [Google Scholar] [CrossRef]

- McGrath, B.P.; Teixeira, C.A.; Holmes, D.G. Optimized Phase Disposition (PD) Modulation of a Modular Multilevel Converter. IEEE Trans. Ind. Appl. 2017, 53, 4624–4633. [Google Scholar] [CrossRef]

- Ghias, A.M.Y.M.; Pou, J.; Agelidis, V.G. Voltage-Balancing Method for Stacked Multicell Converters Using Phase-Disposition PWM. IEEE Trans. Ind. Electron. 2015, 62, 4001–4010. [Google Scholar] [CrossRef]

- Li, B.; Yang, R.; Xu, D.; Wang, G.; Wang, W.; Xu, D. Analysis of the Phase-Shifted Carrier Modulation for Modular Multilevel Converters. IEEE Trans. Power Electron. 2014, 30, 297–310. [Google Scholar] [CrossRef]

- Ghazanfari, A.; Mokhtari, H.; Firouzi, M. Simple Voltage Balancing Approach for CHB Multilevel Inverter Considering Low Harmonic Content Based on a Hybrid Optimal Modulation Strategy. IEEE Trans. Power Deliv. 2012, 27, 2150–2158. [Google Scholar] [CrossRef]

- Sasongko, F.; Sekiguchi, K.; Oguma, K.; Hagiwara, M.; Akagi, H. Theory and Experiment on an Optimal Carrier Frequency of a Modular Multilevel Cascade Converter With Phase-Shifted PWM. IEEE Trans. Power Electron. 2016, 31, 3456–3471. [Google Scholar] [CrossRef]

- Shuren, K. Integrated Traction and Auxiliary Power Supply System in HXD1 Electric Locomotive. Electr. Eng. 2008, 7, 81–86. [Google Scholar]

- Mi, L.; Feng, Q.; Li, Q. Study on Structure and Strength of HXD2 Locomotive Traction Device. Electr. Drive Locomot. 2010, 4, 81–87. [Google Scholar]

- Shi, X.; Sun, L.; Wang, L. Reliability design based on fault tree approach for type HXD3 electric locomotive traction converter. Electr. Locomot. Mass Transit Veh. 2010, 15–19, 102–107. [Google Scholar]

- Manuelle, P.; Singam, B.; Siala, S. Induction motors fed by PWM MV7000 converters enhance electric propulsion performance. In Proceedings of the 2009 13th European Conference on Power Electronics and Applications, Barcelona, Spain, 8–10 September 2009; pp. 1–9. [Google Scholar]

- Sinamics Perfect Harmony GH180. Available online: https://new.siemens.com/global/en/products/drives/sinamics/medium-voltage-converters/sinamics-perfect-harmony-gh180.html (accessed on 6 April 2021).

- Sinamics Medium Voltage Drives–the Optimal Drive for Every Application. Available online: http://www.industry.siemens.com/drives/global/en/converter/mv-drives (accessed on 6 April 2021).

- Benshaw M2L 3000 Medium Voltage Variable Frequency Drives. Available online: https://benshaw.com/motor-control-solutions/medium-voltage-motor-control/variable-frequency-drives/ (accessed on 6 April 2021).

- Gupta, A.K.; Khambadkone, A.M. A Simple Space Vector PWM Scheme to Operate a Three-Level NPC Inverter at High Modulation Index Including Overmodulation Region, With Neutral Point Balancing. IEEE Trans. Ind. Appl. 2007, 43, 751–760. [Google Scholar] [CrossRef]

- Holtz, J.; Oikonomou, N. Synchronous Optimal Pulsewidth Modulation and Stator Flux Trajectory Control for Medium Voltage Drives. In Proceedings of the Fourtieth IAS Annual Meeting, Conference Record of the 2005 Industry Applications Conference, Denver, CO, USA, 13–17 November 2005; Volume 3, pp. 1748–1791. [Google Scholar]

- Holtz, J. Advanced PWM and Predictive Control—An Overview. IEEE Trans. Ind. Electron. 2015, 63, 3837–3844. [Google Scholar] [CrossRef]

- Cheng, Z.; Wu, B. A Novel Switching Sequence Design for Five-Level NPC/H-Bridge Inverters With Improved Output Voltage Spectrum and Minimized Device Switching Frequency. IEEE Trans. Power Electron. 2007, 22, 2138–2145. [Google Scholar] [CrossRef]

- Wang, Z.; Gao, C.; Chen, C.; Xiong, J.; Zhang, K. Ripple Analysis and Capacitor Voltage Balancing of Five-Level Hybrid Clamped Inverter (5L-HC) for Medium-Voltage Applications. IEEE Access 2019, 7, 86077–86089. [Google Scholar] [CrossRef]

- Holmes, D.G.; Lipo, T.A. Pulse Width Modulation for Power Converters: Principles and Practice; John Wiley & Sons: Hoboken, NJ, USA, 2003. [Google Scholar]

- Holtz, J. Pulsewidth modulation-a survey. IEEE Trans. Ind. Electron. 1992, 39, 410–420. [Google Scholar] [CrossRef]

- Bruckner, T.; Holmes, D.G. Optimal pulse-width modulation for three-level inverters. IEEE Trans. Power Electron. 2005, 20, 82–89. [Google Scholar] [CrossRef]

- Jardan, R.K.; Stumpf, P.; Bartal, P.; Varga, Z.; Nagy, I. A Novel Approach in Studying the Effects of Subharmonics on Ultrahigh-Speed AC Motor Drives. IEEE Trans. Ind. Electron. 2011, 58, 1274–1281. [Google Scholar] [CrossRef]

- Wang, K.; Xu, L.; Zheng, Z.; Li, Y. Capacitor Voltage Balancing of a Five-Level ANPC Converter Using Phase-Shifted PWM. IEEE Trans. Power Electron. 2015, 30, 1147–1156. [Google Scholar] [CrossRef]

| Product | Topology, Maximal Power (MW) | Maximal fsw/Hz | Maximal fo/Hz | Modulation Method |

|---|---|---|---|---|

| HXD1 [14] | 2L-VSC 0.817 | 250 | 116 | Piecewise SPWM to SHEPWM |

| HXD2 [15] | 2L-VSC 1.275 | 800 | 220 | Piecewise SPWM to SHEPWM |

| HXD3 [16] | 2L-VSC 1.25 | 450 | 120 | Piecewise SPWM to SHEPWM |

| ConverteamMV7000 [17] | NPC 40 | 500 | 250 | PDPWM and SVPWM |

| Perfect Harmonic [18] | CHB 132 | 250 | 120 | CPS-PWM |

| GH150 [19] | MMC 13.7 | 1000 | 120 | CPS-PWM |

| M2 L-3000 [20] | MMC 7.466 | 600 | 60 | CPS-PWM |

| Siemens SimovertD | CC 27 | Line frequency | 24 | Commutation by load and line voltage |

| GL150 [19] | LCI 75 | Line frequency | 0–105 | Commutation by load |

| Cr | Output Fundamental Voltage Amplitude (V) | Error% |

|---|---|---|

| 27 | 999.9 | 0 |

| 21 | 999.9 | −0.01 |

| 15 | 999.6 | −0.04 |

| 9 | 999.1 | −0.09 |

| 7 | 998.5 | −0.15 |

| 5 | 996.9 | −0.31 |

| 3 | 1057 | 5.7 |

| Different Submodule | 150 Hz | 350 Hz |

|---|---|---|

| Phase shift angle in different submodules (°) | Initial angle of the fundamental output voltage (°) | Initial angle of the fundamental output voltage (°) |

| 0 | 47.9 | 29.8 |

| 45 | 39.5 | 29.7 |

| 90 | 29.9 | 29.8 |

| 135 | 20.2 | 29.9 |

| 180 | 13.0 | 29.8 |

| 225 | 10.5 | 29.8 |

| 270 | 29.9 | 30.1 |

| 315 | 49.1 | 29.9 |

| Items | Simulation Parameters |

|---|---|

| Apparent power | 3 MVA |

| Dc bus voltages | 10,000 V |

| Capacitors in the dc-link | Cd1/Cd3 = 600 μF Cd2 = 300 μF |

| Flying capacitors | Cfx1 = 600 μF, Cfx2 = 300 μF |

| Switching frequency | 500 Hz |

| R–L Load | 20 Ω/10 mH |

| Mechanism | Modulation | Mechanism 1 | Mechanism 2 | Mechanism 3 | Solutions | ||

|---|---|---|---|---|---|---|---|

| Influence | |||||||

| Topology | |||||||

| Brief description: | Dc and fundamental have changed, and the subharmonics affect the motor heating | Periodic changes of THD and thermal stress of devices caused by the overlap | Nonlinear operation produces unexpected harmonics | ||||

| Corresponding Cr | Cr ≤ 5 | Cr < 10 and Cr is an integer | Cr ≤ 9 | ||||

| 2L -VSC | SPWM | Y | Y | N | 1. Synchronous PWM; 2. Optimize PWM | ||

| 3L-NPC | PDPWM | Y | Y | Y | Change Cr to decimals | ||

| CHB | CPS | Y | N | N | 1. Change Cr to decimals 2. Optimized PWM | ||

| 5L-FC | CPS | + | N | N | |||

| MMC | CPS | Y | + | N | Change Cr to decimals | ||

| 5L-HC | CPS | + | N | Y | Closed-loop feedback control combined with 3th ripple suppression | ||

| NNPC | PDPWM | Y | Y | Y | Closed-loop feedback combined with ripple suppression strategy | ||

| 5L-ANPC | Improved CPS [30] | + | N | Y | Closed loop feedback control | ||

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, Z.; He, Z.; Gao, C. A Systematic Study on the Harmonic Overlap Effects for DC/AC Converters under Low Switching Frequency Modulation. Energies 2021, 14, 2811. https://doi.org/10.3390/en14102811

Wang Z, He Z, Gao C. A Systematic Study on the Harmonic Overlap Effects for DC/AC Converters under Low Switching Frequency Modulation. Energies. 2021; 14(10):2811. https://doi.org/10.3390/en14102811

Chicago/Turabian StyleWang, Ze, Zhen He, and Chao Gao. 2021. "A Systematic Study on the Harmonic Overlap Effects for DC/AC Converters under Low Switching Frequency Modulation" Energies 14, no. 10: 2811. https://doi.org/10.3390/en14102811

APA StyleWang, Z., He, Z., & Gao, C. (2021). A Systematic Study on the Harmonic Overlap Effects for DC/AC Converters under Low Switching Frequency Modulation. Energies, 14(10), 2811. https://doi.org/10.3390/en14102811