Fully Depleted, Trench-Pinned Photo Gate for CMOS Image Sensor Applications

Abstract

1. Introduction

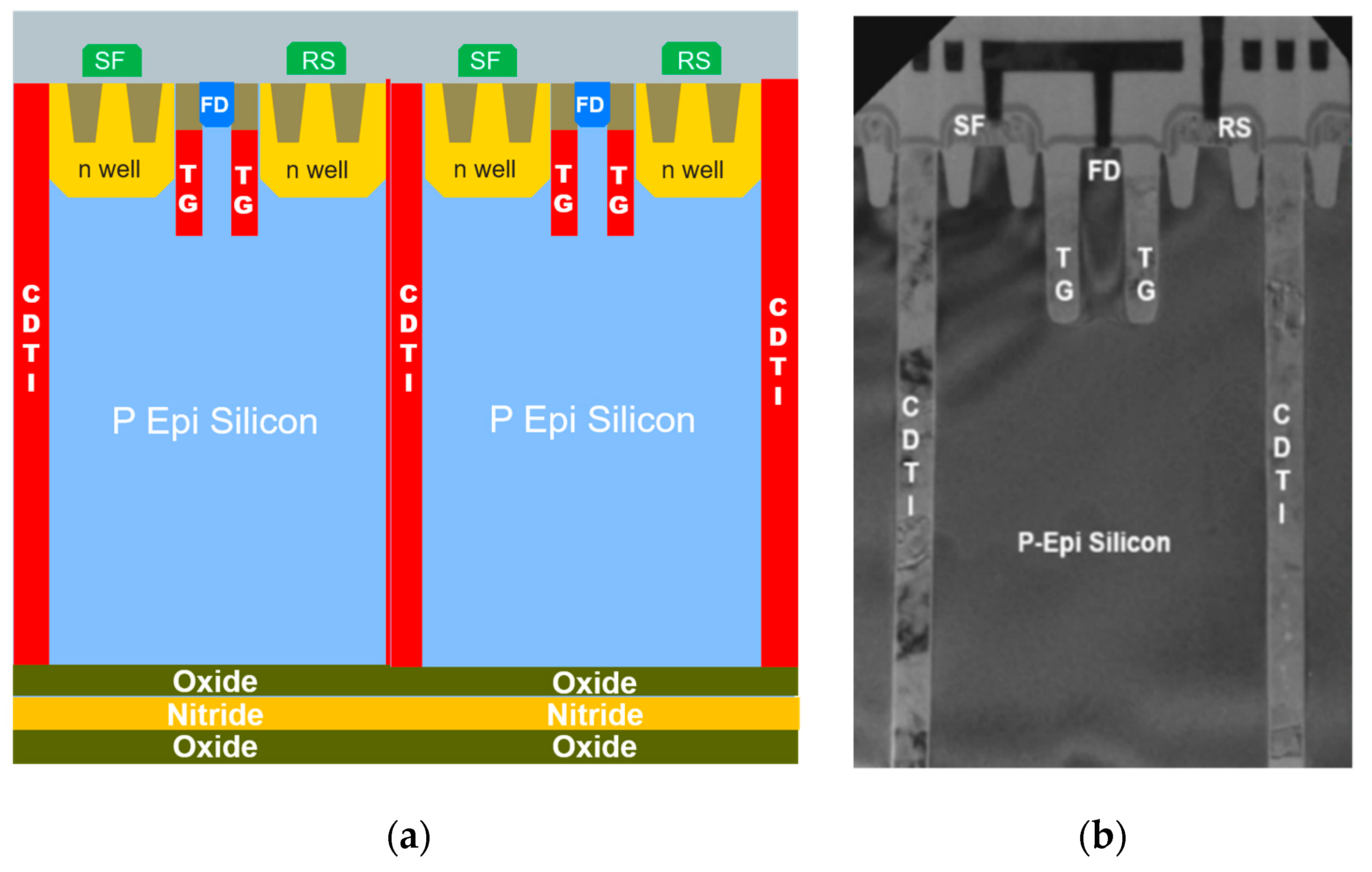

2. Pixel Description

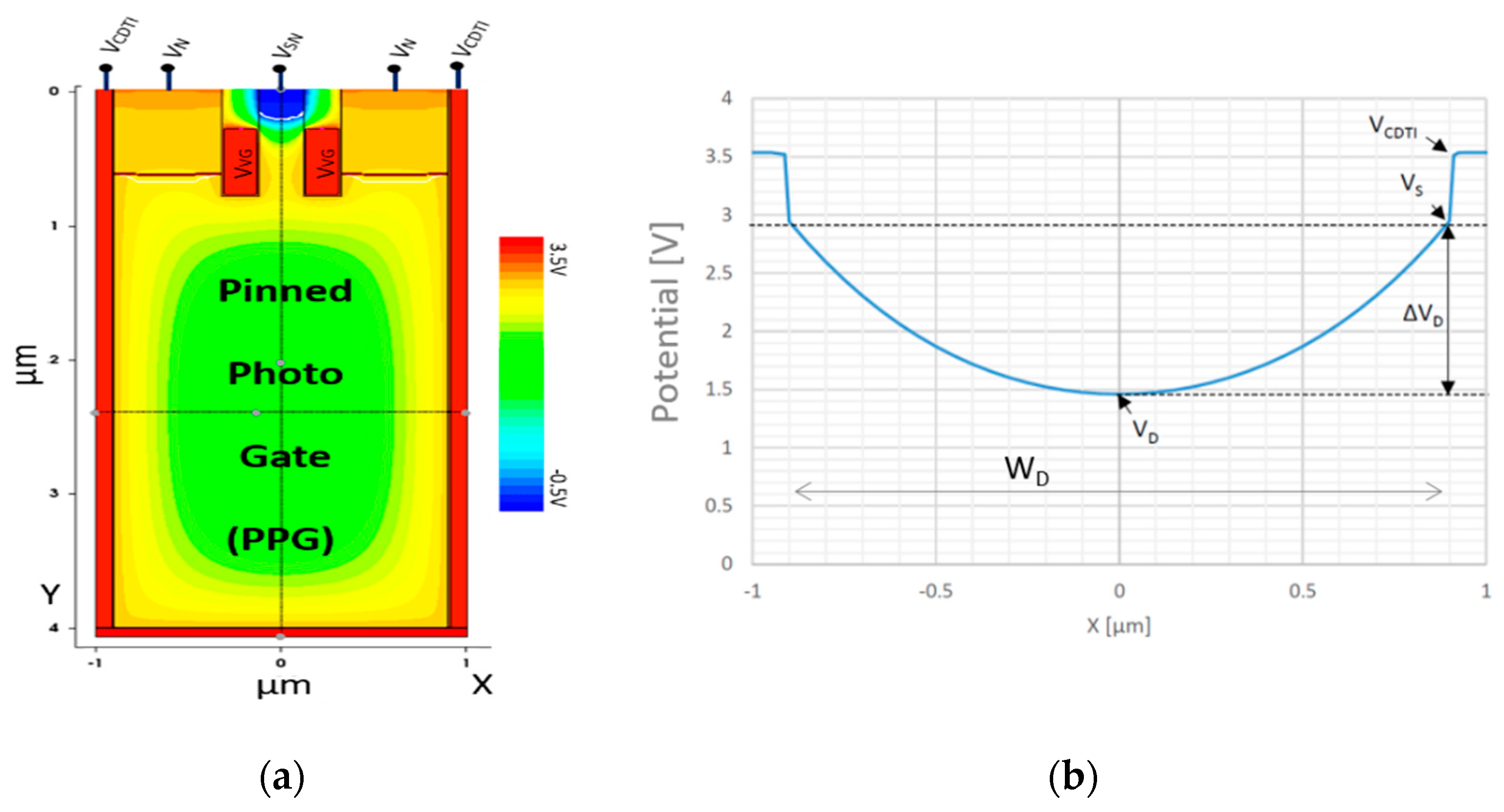

2.1. Vertical Pinned Photo Gate (PPG)

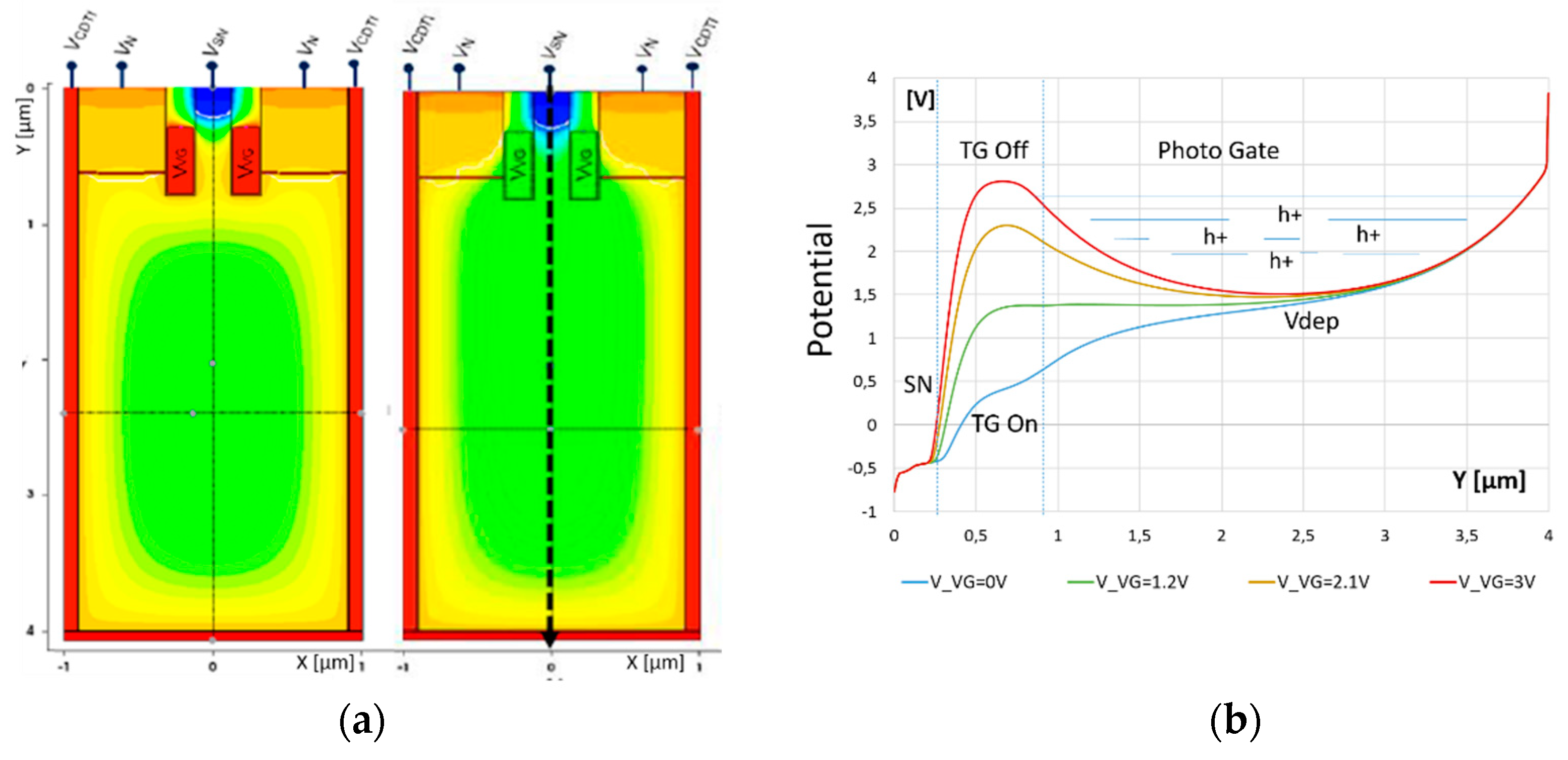

2.2. Vertical Transfer Gate

2.3. Front-Side Readout Transistors

2.4. Backside Positively Charged ONO Stack

3. Results and Discussion

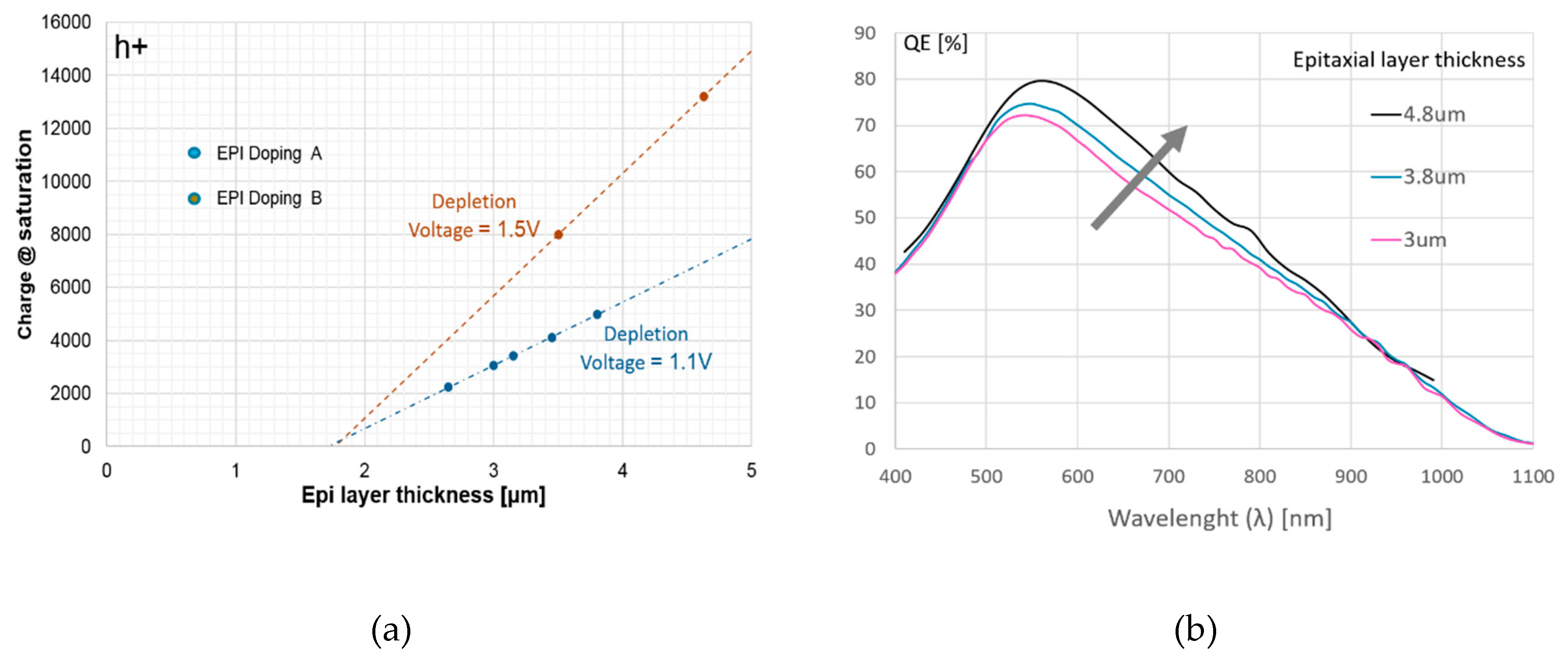

3.1. Full Well Capacity and QE

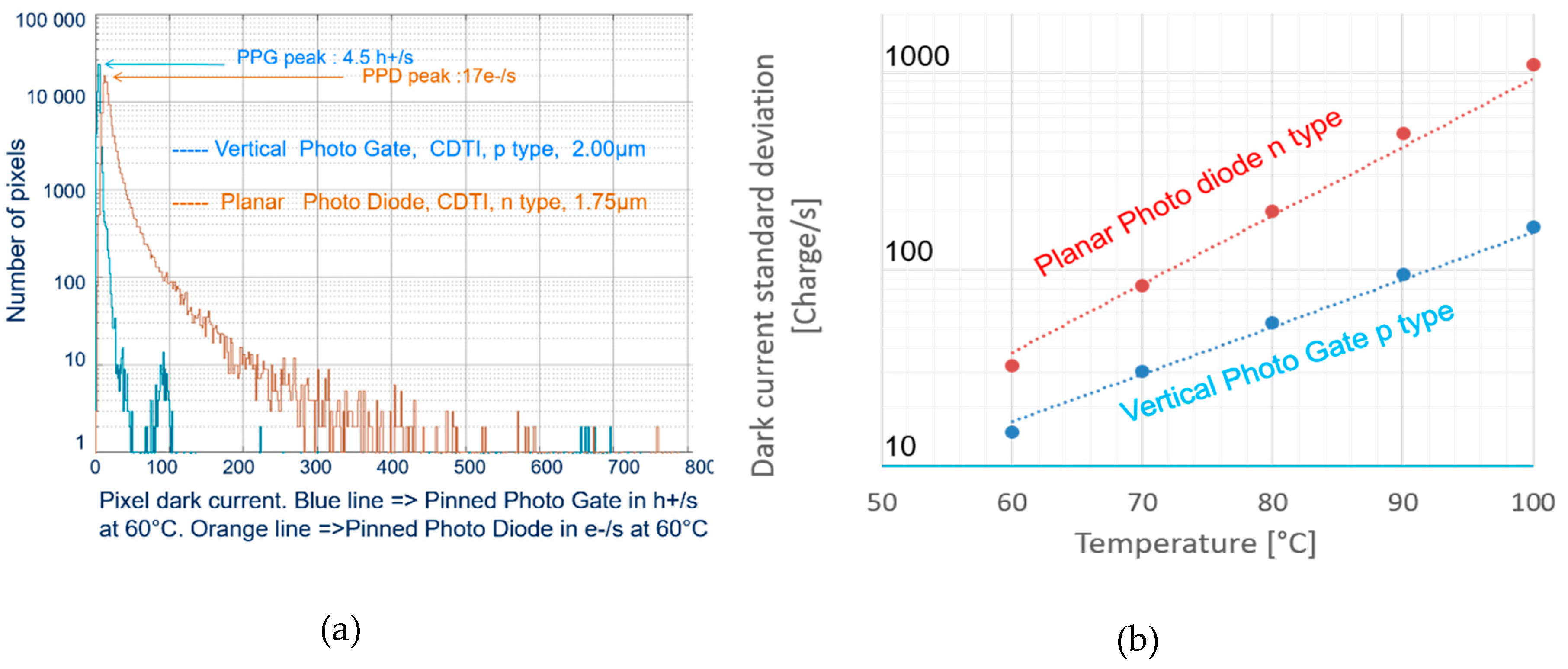

3.2. Dark Current

3.3. Main Characteristics

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Teranishi, N.; Kohono, A.; Ishihara, Y.; Oda, E.; Arai, K. No image lag photodiode structure in the interline CCD image sensor. In Proceedings of the 1982 International Electron Devices Meeting, San Francisco, CA, USA, 13–15 December 1982; Volume 28, pp. 324–327. [Google Scholar]

- Lee, P.; Gee, R.; Guidash, R.; Lee, T.; Fossum, E. An Active Pixel Sensor Fabricated Using CMOS/CCD Process Technology. In Proceedings of the International Image Sensor Workshop (IISW), Dana Point, CA, USA, June 1995. [Google Scholar]

- Michelot, J.; Roy, F.; Prima, J.; Augier, C.; Barbier, F.; Ricq, S.; Boulenc, P.; Essa, Z.; Pinzelli, L.; Leininger, H.; et al. Back illuminated vertically pinned photodiode with in depth charge storage. In Proceedings of the International Image Sensor Workshop (IISW), Hokkaido, Japan, 8–11 June 2011. [Google Scholar]

- Fuse, G.; Sugitani, M. Fundamental Ion Implantation Technologies for Image Sensor Devices. In Proceedings of the International Image Sensors Workshop (IISW), Snowbird, UT, USA, 12–16 June 2013; pp. 17–20. [Google Scholar]

- Teranishi, N.; Fuse, G.; Sugitani, M. A Review of the Ion Implantation Technology for Image Sensors. Sensors 2018, 18, 2358. [Google Scholar] [CrossRef] [PubMed]

- Fossum, E. A Novel Trench-Defined MISIM CCD Structure for X-ray Imaging and Other Applications. Electron Device Lett. 1989, 10, 177–179. [Google Scholar] [CrossRef]

- Roy, F.; Waltz, Y.C.P.; Malinge, P.; Pierron, N.B. Low Noise Global Shutter Image Sensor Working in the Charge Domain. IEEE Electron Device Lett. 2019, 40, 310–313. [Google Scholar] [CrossRef]

- Yamada, T.; Fukumoto, A. Trench CCD Image Sensor. Trans. Consum. Electron. 1989, 35, 360–367. [Google Scholar] [CrossRef]

- Bakker, J.; Esser, L.; Sweeney, C.; Kokshoom, A.; Theuwissen, A. The Tacking CCD: A New Concept. Trans. Consum. Electron. 1991, 38, 1193–1200. [Google Scholar] [CrossRef]

- Roy, F.; Suler, A.; Arnaud, J.; Cazaux, Y.; Montes, L.; Morfouli, P. Back Side Illuminated, Fully Depleted, Pinned Trench Photo MOS for Imaging Applications. In Proceedings of the International Image Sensors Workshop (IISW), Snowbird, UT, USA, 24–27 June 2019. [Google Scholar]

- Ahmed, N.; Roy, F.; Lu, G.-N.; Mamdy, B.; Carrere, J.-P.; Tournier, A.; Virollet, N.; Perrot, C.; Rivoire, M.; Seignard, A.; et al. Mos capacitor deep trench isolation for cmos image sensors. In Proceedings of the 2014 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2014. [Google Scholar]

- Tournier, A.; Roy, F.; Cazaux, Y.; Lalanne, F.; Malinge, P.; Mcdonald, M.; Monnot, G.; Roux, N. A HDR 98dB 3.2 µm Charge Domain Global Shutter CMOS Image Sensor. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018. [Google Scholar]

- Janesick, J. Multi-pinned phase charge-coupled device. NASA Tech. Briefs 1990, 14, 22. [Google Scholar]

- Ramadout, B. Capteurs d’images CMOS à haute résolution à Tranchées Profondes Capacitives. Ph.D. Thesis, École doctorale Électronique, électrotechnique, automatique, Lyon, France, 2010. [Google Scholar]

- Dalleau, T.; Duru, R.; Benoit, D.; Suler, A.; Chaton, C.; Roy, F.; Lu, G.N. Electrostatic surface passivation for p-type BSI Image Sensors. In Proceedings of the International Image Sensors Workshop (IISW), Snowbird, UT, USA, 24–27 June 2019. [Google Scholar]

- Warren, W.L.; Kanicki, J.; Robertson, J.; Poindexter, E.H.; McWhorter, P.J. Electron paramagnetic resonance investigation of charge trapping centers in amorphous silicon nitride films. J. Appl. Phys. 1993, 74, 4034–4046. [Google Scholar] [CrossRef]

- Wilson, M.; Lagowski, J.; Jastrzebski, L.; Savtchouk, A.; Faifer, V. COCOS (Corona Oxidation for Charaterization of Semiconductors) non-contact metrology for gate dielectrics. In AIP Conference Proceedings; American Institute of Physics: Gaithersburg, MD, USA, 2001. [Google Scholar]

- Widenhorn, R.; Blouke, M.; Weber, A.; Rest, A.; Bodegom, E. Temperature dependence of dark current in a CCD. In Proceedings of the SPIE; International Society for Optics and Photonics, Bellingham, WA, USA, 2002; Volume 4669, pp. 193–201. [Google Scholar]

| Characteristics | |

|---|---|

| Pixel | P type, 2.0 µm pitch, 2T5, RS, 103,000 pixels |

| CVF | 90 µV/h+ |

| Saturation charge | 13,000 h+ |

| QE at 550nm | 80% |

| PRNU | 0.5% |

| Mean dark current at 60 °C | 5.3 h+/s |

| Lag | < 1 h+ |

| Temporal noise floor | 2 h+ |

| Dynamic range | 75 dB |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Roy, F.; Suler, A.; Dalleau, T.; Duru, R.; Benoit, D.; Arnaud, J.; Cazaux, Y.; Chaton, C.; Montes, L.; Morfouli, P.; et al. Fully Depleted, Trench-Pinned Photo Gate for CMOS Image Sensor Applications. Sensors 2020, 20, 727. https://doi.org/10.3390/s20030727

Roy F, Suler A, Dalleau T, Duru R, Benoit D, Arnaud J, Cazaux Y, Chaton C, Montes L, Morfouli P, et al. Fully Depleted, Trench-Pinned Photo Gate for CMOS Image Sensor Applications. Sensors. 2020; 20(3):727. https://doi.org/10.3390/s20030727

Chicago/Turabian StyleRoy, Francois, Andrej Suler, Thomas Dalleau, Romain Duru, Daniel Benoit, Jihane Arnaud, Yvon Cazaux, Catherine Chaton, Laurent Montes, Panagiota Morfouli, and et al. 2020. "Fully Depleted, Trench-Pinned Photo Gate for CMOS Image Sensor Applications" Sensors 20, no. 3: 727. https://doi.org/10.3390/s20030727

APA StyleRoy, F., Suler, A., Dalleau, T., Duru, R., Benoit, D., Arnaud, J., Cazaux, Y., Chaton, C., Montes, L., Morfouli, P., & Lu, G.-N. (2020). Fully Depleted, Trench-Pinned Photo Gate for CMOS Image Sensor Applications. Sensors, 20(3), 727. https://doi.org/10.3390/s20030727