A 45 nm Stacked CMOS Image Sensor Process Technology for Submicron Pixel †

Abstract

:1. Introduction

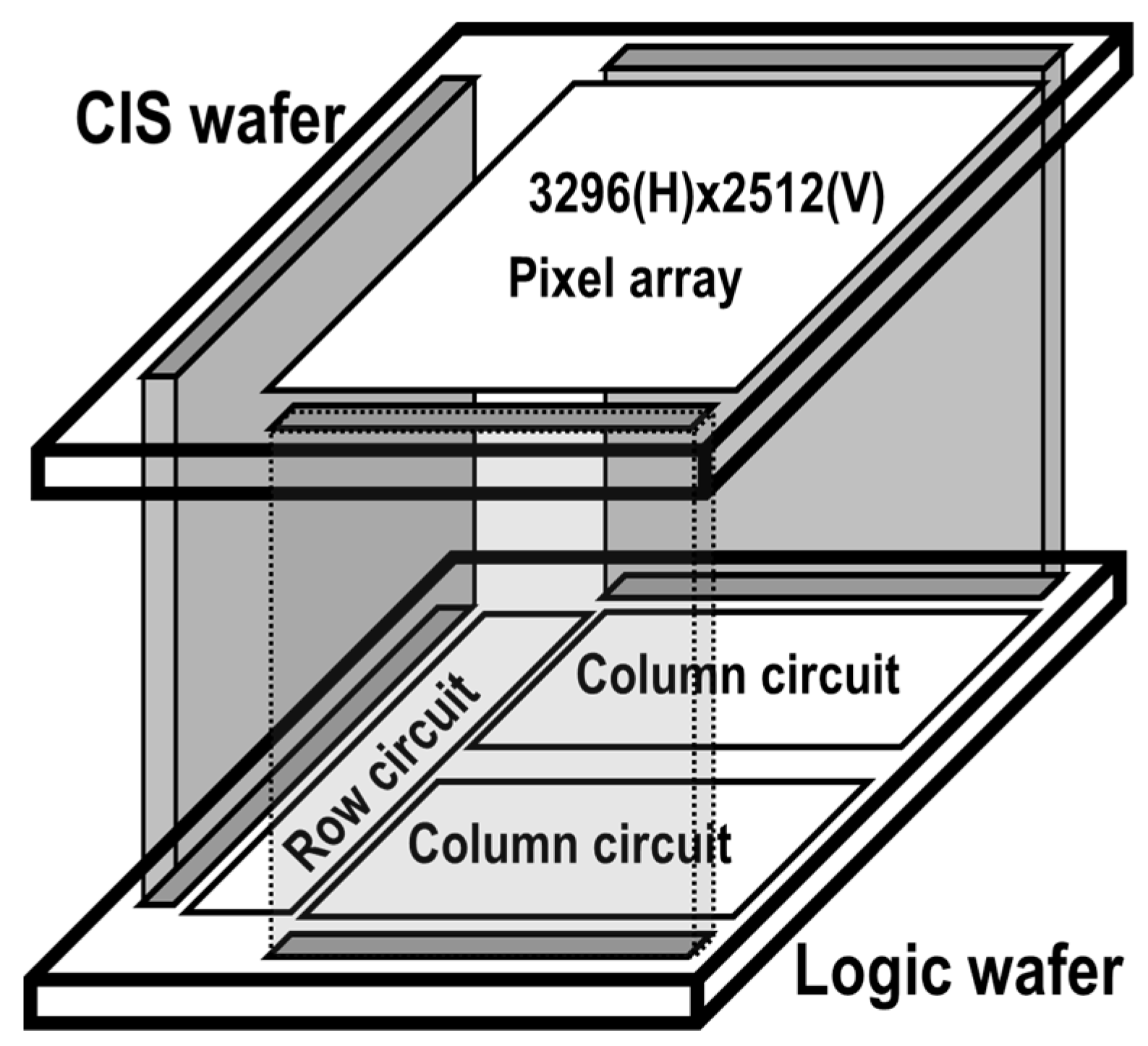

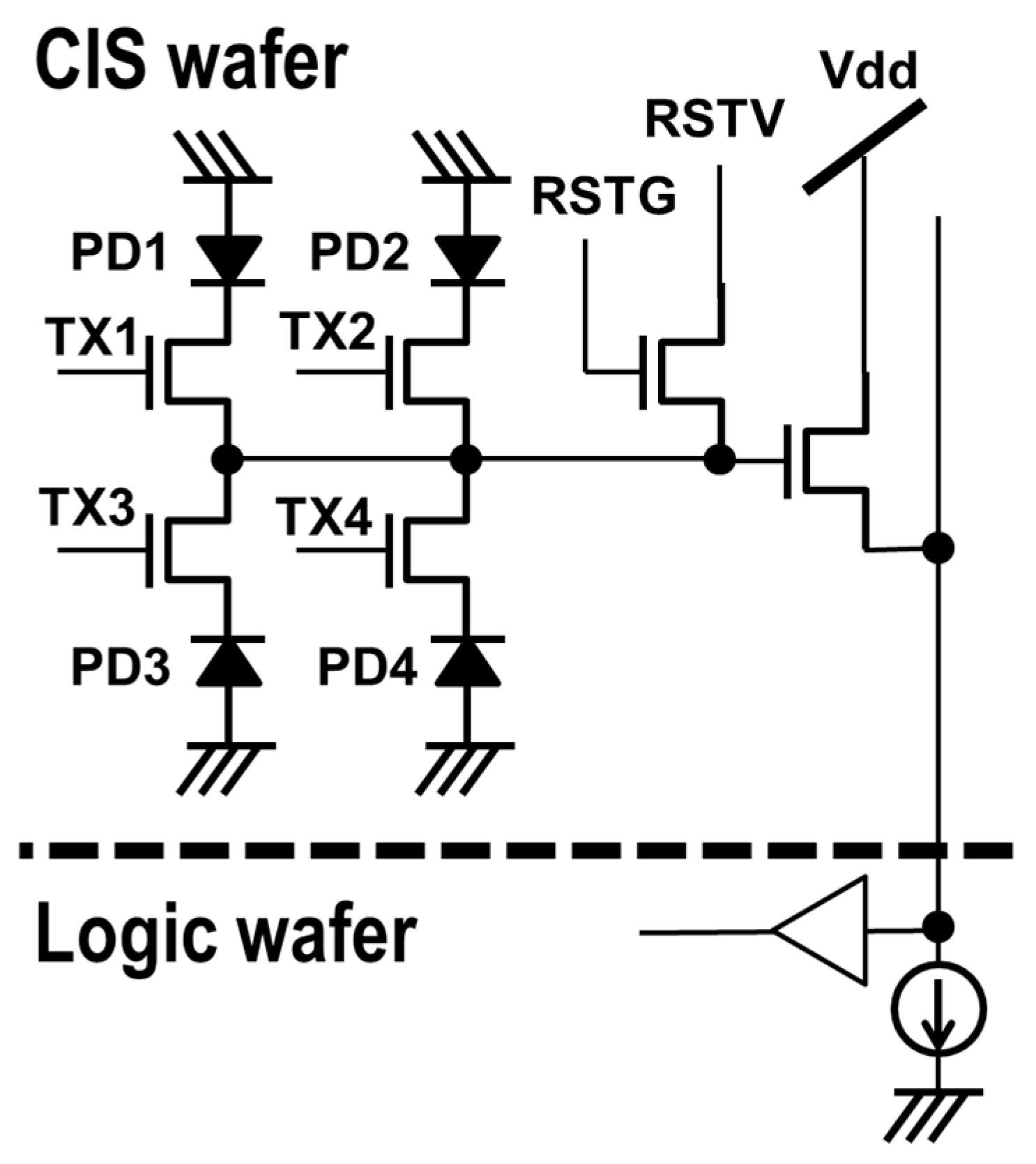

2. A 45 nm Stacked CMOS Image Sensor

3. Experimental Result

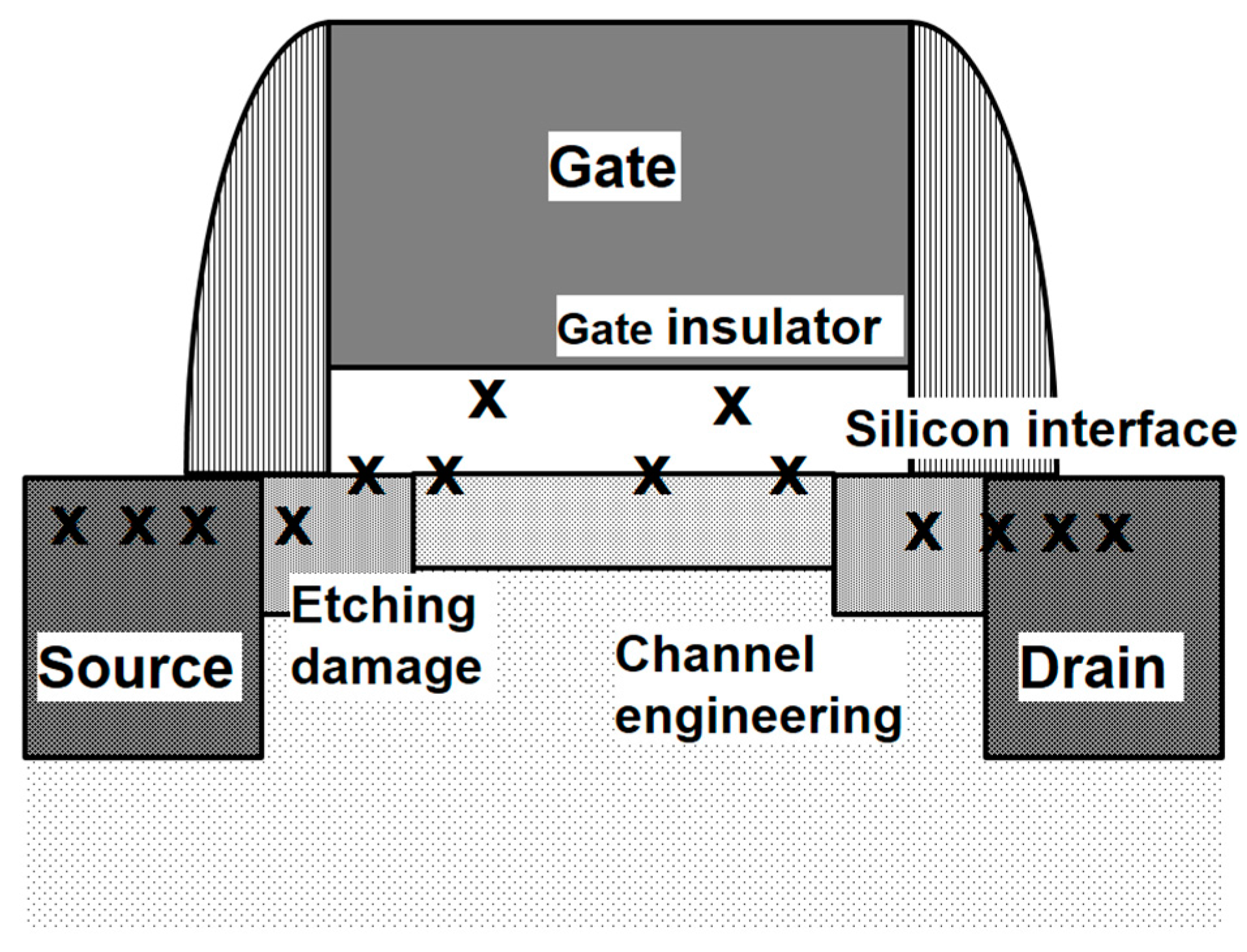

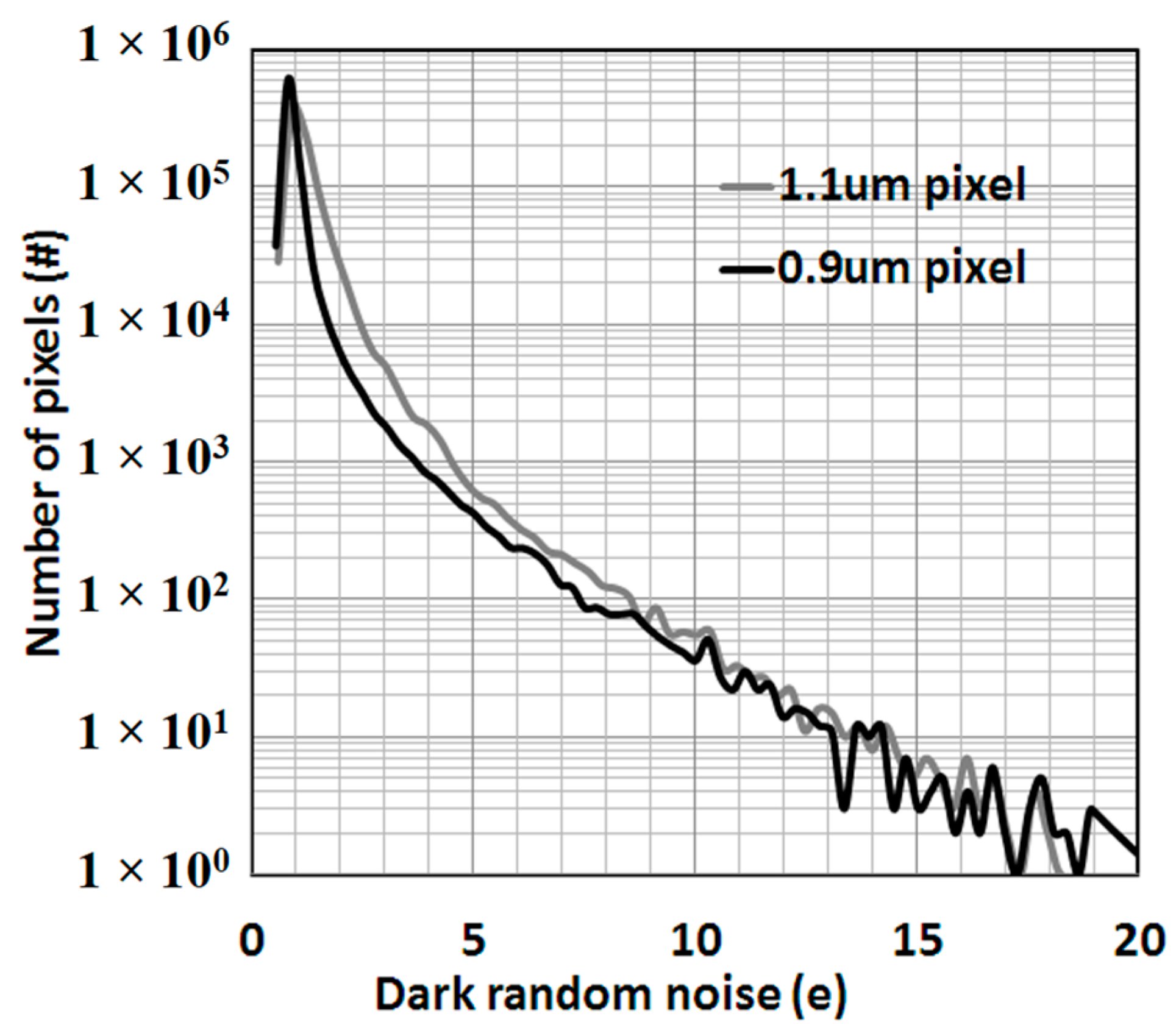

3.1. Low Noise Source Follower Device

3.2. Low Dark Current Pixel

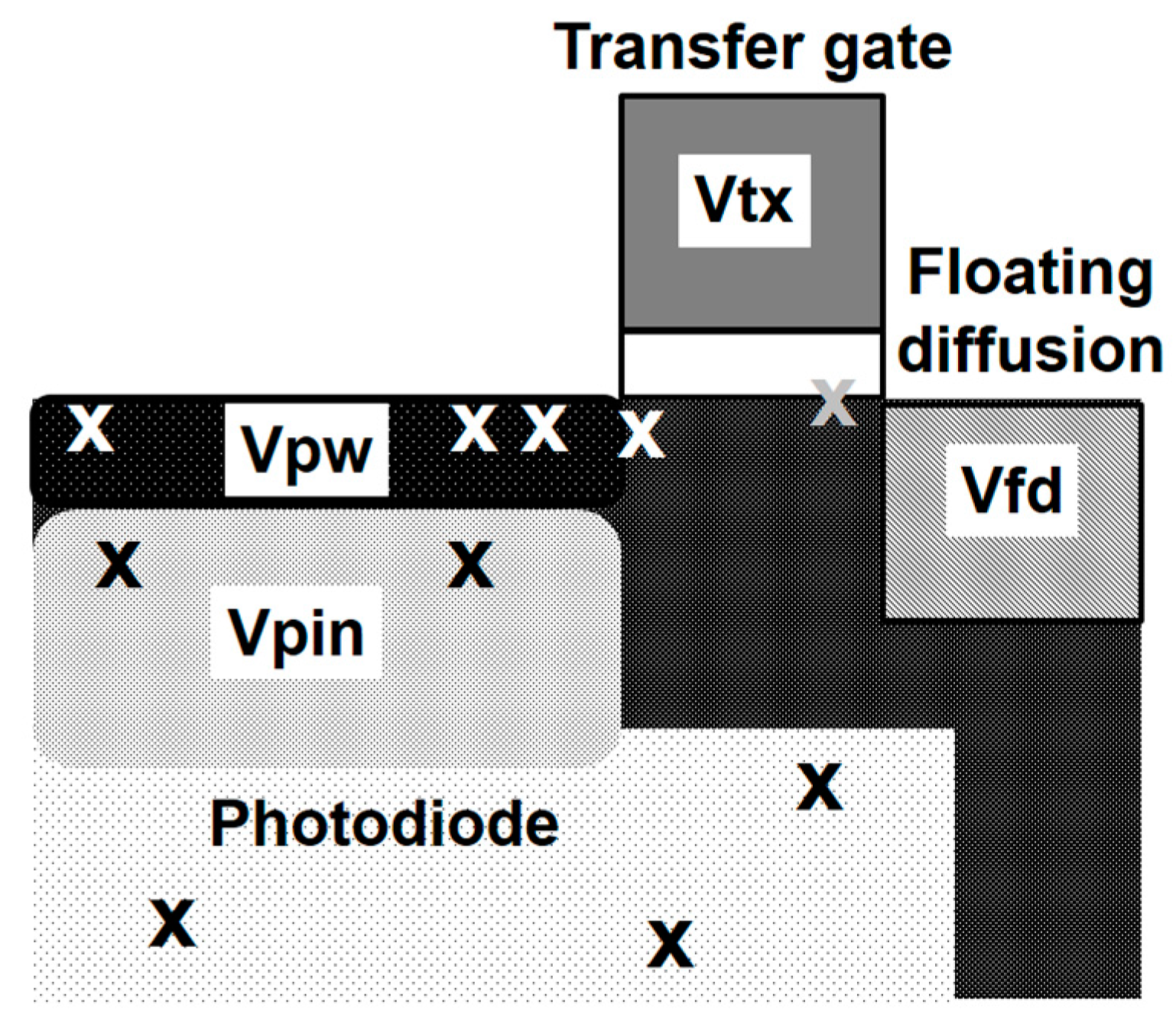

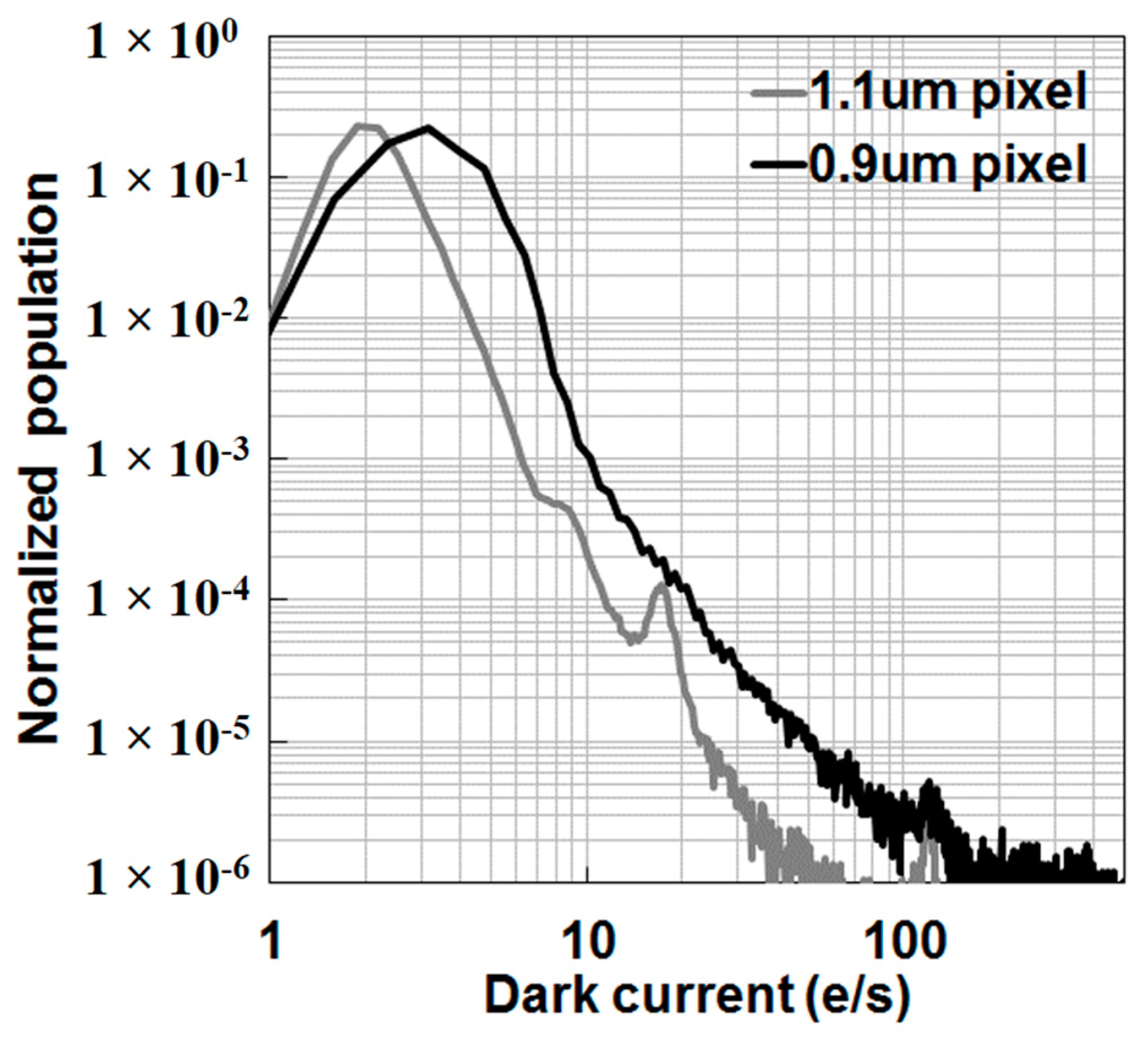

3.3. Pixel Design and Low Dark Current Pixel

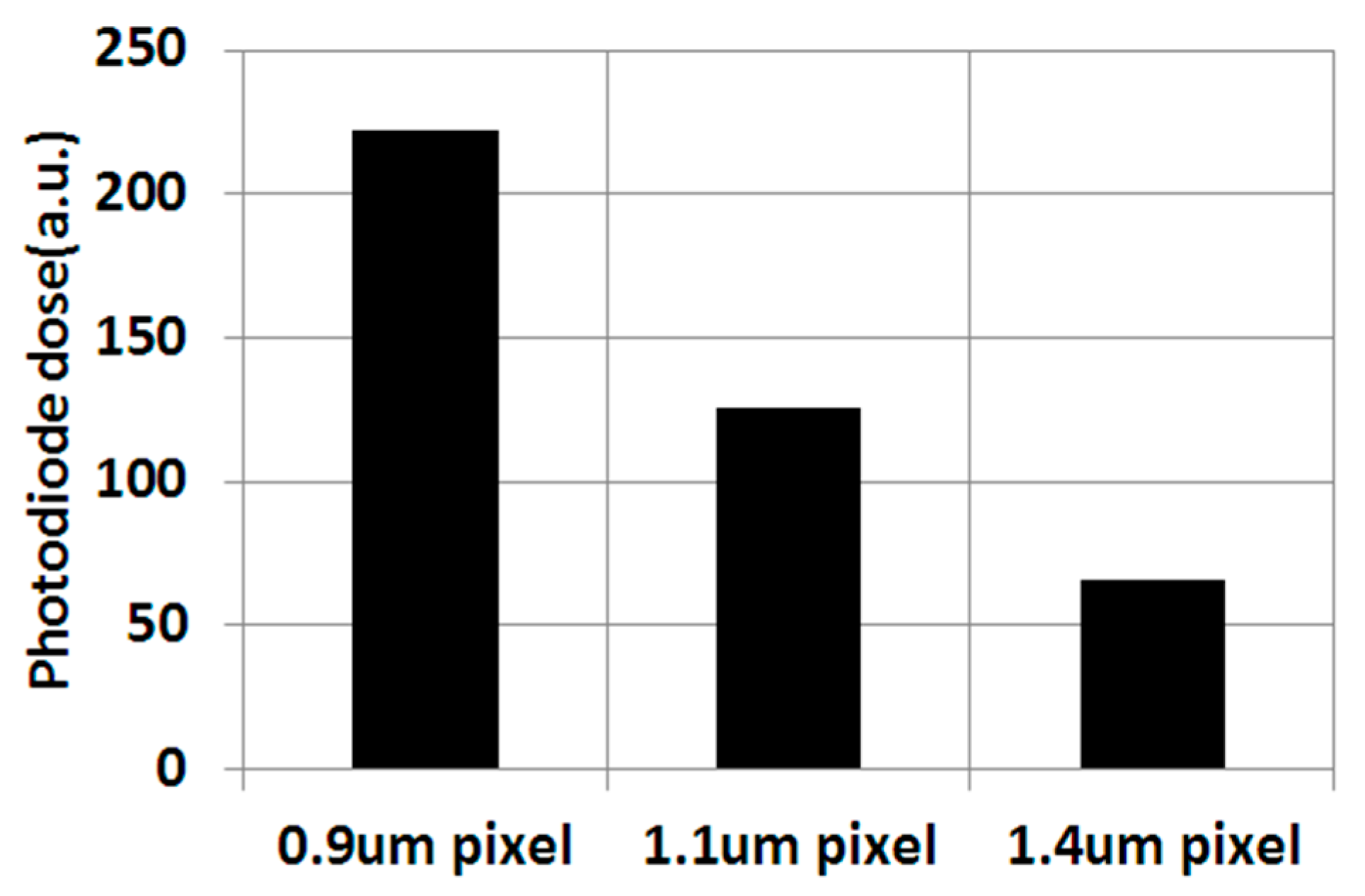

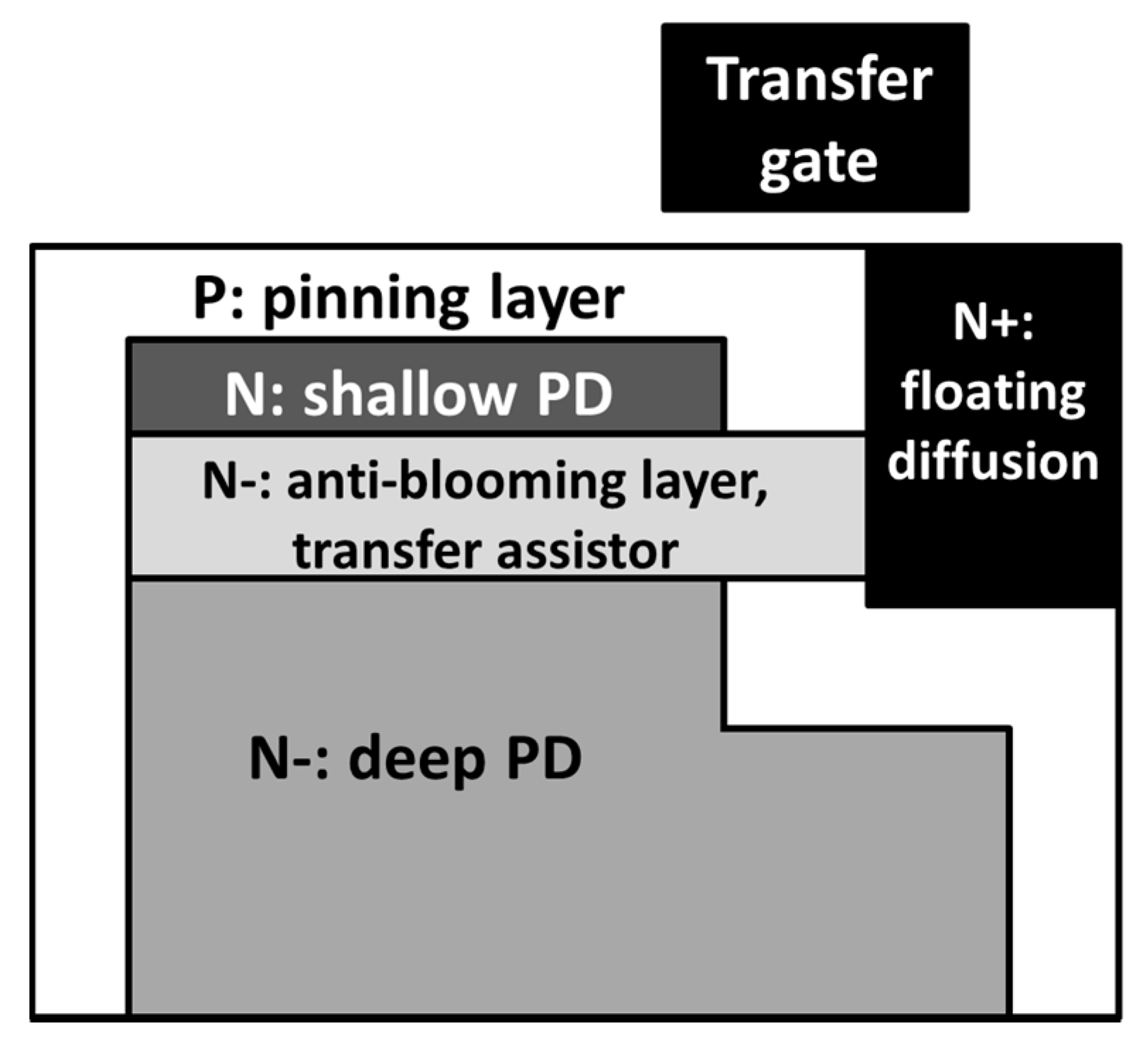

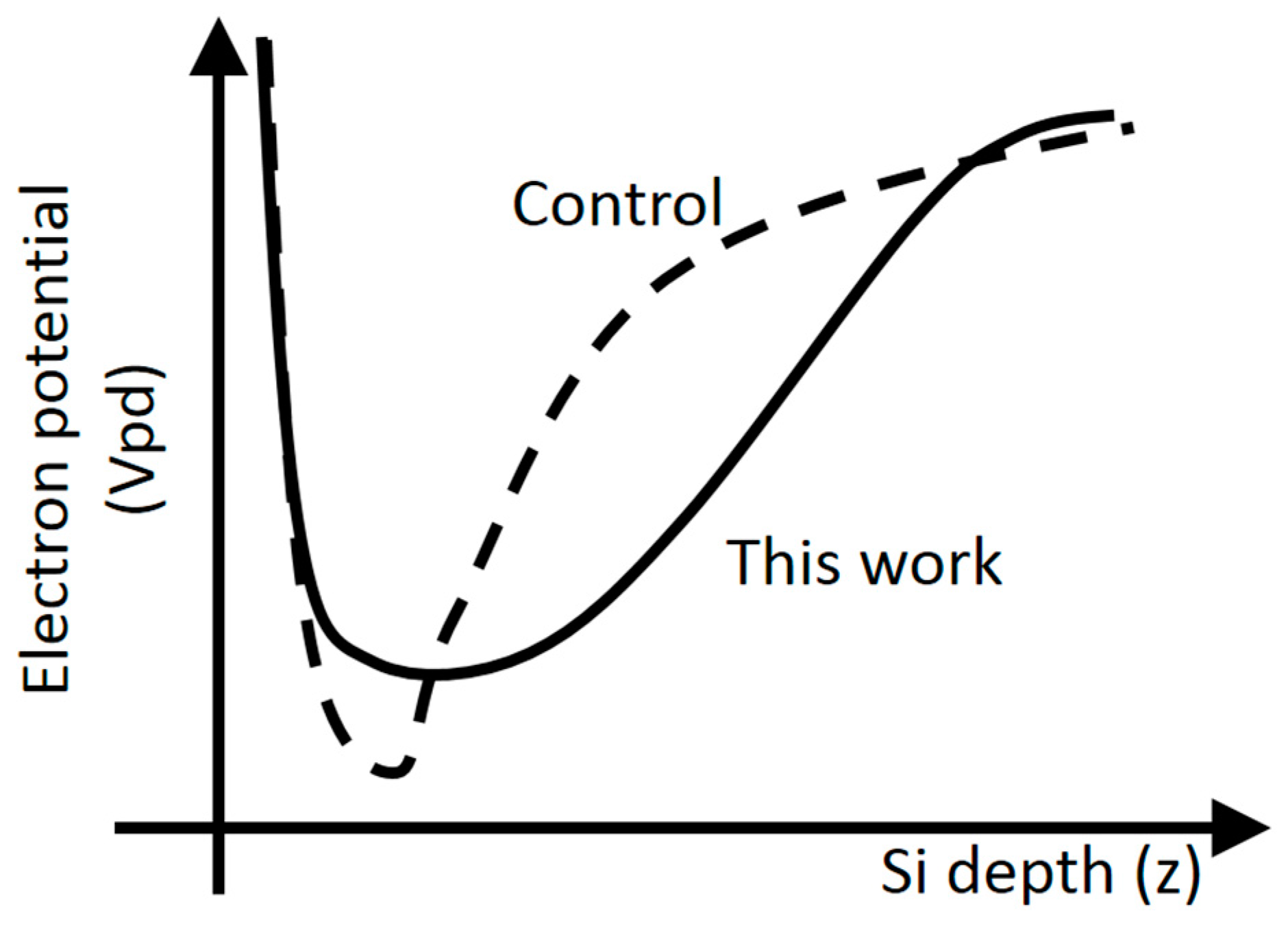

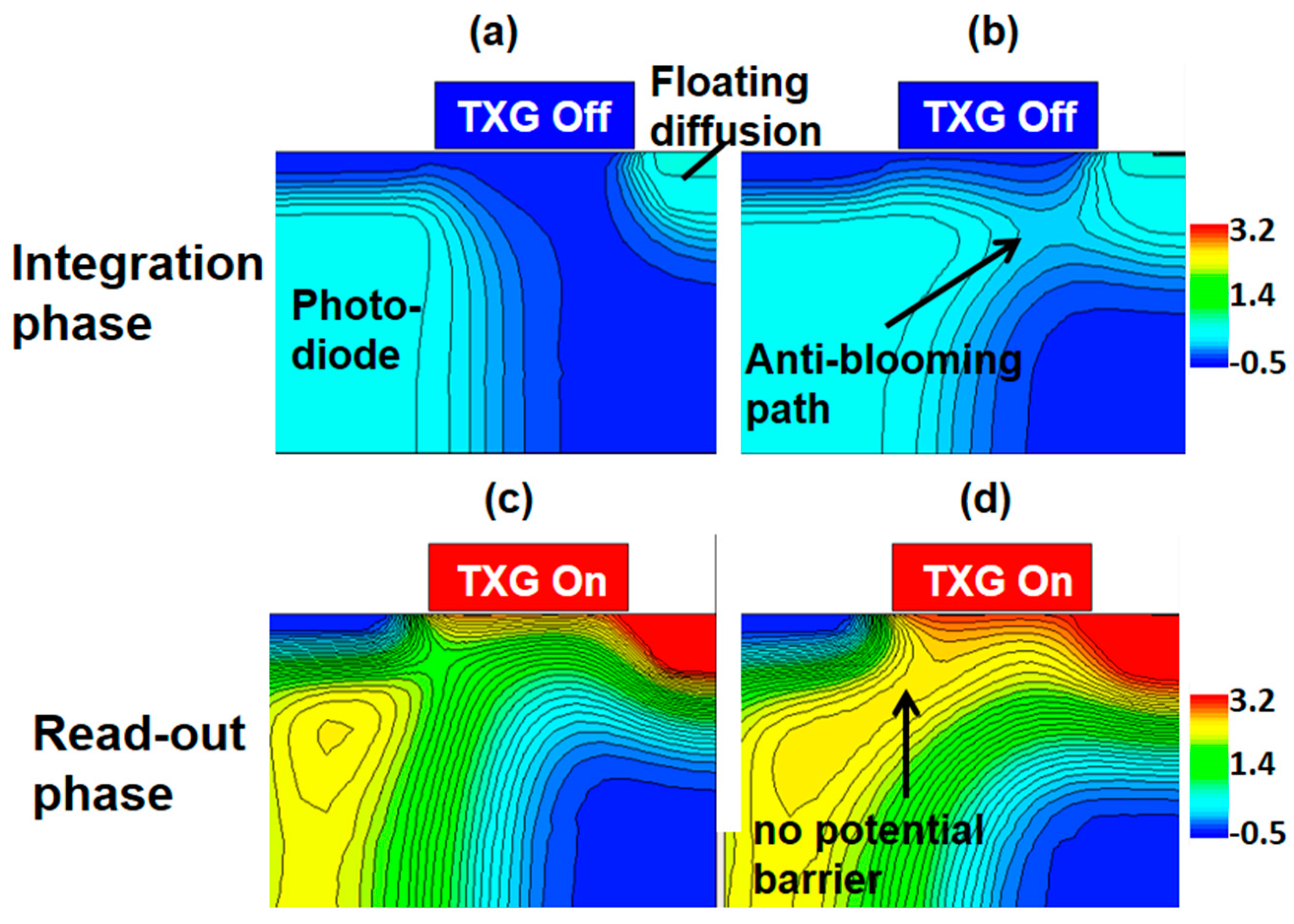

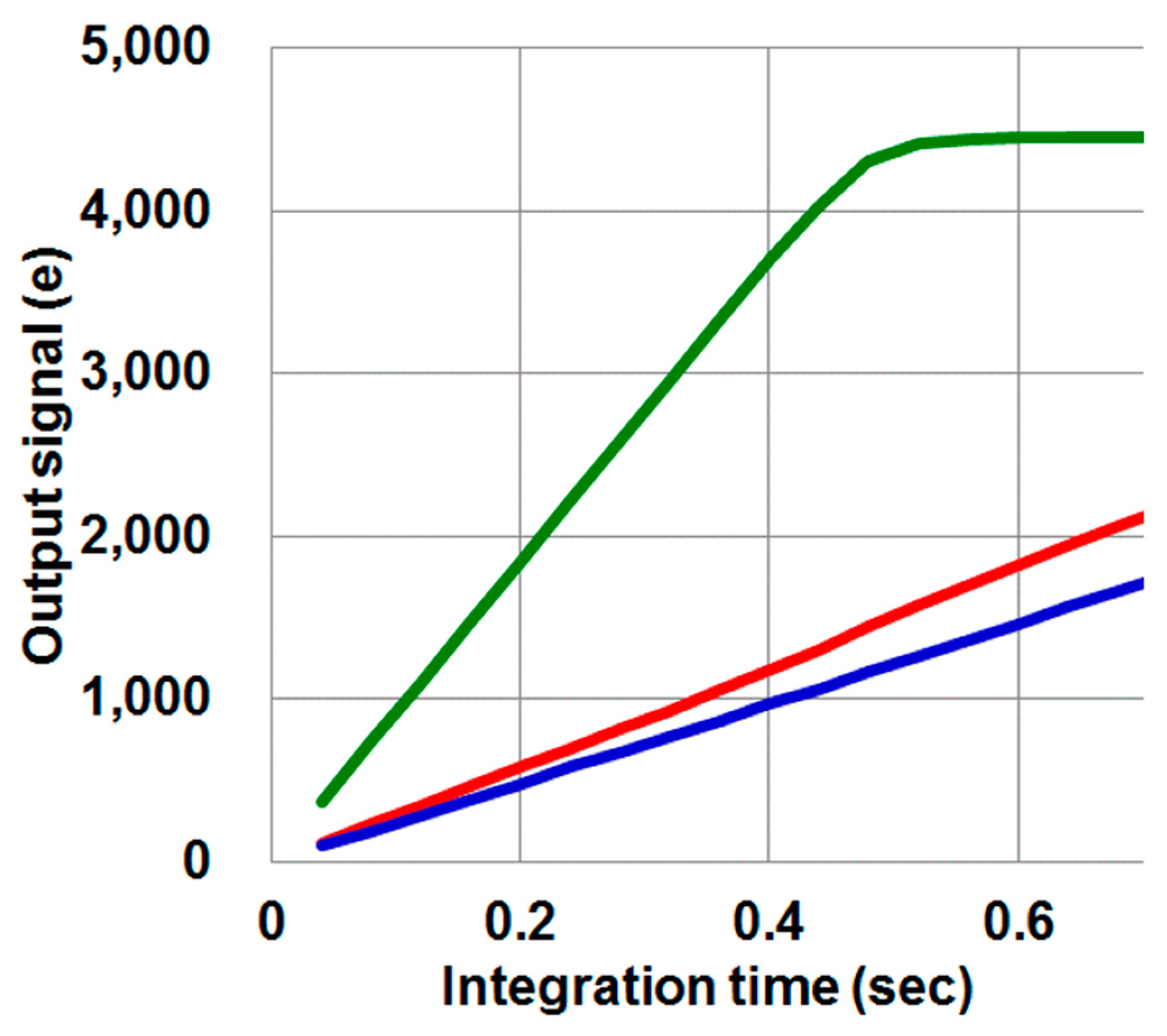

3.4. Anti-Blooming Pixel

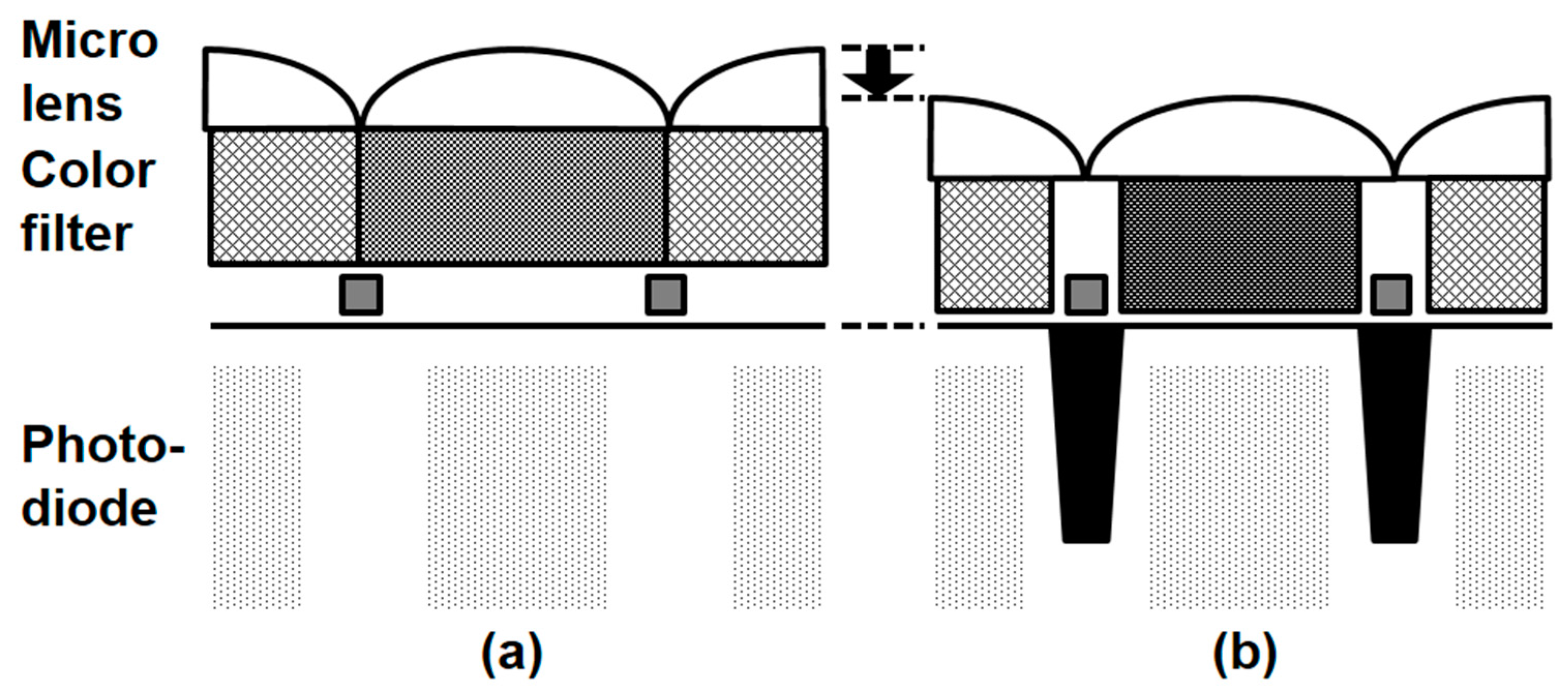

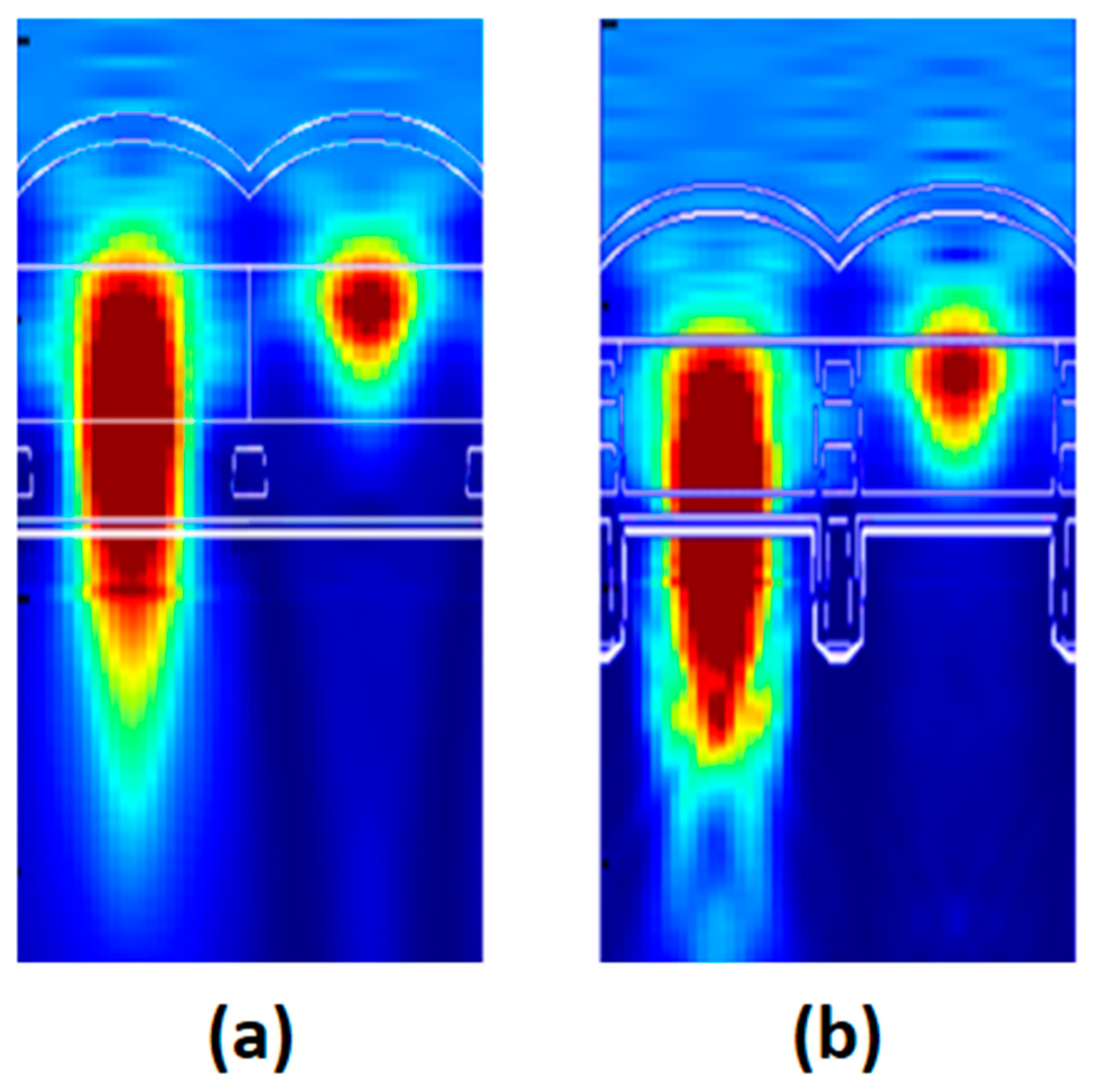

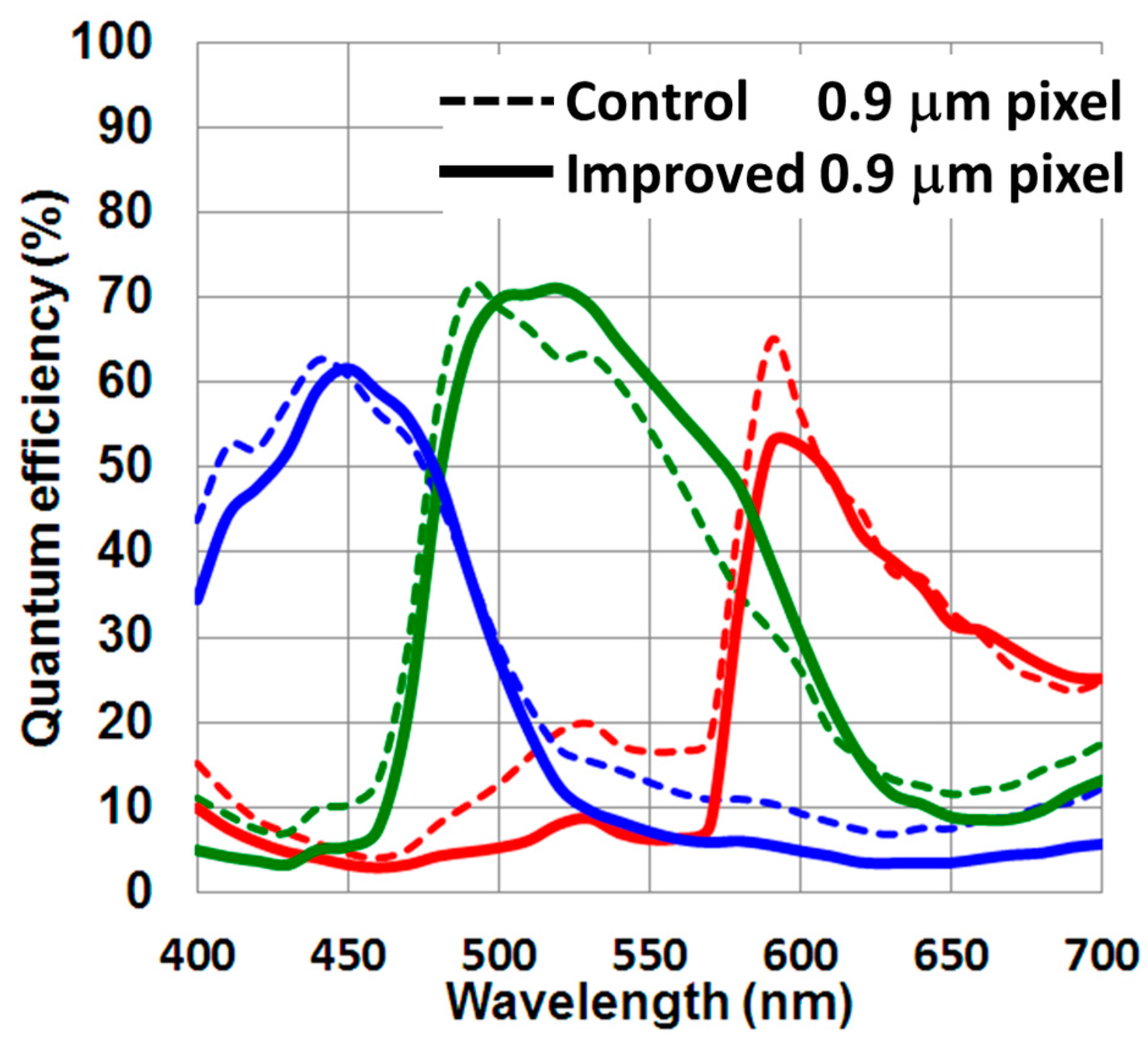

3.5. Low Crosstalk Pixel

4. 0.8 μm Pixel Generation

5. Conclusions

Author Contributions

Conflicts of Interest

References

- Fossum, E.R. What to do with sub-diffraction-limit (SDL) pixels?—A proposal for a gigapixel digital film sensor (DFS). In Proceedings of the IEEE Workshop on Charge-Coupled Devices and Advanced Image Sensors, Nagano, Japan, 8–11 June 2005; pp. 214–217. [Google Scholar]

- Jung, Y.J. Enhancement of low light level images using color-plus-mono dual camera. Opt. Express 2017, 25, 12029–12051. [Google Scholar] [CrossRef] [PubMed]

- Kobayashi, M.; Johnson, M.; Wada, Y.; Tsuboi, H.; Ono, T.; Takada, H.; Togo, K.; Kishi, T.; Takahashi, H.; Ichikawa, T.; et al. A Low Noise and High Sensitivity Image Sensor with Imaging and Phase-Difference Detection AF in All Pixels. ITE Trans. Media Technol. Appl. 2016, 4, 123–128. [Google Scholar] [CrossRef]

- Ahn, J.C.; Moon, C.R.; Kim, B.; Lee, K.; Kim, Y.; Lim, M.; Lee, W.; Park, H.; Moon, K.; Yoo, J.; et al. Advanced image sensor technology for pixel scaling down toward 1.0 µm (Invited). In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar]

- Wuu, S.G.; Wang, C.C.; Hsieh, B.C.; Tu, Y.L.; Tseng, C.H.; Hsu, T.H.; Hsiao, R.S.; Takahashi, S.; Lin, R.J.; Tsai, C.S.; et al. A leading-edge 0.9 µm pixel CMOS image sensor technology with backside illumination: Future challenges for pixel scaling. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010. [Google Scholar]

- Yaung, D.N.; Hsieh, B.C.; Wang, C.C.; Liu, J.C.; Wang, T.J.; Wang, W.D.; Chuang, C.C.; Chao, C.; Tu, Y.L.; Tsai, C.S.; et al. High performance 300 mm backside illumination technology for continuous pixel shrinkage. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011. [Google Scholar]

- Sukegawa, S.; Umebayashi, T.; Nakajima, T.; Kawanobe, H.; Koseki, K.; Hirota, I.; Haruta, T.; Kasai, M.; Fukumoto, K.; Wakano, T.; et al. A 1/4-inch 8 Mpixel back-illuminated stacked CMOS image sensor. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 17–21 February 2013. [Google Scholar]

- Cheng, K.L.; Wu, C.C.; Wang, Y.P.; Lin, D.W.; Chu, C.M.; Tarng, Y.Y.; Lu, S.Y.; Yang, S.J.; Hsieh, M.H.; Liu, C.M.; et al. A Highly Scaled, High Performance 45 nm Bulk Logic CMOS Technology with 0.242 µm2 SRAM Cell. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; pp. 243–246. [Google Scholar]

- Takahashi, S.; Huang, Y.-M.; Sze, J.-J.; Wu, T.-T.; Guo, F.-S.; Hsu, W.-C.; Tseng, T.-H.; Liao, K.; Kuo, C.-C.; Chen, T.-H.; et al. Low Dark Current and Low Noise 0.9 µm Pixel in a 45 nm Stacked CMOS Image Sensor Process Technology. In Proceedings of the 2017 International Image Sensor Workshop, Hiroshima, Japan, 30 May–2 June 2017. [Google Scholar]

- Liu, J.C.; Yaung, D.N.; Sze, J.J.; Wang, C.C.; Hung, G.; Wang, C.J.; Hsu, T.H.; Lin, R.J.; Wang, T.J.; Wang, W.D.; et al. Advanced 1.1 µm Pixel CMOS Image Sensor with 3D Stacked Architecture. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014. [Google Scholar]

- Nakamura, J. Image Sensors and Signal Processing for Digital Still Cameras, 1st ed.; CRC Press: Boca Raton, FL, USA, 2006. [Google Scholar]

- Abe, K.; Sugawa, S.; Kuroda, R.; Watabe, S.; Miyamoto, N.; Teramoto, A.; Ohmi, T.; Kamata, Y.; Shibusawa, K. Analysis of Source Follower Random Telegraph Signal Using nMOS and pMOS Array TEG. In Proceedings of the International Image Sensor Workshop, Hiroshima, Japan, 30 May–2 June 2017; pp. 62–65. [Google Scholar]

- Jantsch, O. Flicker (1/f) noise generated by a random walk of electrons in interfaces. IEEE Trans. Electron Devices 1987, 34, 1100–1115. [Google Scholar] [CrossRef]

- Sze, J.J.; Lin, R.J.; Takahashi, S.; Hung, J.M.; Lu, Y.C.; Tseng, T.H.; Wang, C.C.; Ting, S.F.; Wuu, S.G. The Impact of Gate Edge Damage on Pixel Read Noise. In Proceedings of the International Image Sensor Workshop, Snowbird, UT, USA, 12–16 June 2013. [Google Scholar]

- Taure, Y.; Ning, T.H. Fundamentals of Modern VLSI Devices; Cambridge University Press: Cambridge, UK, 1998. [Google Scholar]

- Watanabe, T.; Park, J.H.; Aoyama, S.; Isobe, K.; Kawahito, S. Effects of Negative-Bias Operation and Optical Stress on Dark Current in CMOS Image Sensors. IEEE Trans. Electron Devices 2010, 57, 1512–1518. [Google Scholar] [CrossRef]

- Sequin, C.H.; Shankoff, T.A.; Sealer, D.A. Measurements on a charge-coupled area image sensor with blooming suppression. IEEE Trans. Electron Devices 1974, 21, 331–341. [Google Scholar] [CrossRef]

- Adachi, S.; Simada, H.; Gotoh, H.; Mizobuchi, K. A novel lateral overflow drain technology for high quantum efficiency CCD imagers. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2000. [Google Scholar]

- Chao, C.; Chou, K.Y.; Liu, C.; Chen, Y.C.; Tu, H.Y.; Cheng, H.Y.; Hsueh, F.L.; Wuu, S.G. Blooming and Antiblooming in 1.1 µm-Pixel CIS. In Proceedings of the International Image Sensor Workshop, Snowbird, UT, USA, 12–16 June 2013. [Google Scholar]

- Kitamura, Y.; Aikawa, H.; Kakehi, K.; Yousyou, T.; Eda, K.; Minami, T.; Uya, S.; Takegawa, Y.; Yamashita, H.; Kohyama, Y.; et al. Suppression of Crosstalk by Using Backside Deep Trench Isolation for 1.12 μm Backside Illuminated CMOS Image Sensor. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012. [Google Scholar]

- Catrysse, P.B.; Wandell, B.A. Roadmap for CMOS image sensors: Moore meets Planck and Sommerfeld. SPIE 2005, 5678, 1–13. [Google Scholar]

| Choice | PROS | CONS |

|---|---|---|

| Pixel devices on CIS wafer | High conversion gain | Low fill factor |

| Dedicated pixel device process | ||

| Pixel devices on logic wafer | High fill factor | Low conversion gain |

| Dedicated photodiode process |

| Process Technology | 45 nm 1P4M Stacked CIS |

|---|---|

| Pixel size | 0.90 μm |

| Pixel supply voltage | 2.8 V |

| Conversion gain | 120 μV/e− |

| Dark current at 60 °C | 3.2 e−/s |

| White pixel counts with dark current of >200 e−/s at 60 °C | 679 ppm |

| Read noise at 18 dB | 0.90 e−·rms |

| Full well capacity | 4100 e− |

| Blooming | 0.5% |

| Image lag | <1 e− |

| Photo response non-uniformity | 0.9% |

| Quantum efficiency at green peak | 71% |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Takahashi, S.; Huang, Y.-M.; Sze, J.-J.; Wu, T.-T.; Guo, F.-S.; Hsu, W.-C.; Tseng, T.-H.; Liao, K.; Kuo, C.-C.; Chen, T.-H.; et al. A 45 nm Stacked CMOS Image Sensor Process Technology for Submicron Pixel. Sensors 2017, 17, 2816. https://doi.org/10.3390/s17122816

Takahashi S, Huang Y-M, Sze J-J, Wu T-T, Guo F-S, Hsu W-C, Tseng T-H, Liao K, Kuo C-C, Chen T-H, et al. A 45 nm Stacked CMOS Image Sensor Process Technology for Submicron Pixel. Sensors. 2017; 17(12):2816. https://doi.org/10.3390/s17122816

Chicago/Turabian StyleTakahashi, Seiji, Yi-Min Huang, Jhy-Jyi Sze, Tung-Ting Wu, Fu-Sheng Guo, Wei-Cheng Hsu, Tung-Hsiung Tseng, King Liao, Chin-Chia Kuo, Tzu-Hsiang Chen, and et al. 2017. "A 45 nm Stacked CMOS Image Sensor Process Technology for Submicron Pixel" Sensors 17, no. 12: 2816. https://doi.org/10.3390/s17122816

APA StyleTakahashi, S., Huang, Y.-M., Sze, J.-J., Wu, T.-T., Guo, F.-S., Hsu, W.-C., Tseng, T.-H., Liao, K., Kuo, C.-C., Chen, T.-H., Chiang, W.-C., Chuang, C.-H., Chou, K.-Y., Chung, C.-H., Chou, K.-Y., Tseng, C.-H., Wang, C.-J., & Yaung, D.-N. (2017). A 45 nm Stacked CMOS Image Sensor Process Technology for Submicron Pixel. Sensors, 17(12), 2816. https://doi.org/10.3390/s17122816