1. Introduction

With the rapid evolution of integrated circuits, process nodes have progressively scaled from micrometer dimensions to advanced 7 nm and 3 nm nodes. In 2024, the Taiwan Semiconductor Manufacturing Company (TSMC) achieved a significant milestone by commencing the mass production of a 2 nm node, as reported in communications on recent industry developments. This relentless miniaturization has substantially increased the transistor density while reducing the power consumption, driving the demand for innovative low-voltage design methodologies [

1]. Consequently, substantial progress has been made in developing low-voltage operational amplifiers, enabling enhanced performance in power-constrained applications. In contrast, the advancement of high-voltage operational amplifiers has lagged despite their critical role in emerging applications. Specifically, sensor analog front ends, medical instrumentation, and automotive electronics increasingly necessitate operational amplifiers capable of delivering a high closed-loop gain, minimal noise, and a low offset under elevated voltage conditions [

2,

3,

4]. High-precision, fast-responding operational amplifiers are paramount to ensure accurate signal acquisition, thereby facilitating superior system-level control and reliability in these high-voltage environments.

Several techniques are widely adopted to achieve high accuracy, including digital trimming (DigiTrim), chopper stabilization, and auto-zeroing. Digital trimming, as can be performed using Analog Devices’ DigiTrim technology [

5], adjusts the circuit performance using digitally programmed weighted current sources. Adjustment data are input via existing analog pins using specific digital keyword sequences. These values can be temporarily programmed, evaluated, and fine-tuned for optimal precision before permanent adjustment. Chopper stabilization [

6], a frequency-domain technique, employs switch-based modulation to shift the input signal to the high-frequency domain, amplify it, and finally demodulate it back to its original frequency. Auto-zeroing, a time-domain error correction method, uses a capacitor to store the instantaneous error during a phase when the inputs are short-circuited, producing a constant output (e.g., zero) [

7]. In the subsequent phase, the stored error is subtracted from the signal, enabling the output to track the input with constant level shifting.

Despite their advantages in achieving low noise and a low offset in high-voltage environments, these techniques have notable limitations. Digital trimming relies on blowing polysilicon fuses for permanent adjustments, rendering the process irreversible [

8]. If the trimming parameters are later found to be suboptimal, redesign or reproduction is necessary, which increases the cost. In chopper amplifiers, charge injection and clock feedthrough from chopping switches introduce the glitching and modulated ripple of the original offset, manifesting at even and odd harmonics of the chopping frequency, respectively [

9]. These artifacts often result in a residual output offset. Due to its signal-sampling nature, auto-zeroing increases the noise power spectral density within the sampling frequency range. This increase stems partly from the folding of 1/f noise tails and partly from the aliasing of broadband thermal noise. It will cause the input-referred noise power spectral density (PSD) to exceed the original thermal noise PSD within twice the Nyquist frequency [

10]. Combining auto-zeroing and chopper techniques can enhance the operational amplifier noise and offset performance [

11].

Most precision operational amplifiers leverage chopping and auto-zeroing to achieve low noise and offsets. Dension et al. introduced a micropower chopper-stabilized amplifier. It achieved a noise floor of 0.98 V

rms over a bandwidth of 0.05 to 100 Hz [

12]. Another study proposed a chopper DC Servo Loop (DSL) utilizing an active Gm-C integrator to mitigate the electrode DC offset, with a power consumption of 3.24

per channel at a 1.8 V supply voltage and an input equivalent noise PSD of 39

[

13]. Bakker et al. presented a nested chopper technique that significantly reduces the offset in traditional chopper amplifiers by adding only one pair of choppers, resulting in an amplifier with no 1/f noise and a thermal noise of 27

[

14]. Additionally, Stanescu et al. combined chopping with symmetric notch filtering, reducing the noise PSD to 7.5 without altering the primary path’s equivalent RC network [

15]. Dzahini et al. introduced a continuous-time auto-zeroing stabilized architecture, achieving a typical input offset voltage of 2

and a temperature drift of 100

[

16]. Research on high-voltage operational amplifiers with high precision remains limited. Kilesnikov et al. focused on high-voltage operational amplifiers without dynamic offset compensation, resulting in an offset voltage of 300

at a 36 V supply voltage [

17]. In contrast, Kusuda proposed an auto-zeroing and chopper operational amplifier operating across a 4.5 to 60 V supply range. It employed post-production trimming to achieve a maximum offset voltage drift of 0.02

and a noise PSD of 6.8

[

18]. Current research on high-voltage operational amplifiers predominantly focuses on optimizing single performance metrics, such as noise or offset voltage reduction, with a limited emphasis on comprehensive multi-dimensional performance enhancement. Furthermore, most existing designs operate at a 30 V supply voltage [

19], which is inadequate for applications requiring higher-voltage environments.

This paper addresses these challenges by proposing a novel operational amplifier design at a 55 V supply voltage. The design integrates chopping and ping-pong auto-zeroing structures, as supported by patents on a ping-pong auto-zeroing amplifier. The auto-zeroing structure suppresses the chopper ripple induced by modulation, while a six-channel parallel connection mitigates chopper glitches caused by charge injection and clock feedthrough. This configuration achieves low noise, a low offset, and rail-to-rail output characteristics under high-voltage conditions, offering a high-performance solution for applications in sensor analog front ends, medical devices, and automotive electronics.

2. Circuit Design

The high-voltage chopper amplifier structure adopted in this paper is shown in

Figure 1.

In chopper amplifier design, the charge injection and clock feedthrough of the chopper switches have always been the primary factors affecting the offset voltage and noise of the operational amplifier. The chopper switch demodulates the mismatch caused by charge injection in the input chopper switch and appears as an offset of the differential input.

Figure 2 illustrates the transient waveform at the amplifier’s input under the influence of charge injection, with the charges injected during each clock transition represented by q1–q4. Ideally, charges q3 and q1 can cancel each other when input to Gm1, similarly to charges q4 and q2.

In practice, due to mismatches, errors are inevitable. Let the charge mismatch

and

. The current resulting from these mismatches is subjected to chopper modulation and flows to

and

, producing the DC bias components

and

, which can be expressed as

Furthermore, since each chopper switch has an on-resistance,

Ron, the input bias currents flowing through them will result in a residual input offset voltage,

.

In high-voltage designs, if traditional switching timing is employed, where the high and low levels of the timing correspond to the positive and negative supply voltages, the charge injection can be expressed as

. When the common-mode level significantly deviates from the supply voltage, the offset voltage induced by charge injection becomes substantial. For instance, using a 50 V supply voltage compared to a 5 V supply voltage design, the input-referred offset voltage increases by 10. Furthermore, the charge injection quantity

of an MOS (Metal Oxide Semiconductor) transistor can be approximated as

The on-resistance

of the transistor can be approximated by the following expression:

From Equations (4) and (5), it is evident that reducing

W and

L minimizes the charge injection effect while also lowering the noise in chopper. This paper proposes a common-mode tracking regulator (CM-Reg) to address the charge injection issue in high-voltage applications. This structure allows the voltage variation across the switch, i.e., the gate–source voltage of the MOS switch, to be set to a fixed value. Additionally, the substrate potential of the MOS transistor can track changes in the input common-mode voltage, further mitigating the impact of the body effect. The circuit is illustrated in

Figure 3 and

Figure 4.

The

generation circuit consists of MP1, MP2, R1, R2, and the tail current source MN3. MN4, a high-voltage transistor, effectively isolates the node, ensuring that the transistors operate within a safe voltage range. The differential input signals INN and INP generate an AC ground signal at node X.

can be expressed as

Under a fixed current condition, remains relatively constant. By adjusting the resistor values, a voltage that varies with the input common-mode voltage can be obtained. In this design, is set to approximately .

Similarly, the input transistors of the

generator are composed of PMOS (P-type Metal Oxide Semiconductor) transistors, mirroring the structure of the

generator. This configuration ensures the largest input range for the amplifier. In

Figure 4, MP5 and MP6 can be regarded as a split form of a single transistor. The value of

can be expressed as

MN3, MN4, MP7, and MP8 are high-voltage transistors employed to ensure that the low-voltage transistors operate within a safe voltage range. In this design,

is set to be equal to the input common-mode level. Furthermore, due to the high-voltage environment, specific nodes may experience transient high-voltage pulses during large-signal settling or power-up processes that could potentially damage devices. To address this, the design incorporates diode-connected MOS transistors to protect nodes prone to such pulses, as shown in the boxed section of

Figure 4. When the input signal exhibits significant fluctuations, these structures clamp the voltage across the nodes, ensuring that the MOS transistors remain within a safe voltage range.

The circuit generates and voltages to power a two-phase non-overlapping clock generator, producing clock signals that track the input common-mode voltage for use by the chopper input switches. This ensures that the NMOS (N-type Metal Oxide Semiconductor) switches maintain a constant 1.6 V gate–source turn-on voltage. Additionally, the back gates of the switches are driven by to avoid threshold voltage changes due to the body effect. As a result, the charge injections and on-resistance are maintained at a constant level with a change in .

The operational amplifier is primarily a three-stage amplifier with a nested Miller compensation structure. The overall circuit schematic is depicted in

Figure 5.

This design integrates input auto-zeroing, output auto-zeroing, and chopper techniques and employs a six-channel parallel configuration. The operation is divided into three phases: offset storage (pre-charge, PC), offset cancelation, and chopper amplification. The timing relationship for the six channels ensures that at any given moment, one channel is in the PC phase, one channel is in the auto-zeroing (AZ) phase, and the remaining four channels are in the amplification phase (CH or CH

INV). The timing diagram for the six channels is shown in

Figure 6a, while the single-channel timing is illustrated in

Figure 6b.

During the offset storage phase, also known as the pre-charge phase, switches S1, S2, S3, S4, S5, S6, S7, S8, and S9 are closed. Currently, the common-mode buffer (CM-buf) provides a 1.6 V common-mode voltage to the input of the amplifier while biasing the amplifier’s output common-mode voltage at

. In this configuration, the circuit employs an auto-zeroing structure with an “auxiliary amplifier,” where

represents the auxiliary amplifier. To analyze the offset voltage in this phase, we denote the trans-impedance of GM1 as R and account for the offset voltage

of

. This leads to Equations (7) and (8).

At this point, the equivalent offset voltage at the input can be expressed as

The offset voltage is stored on Caz. During the offset cancelation, switches S3 and S4 are opened, while the other switches remain unchanged. At this stage, the trans-impedance R and form a negative feedback system, thereby eliminating the offset voltage. Generally, since , ensuring can significantly reduce the offset voltage. Moreover, when switches S3 and S4 are closed, the circuit effectively replicates the amplifier’s offset voltage Vos1 at nodes X and Y. The input-referred offset of the entire circuit is , substantially better than the equivalent total offset voltage of Vos derived in Equation (9).

In the chopping phase, switches S10 and S11 are closed, and Gm1, in conjunction with the cascaded Gm2 and Gm3, amplifies the input signal. Since the circuit has undergone the auto-zeroing phase, the original offset of Gm1 is canceled by , resulting in a significantly reduced chopping ripple at the output. The chopper modulates the equivalent offset voltage and 1/f noise at the input to the chopping frequency Fc, which is filtered out by a low-pass filter. Additionally, when configured in a six-channel parallel connection, the charge injection effects of the MOS switches at the chopping frequency are also mitigated.

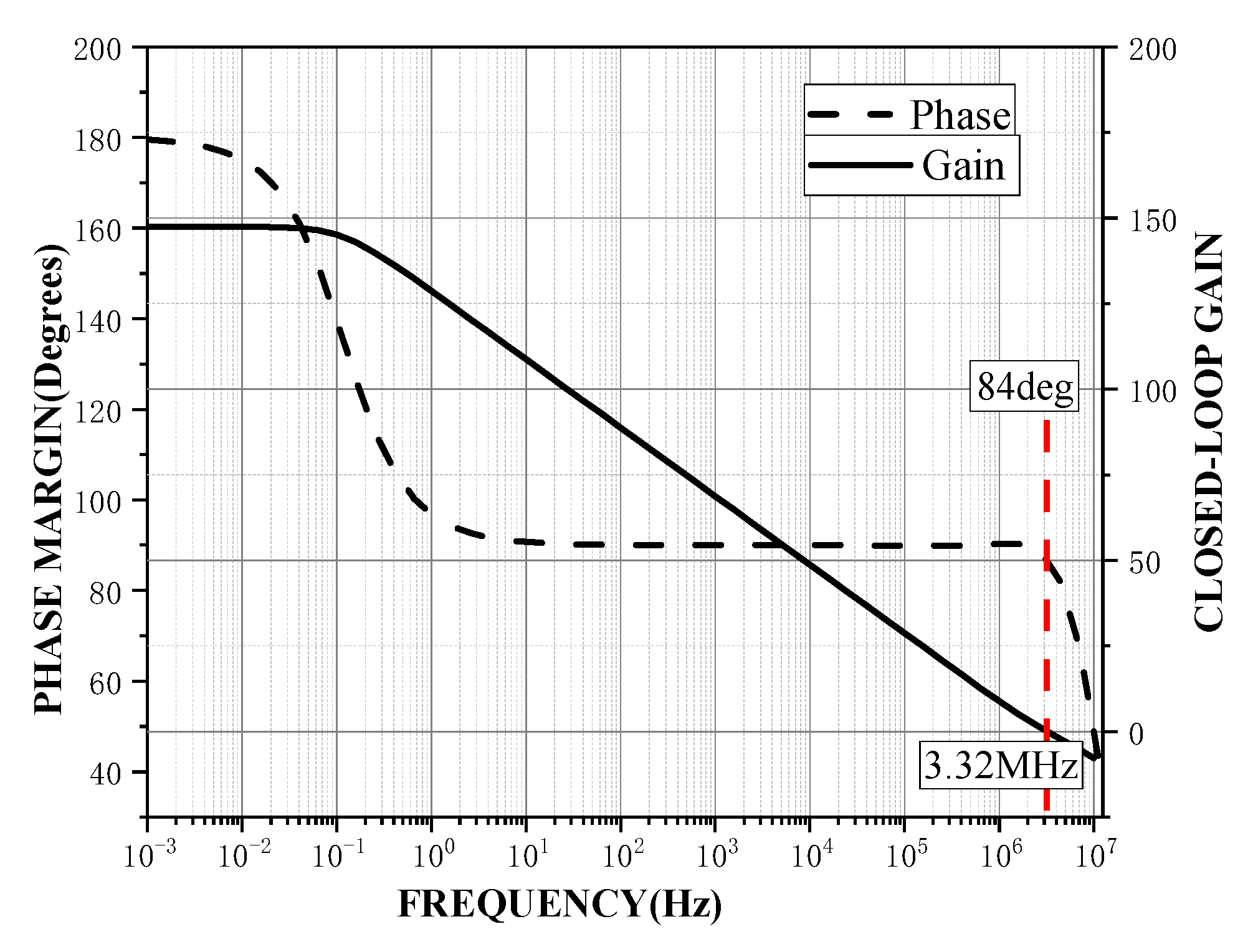

The core of the circuit is a three-stage amplifier with a nested Miller compensation structure [

20].

Figure 7 shows a simplified schematic of the circuit.

In

Figure 7, Gmi, Ri, and Ci (where i = 1, 2, 3) represent the transconductance, output impedance, and equivalent parasitic capacitor of the ith stage, respectively. Gm1 and Gm2 are the compensation capacitors, and CL includes the load capacitor and output parasitic capacitor of the third stage. Assuming that the DC gain of the amplifier is very high and that the compensation and load capacitors are much larger than the parasitic capacitors, this circuit’s closed-loop signal transfer function

can be expressed as

The three poles can be derived by describing (11) and (12) as fp1, fp2, and fp3, respectively.

From Equation (10), we have two zeros, which are

The zero in the right half-plane may reduce the closed-loop stability; therefore, the design must connect a nulling resistor in series with the compensation capacitor to eliminate the right half-plane zero.

The structure of the first-stage amplifier, as depicted in

Figure 8, primarily comprises two sets of differential input cascode amplifiers. An auxiliary amplifier is incorporated into the cascode amplifier to eliminate the offset. The operational amplifier utilizes complementary NMOS and PMOS differential pairs for its input stage. This configuration provides two benefits: first, it enhances the transconductance of the amplifier; secondly, since the input transistors share the bias current, it doubles the output capability without increasing the power consumption.

The design of the second and third amplifier stages is based on a conventional folded cascode structure, with the output stage optimized for high-voltage operation. A linear transconductance loop tailored for high-voltage applications is introduced, with the overall architecture depicted in

Figure 9. To ensure effective cascading in the first stage, which has an output common-mode voltage of 1.8 V, the PMOS differential input pair of the subsequent stages employs a 4.2 V supply to maintain bias compatibility.

The output stage is an enhanced high-voltage design built upon a traditional Class AB structure, operating at a 55 V supply voltage to meet the demands of high-voltage applications. Within the designed linear transconductance loop, NDMOS (N-type Double-Diffused MOSFET) devices (DMOS1 and DMOS2) are utilized as high-voltage clamping devices to limit the voltage difference between the 5 V transistors and the supply rails to no more than 4 V, which thereby effectively protects low-voltage devices from breakdown.

Similarly, DMOS3 and DMOS4 are incorporated in the output stage to provide overvoltage protection for transistors M7 and M8. This design enhances the circuit’s adaptability to high-voltage environments and improves the amplifier’s gain performance by increasing the equivalent output impedance, Rout, which is expressed in Equation (18).

Switching regulators are commonly used for step-down conversion within system-on-chip or digital circuits in low-voltage applications. However, in high-voltage environments, this approach introduces significant electromagnetic interference and results in substantial ripple and noise in the output voltage. To address this, the proposed design employs a high-voltage LDO (Low-Dropout Regulator) as an intermediate stage for voltage conversion, directly generating a low-voltage supply from a 55 V high-voltage source to power the chip. The circuit is illustrated in

Figure 10. To protect the MOSFET (Metal Oxide Semiconductor Field Effect Transistor) in the error amplifier from high-voltage breakdown, high-voltage DMOS (Double-Diffused MOSFET) transistors are incorporated in each branch to isolate high-voltage nodes, ensuring the MOSFETs operate within a safe voltage range.

A bias circuit generates the reference for the error amplifier. A depletion-mode MOSFET, M1, and resistor, R1, form a current-generating branch in the bias circuit. Due to the negative threshold voltage, the Vth of M1 remains conductive when the circuit is unpowered, ensuring excellent self-startup characteristics without requiring an additional startup circuit. During regular operation, the branch current can be approximated as , forming a stable current source. Using a current mirror structure, this current is replicated in the branch generating , providing a stable reference voltage.

A pre-regulator structure is introduced to supply a stable voltage to the error amplifier and bias circuit to enhance the high-voltage protection further. This pre-regulator effectively limits the gate–source voltage of each MOSFET to prevent high-voltage breakdown and ensure circuit reliability.

Overvoltage protection circuits are critical in larger power systems, as shown in

Figure 11. This circuit primarily consists of a sampling circuit, a comparator, and an output shaping circuit. The comparator compares the two branch currents, I

1 and I

2, to determine whether an undervoltage condition exists. The current through the MOSFET is determined by the gate–source voltage V

GS and the width-to-length ratio (W/L). In this configuration, the circuit operates in two typical states: one is the V

GS-dominant mode, where the effect of V

GS on the current is greater than the effect of the width-to-length ratio. At this point, the voltage at node Y is pulled up to VDD (Voltage Drain Drain), the output V

out is high, and transistor M7 is turned off. The second is the width-to-length ratio-dominant mode, where the influence of V

GS is less than that of the width-to-length ratio. At this point, the voltage at node Y is pulled down to VSS (Voltage Source Source), the output V

out is low, and M7 is turned on. By comparing the magnitudes of I1 and I2, the circuit dynamically controls the conduction state of M7 to achieve undervoltage protection. When VDD rises from 0 V, the width-to-length ratio primarily determines the current. Since, at this point, the voltage V

Y at node Y is pulled down to VSS, V

out = 0, and M7 conducts. The output voltage

VX1 can be expressed as

When VDD rises to a specific value, the effect of V

GS gradually dominates, pulling the voltage at node Y up to VDD, resulting in V

out = 1 and M7 turning off. At this point, the output voltage

VX2 becomes

In the critical state where the effect of the width-to-length ratio on the current is balanced with the effect of V

GS on the current, I1 = I2. At this point, the threshold voltage

Vin for undervoltage protection can be derived, expressed as