Retesting Schemes That Improve Test Quality and Yield Using a Test Guardband

Abstract

:1. Introduction

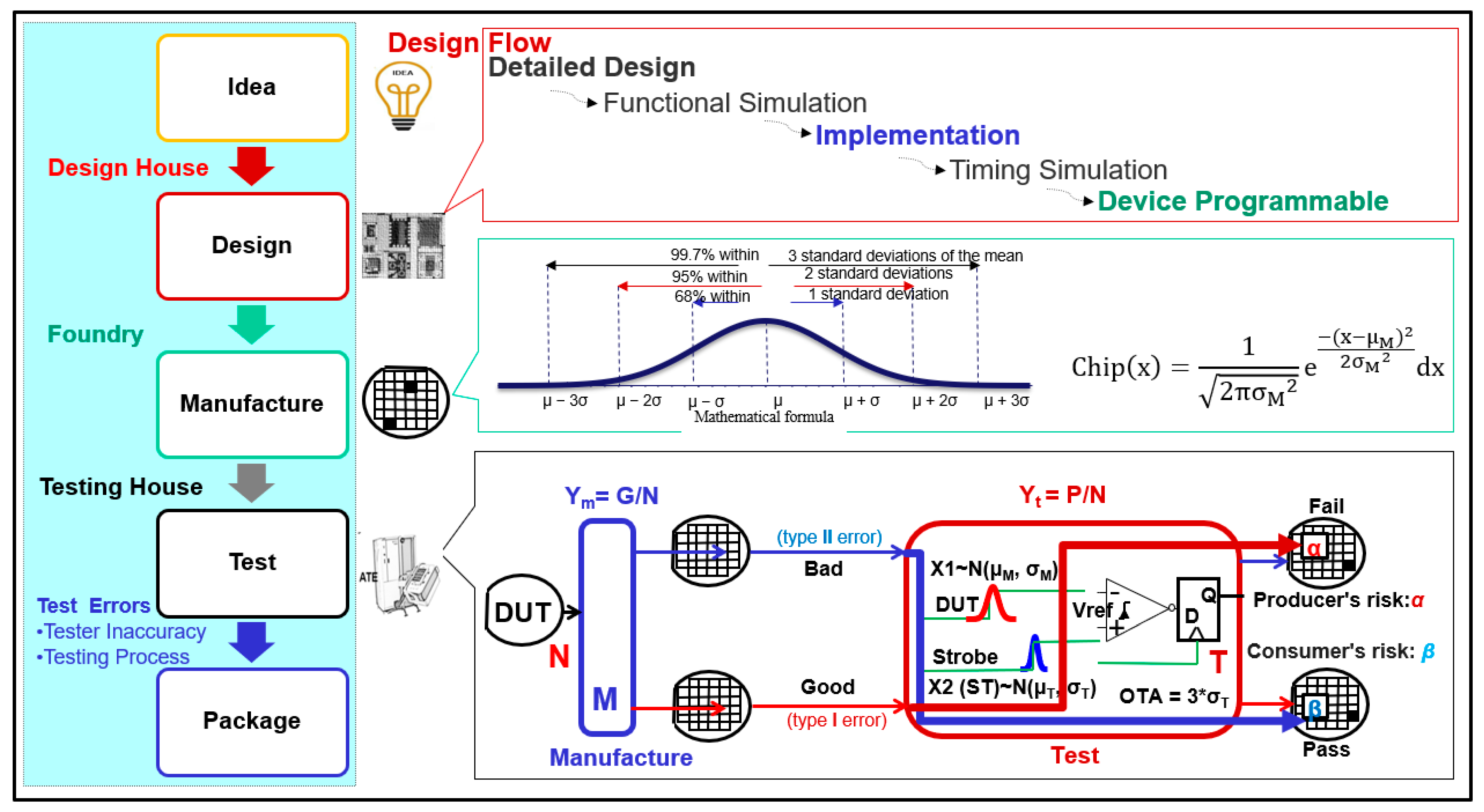

2. Semiconductor Manufacturing and Testing Process

2.1. Semiconductor Manufacturing Yield Calculation

2.2. Threshold Test System for Determining the Chip Quality

2.3. Chip Test Yield Estimation (Yt)

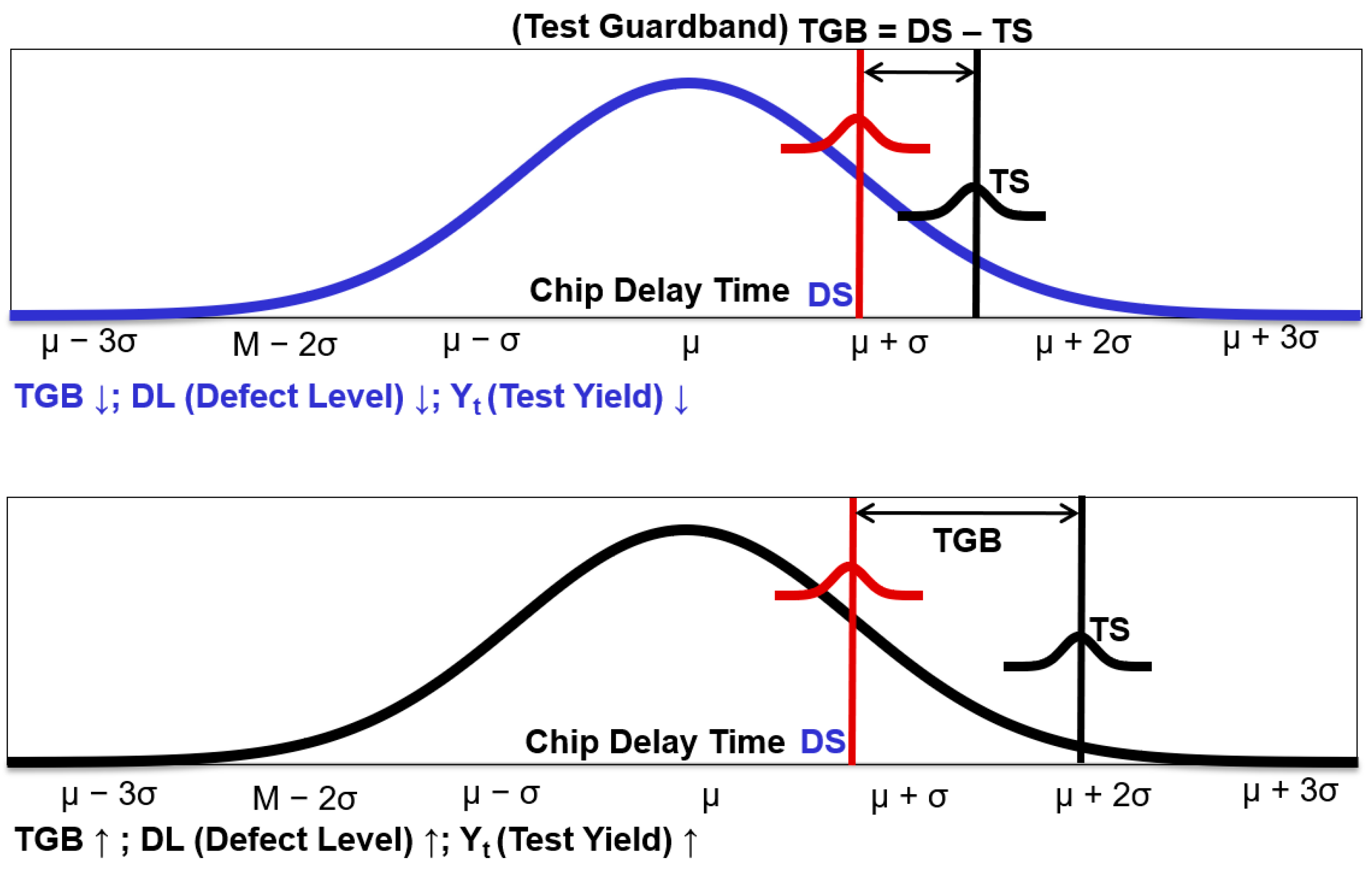

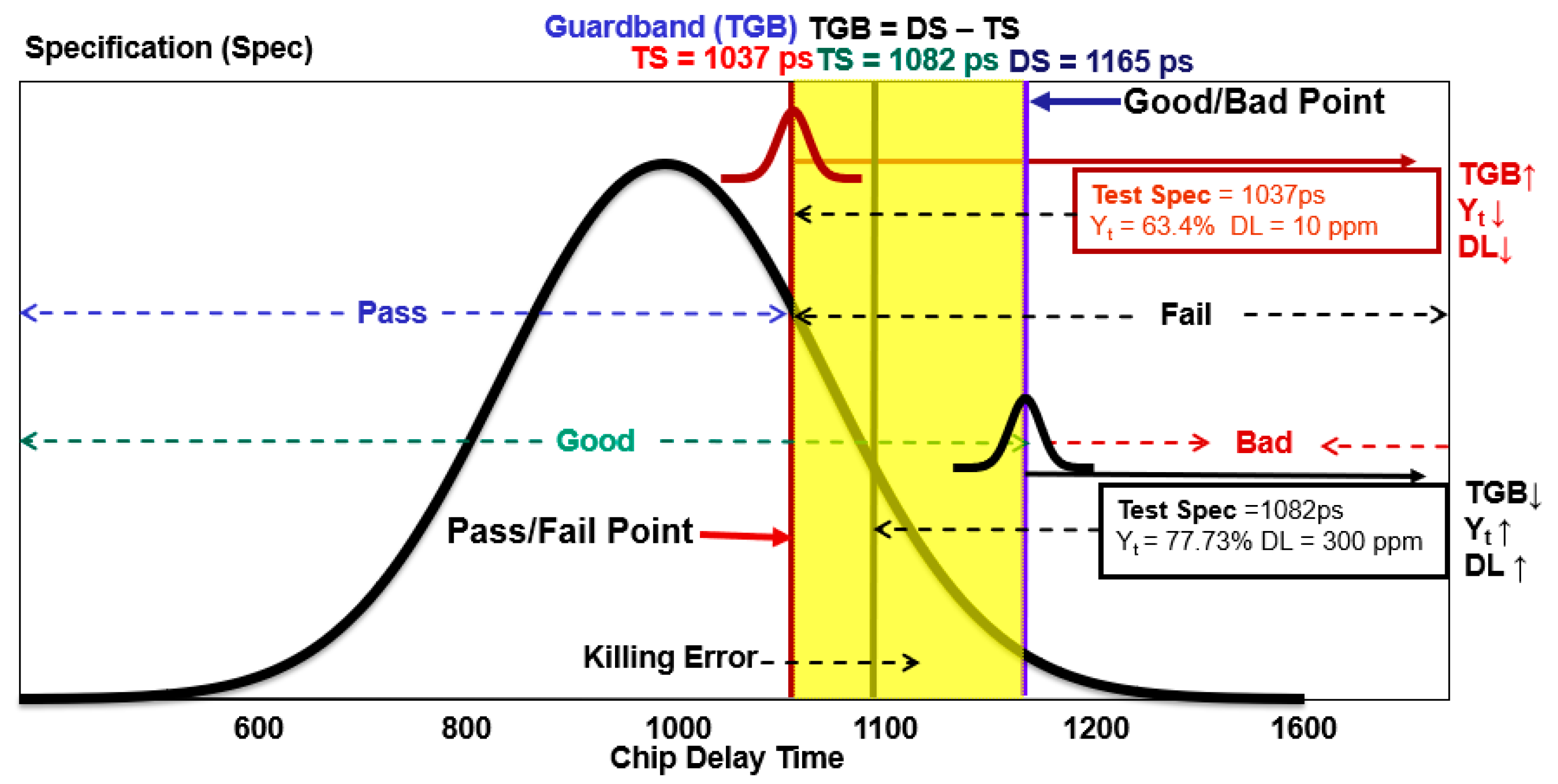

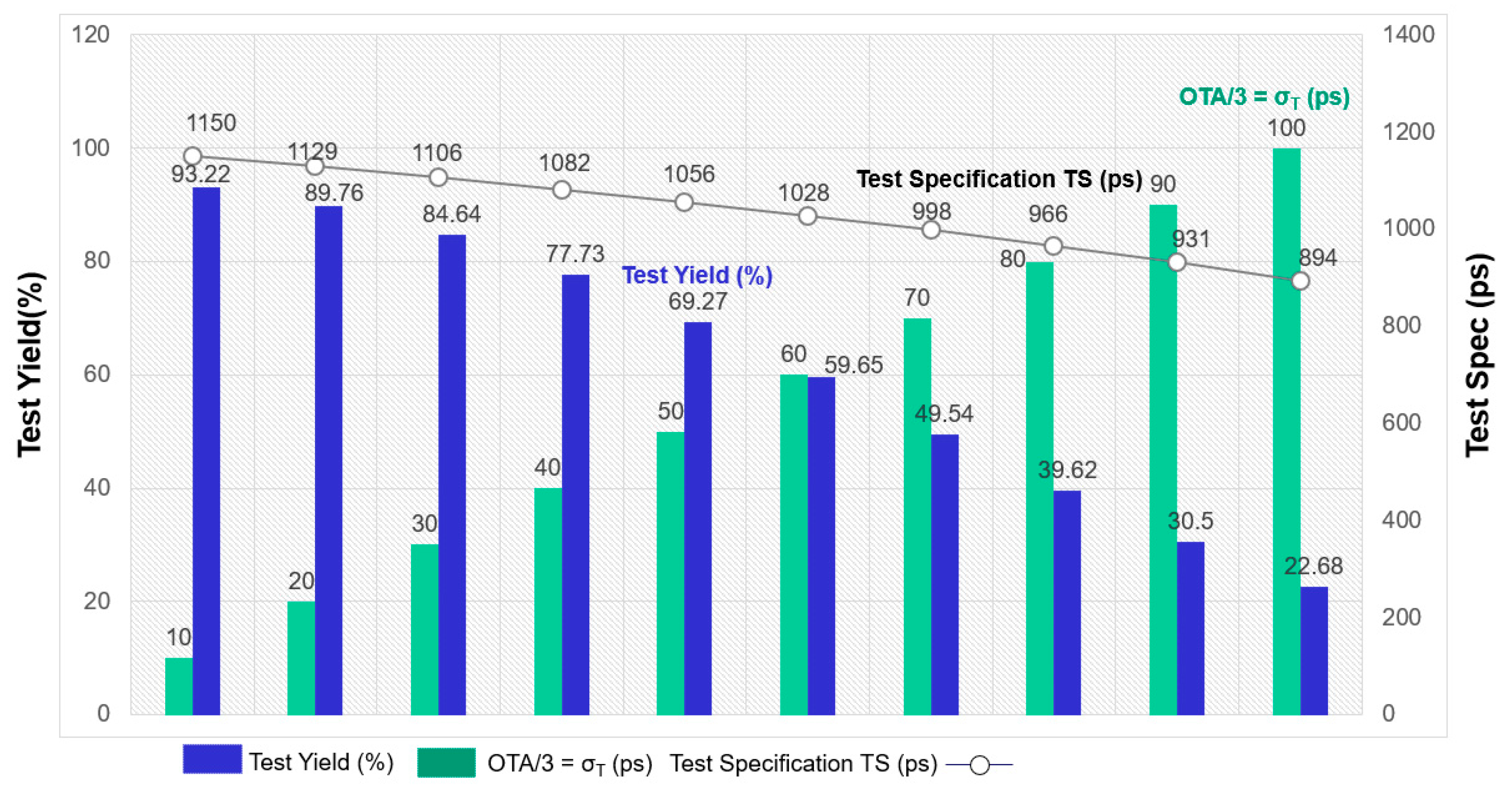

3. Impact of Guardband Testing on Yield

The Accuracy of Automated Test Equipment Affects the Test Results

4. Retest Solution to Improve the Yield

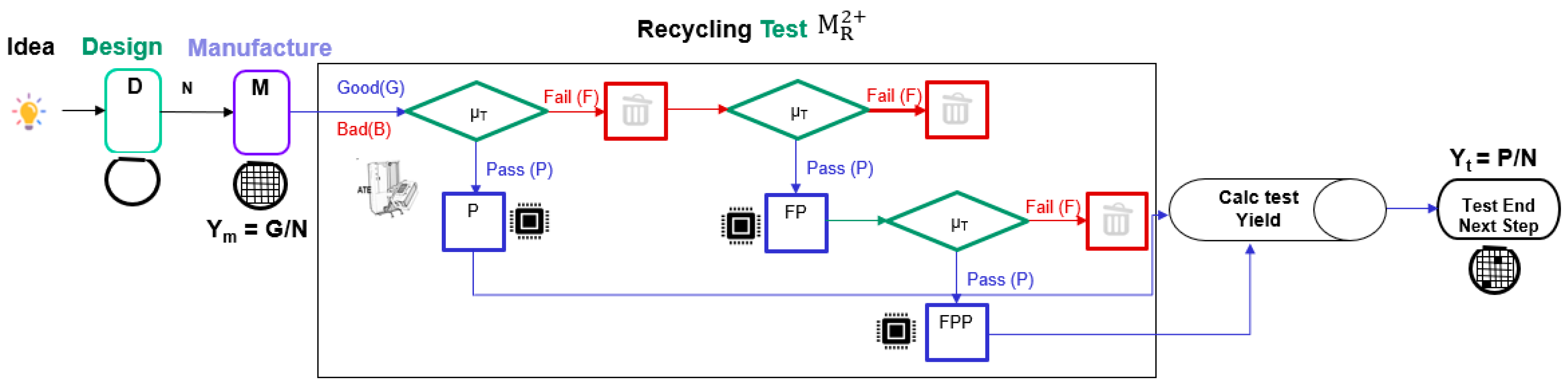

4.1. Scheme 1: Recycling Test Method

4.2. Scheme 2: Multiple Test Method

4.3. Scheme 3: Repeat Test Method

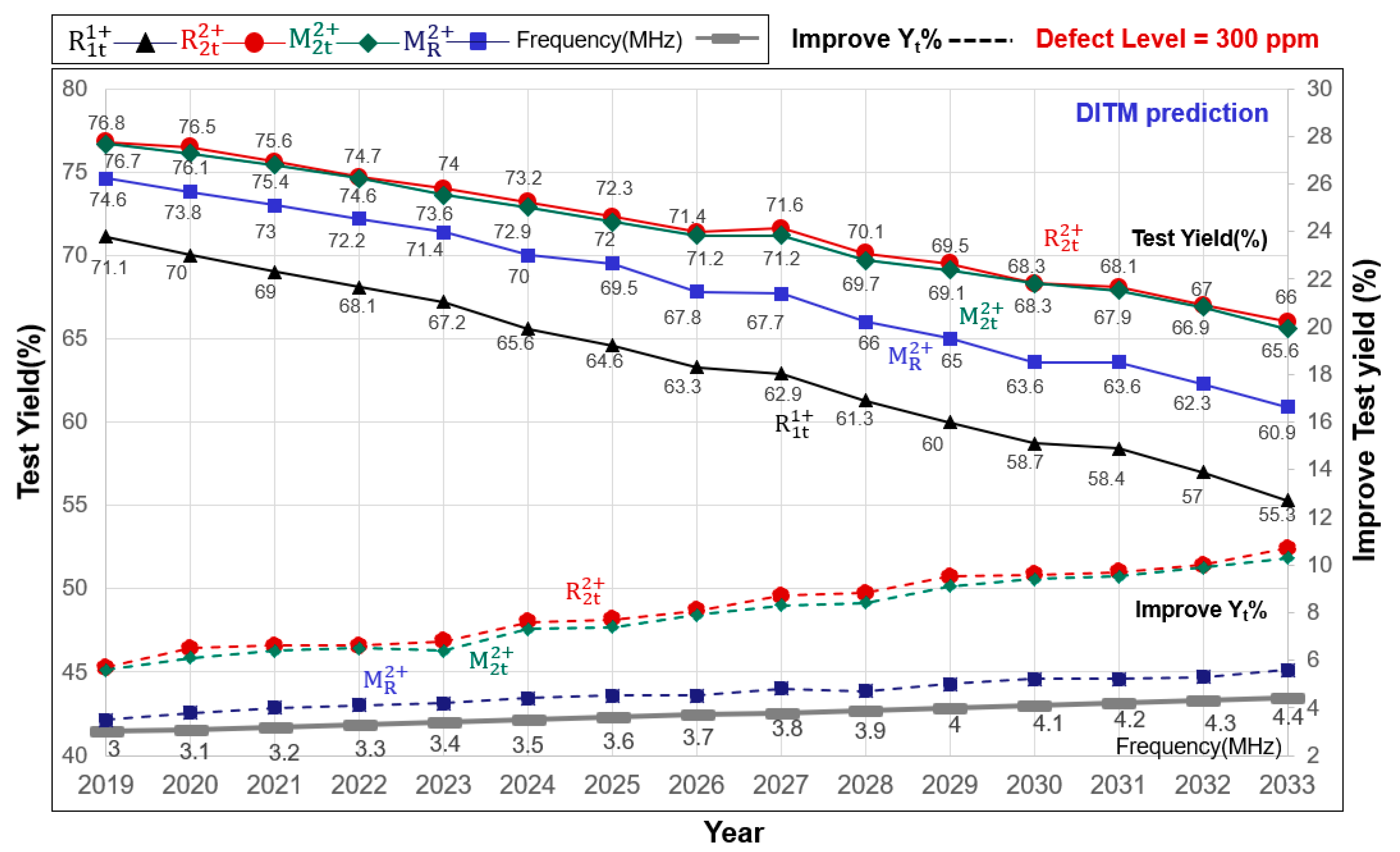

5. Apply Three Yield Improvement Test Solutions to the 2021 IRDS Datasheet (300 ppm)

- (1)

- The operation is simple; the test guardband is moved and the test method is changed.

- (2)

- Missing (β) and killing (α) errors are reduced.

- (3)

- The yield (Yt) of the test is increased.

- (4)

- The capability of the ATE substantially improves.

- (5)

- The chips that can be sold increase.

- (6)

- The profits of the company increase.

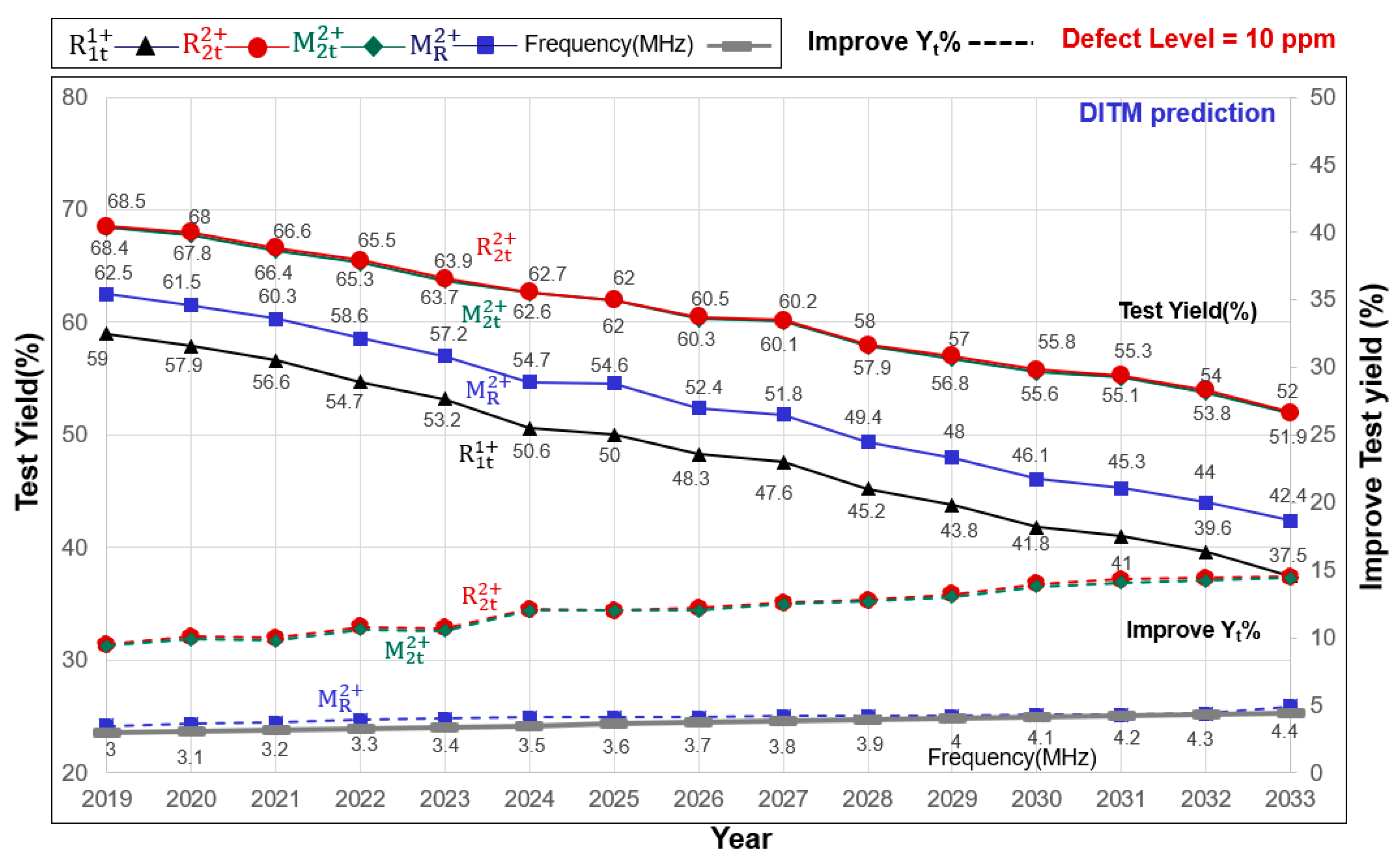

5.1. Use Retesting Test Method to Select High-Quality (10 ppm) Good Chips

- (1)

- The operation is simple; it only involves adjusting the TGB and changing the test method.

- (2)

- The proposed scheme can markedly reduce killing and missing errors.

- (3)

- It can substantially improve the yield (Yt) of the test.

- (4)

- It can substantially enhance the ability of the ATE.

- (5)

- The proposed scheme can significantly increase the number of chips that can be sold.

- (6)

- More high-quality chips can be selected.

- (7)

- The profits of the company significantly increase.

5.2. Retesting Scheme Advantages

- (1)

- The proposed solution does not require spending considerable time collecting large wafer data and can reduce software development costs.

- (2)

- This solution can be based on the estimated data, and the trend curve of the future wafer, Yt, can be calculated.

- (3)

- No additional hardware equipment is required, which not only reduces the cost of testing but also controls the relative quality of the product.

- (4)

- DITM’s rapid calculation is used to estimate the yield trend of the product. Primarily based on the effective data (specifications of the components proposed by the manufacturer) and the model of the testing machine (instrument parameters), the required test specifications can be rapidly calculated.

- (5)

- They are achieved by adjusting the TGB to avoid α errors and reduce β errors, which increases Yt and improves Yq.

- (6)

- They can effectively improve the performance of the testing machine.

- (7)

- They can use the current testing machines to screen out high-quality wafers.

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- International Technology Roadmap for Semiconductors, Test and Test Equipment. 1999. Available online: http://cva.stanford.edu/classes/cs99s/papers/roadmap1999.pdf (accessed on 7 July 2023).

- International Technology Roadmap for Semiconductors, Test and Test Equipment. 2001. Available online: https://www.dropbox.com/sh/vxigcu48nfe4t81/AACuMvZEh1peQ6G8miYFCSEJa?dl=0&preview=Test.pdf (accessed on 7 July 2023).

- International Technology Roadmap for Semiconductors 2.0., System Integration. 2015. Available online: http://www.itrs2.net/itrs-reports.html (accessed on 7 July 2023).

- The IEEE International Roadmap for Devices and Systems Table. 2017. Available online: https://irds.ieee.org/images/files/pdf/2017/2017IRDS_MM.pdf (accessed on 7 July 2023).

- Dalal, W.; Miao, S. The Value of Tester Accuracy. In Proceedings of the International Test Conference 1999, Atlantic City, NJ, USA, 30 September 1999; pp. 518–523. [Google Scholar]

- West, B.G. Accuracy requirements in at-speed functional test. In Proceedings of the IEEE International Test Conference (ITC), Baltimore, MD, USA, 30–30 September 1999; pp. 17–21. [Google Scholar]

- Yeh, C.H.; Chen, J.E. Predict the Test Yield of Future Integrated Circuits through the Deductive Estimation Method. J. Circuits Syst. Comput. 2023, 32, 2350202. [Google Scholar] [CrossRef]

- AEC-Q004; Zero Defects Guideline. Automotive Electronics Council: Sydney, Australia, 2006.

- AEC-Q001-REV-C; Guidelines for Part Average Testing. Automotive Electronics Council: Sydney, Australia, 2003.

- Raina, R. Achieving Zero-Defects for Automotive Applications. In Proceedings of the IEEE International Test Conference, Santa Clara, CA, USA, 28–30 October 2008; pp. 1–10. [Google Scholar]

- Nigh, P. Achieving quality levels of 100 DPM: It’s possible… but roll up your sleeves and be prepared to do some work. In Proceedings of the 2004 International Conferce on Test, Charlotte, NC, USA, 26–28 October 2004; p. 1420. [Google Scholar] [CrossRef]

- Horng, S.C.; Lin, S.Y.; Cheng, M.H.; Yang, F.Y.; Liu, C.H.; Lee, W.Y.; Tsai, C.H. Reducing the overkills and retests in wafer testing process. In Proceedings of the Advanced Semiconductor Manufacturing Conference and Workshop (IEEEI/SEMI 2003), Munich, Germany, 31 March–1 April 2003; pp. 286–291. [Google Scholar]

- Jena, S.K.; Biswas, S.; Deka, J.K. Maximizing Yield through Retesting of Rejected Circuits using Approximation Technique. In Proceedings of the 2020 IEEE Region 10 Conference (Tencon 2020), Osaka, Japan, 16–19 November 2020; pp. 182–187. [Google Scholar]

- Chang, P.; Huang, Y.K. Intelligent Method for Retesting a Wafer; Teslence Technology Co., Ltd.: Taipei, Taiwan, 2021; Available online: https://www.swtest.org/swtw_library/2019proc/PDF/S02_02_Chang_SWTest_2019.pdf (accessed on 28 February 2022).

- Kirmse, M.; Petersohn, U.; Paffrath, E. Optimized Test Error Detection by Probabilistic Retest Recommendation Models. In Proceedings of the 2011 Asian Test Symposium, New Delhi, India, 20–23 November 2011; pp. 317–322. [Google Scholar]

- Cheng, K.C.C.; Chen, L.L.Y.; Li, J.W.; Li, K.S.M.; Tsai, N.C.Y.; Wang, S.J.; Hsu, C.L. Machine Learning-Based Detection Method for Wafer Test Induced Defects. IEEE Trans. Semicond. Manuf. 2021, 34, 161–167. [Google Scholar] [CrossRef]

- Selg, H.; Jenihhin, M.; Ellervee, P. Wafer-Level Die Re-Test Success Prediction Using Machine Learning. In Proceedings of the 2020 IEEE Latin-American Test Symposium (LATS), Maceio, Brazil, 30 March–April 2020; pp. 1–5. [Google Scholar]

- Hua, L.; Deguang, Z. Study on Retest Reduction by Minimizing Probe Card Contact Resistance at Wafer Test. In Proceedings of the Semiconductor Technology International Conference (CSTIC), Shanghai, China, 14–15 March 2021; pp. 1–4. [Google Scholar]

- Fisher, P.D.; Nesbitt, R. The test of time. Clock-cycle estimation and test challenges for future microprocessors. IEEE Circuits Devices Mag. 1998, 14, 37–44. [Google Scholar] [CrossRef]

- Yeh, C.H.; Chen, J.E. Recycling Test Methods to Improve Test Capacity and Increase Chip Shipments. IEEE Des. Test 2022, 40, 45–52. [Google Scholar] [CrossRef]

- Yeh, C.H.; Chen, J.E. The Decision Mechanism Uses the Multiple-Tests Scheme to improve Test Yield in IC Testing. In Proceedings of the 2020 IEEE International Test Conference in Asia (ITC-Asia), Taipei, Taiwan, 23–25 September 2020; pp. 88–93. [Google Scholar]

- Yeh, C.H.; Chen, J.E. Repeated Testing Applications for Improving the IC Test Quality to Achieve Zero Defect Product Requirements. J. Electron. Test 2019, 35, 459–472. [Google Scholar] [CrossRef]

- The IEEE International Roadmap for Devices and Systems Table. 2021. Available online: https://irds.ieee.org/editions/2021 (accessed on 20 April 2022).

- Williams, R.H.; Hawkins, C.F. The Economics of Guardband Placement. In Proceedings of the IEEE International Test Conference—(ITC), Baltimore, MD, USA, 17–21 October 1993; pp. 218–225. [Google Scholar]

| OTA/3 = σT | ps | 100 | 90 | 80 | 70 | 60 | 50 | 40 | 30 | 20 | 10 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| Test specification (TS) | ps | 894 | 931 | 966 | 998 | 1028 | 1056 | 1082 | 1106 | 1129 | 1150 |

| TGB = DS − TS | ps | 271 | 234 | 199 | 167 | 137 | 109 | 83 | 59 | 36 | 15 |

| Yt | % | 22.68 | 30.5 | 39.62 | 49.54 | 59.65 | 69.27 | 77.73 | 84.64 | 89.76 | 93.22 |

| DL | ppm | 300 | 300 | 300 | 300 | 300 | 300 | 300 | 300 | 300 | 300 |

| Ym | % | 95% | 95% | 95% | 95% | 95% | 95% | 95% | 95% | 95% | 95% |

| Year | Unit | 2019 | 2020 | 2021 | 2022 | 2023 | 2024 | 2025 | 2026 | 2027 | 2028 | 2029 | 2030 | 2031 | 2032 | 2033 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Device period | us | 0.33 | 0.32 | 0.31 | 0.30 | 0.29 | 0.28 | 0.27 | 0.27 | 0.26 | 0.25 | 0.25 | 0.24 | 0.23 | 0.233 | 0.22 | |

| Chip frequency | GHz | 3.0 | 3.1 | 3.2 | 3.3 | 3.4 | 3.5 | 3.6 | 3.7 | 3.8 | 3.9 | 4.0 | 4.1 | 4.2 | 4.3 | 4.4 | |

| σM | ps | 79 | 76 | 74 | 72 | 70 | 68 | 66 | 64 | 62 | 61 | 59 | 58 | 56 | 55 | 54 | |

| μM | ps | 231 | 223 | 217 | 210 | 204 | 199 | 193 | 188 | 182 | 178 | 174 | 170 | 165 | 162 | 158 | |

| OTA | ps | 75 | 75 | 75 | 75 | 75 | 75 | 75 | 75 | 75 | 75 | 75 | 75 | 75 | 75 | 75 | |

| DL | ppm | 300.0 | 300.0 | 300.0 | 300.0 | 300.0 | 300.0 | 300.0 | 300.0 | 300.0 | 300.0 | 300.0 | 300.0 | 300.0 | 300.0 | 300.0 | |

| Yt | % | 71.1 | 70 | 69 | 68.1 | 67.2 | 65.6 | 64.6 | 63.3 | 62.9 | 61.3 | 60 | 58.7 | 58.4 | 57 | 55.3 | |

| TS(μT) | ps | 277 | 265 | 256 | 246 | 237 | 228 | 220 | 211 | 204 | 197 | 190 | 184 | 178 | 173 | 166 | |

| Yt | % | 74.6 | 73.8 | 73 | 72.2 | 71.4 | 70 | 69.5 | 67.8 | 67.7 | 66 | 65 | 63.6 | 63.6 | 62.3 | 60.9 | |

| TS(μT) | ps | 278 | 266 | 257 | 247 | 238 | 229 | 221 | 212 | 205 | 197 | 192 | 185 | 178 | 173 | 167 | |

| Yield↑ | Improvement | % | 3.5 | 3.8 | 4 | 4.1 | 4.2 | 4.4 | 4.5 | 4.5 | 4.8 | 4.7 | 5 | 5.2 | 5.2 | 5.3 | 5.6 |

| Yt | % | 76.7 | 76.1 | 75.4 | 74.6 | 73.6 | 72.9 | 72 | 71.2 | 71.2 | 69.7 | 69.1 | 68.3 | 67.9 | 66.9 | 65.6 | |

| TS1(μT1) TS2(μT2) | μT | ps | 308 302 | 297 291 | 287 282 | 277 271 | 268 261 | 259 254 | 251 246 | 243 237 | 237 230 | 229 314 | 223 217 | 216 211 | 210 204 | 205 199 | 199 192 |

| Yield↑ | Improvement | % | 5.6 | 6.1 | 6.4 | 6.5 | 6.4 | 7.3 | 7.4 | 7.9 | 8.3 | 8.4 | 9.1 | 9.4 | 9.5 | 9.9 | 10.3 |

| Yt | % | 76.8 | 76.5 | 75.6 | 74.7 | 74 | 73.2 | 72.3 | 71.4 | 71.6 | 70.1 | 69.5 | 68.3 | 68.1 | 67 | 66 | |

| TS(μT) | ps | 305 | 294 | 284 | 274 | 265 | 257 | 248 | 240 | 234 | 226 | 220 | 214 | 207 | 202 | 196 | |

| Yield↑ | Improvement | % | 5.7 | 6.5 | 6.6 | 6.6 | 6.8 | 7.6 | 7.7 | 8.1 | 8.7 | 8.8 | 9.5 | 9.6 | 9.7 | 10 | 10.7 |

| Year | Unit | 2019 | 2020 | 2021 | 2022 | 2023 | 2024 | 2025 | 2026 | 2027 | 2028 | 2029 | 2030 | 2031 | 2032 | 2033 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Device period | us | 0.33 | 0.32 | 0.31 | 0.30 | 0.29 | 0.28 | 0.27 | 0.27 | 0.26 | 0.25 | 0.25 | 0.24 | 0.23 | 0.233 | 0.22 | |

| Chip frequency | GHz | 3.0 | 3.1 | 3.2 | 3.3 | 3.4 | 3.5 | 3.6 | 3.7 | 3.8 | 3.9 | 4.0 | 4.1 | 4.2 | 4.3 | 4.4 | |

| σM | ps | 79 | 76 | 74 | 72 | 70 | 68 | 66 | 64 | 62 | 61 | 59 | 58 | 56 | 55 | 54 | |

| μM | ps | 231 | 223 | 217 | 210 | 204 | 199 | 193 | 188 | 182 | 178 | 174 | 170 | 165 | 162 | 158 | |

| OTA | ps | 75 | 75 | 75 | 75 | 75 | 75 | 75 | 75 | 75 | 75 | 75 | 75 | 75 | 75 | 75 | |

| DL | ppm | 10.0 | 10.0 | 10.0 | 10.0 | 10.0 | 10.0 | 10.0 | 10.0 | 10.0 | 10.0 | 10.0 | 10.0 | 10.0 | 10.0 | 10.0 | |

| Yt | % | 59 | 57.9 | 56.6 | 54.7 | 53.2 | 50.6 | 50 | 48.3 | 47.6 | 45.2 | 43.8 | 41.8 | 41 | 39.6 | 37.5 | |

| TS(μT) | ps | 250 | 239 | 230 | 219 | 210 | 200 | 193 | 185 | 178 | 170 | 164 | 157 | 151 | 146 | 139 | |

| Yt | % | 62.5 | 61.5 | 60.3 | 58.6 | 57.2 | 54.7 | 54.6 | 52.4 | 51.8 | 49.4 | 48 | 46.1 | 45.3 | 44 | 42.4 | |

| TS(μT) | ps | 250 | 239 | 230 | 220 | 211 | 201 | 194 | 185 | 178 | 170 | 164 | 158 | 151 | 146 | 139 | |

| Yield↑ | Improvement | % | 3.5 | 3.6 | 3.7 | 3.9 | 4 | 4.1 | 4.1 | 4.1 | 4.2 | 4.2 | 4.2 | 4.3 | 4.3 | 4.4 | 4.9 |

| Yt | % | 68.4 | 67.8 | 66.4 | 65.3 | 63.7 | 62.6 | 62 | 60.3 | 60.1 | 57.9 | 56.8 | 55.6 | 55.1 | 53.8 | 51.9 | |

| TS1(μT1) TS2(μT2) | μT | ps | 286 283 | 275 271 | 266 262 | 256 252 | 246 241 | 238 234 | 230 225 | 222 219 | 215 211 | 207 203 | 201 197 | 195 191 | 189 185 | 184 180 | 177 173 |

| Yield↑ | Improvement | % | 9.4 | 9.9 | 9.8 | 10.6 | 10.5 | 12 | 12 | 12 | 12.5 | 12.7 | 13 | 13.8 | 14.1 | 14.2 | 14.4 |

| Yt | % | 68.5 | 68 | 66.6 | 65.5 | 63.9 | 62.7 | 62 | 60.5 | 60.2 | 58 | 57 | 55.8 | 55.3 | 54 | 52 | |

| TS(μT) | μT | ps | 284 | 273 | 264 | 254 | 244 | 236 | 228 | 220 | 213 | 205 | 199 | 193 | 187 | 182 | 175 |

| Yield↑ | Improvement | % | 9.5 | 10.1 | 10 | 10.8 | 10.7 | 12.1 | 12 | 12.2 | 12.6 | 12.8 | 13.2 | 14 | 14.3 | 14.4 | 14.5 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yeh, C.-H.; Chen, J.-E. Retesting Schemes That Improve Test Quality and Yield Using a Test Guardband. Eng 2023, 4, 3007-3025. https://doi.org/10.3390/eng4040169

Yeh C-H, Chen J-E. Retesting Schemes That Improve Test Quality and Yield Using a Test Guardband. Eng. 2023; 4(4):3007-3025. https://doi.org/10.3390/eng4040169

Chicago/Turabian StyleYeh, Chung-Huang, and Jwu-E Chen. 2023. "Retesting Schemes That Improve Test Quality and Yield Using a Test Guardband" Eng 4, no. 4: 3007-3025. https://doi.org/10.3390/eng4040169

APA StyleYeh, C.-H., & Chen, J.-E. (2023). Retesting Schemes That Improve Test Quality and Yield Using a Test Guardband. Eng, 4(4), 3007-3025. https://doi.org/10.3390/eng4040169