A Monolithic Three-Axis Accelerometer with Wafer-Level Package by CMOS MEMS Process †

Abstract

:1. Introduction

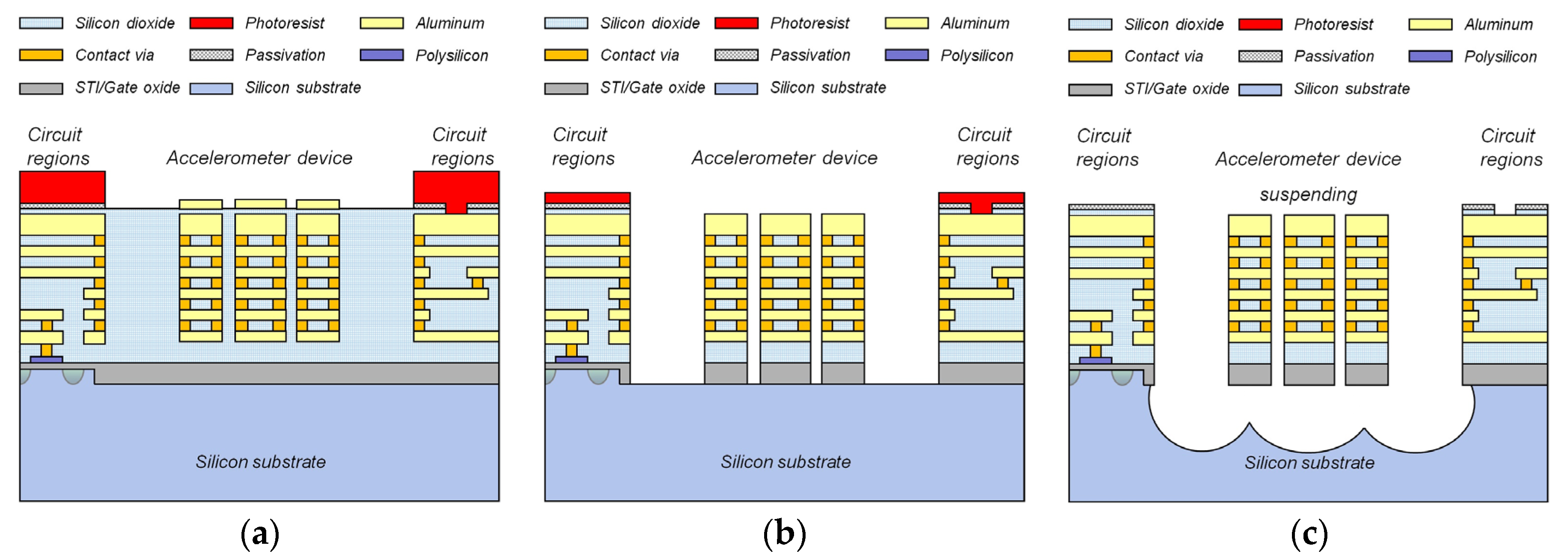

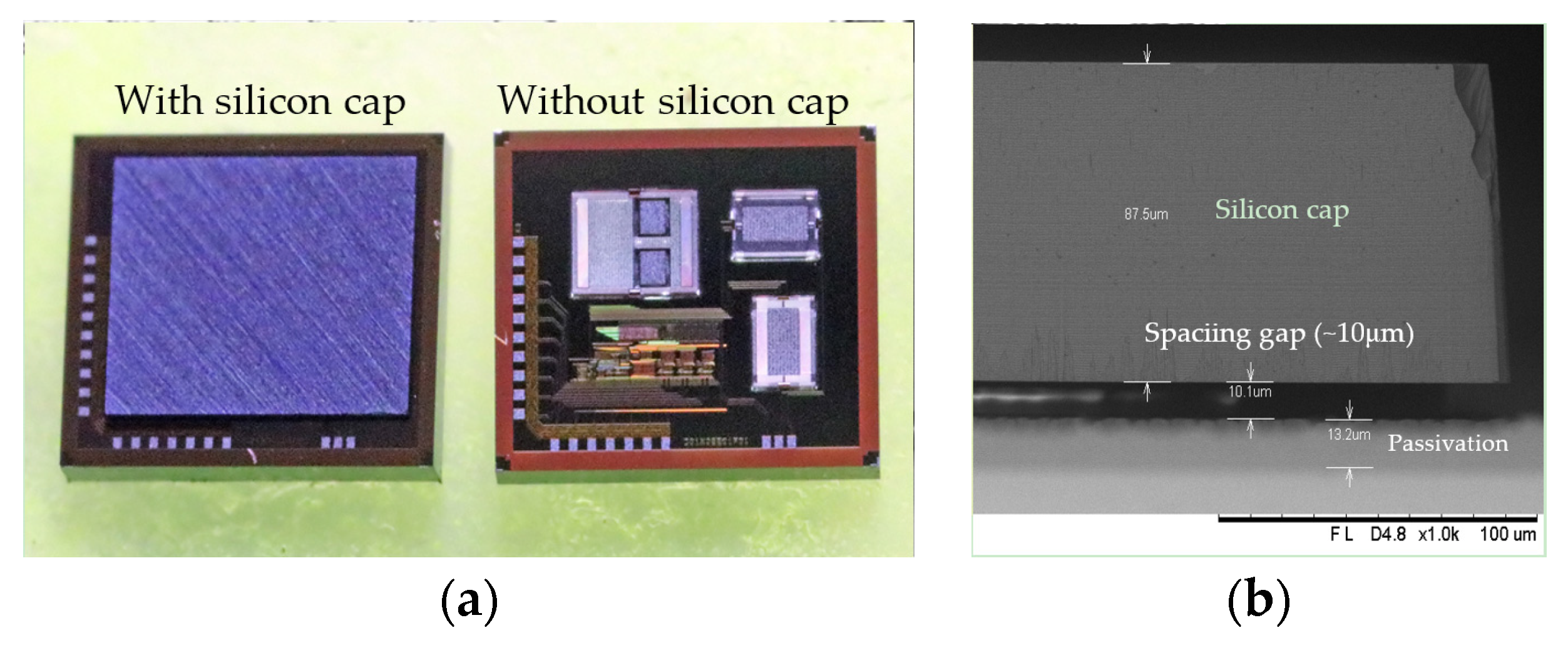

2. Fabrication

3. Design Features

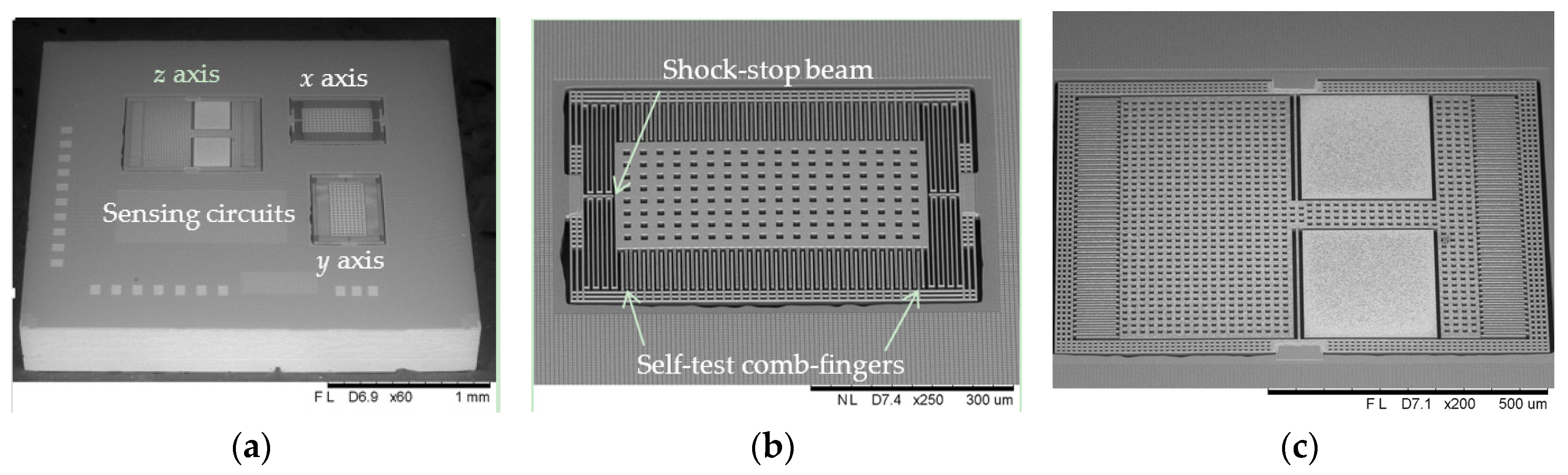

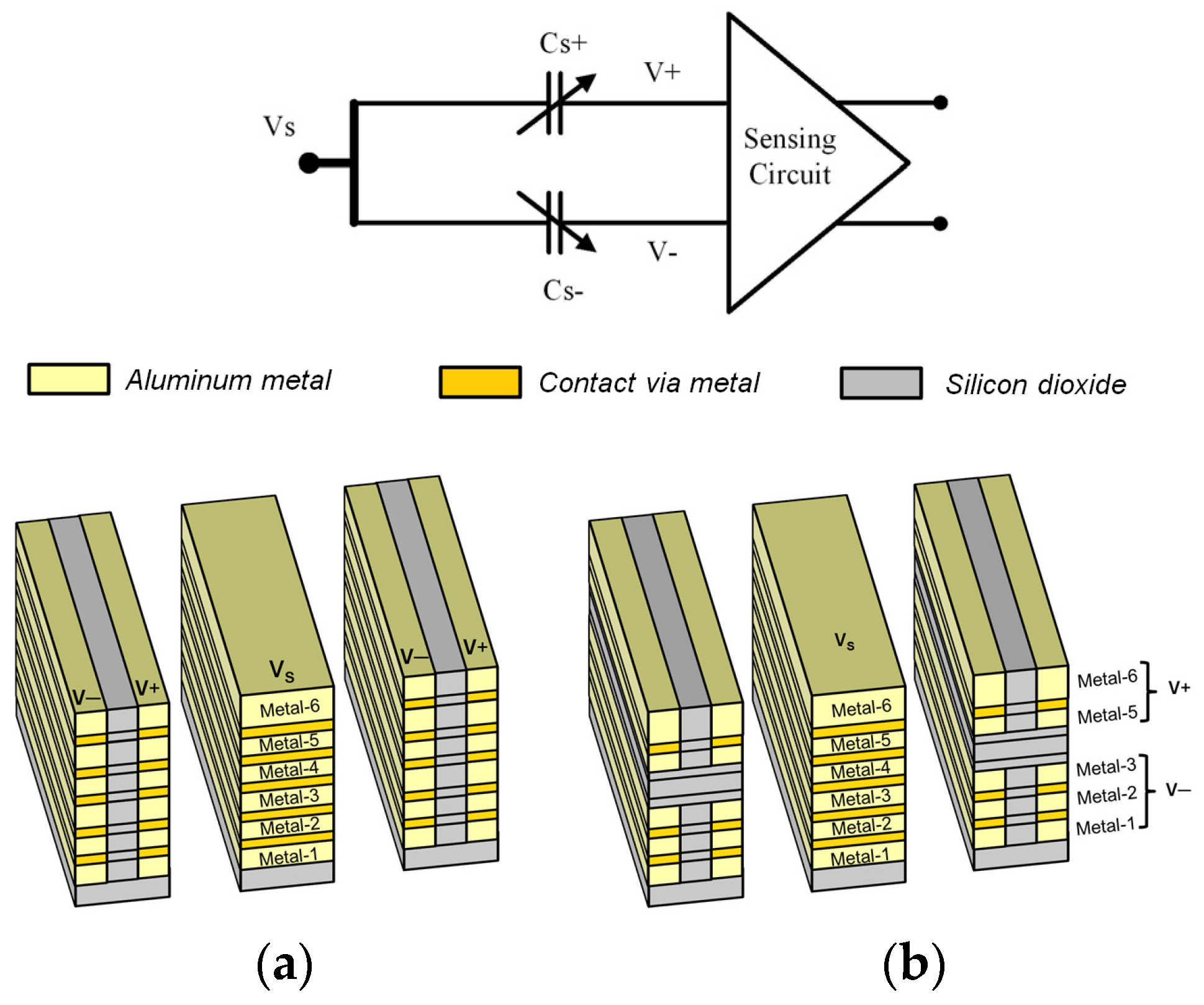

3.1. Micromechanical Resonator

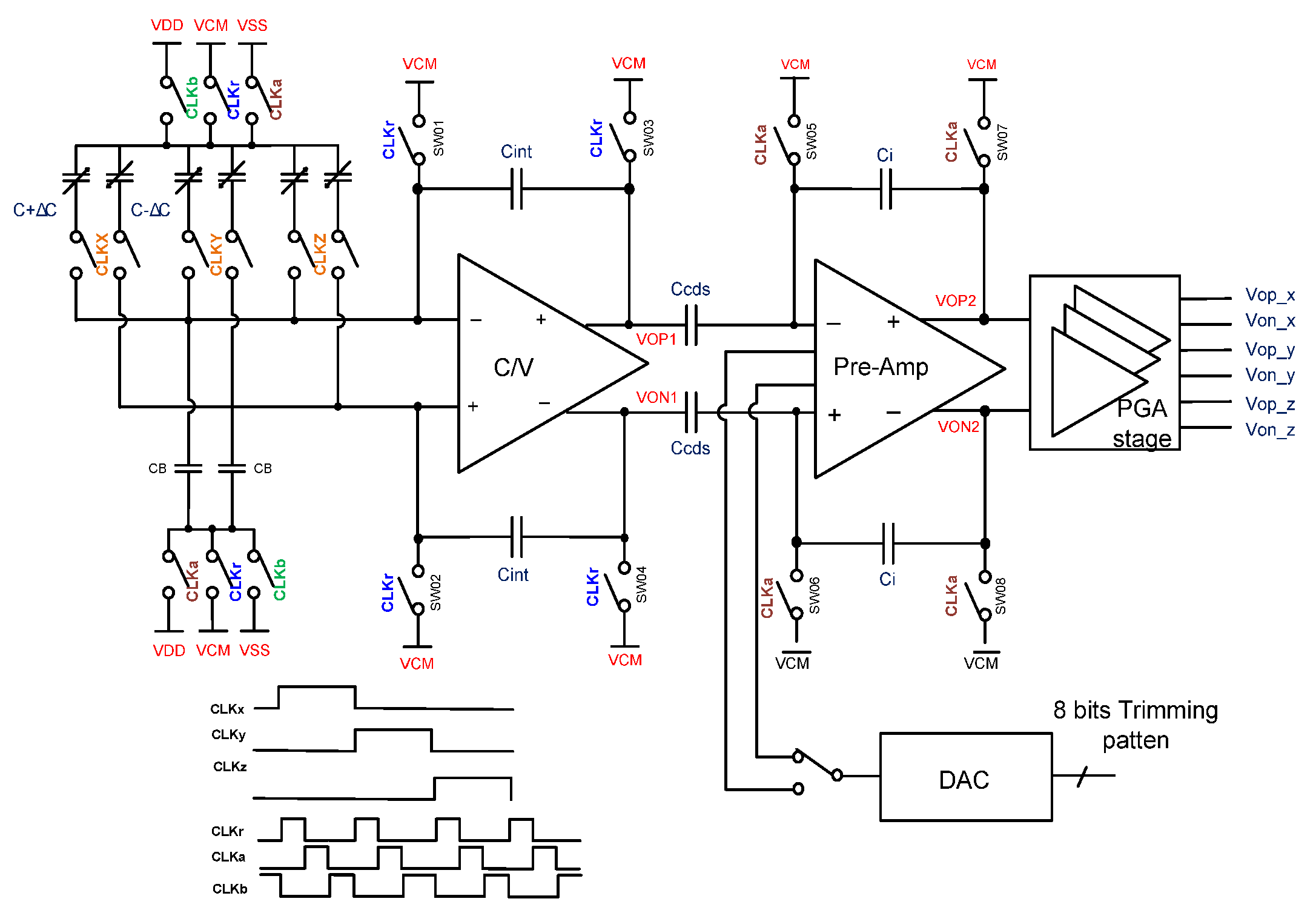

3.2. Circuits

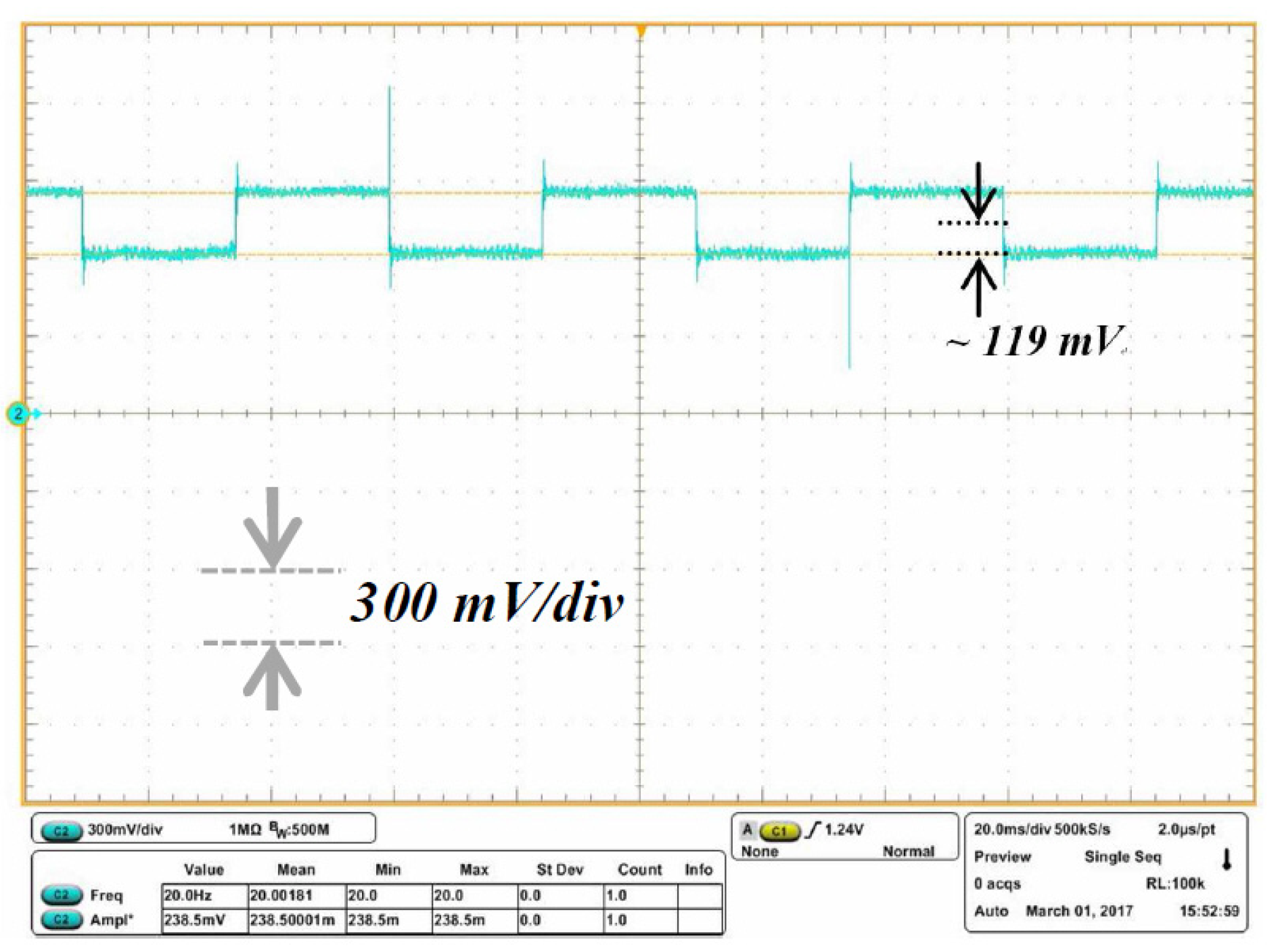

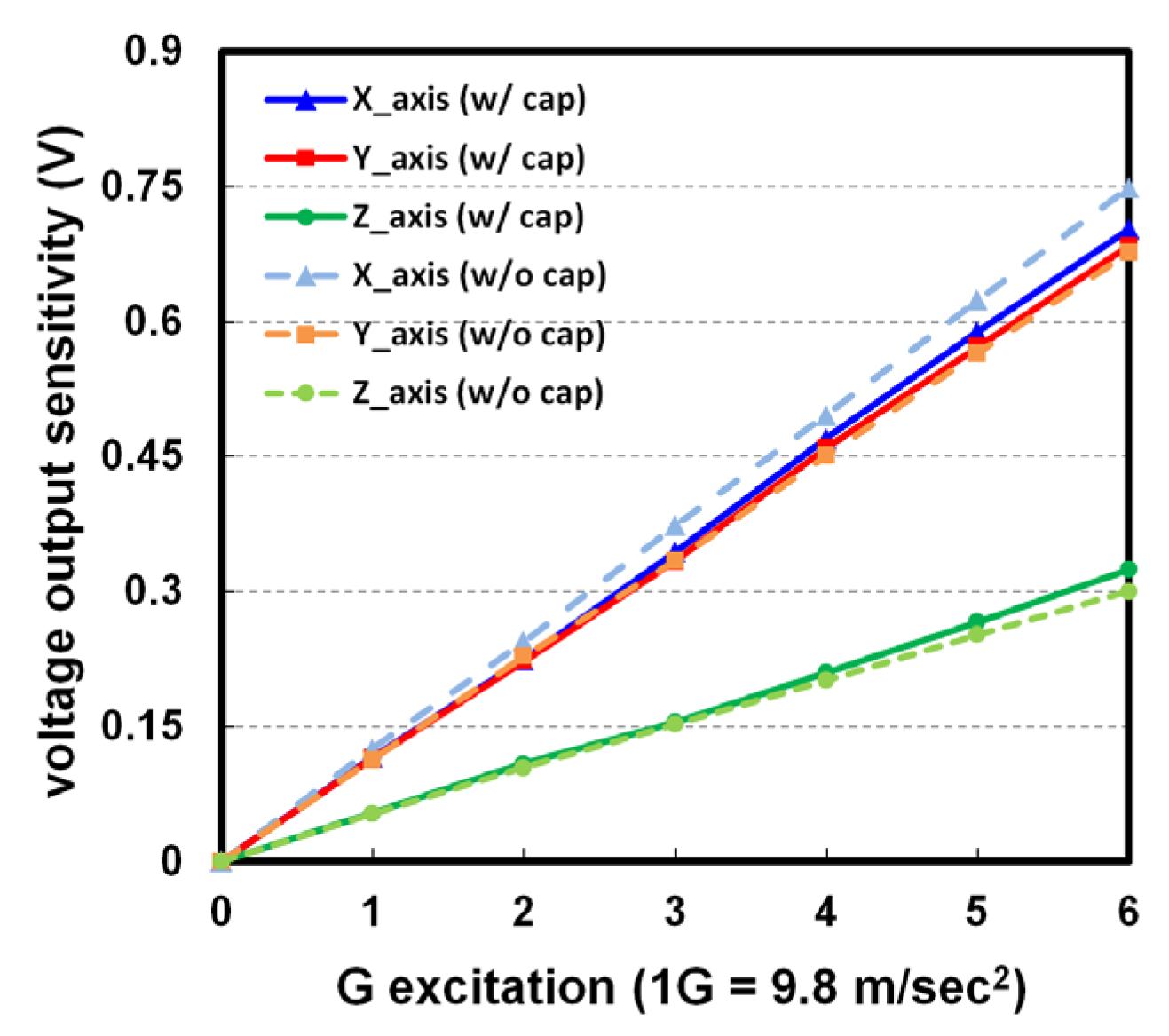

4. Experimental Results

5. Conclusions

Acknowledgments

Conflicts of Interest

References

- Vigna, B. MEMS epiphany. In Proceedings of the IEEE MEMS 2009, Sorrento, Italy, 26–29 January 2009; pp. 1–6. [Google Scholar]

- Marek, J. MEMS for automotive and consumer electronics. In Proceedings of the 2010 IEEE International Solid-State Circuits Conference, Francisco, CA, USA, 7–11 February 2010; pp. 9–17. [Google Scholar]

- Chua, S.L.; Razzaq, A.; Wee, K.H.; Li, K.H.; Yu, H.; Tan, C.S. 3D CMOS-MEMS stacking with TSV-less and face-to-face direct metal bonding. In Proceedings of the IEEE Symposium on VSLI Technology, Honolulu, HI, USA, 9–12 June 2014. [Google Scholar]

- Zhu, W.; Zhang, Y.; Meng, G.; Wallace, C.S.; Yazdi, N. A CMOS-integrated four-quadrant symmetric micro-g accelerometer. In Proceedings of the IEEE MEMS, Shanghai, China, 24–28 January 2016; pp. 926–929. [Google Scholar]

- Funk, K.; Emmerich, H.; Schilp, A.; Offenberg, M.; Neul, R.; Larmer, F. A surface micromachined silicon gyroscope using thick polysilicon layer. In Proceedings of the IEEE MEMS 1999, Orlando, FL, USA, 17–21 January 1999; pp. 57–60. [Google Scholar]

- Tseng, S.H.; Lu, M.S.C.; Wu, P.C.; Teng, Y.C.; Tsai, H.H.; Juang, Y.Z. Implementation of a monolithic capacitive accelerometer in a wafer-level 0.18 μm CMOS MEMS process. J. Micromech. Microeng. 2012, 22, 055010. [Google Scholar] [CrossRef]

- Klug, G. Advanced solutions for ultra-thin wafers and packaging. In Proceedings of the IEEE European Microelectronics and Packaging Conference (EMPC), Rimini, Italy, 16–18 June 2009; pp. 1–4. [Google Scholar]

- Coventor Inc. 2014. CoSolveEM Toolbox Rev. A.

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tseng, S.H.; Yeh, C.Y.; Chang, A.Y.; Wang, Y.J.; Chen, P.C.; Tsai, H.H.; Juang, Y.Z. A Monolithic Three-Axis Accelerometer with Wafer-Level Package by CMOS MEMS Process. Proceedings 2017, 1, 337. https://doi.org/10.3390/proceedings1040337

Tseng SH, Yeh CY, Chang AY, Wang YJ, Chen PC, Tsai HH, Juang YZ. A Monolithic Three-Axis Accelerometer with Wafer-Level Package by CMOS MEMS Process. Proceedings. 2017; 1(4):337. https://doi.org/10.3390/proceedings1040337

Chicago/Turabian StyleTseng, S. H., C. Y. Yeh, A. Y. Chang, Y. J. Wang, P. C. Chen, H. H. Tsai, and Y. Z. Juang. 2017. "A Monolithic Three-Axis Accelerometer with Wafer-Level Package by CMOS MEMS Process" Proceedings 1, no. 4: 337. https://doi.org/10.3390/proceedings1040337

APA StyleTseng, S. H., Yeh, C. Y., Chang, A. Y., Wang, Y. J., Chen, P. C., Tsai, H. H., & Juang, Y. Z. (2017). A Monolithic Three-Axis Accelerometer with Wafer-Level Package by CMOS MEMS Process. Proceedings, 1(4), 337. https://doi.org/10.3390/proceedings1040337