Progress in Passive Silicon Photonic Devices: A Review

Abstract

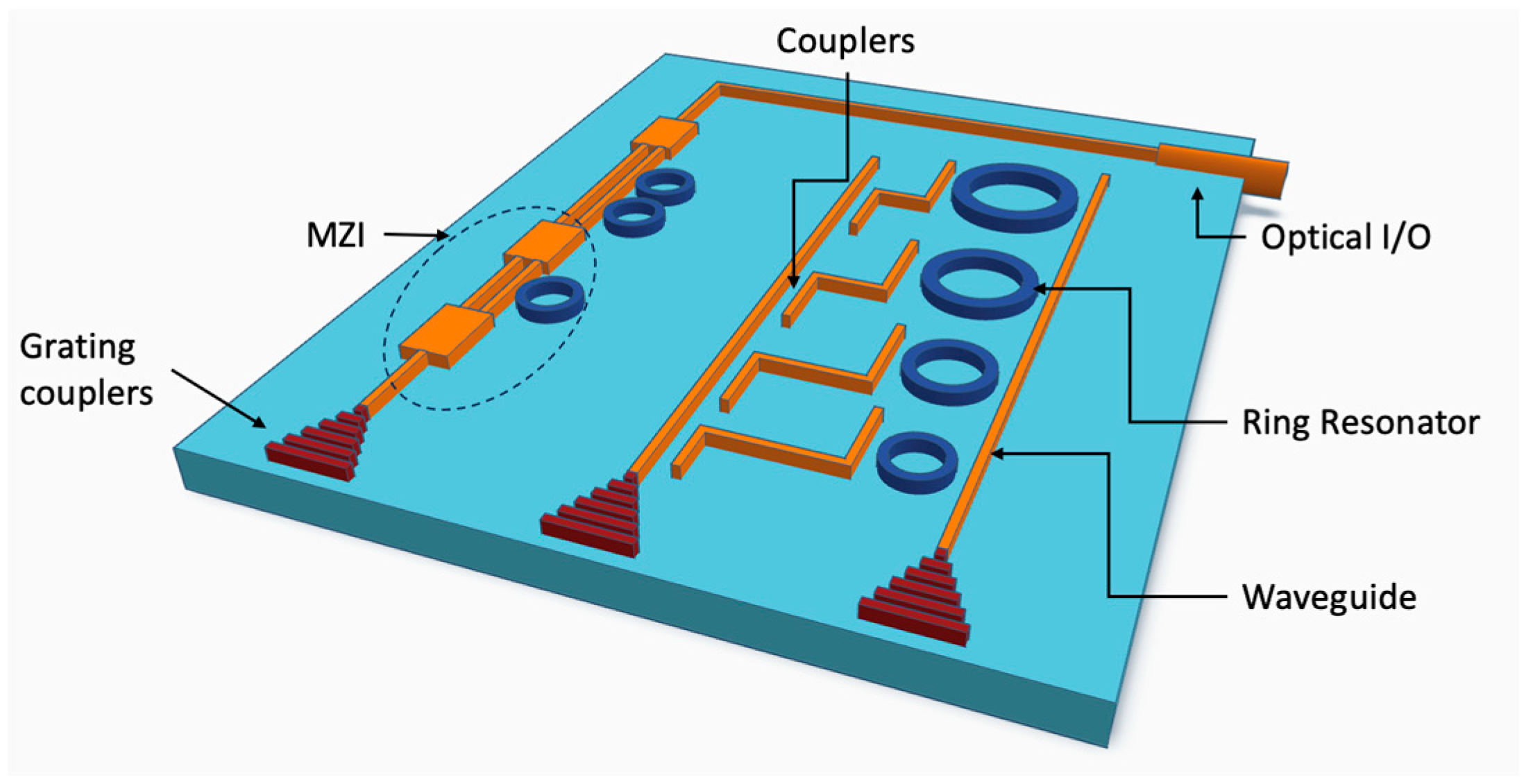

1. Introduction

1.1. The Imperative for Silicon Photonics in the AI and Zettabyte Era

1.2. Passive vs. Active Devices in PICs

1.3. Overview of the Review

2. Fundamental Building Blocks: Waveguides for Light Confinement and Propagation

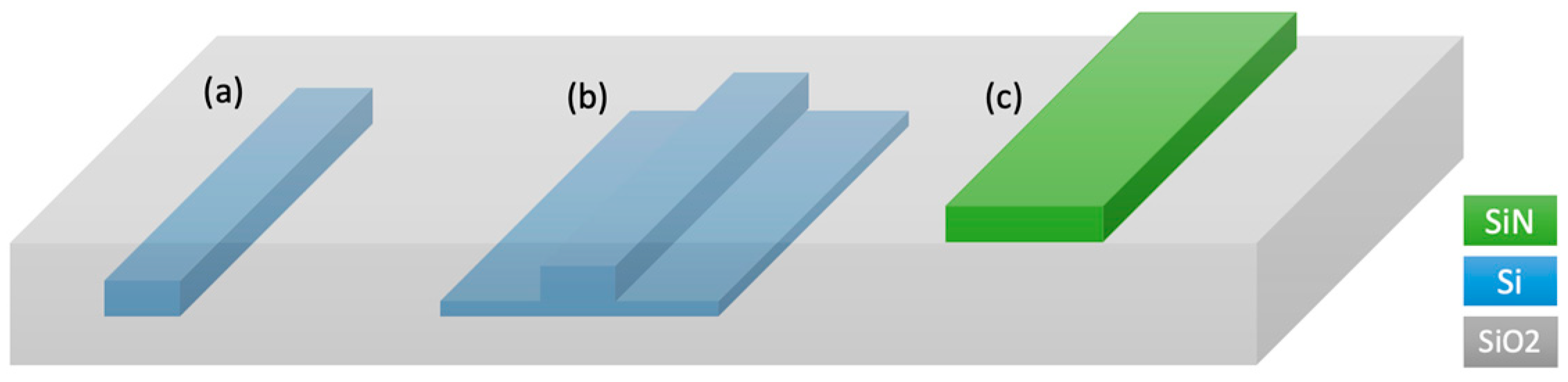

2.1. Conventional Silicon Waveguide Architectures on SOI

2.2. Strip Waveguides

2.3. Rib Waveguides

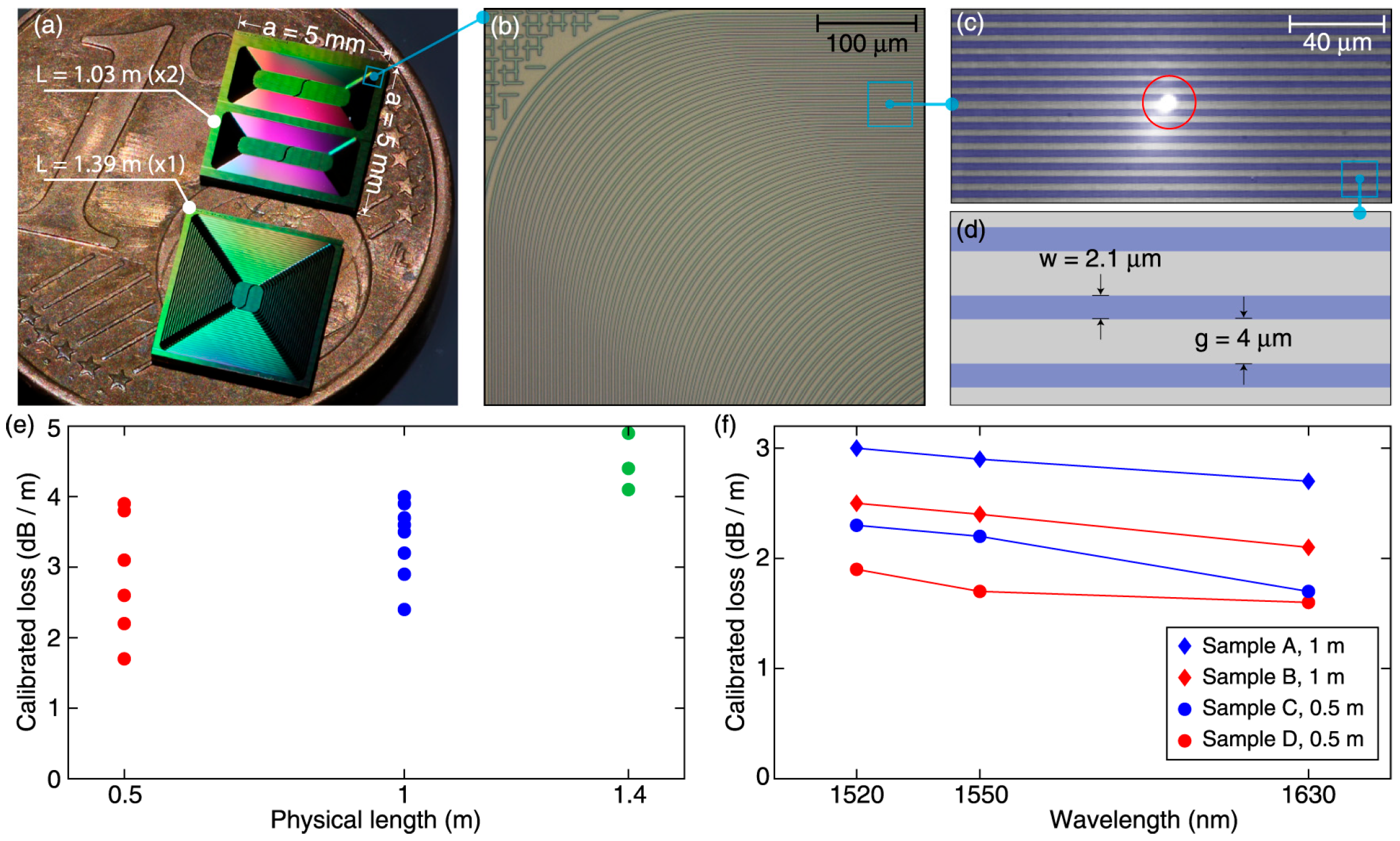

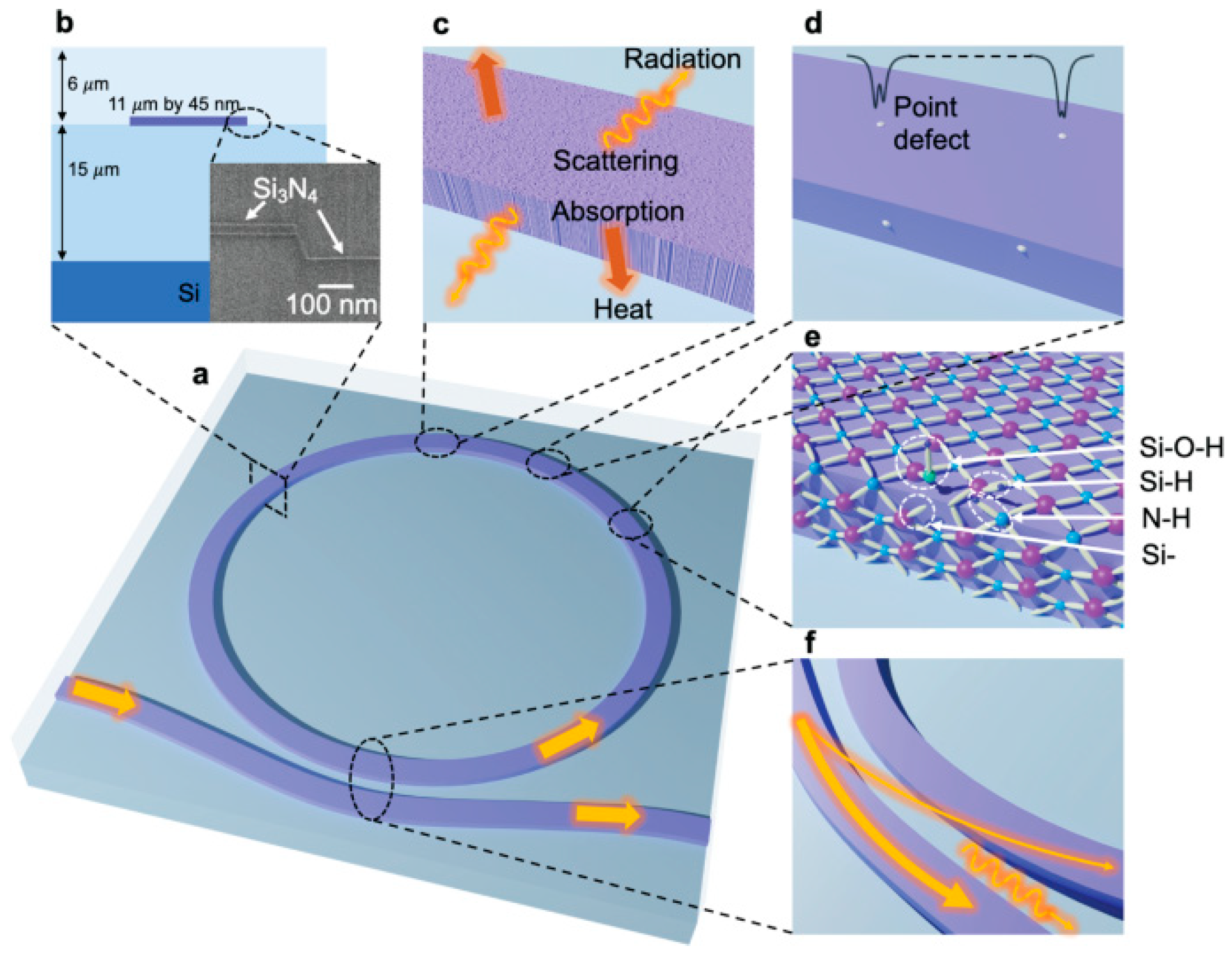

2.4. The Silicon Nitride (SiN) Platform: A Key Alternative

2.5. Advanced Waveguide Engineering: Sub-Wavelength Grating (SWG) Metamaterials

3. Light Coupling and Splitting: The Interface to and Within the Chip

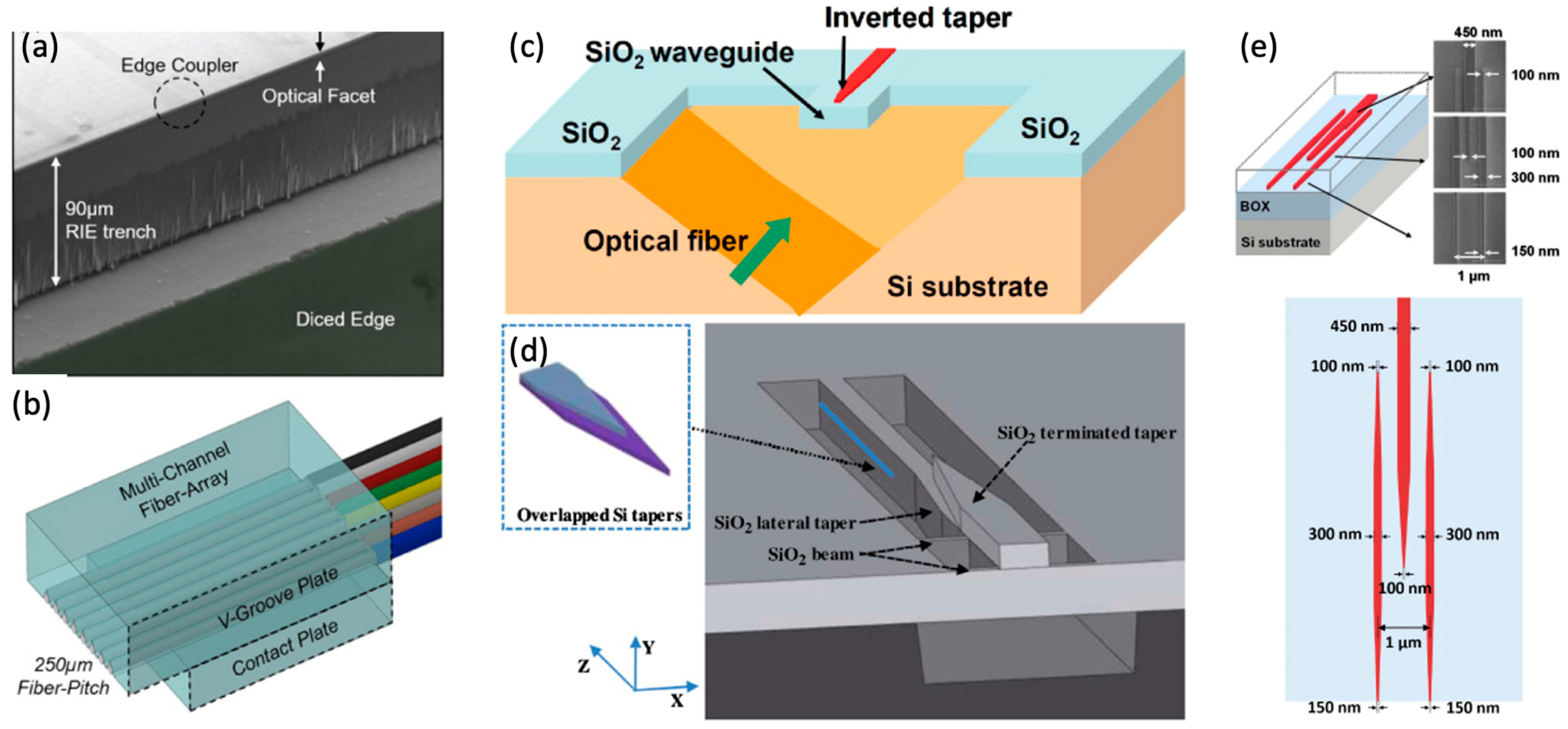

3.1. Fiber-to-Chip Couplers

3.1.1. Grating Couplers (GCs)

3.1.2. Edge Couplers (ECs)

3.2. On-Chip Power Splitters and Routers

3.2.1. Y-Branch Splitters

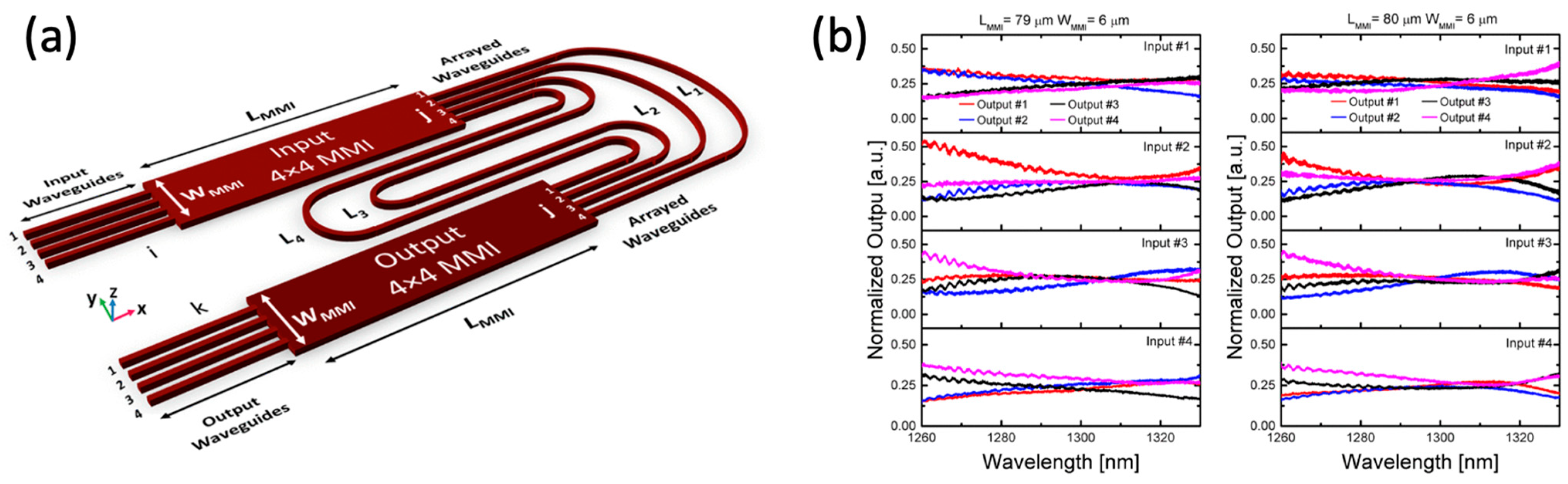

3.2.2. Multimode Interference (MMI) Couplers

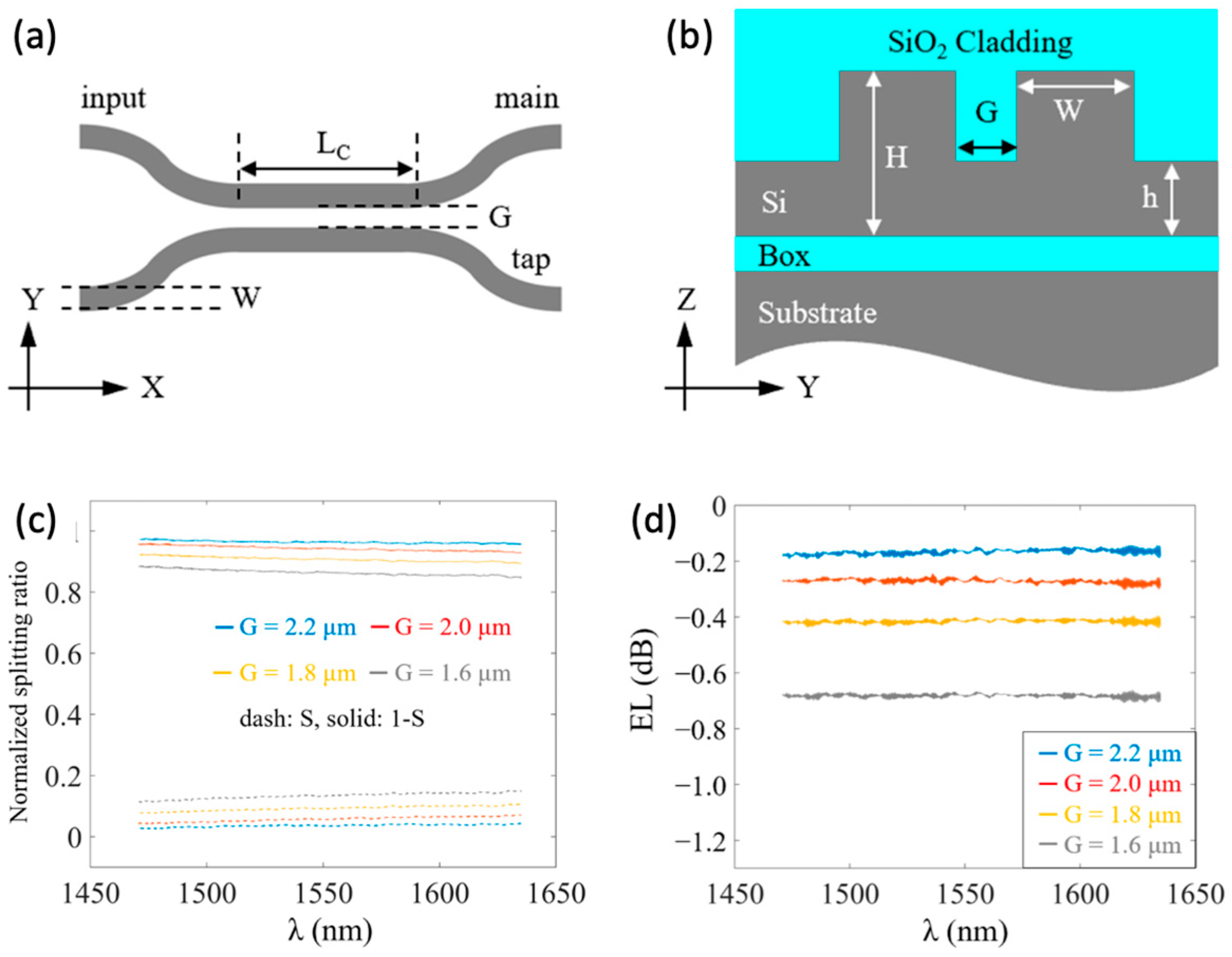

3.2.3. Directional Couplers (DCs)

4. Wavelength Filtering and Routing: Manipulating the Spectrum

4.1. Resonant Structures: Microring Resonators (MRRs)

4.2. Interferometric Devices: Mach–Zehnder Interferometers (MZIs)

4.3. Channel Demultiplexing: Arrayed Waveguide Gratings (AWGs)

5. Foundry Comparison for Fabrication

5.1. The Multi-Project Wafer (MPW) Model

5.2. Comparative Overview of Major Foundries

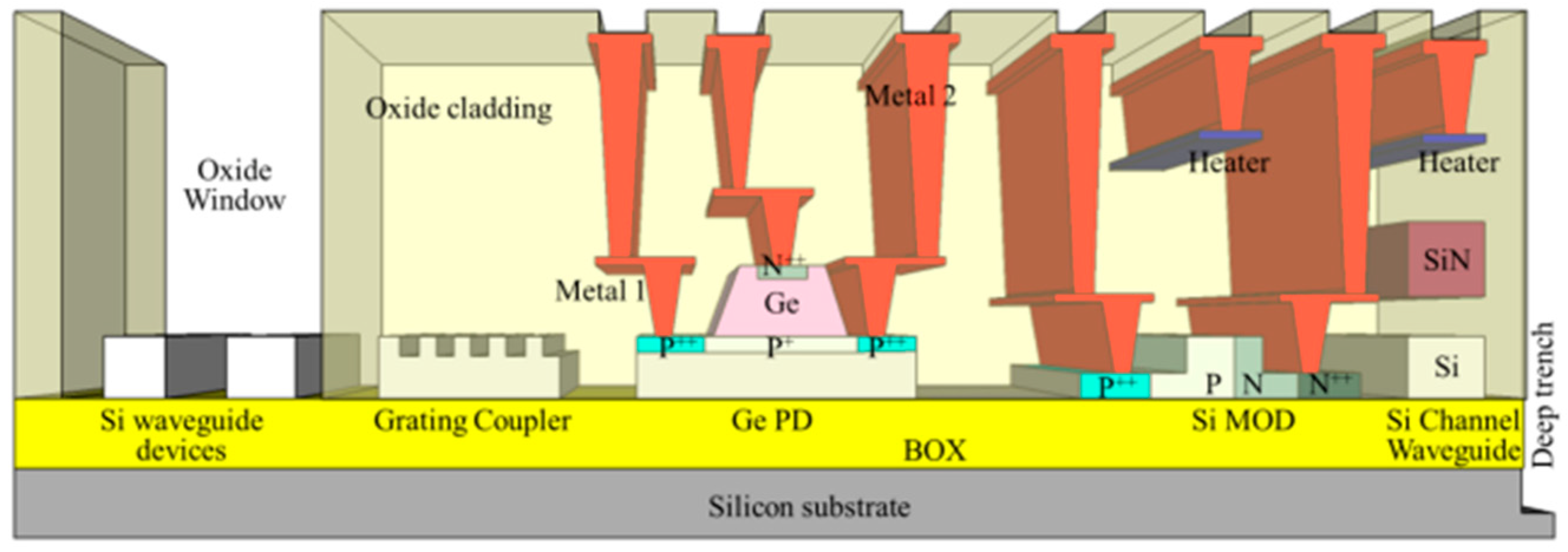

5.3. Integration with Active Devices: Approaches for System-Level Functionality

5.3.1. Monolithic Integration

5.3.2. Heterogeneous Integration

5.3.3. Hybrid Integration

6. Challenges and Future Outlook

6.1. Persistent Technical Hurdles

6.1.1. Polarization Management

6.1.2. Packaging and Integration

6.2. Emerging Trends and Future Directions

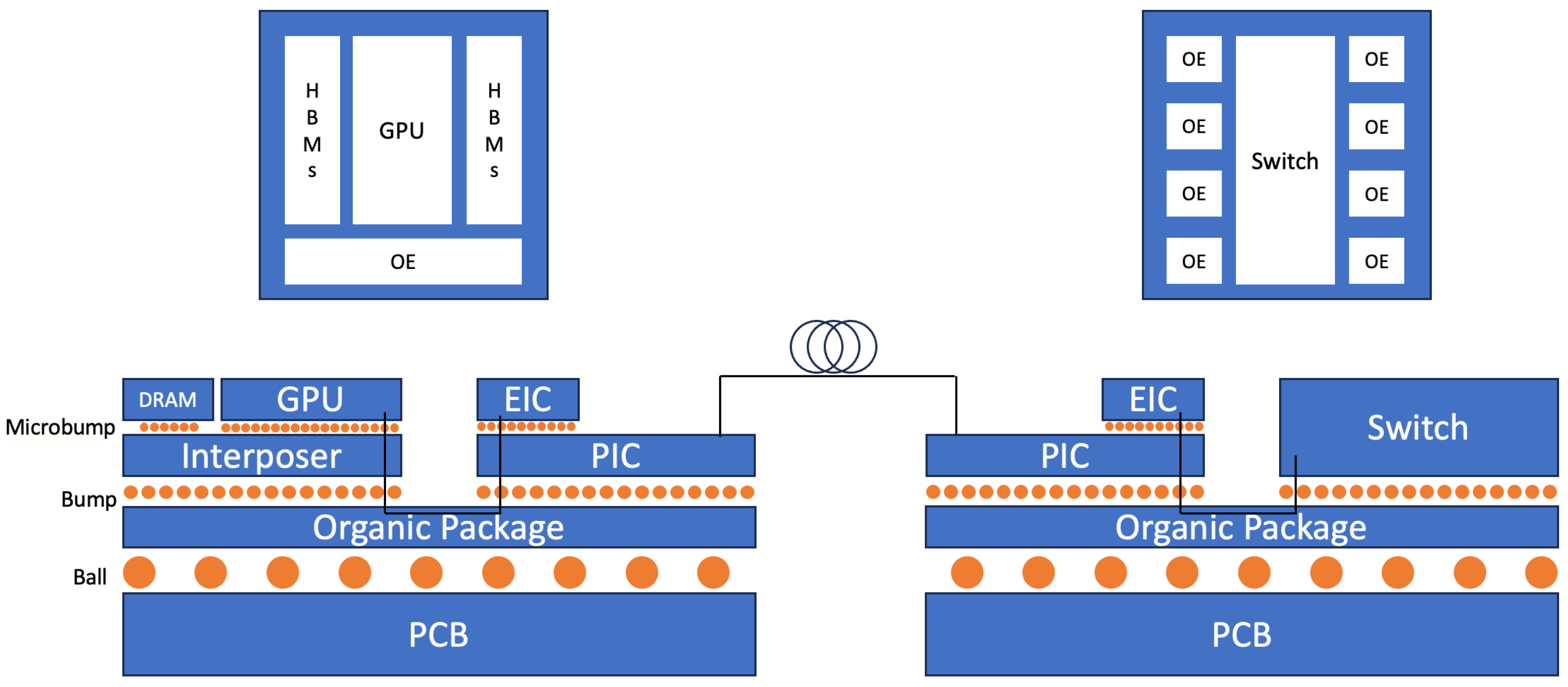

6.2.1. Co-Packaged Optics (CPO)

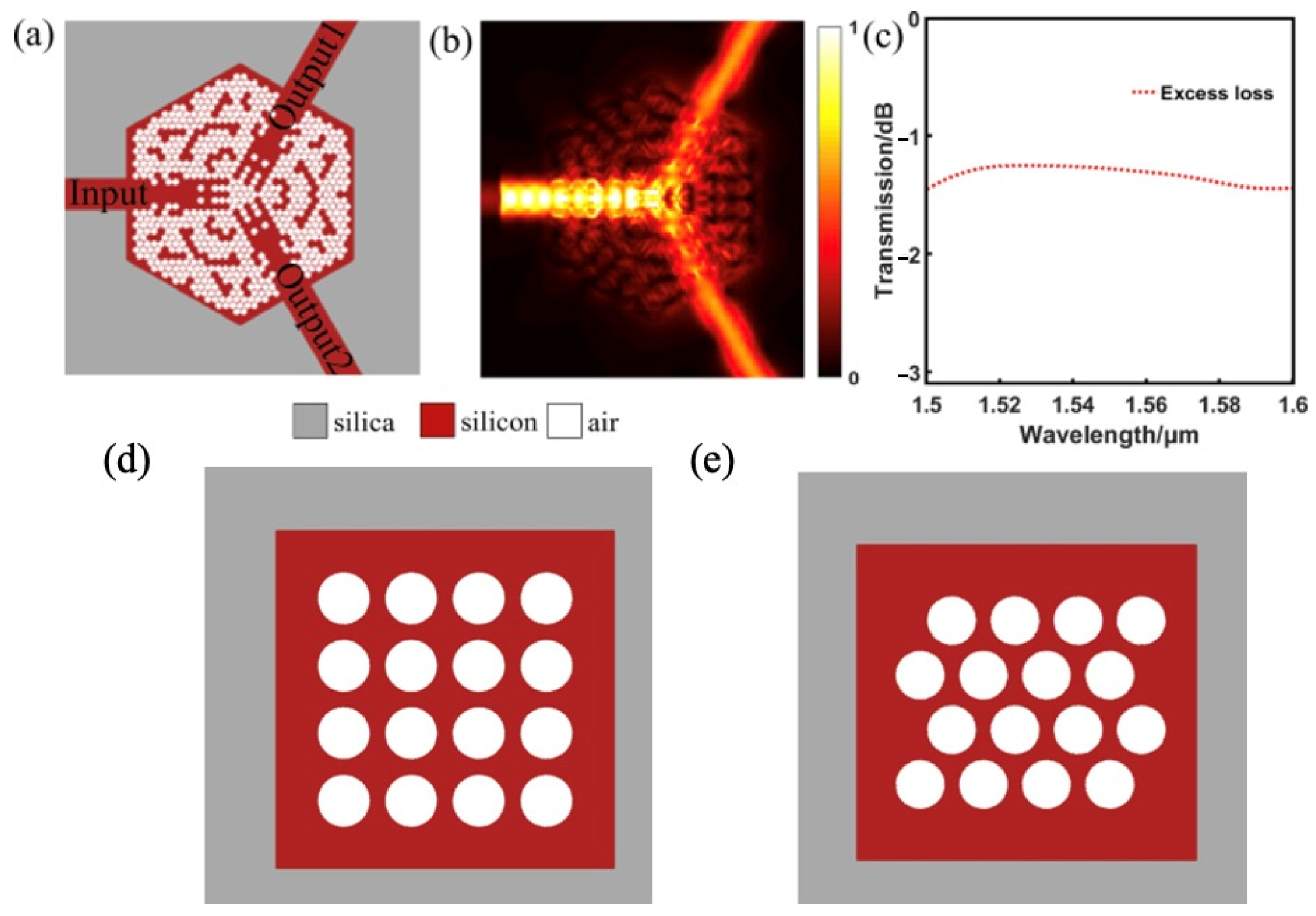

6.2.2. Inverse Design and Artificial Intelligence (AI)

6.2.3. New Frontiers: Quantum and Sensing

7. Conclusions

7.1. Synthesis of Key Advancements

7.2. Concluding Perspective on the Field’s Trajectory

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Udkar, S. Harnessing Photonic Computing for Next-Generation CPUs and GPUs in High-Performance Computing. Int. J. Emerg. Trends Comput. Sci. Inf. Technol. 2024, 5, 23–36. [Google Scholar] [CrossRef]

- Wang, Z.; Xiao, Y.; Liao, K.; Li, T.; Song, H.; Chen, H.; Uddin, S.M.Z.; Mao, D.; Wang, F.; Zhou, Z.; et al. Metasurface on integrated photonic platform: From mode converters to machine learning. Nanophotonics 2022, 11, 3531–3546. [Google Scholar] [CrossRef] [PubMed]

- Ning, S.; Zhu, H.; Feng, C.; Gu, J.; Jiang, Z.; Ying, Z.; Midkiff, J.; Jain, S.; Hlaing, M.H.; Pan, D.Z.; et al. Photonic-Electronic Integrated Circuits for High-Performance Computing and AI Accelerators. J. Light. Technol. 2024, 42, 7834–7859. [Google Scholar] [CrossRef]

- Resch, M.M.; Gebert, J.; Hoppe, D. The Future of HPC and AI. In Proceedings of the 2025 International Conference on Intelligent Control, Computing and Communications (IC3), Mathura, India, 13–14 February 2025; pp. 897–904. [Google Scholar] [CrossRef]

- Margalit, N.; Xiang, C.; Bowers, S.M.; Bjorlin, A.; Blum, R.; Bowers, J.E. Perspective on the future of silicon photonics and electronics. Appl. Phys. Lett. 2021, 118, 220501. [Google Scholar] [CrossRef]

- Rahim, A.; Hermans, A.; Wohlfeil, B.; Petousi, D.; Kuyken, B.; Van Thourhout, D.; Baets, R.G. Taking silicon photonics modulators to a higher performance level: State-of-the-art and a review of new technologies. Adv. Photonics 2021, 3, 024003. [Google Scholar] [CrossRef]

- Hirokawa, T.; Bian, Y.; Giewont, K.; Aboketaf, A.; Chandran, S.; Cho, J.-K.; Chowdhury, Z.; Lee, W.S.; Liu, Q.; Sharma, P.; et al. Latest progress and challenges in 300 mm monolithic silicon photonics manufacturing. In Proceedings of the Optical Fiber Communication Conference, San Diego, CA, USA, 24–28 March 2024; Optica Publishing Group: Washington, DC, USA, 2024; p. Th3H-2. [Google Scholar] [CrossRef]

- Shekhar, S.; Bogaerts, W.; Chrostowski, L.; Bowers, J.E.; Hochberg, M.; Soref, R.; Shastri, B.J. Roadmapping the next generation of silicon photonics. Nat. Commun. 2024, 15, 751. [Google Scholar] [CrossRef] [PubMed]

- Dhote, C.; Singh, A.; Kumar, S. Silicon Photonics Sensors for Biophotonic Applications—A Review. IEEE Sens. J. 2022, 22, 18228–18239. [Google Scholar] [CrossRef]

- Debnath, K.; Arimoto, H.; Husain, M.K.; Prasmusinto, A.; Al-Attili, A.; Petra, R.; Chong, H.M.H.; Reed, G.T.; Saito, S. Low-Loss Silicon Waveguides and Grating Couplers Fabricated Using Anisotropic Wet Etching Technique. Front. Mater. 2016, 3, 10. [Google Scholar] [CrossRef]

- Dong, P.; Qian, W.; Liao, S.; Liang, H.; Kung, C.-C.; Feng, N.-N.; Shafiiha, R.; Fong, J.; Feng, D.; Krishnamoorthy, A.V.; et al. Low loss shallow-ridge silicon waveguides. Opt. Express 2010, 18, 14474–14479. [Google Scholar] [CrossRef]

- Vlasov, Y.A.; McNab, S.J. Losses in single-mode silicon-on-insulator strip waveguides and bends. Opt. Express 2004, 12, 1622–1631. [Google Scholar] [CrossRef]

- Gould, M.; Pomerene, A.; Hill, C.; Ocheltree, S.; Zhang, Y.; Baehr-Jones, T.; Hochberg, M. Ultra-thin silicon-on-insulator strip waveguides and mode couplers. Appl. Phys. Lett. 2012, 101, 221106. [Google Scholar] [CrossRef]

- Wu, S.; Mu, X.; Cheng, L.; Mao, S.; Fu, H.Y. State-of-the-Art and Perspectives on Silicon Waveguide Crossings: A Review. Micromachines 2020, 11, 326. [Google Scholar] [CrossRef] [PubMed]

- Wei, J.; Zhu, C.; Yu, Y.; Wang, R.; Yu, S. Low-loss silicon waveguide and an ultrahigh-Q silicon microring resonator in the 2 µm wave band. Opt. Lett. 2024, 49, 3271–3274. [Google Scholar] [CrossRef]

- Tran, M.A.; Huang, D.; Komljenovic, T.; Peters, J.; Malik, A.; Bowers, J.E. Ultra-Low-Loss Silicon Waveguides for Heterogeneously Integrated Silicon/III-V Photonics. Appl. Sci. 2018, 8, 1139. [Google Scholar] [CrossRef]

- Thander, A.K. Numerical methods for modal analysis in optical rib waveguide structures: A review. J. Opt. 2024, 1–7. [Google Scholar] [CrossRef]

- Huang, H.; Liu, K.; Qi, B.; Sorger, V.J. Re-Analysis of Single-Mode Conditions for Silicon Rib Waveguides at 1550 nm Wavelength. J. Light. Technol. 2016, 34, 3811–3817. [Google Scholar] [CrossRef]

- Li, Z.; Fan, Z.; Zhou, J.; Cong, Q.; Zeng, X.; Zhang, Y.; Jia, L. Process Development of Low-Loss LPCVD Silicon Nitride Waveguides on 8-Inch Wafer. Appl. Sci. 2023, 13, 3660. [Google Scholar] [CrossRef]

- Li, D.; Li, B.; Tang, B.; Zhang, P.; Yang, Y.; Liu, R.; Xie, L.; Li, Z. Broadband Silicon Nitride Power Splitter Based on Bent Directional Couplers with Low Thermal Sensitivity. Micromachines 2022, 13, 559. [Google Scholar] [CrossRef] [PubMed]

- Chandran, S.; Bian, Y.; Lee, W.S.; Abumazwed, A.; Liu, N.; Xu, L.; Ding, H.; Aboketaf, A.; Rakowski, M.; Dezfulian, K.; et al. High performance silicon nitride passive optical components on monolithic silicon photonics platform. In Proceedings of the Optical Fiber Communication Conference, San Diego, CA, USA, 24–28 March 2024; Optica Publishing Group: Washington, DC, USA, 2024; p. Th3H-4. [Google Scholar] [CrossRef]

- Bauters, J.F.; Heck, M.J.R.; John, D.D.; Barton, J.S.; Bruinink, C.M.; Leinse, A.; Heideman, R.G.; Blumenthal, D.J.; Bowers, J.E. Planar waveguides with less than 0.1 dB/m propagation loss fabricated with wafer bonding. Opt. Express 2011, 19, 24090–24101. [Google Scholar] [CrossRef]

- Ji, X.; Wang, R.N.; Liu, Y.; Riemensberger, J.; Qiu, Z.; Kippenberg, T.J. Efficient mass manufacturing of high-density, ultra-low-loss Si3N4 photonic integrated circuits. Optica 2024, 11, 1397–1407. [Google Scholar] [CrossRef]

- Ji, X.; Okawachi, Y.; Gil-Molina, A.; Corato-Zanarella, M.; Roberts, S.; Gaeta, A.L.; Lipson, M. Ultra-Low-Loss Silicon Nitride Photonics Based on Deposited Films Compatible with Foundries. Laser Photonics Rev. 2023, 17, 2200544. [Google Scholar] [CrossRef]

- Fahrenkopf, N.M.; McDonough, C.; Leake, G.L.; Su, Z.; Timurdogan, E.; Coolbaugh, D.D. The AIM Photonics MPW: A Highly Accessible Cutting Edge Technology for Rapid Prototyping of Photonic Integrated Circuits. IEEE J. Sel. Top. Quantum Electron. 2019, 25, 8201406. [Google Scholar] [CrossRef]

- Carpenter, L.G.; van Niekerk, M.; Begović, A.; Sundaram, V.S.; Deenadayalan, V.; Palone, T.; Fanto, M.; Preble, S.; Baiocco, C.; Leake, G.L.; et al. Towards Low Propagation Losses in Active Photonic Multi-Project Wafer Runs. In Proceedings of the OSA Advanced Photonics Congress 2021, Washington, DC, USA, 26–29 July 2021; Optica Publishing Group: Washington, DC, USA, 2021; p. ITu3A.5. [Google Scholar] [CrossRef]

- Kim, E.; Carpenter, L.; Smith, A.M.; Tison, C.C.; Coleman, D.; Leake, G.; Fanto, M.; Rizzo, A.J.; García-Blanco, S.M.; Cheben, P. Ultra-low loss dispersion-engineered silicon nitride waveguides on 300 mm wafers. In Proceedings of the Integrated Optics: Devices, Materials, and Technologies XXIX, San Francisco, CA, USA, 27–30 January 2025; SPIE: Bellingham, DC, USA, 2025; pp. 271–277. [Google Scholar] [CrossRef]

- Pfeiffer, M.H.P.; Herkommer, C.; Liu, J.; Morais, T.; Zervas, M.; Geiselmann, M.; Kippenberg, T.J. Photonic Damascene Process for Low-Loss, High-Confinement Silicon Nitride Waveguides. IEEE J. Sel. Top. Quantum Electron. 2018, 24, 6101411. [Google Scholar] [CrossRef]

- Liu, J.; Huang, G.; Wang, R.N.; He, J.; Raja, A.S.; Liu, T.; Engelsen, N.J.; Kippenberg, T.J. High-yield, wafer-scale fabrication of ultralow-loss, dispersion-engineered silicon nitride photonic circuits. Nat. Commun. 2021, 12, 2236. [Google Scholar] [CrossRef]

- Luque-González, J.M.; Sánchez-Postigo, A.; Hadij-ElHouati, A.; Ortega-Moñux, A.; Wangüemert-Pérez, J.G.; Schmid, J.H.; Cheben, P.; Molina-Fernández, Í.; Halir, R. A review of silicon subwavelength gratings: Building break-through devices with anisotropic metamaterials. Nanophotonics 2021, 10, 2765–2797. [Google Scholar] [CrossRef]

- Bock, P.J.; Cheben, P.; Schmid, J.H.; Lapointe, J.; Delâge, A.; Xu, D.-X.; Janz, S.; Densmore, A.; Hall, T.J. Subwavelength grating crossings for silicon wire waveguides. Opt. Express 2010, 18, 16146–16155. [Google Scholar] [CrossRef]

- Molina-Fernández, I.; Wangüemert-Perez, J.G.; Ortega-Moñuz, A.; Halir, R.; Rubio, J.d.O.; Sánchez-Postigo, A.; Luque-González, J.M.; Hadij-Elhouati, A.; Pereira-Martín, D.; Gonzalez-Andrade, D.; et al. Silicon subwavelength waveguiding devices. In Proceedings of the High Contrast Metastructures IX, San Francisco, CA, USA, 26 February 2020; SPIE: Bellingham, DC, USA, 2020; pp. 114–120. [Google Scholar] [CrossRef]

- Kazanskiy, N.L.; Butt, M.A.; Khonina, S.N. Silicon photonic devices realized on refractive index engineered subwavelength grating waveguides—A review. Opt. Laser Technol. 2021, 138, 106863. [Google Scholar] [CrossRef]

- Shi, Y.; Shao, B.; Zhang, Z.; Zhou, T.; Luo, F.; Xu, Y. Ultra-Broadband and Low-Loss Silicon-Based Power Splitter Based on Subwavelength Grating-Assisted Multimode Interference Structure. Photonics 2022, 9, 435. [Google Scholar] [CrossRef]

- Zhu, D.; Ye, H.; Liu, Y.; Li, J.; Wang, Y.; Yu, Z. Silicon subwavelength grating-assisted asymmetric directional coupler around 2 μm and its applications. Opt. Laser Technol. 2021, 136, 106789. [Google Scholar] [CrossRef]

- Chen, J.; Xiao, J. Ultracompact silicon-based polarization splitter and rotator based on asymmetric directional couplers with subwavelength gratings. JOSA B 2022, 39, 345–354. [Google Scholar] [CrossRef]

- Halir, R.; Bock, P.J.; Cheben, P.; Ortega-Moñux, A.; Alonso-Ramos, C.; Schmid, J.H.; Lapointe, J.; Xu, D.; Wangüemert-Pérez, J.G.; Molina-Fernández, Í.; et al. Waveguide sub-wavelength structures: A review of principles and applications. Laser Photonics Rev. 2015, 9, 25–49. [Google Scholar] [CrossRef]

- Sultan, A.; Khalil, M.; Mehravar, L.; Xu, C. Highly Efficient Polarization-Insensitive Grating Couplers on Thin-Film Lithium Niobate with an Integrated Gold Layer. Photonics 2025, 12, 111. [Google Scholar] [CrossRef]

- Cheng, L.; Mao, S.; Li, Z.; Han, Y.; Fu, H.Y. Grating Couplers on Silicon Photonics: Design Principles, Emerging Trends and Practical Issues. Micromachines 2020, 11, 666. [Google Scholar] [CrossRef]

- Tahara, N.; Nawa, S.; Taira, R.; Suyama, S.; Hirotani, K.; Kamata, M.; Maegami, Y.; Tsuchizawa, T.; Yamamoto, N.; Yamada, K.; et al. High efficiency silicon photonics grating coupler compatible to standard foundry service. In Proceedings of the Silicon Photonics XX, San Francisco, CA, USA, 28–30 January 2025; SPIE: Bellingham, DC, USA, 2025; pp. 57–65. [Google Scholar] [CrossRef]

- Cheng, H.; Wu, J.; Wang, Y.; Ran, C.; Li, H.; Wang, Y.; Li, Y.; Zhang, S.; Wang, C.; Yang, J. Ultra-Compact, High-Efficiency Vertical Meta-Grating Couplers for Meta-Photonic Integrated Circuits. Nanomaterials 2025, 15, 583. [Google Scholar] [CrossRef]

- Zhou, W.; Lu, K.; Kang, S.; Wu, X.; Tong, Y. Efficient Polarization-Diversity Grating Coupler With Multipolar Radiation Mode Enhancement. IEEE Photonics J. 2025, 17, 7100206. [Google Scholar] [CrossRef]

- Korček, R.; Fraser, W.; Wilmart, Q.; Quiroz, D.M.; Litvik, J.; Zubor, L.; Krehel, T.; Edmond, S.; Milanizadeh, M.; Schmid, J.H.; et al. High-efficiency off-chip grating couplers for silicon nitride photonics. In Proceedings of the Integrated Optics: Devices, Materials, and Technologies XXVIII, San Francisco, CA, USA, 29 January–1 February 2024; SPIE: Bellingham, DC, USA, 2024; pp. 41–45. [Google Scholar] [CrossRef]

- Wan, Y.; Zhang, Y.; Wang, J. O-band low loss and polarization insensitivity bilayer and double-tip edge coupler. Adv. Photonics Nexus 2025, 4, 026004. [Google Scholar] [CrossRef]

- Ai, X.; Xuan, M.W.; Zhang, Y.; Hsu, W.-L.; Veilleux, S.; Dagenais, M. Broadband high coupling efficiency edge coupler with low polarization-dependence on the silicon-nitride platform. Opt. Express 2025, 33, 16253–16262. [Google Scholar] [CrossRef] [PubMed]

- Liu, M.; Zhang, T.; Xu, B.; Zhang, Y.; Du, J.; Sun, J.; Wang, J. High-efficiency bident edge coupler based on thin film lithium niobate. Opt. Express 2025, 33, 16338–16349. [Google Scholar] [CrossRef]

- Zhang, T.; Li, J.; Li, M.; Liu, J. Design and Optimization of a High-Efficiency 3D Multi-Tip Edge Coupler Based Lithium Niobate on Insulator Platform. Photonics 2024, 11, 134. [Google Scholar] [CrossRef]

- Chen, B.; Ruan, Z.; Wang, M.; Gong, S.; Liu, L. High-performance and fabrication-tolerant edge coupler on thin film lithium niobate based on a three-dimensional inverse taper. APL Photonics 2024, 9, 116111. [Google Scholar] [CrossRef]

- Bian, Y.; Hirokawa, T.; Karra, V.; Dasgupta, A.; Lee, W.S.; Aboketaf, A.; Afzal, F.; Sporer, R.; Nummy, K.; Giewont, K.; et al. Monolithically integrated self-aligned SiN edge coupler with <0.6/0.8 dB TE/TM insertion loss, <−39 dB back reflection and >520 mW high-power handling capability. In Proceedings of the Optical Fiber Communication Conference (OFC) 2023, San Diego, CA, USA, 5–9 March 2023; Optica Publishing Group: Washington, DC, USA, 2023; p. M3C.3. [Google Scholar] [CrossRef]

- Marchetti, R.; Lacava, C.; Carroll, L.; Gradkowski, K.; Minzioni, P. Coupling strategies for silicon photonics integrated chips [Invited]. Photonics Res. 2019, 7, 201–239. [Google Scholar] [CrossRef]

- Xu, Y.; Tian, Z.; Meng, X.; Chai, Z. Methods and applications of on-chip beam splitting: A review. Front. Phys. 2022, 10, 985208. [Google Scholar] [CrossRef]

- Han, L.; Kuo, B.P.-P.; Alic, N.; Radic, S. Ultra-broadband multimode 3dB optical power splitter using an adiabatic coupler and a Y-branch. Opt. Express 2018, 26, 14800–14809. [Google Scholar] [CrossRef]

- Krutov, I.A.; Saygin, M.Y.; Dyakonov, I.V.; Kulik, S.P. Optimized low-loss integrated photonics silicon-nitride Y-branch splitter. AIP Conf. Proc. 2020, 2241, 020027. [Google Scholar] [CrossRef]

- Lv, D.; Wu, L.; Liu, C.; Li, A.; Wang, R.; Wu, A. Broadband and Low-Loss Silicon Photonic Directional Coupler for Signal Power Tapping on the 3 μm SOI Waveguide Platform. Photonics 2023, 10, 776. [Google Scholar] [CrossRef]

- Frishman, A.; Malka, D. An Optical 1×4 Power Splitter Based on Silicon–Nitride MMI Using Strip Waveguide Structures. Nanomaterials 2023, 13, 2077. [Google Scholar] [CrossRef] [PubMed]

- Taha, A.M.; Chandran, S.; Viegas, J.; Bian, Y.; Rakowski, M.; Augur, R.; Jacob, A.; Dahlem, M.S. Compact MMI-Based AWGs in a Scalable Monolithic Silicon Photonics Platform. IEEE Photonics J. 2021, 13, 6600306. [Google Scholar] [CrossRef]

- Xu, L.; Chandran, S.; Bian, Y.; Liu, N.; Abumazwed, A.; Lee, W.S.; Zhang, J.; Deptuck, D.; Rakowski, M.; Krishnamoorthy, S.; et al. Low-loss SiN 2 × 2 MMI 50/50 Couplers for Monolithically Integrated Silicon Photonics. In Proceedings of the CLEO 2023, San Jose, CA, USA, 7–12 May 2023; Optica Publishing Group: Washington, DC, USA, 2023; p. JW2A.86. [Google Scholar] [CrossRef]

- Vilas, J.; de Cabo, R.F.; Olivares, I.; González-Andrade, D.; Velasco, A.V.; Dias-Ponte, A. Low-Loss Directional Coupler for the C, L and U Bands Based on Subwavelength Gratings. IEEE Photonics Technol. Lett. 2023, 35, 1331–1334. [Google Scholar] [CrossRef]

- Yao, Z.; Wu, K.; Tan, B.X.; Wang, J.; Li, Y.; Zhang, Y.; Poon, A.W. Integrated Silicon Photonic Microresonators: Emerging Technologies. IEEE J. Sel. Top. Quantum Electron. 2018, 24, 5900324. [Google Scholar] [CrossRef]

- Bogaerts, W.; De Heyn, P.P.; Van Vaerenbergh, T.T.; De Vos, K.K.; Selvaraja, S.K.; Claes, T.T.; Dumon, P.; Bienstman, P.; Van Thourhout, D.D.; Baets, R.R. Silicon microring resonators. Laser Photonics Rev. 2012, 6, 47–73. [Google Scholar] [CrossRef]

- Van, V. Optical Microring Resonators: Theory, Techniques, and Applications; CRC Press: Boca Raton, FL, USA, 2016. [Google Scholar] [CrossRef]

- Nijem, J.; Naiman, A.; Zektzer, R.; Frydendahl, C.; Mazurski, N.; Levy, U. High-Q and high finesse silicon microring resonator. Opt. Express 2024, 32, 7896–7906. [Google Scholar] [CrossRef] [PubMed]

- Xuan, Y.; Liu, Y.; Varghese, L.T.; Metcalf, A.J.; Xue, X.; Wang, P.-H.; Han, K.; Jaramillo-Villegas, J.A.; Al Noman, A.; Wang, C.; et al. High-Q silicon nitride microresonators exhibiting low-power frequency comb initiation. Optica 2016, 3, 1171–1180. [Google Scholar] [CrossRef]

- Cui, S.; Cao, K.; Yu, Y.; Zhang, X. Ultra-high-Q racetrack microring based on silicon-nitride. arXiv 2022, arXiv:2209.01097. [Google Scholar] [CrossRef]

- Puckett, M.W.; Liu, K.; Chauhan, N.; Zhao, Q.; Jin, N.; Cheng, H.; Wu, J.; Behunin, R.O.; Rakich, P.T.; Nelson, K.D.; et al. 422 Million intrinsic quality factor planar integrated all-waveguide resonator with sub-MHz linewidth. Nat. Commun. 2021, 12, 934. [Google Scholar] [CrossRef]

- Perestjuk, M.; Armand, R.; Campos, M.G.S.; Ferhat, L.; Reboud, V.; Bresson, N.; Hartmann, J.-M.; Mathieu, V.; Ren, G.; Boes, A.; et al. One million quality factor integrated ring resonators in the mid-infrared. Nanophotonics 2025, 14, 1009–1015. [Google Scholar] [CrossRef]

- Liu, X.; Ruan, Z.; Sun, S.; Guo, C.; Chen, K.; Zhu, N.; Liu, L. Sharp bend and large FSR ring resonator based on the free-form curves on a thin-film lithium niobate platform. Opt. Express 2024, 32, 9433–9441. [Google Scholar] [CrossRef]

- Ouyang, B.; Xing, Y.; Bogaerts, W.; Caro, J. Silicon ring resonators with a free spectral range robust to fabrication variations. Opt. Express 2019, 27, 38698–38707. [Google Scholar] [CrossRef]

- Marques, A.; Cabrita, P.; Carvalhais, M.; Novo, C.; Lima, M.; Rodrigues, F.; Teixeira, A. Simulation and Experimental Validation of a Silicon Photonics Ring Assisted Mach-Zehnder Interferometer Filter. In Proceedings of the 13th International Conference on Photonics, Optics and Laser Technology, Porto, Portugal, 22–24 February 2025; pp. 147–151. [Google Scholar] [CrossRef]

- Chen, H.-Z.; Ho, K.-L.; Wang, P.-H. High-Extinction Photonic Filters by Cascaded Mach–Zehnder Interferometer-Coupled Resonators. Photonics 2024, 11, 1055. [Google Scholar] [CrossRef]

- Hiraki, T.; Fukuda, H.; Yamada, K.; Yamamoto, T. Small Sensitivity to Temperature Variations of Si-Photonic Mach–Zehnder Interferometer Using Si and SiN Waveguides. Front. Mater. 2015, 2, 26. [Google Scholar] [CrossRef]

- Yuan, S.; Feng, J.; Yu, Z.; Chen, J.; Liu, H.; Chen, Y.; Guo, S.; Huang, F.; Akimoto, R.; Zeng, H. Silicon Nanowire-Assisted High Uniform Arrayed Waveguide Grating. Nanomaterials 2023, 13, 182. [Google Scholar] [CrossRef]

- Stanton, E.J.; Spott, A.; Davenport, M.L.; Volet, N.; Bowers, J.E. Low-loss arrayed waveguide grating at 760 nm. Opt. Lett. 2016, 41, 1785–1788. [Google Scholar] [CrossRef]

- Stanton, E.J.; Volet, N.; Bowers, J.E. Low-loss arrayed waveguide grating at 2.0 µm. In Proceedings of the Conference on Lasers and Electro-Optics (2017), San Jose, CA, USA, 14–19 May 2017; Optica Publishing Group: Washington, DC, USA, 2017; p. STh1M.7. [Google Scholar] [CrossRef]

- Liu, Y.; Wang, X.; Yao, Y.; Du, J.; Song, Q.; Xu, K. Silicon photonic arrayed waveguide grating with 64 channels for the 2 µm spectral range. Opt. Lett. 2022, 47, 1186–1189. [Google Scholar] [CrossRef] [PubMed]

- Siew, S.Y.; Li, B.; Gao, F.; Zheng, H.Y.; Zhang, W.; Guo, P.; Xie, S.W.; Song, A.; Dong, B.; Luo, L.W.; et al. Review of Silicon Photonics Technology and Platform Development. J. Light. Technol. 2021, 39, 4374–4389. [Google Scholar] [CrossRef]

- Lim, A.E.-J.; Song, J.; Fang, Q.; Li, C.; Tu, X.; Duan, N.; Chen, K.K.; Tern, R.P.-C.; Liow, T.-Y. Review of silicon photonics foundry efforts. IEEE J. Sel. Top. Quantum Electron. 2013, 20, 405–416. [Google Scholar] [CrossRef]

- Absil, P.P.; De Heyn, P.; Chen, H.; Verheyen, P.; Lepage, G.; Pantouvaki, M.; De Coster, J.; Khanna, A.; Drissi, Y.; Van Thourhout, D.; et al. Imec iSiPP25G silicon photonics: A robust CMOS-based photonics technology platform. In Proceedings of the Silicon Photonics X, San Francisco, CA, USA, 7–12 February 2015; SPIE: Bellingham, DC, USA, 2015; pp. 166–171. [Google Scholar] [CrossRef]

- Ferraro, F.J.; De Heyn, P.; Kim, M.; Rajasekaran, N.; Berciano, M.; Muliuk, G.; Bode, D.; Lepage, G.; Janssen, S.; Magdziak, R.; et al. Imec silicon photonics platforms: Performance overview and roadmap. In Proceedings of the Next-Generation Optical Communication: Components, Sub-Systems, and Systems XII, San Francisco, CA, USA, 31 January–2 February 2023; SPIE: Bellingham, DC, USA, 2023; pp. 22–28. [Google Scholar] [CrossRef]

- Quack, N.; Takabayashi, A.Y.; Sattari, H.; Edinger, P.; Jo, G.; Bleiker, S.J.; Errando-Herranz, C.; Gylfason, K.B.; Niklaus, F.; Khan, U.; et al. Integrated silicon photonic MEMS. Microsyst. Nanoeng. 2023, 9, 27. [Google Scholar] [CrossRef]

- Roelkens, G.; Zhang, J.; Bogaert, L.; Billet, M.; Wang, D.; Pan, B.; Kruckel, C.J.; Soltanian, E.; Maes, D.; Vanackere, T.; et al. Micro-Transfer Printing for Heterogeneous Si Photonic Integrated Circuits. IEEE J. Sel. Top. Quantum Electron. 2023, 29, 8200414. [Google Scholar] [CrossRef]

- Sahrling, M.; Li, S.; Lee, F.; Rusu, S. TSMC in the Silicon Photonics Era—An electrical perspective. In Proceedings of the Optical Fiber Communication Conference (OFC) 2025, San Francisco, CA, USA, 30 March–3 April 2025; Optica Publishing Group: Washington, DC, USA, 2025; p. Tu3G.1. [Google Scholar] [CrossRef]

- Hsia, H.; Tsai, C.; Ting, K.; Kuo, F.; Lin, C.; Wang, C.; Hou, S.; Chiou, W.; Yu, D.C. Heterogeneous Integration of a Compact Universal Photonic Engine for Silicon Photonics Applications in HPC. In Proceedings of the 2021 IEEE 71st Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 1 June–4 July 2021; pp. 263–268. [Google Scholar] [CrossRef]

- Lu, H.-Y.; Tang, C.-T.; Chen, C.-H.; Tan, B.-X.; Liu, W.-K.; Chiang, H.-Y.; Tsai, S.-Y.; Hsieh, T.-L.; Mao, W.-J.; Lo, W.-T.; et al. Low-loss High-uniformity Silicon Nitride Optical Building Blocks Integrated on Silicon Photonics Platform. In Proceedings of the 2025 Optical Fiber Communications Conference and Exhibition (OFC), San Francisco, CA, USA, 30 March–3 April 2025; pp. 1–3. [Google Scholar] [CrossRef]

- Giewont, K.; Hu, S.; Peng, B.; Rakowski, M.; Rauch, S.; Rosenberg, J.C.; Sahin, A.; Stobert, I.; Stricker, A.; Nummy, K.; et al. 300-mm Monolithic Silicon Photonics Foundry Technology. IEEE J. Sel. Top. Quantum Electron. 2019, 25, 8200611. [Google Scholar] [CrossRef]

- Bian, Y.; Hirokawa, T.; Lee, W.S.; Chandran, S.; Giewont, K.; Aboketaf, A.; Liu, Q.; Sporer, R.; Rakowski, M.; Dezfulian, K.; et al. 300-mm monolithic CMOS silicon photonics foundry technology. In Proceedings of the CLEO: Applications and Technology 2024, Charlotte, NC, USA, 5–10 May 2024; p. ATu3H-1. [Google Scholar]

- Littlejohns, C.G.; Rowe, D.J.; Du, H.; Li, K.; Zhang, W.; Cao, W.; Bucio, T.D.; Yan, X.; Banakar, M.; Tran, D.; et al. CORNERSTONE’s Silicon Photonics Rapid Prototyping Platforms: Current Status and Future Outlook. Appl. Sci. 2020, 10, 8201. [Google Scholar] [CrossRef]

- Tossoun, B.; Xiao, X.; Cheung, S.; Yuan, Y.; Peng, Y.; Srinivasan, S.; Giamougiannis, G.; Huang, Z.; Singaraju, P.; London, Y.; et al. Large-Scale Integrated Photonic Device Platform for Energy-Efficient AI/ML Accelerators. IEEE J. Sel. Top. Quantum Electron. 2025, 31, 8200326. [Google Scholar] [CrossRef]

- Liu, Q.; Aboketaf, A.; Pal, S.; Mosleh, S.; Banihashemian, S.F.; Pavadai, S.; Lee, J.-C.; Bian, Y.; Gong, M.; Orner, B.; et al. High-Power Micro-Ring Modulator and Multi-Channel Coupled Ring Resonator for WDM Design on a 300-mm Monolithic Foundry Platform. In Proceedings of the Optical Fiber Communication Conference (OFC) 2024, San Diego, CA, USA, 24–28 March 2024; Optica Publishing Group: Washington, DC, USA, 2024; p. M3A.2. [Google Scholar] [CrossRef]

- Bian, Y.; Aboketaf, A.; Lee, W.S.; Chandran, S.; Huante-Ceron, E.; Najafi, A.; Villafranca, A.; Shiran, H.; Holt, J.; Afzal, F.; et al. Monolithically integrated high-performance Ge-on-Si PIN photodetectors with nearly 60 GHz EO bandwidth, 0.95 A/W re-sponsivity, <30 nA dark current and −36 dB optical return loss enabled by Ge shape optimization. In Proceedings of the Optical Fiber Communication Conference (OFC) 2025, San Francisco, CA, USA, 30 March–3 April 2025; Optica Publishing Group: Washington, DC, USA, 2025; p. Th3E.6. [Google Scholar] [CrossRef]

- Bian, Y.; Ramachandran, K.; Wu, Z.-J.; Hedrick, B.; Dezfulian, K.K.; Houghton, T.; Nummy, K.; Fisher, D.; Hirokawa, T.; Donegan, K.; et al. 3D Integrated Laser Attach Technology on a 300-mm Monolithic CMOS Silicon Photonics Platform. IEEE J. Sel. Top. Quantum Electron. 2023, 29, 8200519. [Google Scholar] [CrossRef]

- Xiang, C.; Jin, W.; Huang, D.; Tran, M.A.; Guo, J.; Wan, Y.; Xie, W.; Kurczveil, G.; Netherton, A.M.; Liang, D.; et al. High-Performance Silicon Photonics Using Heterogeneous Integration. IEEE J. Sel. Top. Quantum Electron. 2022, 28, 8200515. [Google Scholar] [CrossRef]

- Xiang, C.; Liu, J.; Guo, J.; Chang, L.; Wang, R.N.; Weng, W.; Peters, J.; Xie, W.; Zhang, Z.; Riemensberger, J.; et al. Laser soliton microcombs heterogeneously integrated on silicon. Science 2021, 373, 99–103. [Google Scholar] [CrossRef]

- Liu, Y.; Qiu, Z.; Ji, X.; Bancora, A.; Lihachev, G.; Riemensberger, J.; Wang, R.N.; Voloshin, A.; Kippenberg, T.J. A fully hybrid integrated erbium-based laser. Nat. Photonics 2024, 18, 829–835. [Google Scholar] [CrossRef]

- Elshaari, A.W.; Pernice, W.; Srinivasan, K.; Benson, O.; Zwiller, V. Hybrid integrated quantum photonic circuits. Nat. Photonics 2020, 14, 285–298. [Google Scholar] [CrossRef]

- Dai, D.; Liu, L.; Gao, S.; Xu, D.-X.; He, S. Polarization management for silicon photonic integrated circuits. Laser Photonics Rev. 2013, 7, 303–328. [Google Scholar] [CrossRef]

- Bian, Y.; Lee, W.S.; Chandran, S.; Hirokawa, T.; Sorbara, M.; Aboketaf, A.; Dezfulian, K.K.; Najafi, A.; Mosleh, S.; Banihashemian, F.; et al. Minimizing polarization dependent loss for monolithic silicon photonic components and receiver circuits. In Proceedings of the CLEO: Applications and Technology 2024, Charlotte, NC, USA, 5–10 May 2024; Optica Publishing Group: Washington, DC, USA, 2024; p. AM2J-5. [Google Scholar] [CrossRef]

- Bian, Y.; Lee, W.S.; Chandran, S.; Hirokawa, T.; Sorbara, M.; Aboketaf, A.; Dezfulian, K.K.; Najafi, A.; Mosleh, S.; Banihashemian, F.; et al. Towards polarization insensitive photonic integrated circuits: Polarization dependent loss reduction of CMOSintegrated monolithic SiPh components. In Proceedings of the 2024 Optical Fiber Communications Conference and Exhibition (OFC), San Diego, CA, USA, 24–28 March 2024; IEEE: New York, NY, USA, 2024; pp. 1–3. Available online: https://ieeexplore.ieee.org/abstract/document/10526737/ (accessed on 9 August 2025).

- Bian, Y.; Ding, H.; Aboketaf, A.; Karra, V.; Sorbara, M.; Hirokawa, T.; Mosleh, S.; Hedges, C.; Lee, W.S.; Chandran, S.; et al. Polarization mode dispersion in CMOS-integrated monolithic SiPh components: Simulations and experiments. In Proceedings of the 2023 Optical Fiber Communications Conference and Exhibition (OFC), San Diego, CA, USA, 5–9 March 2023; pp. 1–3. [Google Scholar] [CrossRef]

- Villegas, J.E.; Tamalampudi, S.R.; Rasras, M. High-speed polarization control in integrated silicon photonics. Opt. Express 2025, 33, 18477–18491. [Google Scholar] [CrossRef]

- Shahwar, D.; Yoon, H.H.; Akkanen, S.-T.; Li, D.; Muntaha, S.T.; Cherchi, M.; Aalto, T.; Sun, Z. Polarization management in silicon photonics. npj Nanophotonics 2024, 1, 35. [Google Scholar] [CrossRef]

- Pruessner, M.W.; Tyndall, N.F.; Stievater, T.H. MEMS-tunable polarization management in photonic integrated circuits. Opt. Express 2023, 31, 31316–31328. [Google Scholar] [CrossRef]

- O’Brien, P.; Carrol, L.; Eason, C.; Lee, J.S. Packaging of Silicon Photonic Devices. In Silicon Photonics III: Systems and Applications; Pavesi, L., Lockwood, D.J., Eds.; Springer: Berlin/Heidelberg, Germany, 2016; pp. 217–236. [Google Scholar] [CrossRef]

- Carroll, L.; Lee, J.-S.; Scarcella, C.; Gradkowski, K.; Duperron, M.; Lu, H.; Zhao, Y.; Eason, C.; Morrissey, P.; Rensing, M.; et al. Photonic Packaging: Transforming Silicon Photonic Integrated Circuits into Photonic Devices. Appl. Sci. 2016, 6, 426. [Google Scholar] [CrossRef]

- Tan, M.; Xu, J.; Liu, S.; Feng, J.; Zhang, H.; Yao, C.; Chen, S.; Guo, H.; Han, G.; Wen, Z.; et al. Co-packaged optics (CPO): Status, challenges, and solutions. Front. Optoelectron. 2023, 16, 1. [Google Scholar] [CrossRef] [PubMed]

- Lee, B.G.; Nedovic, N.; Greer, T.H.; Gray, C.T. Beyond CPO: A Motivation and Approach for Bringing Optics Onto the Silicon Interposer. J. Light. Technol. 2023, 41, 1152–1162. [Google Scholar] [CrossRef]

- Shen, X.; Chen, B.; Zhu, Y.; Shi, W. Silicon photonic integrated circuits and its application in data center. In Proceedings of the Seventh Symposium on Novel Photoelectronic Detection Technology and Applications, Kunming, China, 5–7 November 2020; SPIE: Bellingham, DC, USA, 2021; pp. 2110–2123. [Google Scholar] [CrossRef]

- Pira, L.; Antony, A.; Prathap, N.; Peace, D.; Romero, J. Enhanced Photonic Chip Design via Interpretable Machine Learning Techniques. arXiv 2025, arXiv:2505.09266. [Google Scholar] [CrossRef]

- Mao, S.; Cheng, L.; Zhao, C.; Khan, F.N.; Li, Q.; Fu, H.Y. Inverse Design for Silicon Photonics: From Iterative Optimization Algorithms to Deep Neural Networks. Appl. Sci. 2021, 11, 3822. [Google Scholar] [CrossRef]

- Shen, R.; Hong, B.; Ren, X.; Yang, F.; Chu, W.; Cai, H.; Huang, W. Recent progress on inverse design for integrated photonic devices: Methodology and applications. J. Nanophotonics 2024, 18, 010901. [Google Scholar] [CrossRef]

- Ma, H.; Huang, J.; Zhang, K.; Yang, J. Inverse-designed arbitrary-input and ultra-compact 1 × N power splitters based on high symmetric structure. Sci. Rep. 2020, 10, 11757. [Google Scholar] [CrossRef]

- Yang, K.Y.; Shirpurkar, C.; White, A.D.; Zang, J.; Chang, L.; Ashtiani, F.; Guidry, M.A.; Lukin, D.M.; Pericherla, S.V.; Yang, J.; et al. Multi-dimensional data transmission using inverse-designed silicon photonics and microcombs. Nat. Commun. 2022, 13, 7862. [Google Scholar] [CrossRef] [PubMed]

- Rad, H.A.; Ainsworth, T.; Alexander, R.N.; Altieri, B.; Askarani, M.F.; Baby, R.; Banchi, L.; Baragiola, B.Q.; Bourassa, J.E.; Chadwick, R.S.; et al. Scaling and networking a modular photonic quantum computer. Nature 2025, 638, 912–919. [Google Scholar] [CrossRef] [PubMed]

- Alexander, K.; Bahgat, A.; Benyamini, A.; Black, D.; Bonneau, D.; Burgos, S.; Burridge, B.; Cable, H.; Campbell, G.; Catalano, G.; et al. A manufacturable platform for photonic quantum computing. Nature 2025, 641, 876–883. [Google Scholar] [CrossRef] [PubMed]

- Jain, S.; Hlaing, M.H.; Fan, K.-C.; Midkiff, J.; Ning, S.; Feng, C.; Hsiao, P.-Y.; Camp, P.T.; Chen, R.T. Incubating advances in integrated photonics with emerging sensing and computational capabilities. Appl. Phys. Rev. 2025, 12, 011337. [Google Scholar] [CrossRef]

- Sajan, S.C.; Singh, A.; Sharma, P.K.; Kumar, S. Silicon Photonics Biosensors for Cancer Cells Detection—A Review. IEEE Sens. J. 2023, 23, 3366–3377. [Google Scholar] [CrossRef]

- Qiao, Q.; Liu, X.; Ren, Z.; Dong, B.; Xia, J.; Sun, H.; Lee, C.; Zhou, G. MEMS-Enabled On-Chip Computational Mid-Infrared Spectrometer Using Silicon Photonics. ACS Photonics 2022, 9, 2367–2377. [Google Scholar] [CrossRef]

- Zhang, X.; Kwon, K.; Henriksson, J.; Luo, J.; Wu, M.C. A large-scale microelectromechanical-systems-based silicon photonics LiDAR. Nature 2022, 603, 253–258. [Google Scholar] [CrossRef] [PubMed]

| Ref | Loss (dB/cm) | Wavelength | Platform | Bend Loss (dB) | Core Thickness | Wafer Size (inch) | Polarization Handling |

|---|---|---|---|---|---|---|---|

| [24] | 0.06 | Cband | SIN | NA | 730 nm | 4 | TE |

| [21] | 0.34 | Oband | SIN | 0.018 for 50 μm | NA | NA | TE |

| [11] | 0.274 ± 0.008 | Cband | SOI | <10−4 for 100 μm | 250 nm | 6 | TE |

| [28] | 0.055 | Cband | SIN | NA | 870 nm | NA | TE/TM |

| [23] | 0.014 @1.55 μm | Cband | SIN | NA | 720 nm | 4 | TE |

| [12] | TE: 3.6 ± 0.1 @1.5 μm, TE: 6.8 ± 0.2 @1.3 μm, TM: 3.5 ± 0.1 @1.3 μm | 1.2–1.7 μm | SOI | 0.086 ± 0.005 for 1 μm, 0.013 ± 0.005 for 2 μm | 220 nm | 8 | TE/TM |

| [19] | 0.157 @1.55 μm, 0.06 @1.58 μm | 1.49–1.58 μm | SIN | 0.013 for 50 μm, 0.0095 for 80 μm | 400 nm | 8 | TE/TM |

| [13] | 2.01 ± 0.231 | Cband | SOI | 0.05 ± 0.005 for 30 μm | 50 nm | 6 | TE |

| [22] | 0.00045 | 1.58–1.61 μm | SIN | NA | 50 nm | NA | TE |

| [16] | 0.16 | C + L band | SOI | NA | 500 nm | NA | TE |

| Ref | Type | Coupling Eff. per Facet (dB) | Wavelength | Platform | Mode |

|---|---|---|---|---|---|

| [46] | Bident EC | 1.52 @1.55 μm | Cband | TFLN | TE/TM |

| [42] | 2D GC | 2.54 | 1510–1560 nm | SOI | TE |

| [45] | Double-tip EC | 0.12/0.9 for TE/TM | 1070–1830 nm | SIN | TE/TM |

| [47] | 3D multi-tip EC | 0.0682/0.0958 for TE/TM @1.55 μm | Cband | TFLN | TE/TM |

| [38] | GC | 0.97/1.05 for TE/TM | Cband | TFLN | TE/TM |

| [48] | 3D EC | 0.29/0.24 for TE/TM | 1490–1670 nm | TFLN | TE/TM |

| [41] | Vertical metal GC | 2.77/2.55 for TE/TM | Cband | SOI | TE/TM |

| [44] | Double-tip EC | 1.52/2 for TE/TM | Oband | SOI | TE/TM |

| [49] | EC | 0.6/0.8 for TE/TM | Oband | SIN | TE/TM |

| Ref | Type | Coupling Efficiency per Facet (dB) | Wavelength | Platform | Mode |

|---|---|---|---|---|---|

| [20] | DC | 0.25 | 1510–1590 nm | SIN | TE |

| [55] | 1 × 4 MMI | 0.13 | Oband | SIN | TE |

| [58] | DC | 0.24 | C + L + Uband | SOI | TE |

| [57] | 2 × 2 MMI | 0.07 @1.31 μm | Oband | SIN | TE |

| [54] | DC | 0.272 @1.55 μm | S + C + Lband | SOI | TE |

| [36] | DC | 0.42/0.28 for TE/TM | C + Lband | SOI | TE/TM |

| [53] | Y-BRANCH | 0.1 @808 nm | 760–860 nm | SIN | TE |

| [52] | Y-BRANCH | 0.06 @1.55 μm | 1400–1565 nm | SOI | TE/TM |

| [34] | 2 × 2 MMI | 0.08 @1.55 μm | Cband | SOI | TE |

| [35] | DC | 0.1 @2 μm | 1.95–2.02 μm | SOI | TE |

| Ref | Q | Loss (dB/cm) | FWHM | Radius | FSR | Wavelength | Platform | Mode |

|---|---|---|---|---|---|---|---|---|

| [65] | 422 M | 0.0006 | 906 kHz | 11.787 mm | 2.713 GHz | 1.55–1.65 μm | SIN | TE |

| [62] | 2 M | 0.3 | 1.8 pm | 50 μm | 2 nm | Cband | SOI | TE |

| [64] | 45.7 M | 0.018 | 0.1 pm (12.5 MHz) | * 100 μm–4 mm | 0.52 nm | Cband | SIN | TE/TM |

| [15] | 2 M | 0.25 | 1.76 pm | ** 39 μm | 0.6 nm | 2–2.4 μm | SOI | TE |

| [63] | 17 M | 0.021 | 0.28 pm (35 MHz) | 100 μm | 25 GHz | 1.52–1.6 μm | SIN | TE/TM |

| [66] | 1.01 M | 0.15 | 0.5–1.5 MHz | 250 μm | NA | 3.5–4.6 μm | SIGE | TE |

| [67] | 48 K | 8.5 | 0.07 nm (8.8 GHz) | 15 μm | 10.36 nm | 1.5–1.6 μm | LNOI | TE |

| Ref | # of Channels | Loss (dB) | Channel Spacing | Crosstalk | Wavelength | Platform | Mode |

|---|---|---|---|---|---|---|---|

| [72] | 8&16 | 8 CHs: 6.26, 16 CHs: 10.1 | 200 GHz | NA | Cband | SOI | TE |

| [56] | 4 | 0.66 | 100 GHz | 9.6 | Oband | SOI | TE |

| [74] | 8 | 0.5 | 1.85 nm | 30.2 | 1.88–2.02 μm | SOI | TE |

| [73] | 8 | 0.5 | 0.5 nm | 23 | centered@ 760 μm | SIN | TE |

| [75] | 64 | 5 | 0.7 nm | 10 | 1.967–2.012 μm | SOI | TE |

| Foundry | Platform Highlights | Key Materials | Process Node(s)/Wafer Size |

|---|---|---|---|

| AIM Photonics | US-based open-access R&D hub; Comprehensive MPW platform (Active, Passive, Low-Loss, Sensor, QFlex); “Bite-size” process customization. | Si, SiN (incl. thick film), Ge | 90 nm/45 nm base on 300 mm |

| IMEC | iSiPP platforms (iSiPP50G, iSiPP200); Advanced co-integration of SiN; Heterogeneous III-V/LNO integration via flip-chip/micro-transfer printing. | Si, poly-Si, SiN, Ge, III-V (InP), LNO | 130 nm base on 200 mm, 300 mm |

| TSMC | High-volume 65 nm SiPh process; COUPE™ advanced packaging for 3D stacking; Fully automated wafer-level testing (EWAT/OWAT). | Si, SiN (low-temp PECVD) | 65 nm on 300 mm |

| GlobalFoundries | GF Fotonix™ platform; Monolithic RF-CMOS integration; Turnkey solutions including advanced packaging; 200 G/λ capable. | Si, SiN, Ge | 90 nm, 45 nm on 200 mm/300 mm |

| Tower Semiconductor | PH18 “open” foundry platform on 200 mm; Complements SiGe BiCMOS processes; Strong PDK support from major EDA vendors. | Si, SiN, Ge | 180 nm base on 200 mm |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, Q.; Bian, Y.; Xiong, J. Progress in Passive Silicon Photonic Devices: A Review. Photonics 2025, 12, 928. https://doi.org/10.3390/photonics12090928

Liu Q, Bian Y, Xiong J. Progress in Passive Silicon Photonic Devices: A Review. Photonics. 2025; 12(9):928. https://doi.org/10.3390/photonics12090928

Chicago/Turabian StyleLiu, Qidi, Yusheng Bian, and Jiawei Xiong. 2025. "Progress in Passive Silicon Photonic Devices: A Review" Photonics 12, no. 9: 928. https://doi.org/10.3390/photonics12090928

APA StyleLiu, Q., Bian, Y., & Xiong, J. (2025). Progress in Passive Silicon Photonic Devices: A Review. Photonics, 12(9), 928. https://doi.org/10.3390/photonics12090928