Robust Offset-Cancellation Sense Amplifier for an Offset-Canceling Dual-Stage Sensing Circuit in Resistive Nonvolatile Memories

Abstract

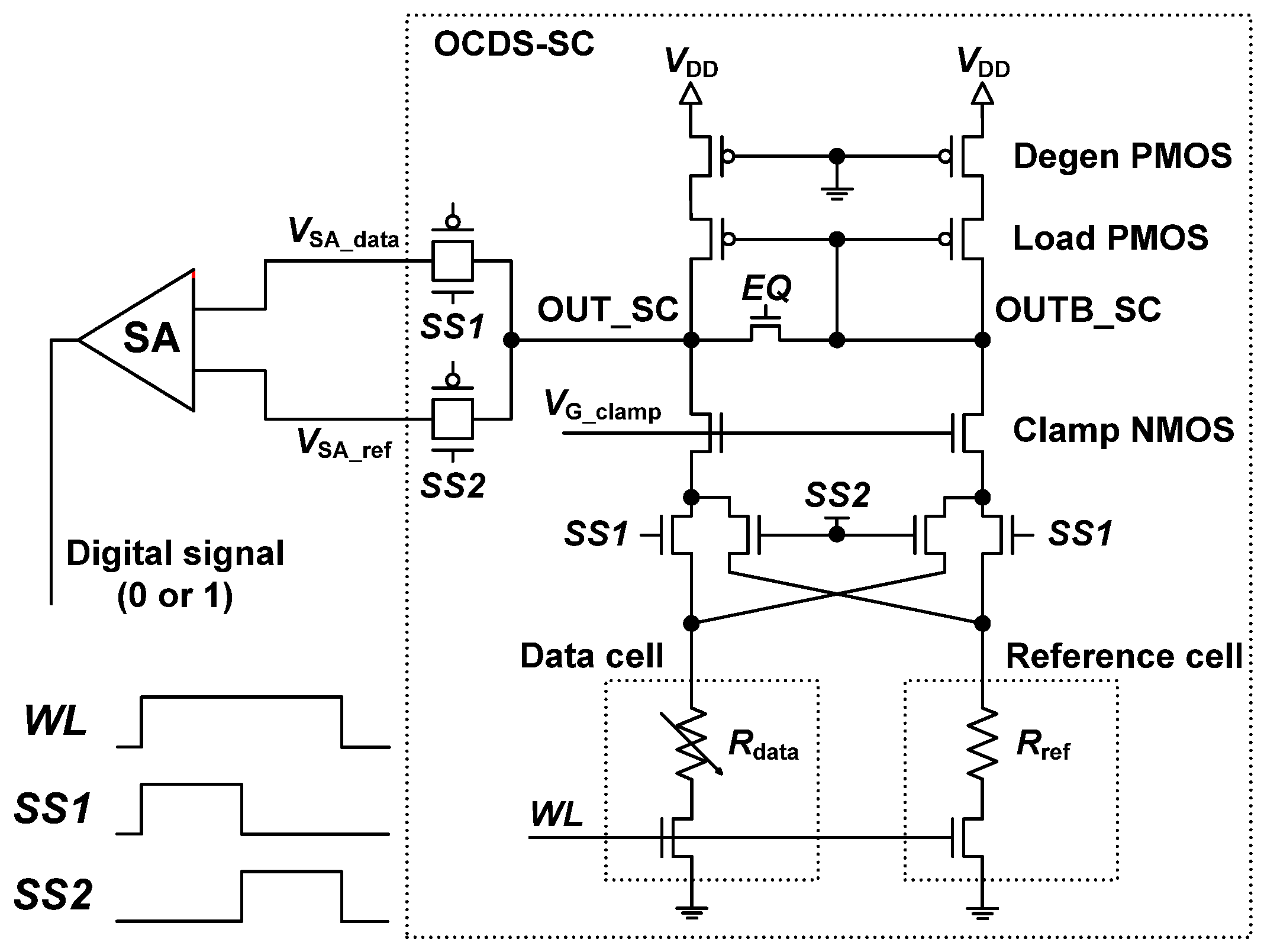

:1. Introduction

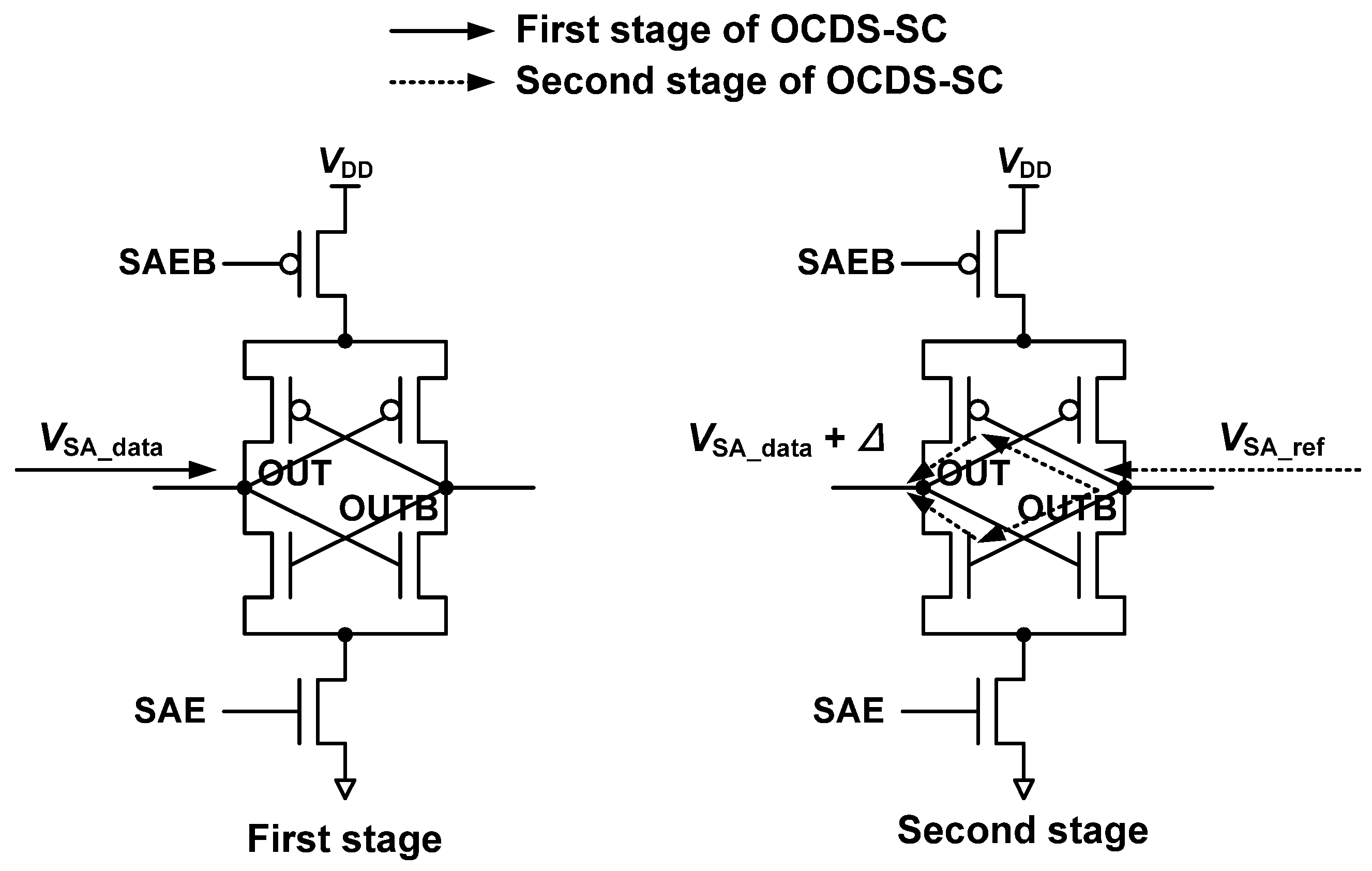

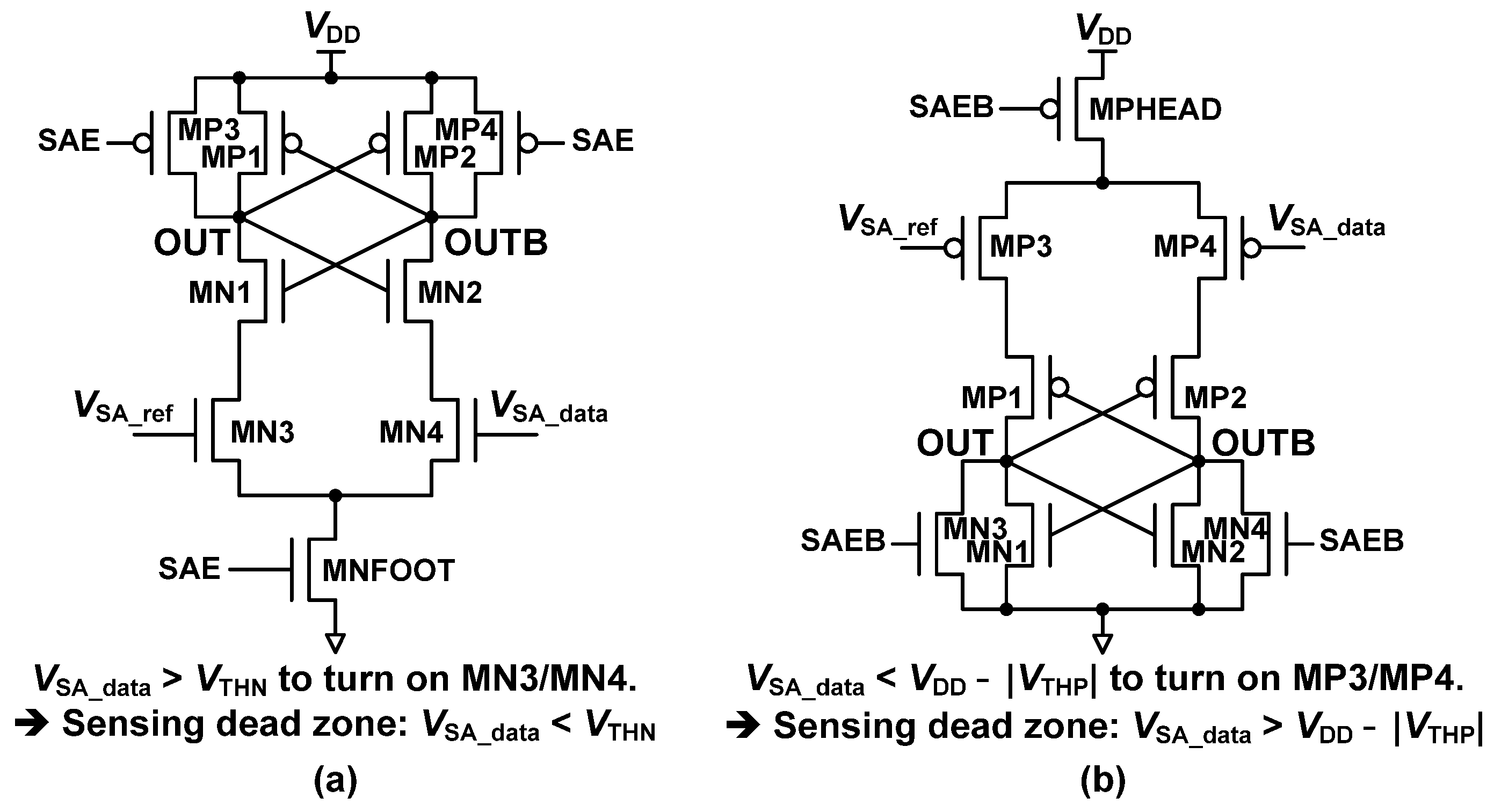

2. Problems in Conventional Latch-Type SAs

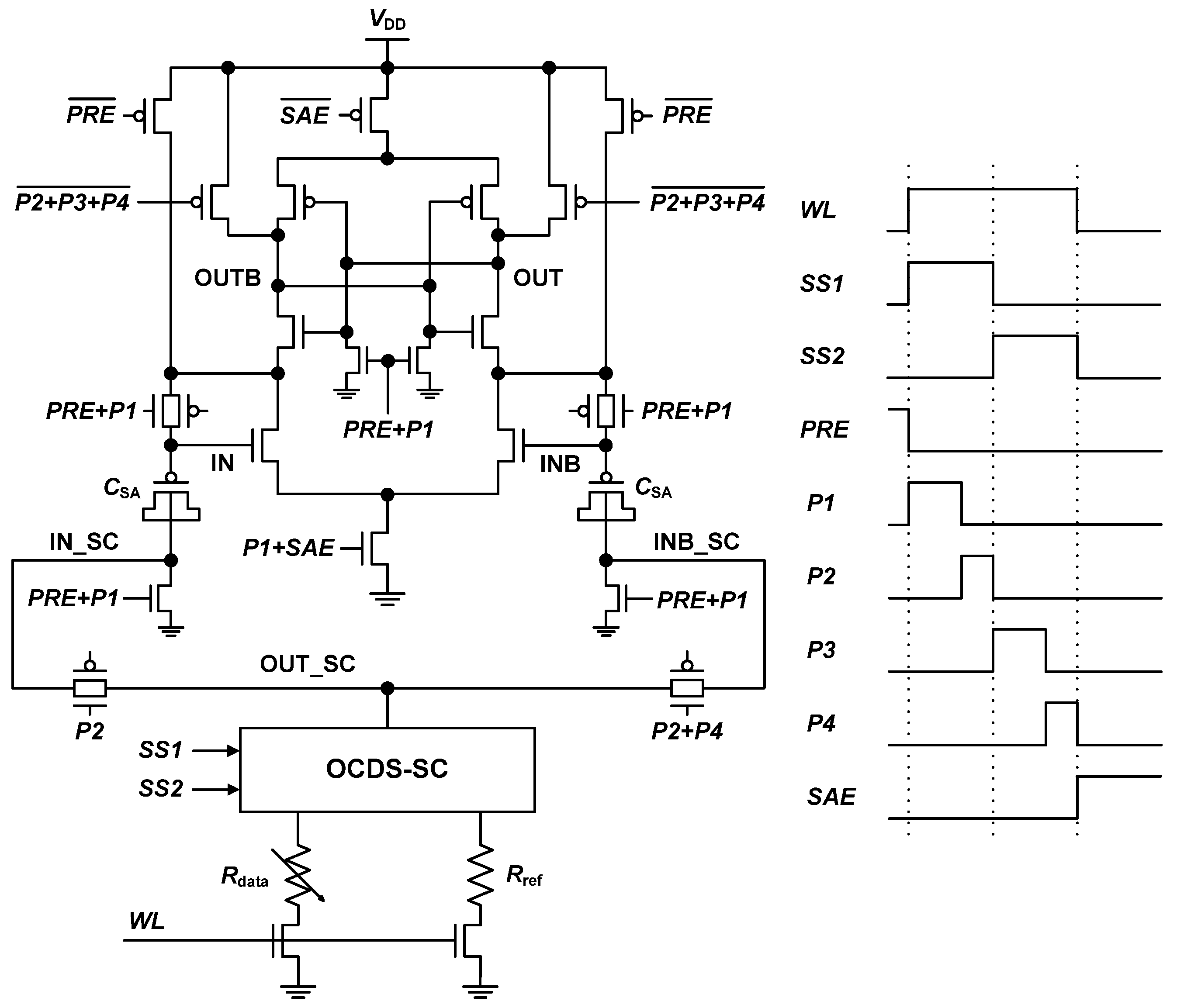

3. Proposed OCZS-SA

3.1. Circuit Diagram and Operation

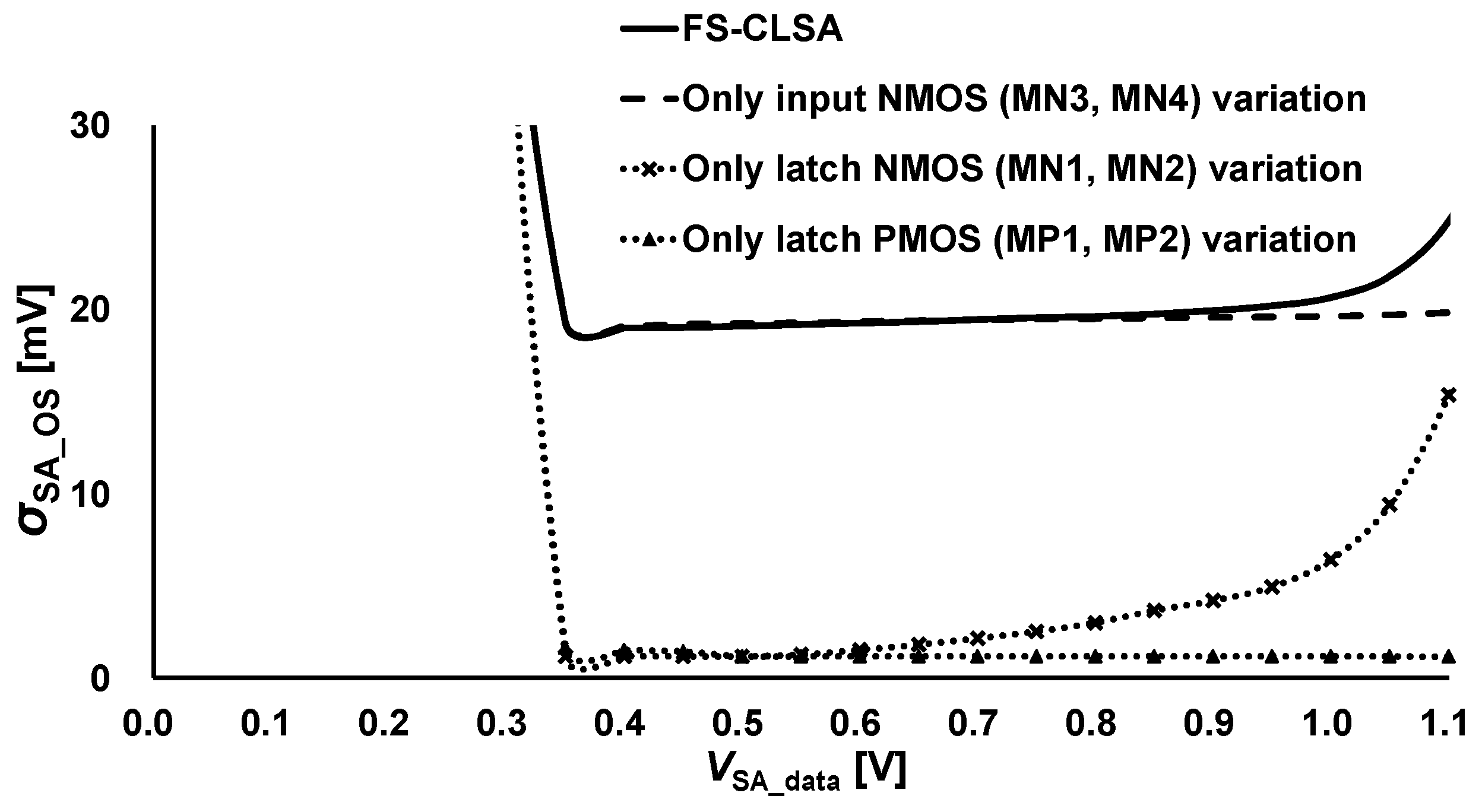

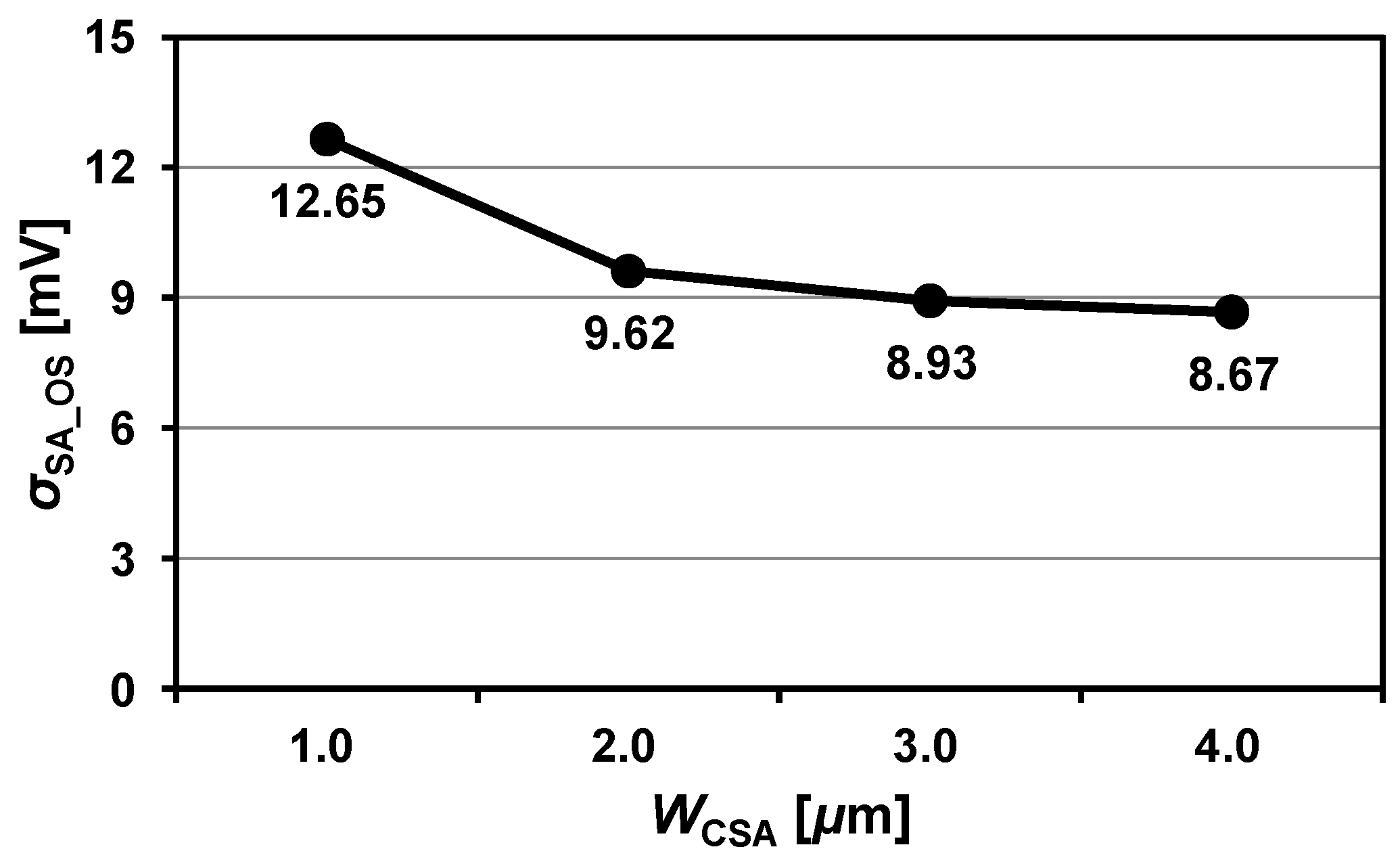

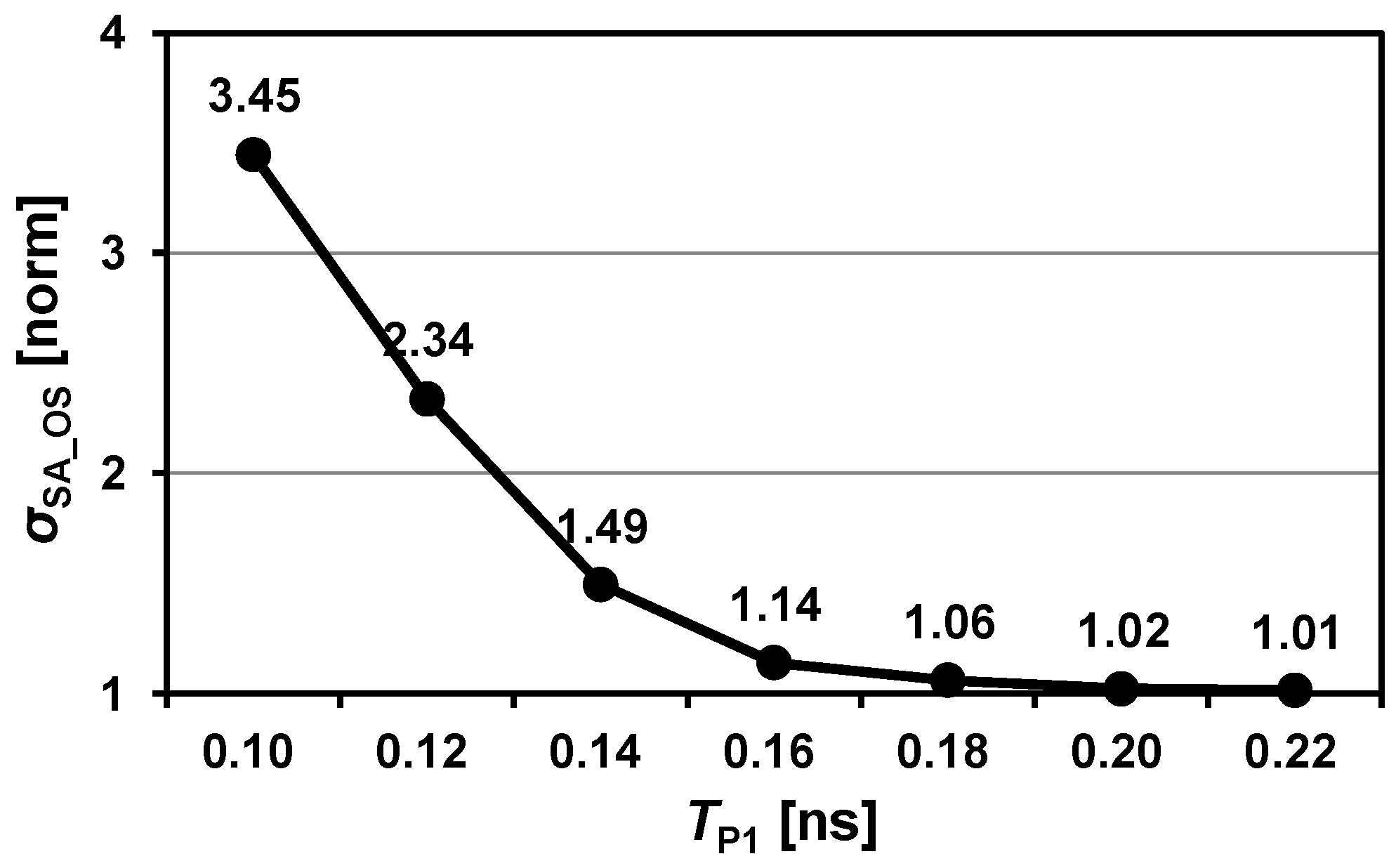

3.2. First Advantage: Offset Voltage Cancellation

3.3. Second Advantage: Zero Sensing Dead Zone

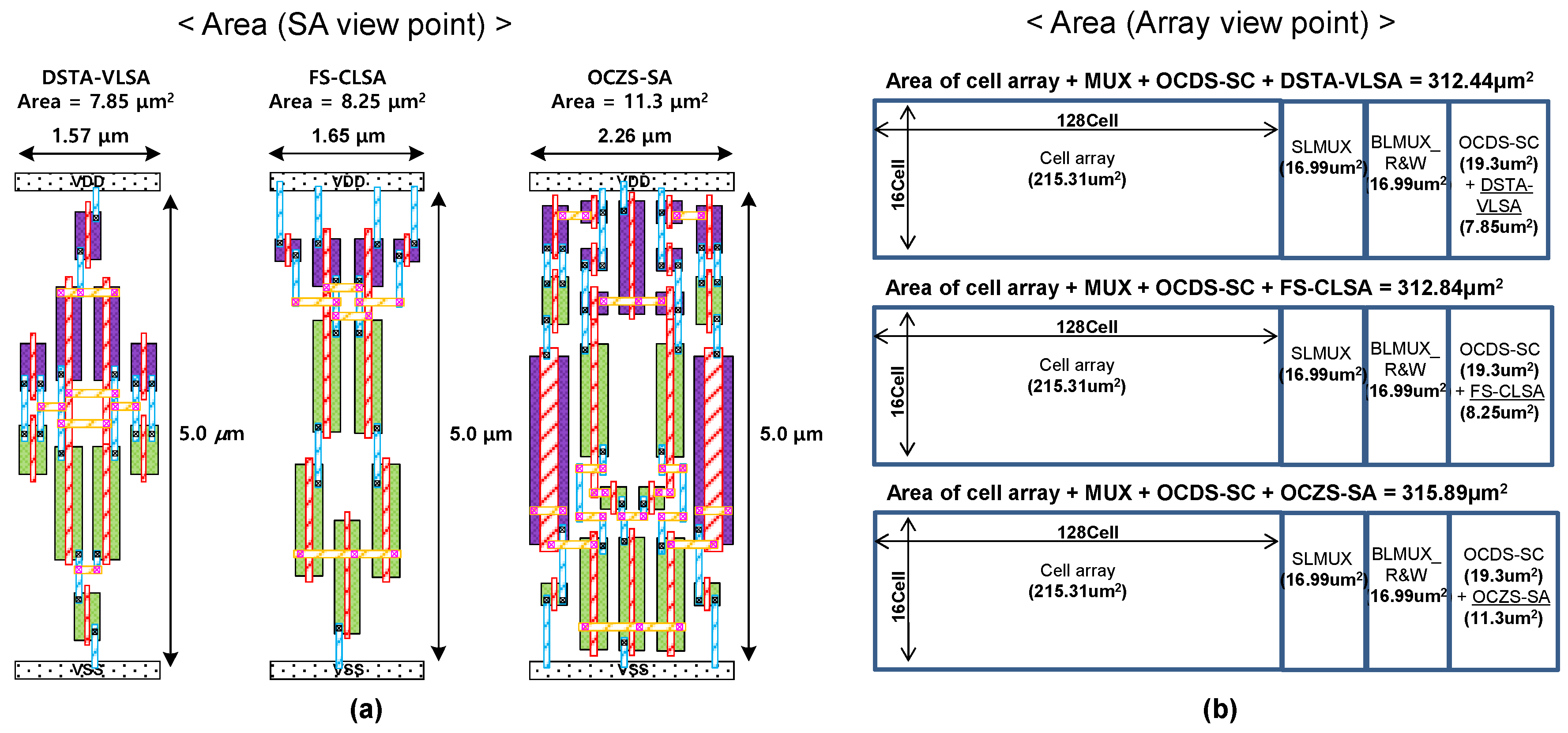

4. Simulation Results and Comparison

5. Conclusions

Funding

Conflicts of Interest

References

- Kawahara, A.; Azuma, R.; Ikeda, Y.; Kawai, K.; Katoh, Y.; Hayakawa, Y.; Tsuji, K.; Yoneda, S.; Himeno, A.; Shimakawa, K.; et al. An 8 Mb Multi-Layered Cross-Point ReRAM Macro With 443 MB/s Write Throughput. IEEE J. Solid State Circuits 2012, 48, 178–185. [Google Scholar] [CrossRef]

- Lin, C.; Kang, S.; Wang, Y.; Lee, K.; Zhu, X.; Li, X.; Hsu, W.; Kao, Y.; Liu, M.; Chen, W.; et al. 45nm low power CMOS logic compatible embedded STT MRAM utilizing a reverse-connection 1T/1MTJ cell. IEEE Int. Electron Devices Meet. (IEDM) 2009, 1–4. [Google Scholar] [CrossRef]

- Rizzo, N.D.; Houssameddine, D.; Janesky, J.; Whig, R.; Mancoff, F.B.; Schneider, M.L.; de Herrera, M.; Sun, J.J.; Nagel, K.; Deshpande, S.; et al. A Fully Functional 64 Mb DDR3 ST-MRAM Built on 90 nm CMOS Technology. IEEE Trans. Magn. 2013, 49, 4441–4446. [Google Scholar] [CrossRef]

- Chang, M.-F.; Shen, S.-J.; Liu, C.-C.; Wu, C.-W.; Lin, Y.-F.; King, Y.-C.; Lin, C.-J.; Liao, H.-J.; Chih, Y.-D.; Yamauchi, H. An Offset-Tolerant Fast-Random-Read Current-Sampling-Based Sense Amplifier for Small-Cell-Current Nonvolatile Memory. IEEE J. Solid State Circuits 2013, 48, 864–877. [Google Scholar] [CrossRef]

- Na, T.; Kim, J.; Kim, J.P.; Kang, S.H.; Jung, S.-O. Reference-Scheme Study and Novel Reference Scheme for Deep Submicrometer STT-RAM. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 3376–3385. [Google Scholar] [CrossRef]

- Na, T.; Kim, J.; Kim, J.P.; Kang, S.H.; Jung, S.-O. A Double-Sensing-Margin Offset-Canceling Dual-Stage Sensing Circuit for Resistive Nonvolatile Memory. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 1109–1113. [Google Scholar] [CrossRef]

- Na, T.; Woo, S.-H.; Kim, J.; Jeong, H.; Jung, S.-O. Comparative Study of Various Latch-Type Sense Amplifiers. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2013, 22, 425–429. [Google Scholar] [CrossRef]

- Nho, H.; Yoon, S.-S.; Wong, S.; Jung, S.-O. Numerical Estimation of Yield in Sub-100-nm SRAM Design Using Monte Carlo Simulation. IEEE Trans. Circuits Syst. II Express Briefs 2008, 55, 907–911. [Google Scholar] [CrossRef]

- Na, T.; Kim, J.; Kim, J.P.; Kang, S.H.; Jung, S.-O. An Offset-Canceling Triple-Stage Sensing Circuit for Deep Submicrometer STT-RAM. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 22, 1620–1624. [Google Scholar] [CrossRef]

- Na, T.; Kim, J.P.; Kang, S.H.; Jung, S.-O. Read Disturbance Reduction Technique for Offset-Canceling Dual-Stage Sensing Circuits in Deep Submicrometer STT-RAM. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 578–582. [Google Scholar] [CrossRef]

- Kim, J.; Ryu, K.; Kang, S.H.; Jung, S.-O. A Novel Sensing Circuit for Deep Submicron Spin Transfer Torque MRAM (STT-MRAM). IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2010, 20, 181–186. [Google Scholar] [CrossRef]

- Na, T.; Kang, S.H.; Jung, S.-O. Distribution Analysis and Multiple-point Tail Fitting Yield Estimation Method for STT-MRAM. J. Semicond. Technol. Sci. 2020, 20, 271–280. [Google Scholar] [CrossRef]

| DSTA-VLSA | FS-CLSA | OCZS-SA | |

|---|---|---|---|

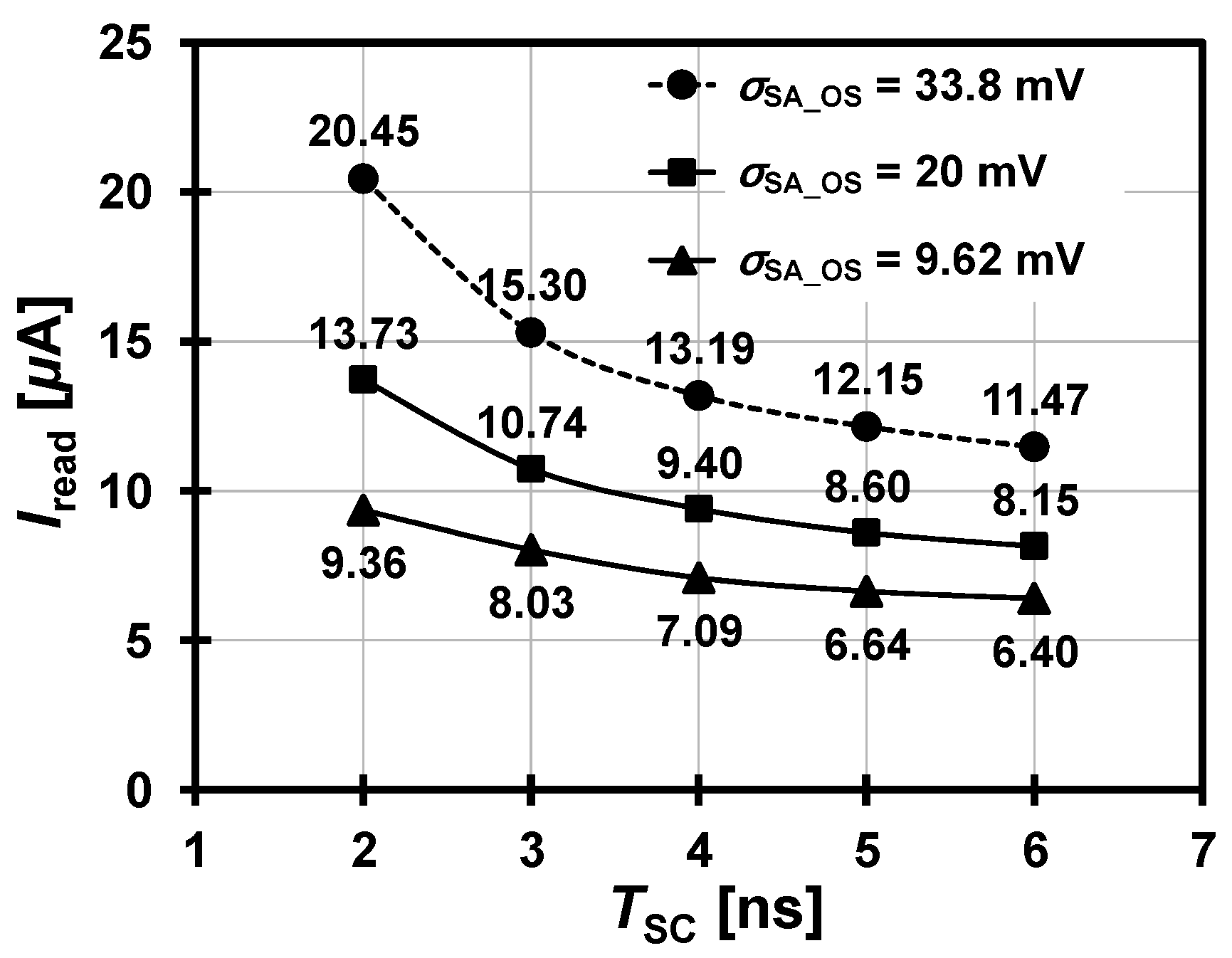

| Average σSA_OS (mV) | 33.8 1) | 20.0 2) | 9.62 |

| Sensing dead zone | None | VSA_data < VTHN | None |

| Normalized area overhead (SA viewpoint) | 0.95 | 1 | 1.37 |

| Normalized area overhead (Array viewpoint) | 0.999 | 1 | 1.010 |

| Normalized read energy/bit (SA viewpoint) | 0.94 | 1 | 2.25 |

| Normalized read energy/bit 3) (SC + SA viewpoint) | 1.43 | 1 | 0.84 |

© 2020 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Na, T. Robust Offset-Cancellation Sense Amplifier for an Offset-Canceling Dual-Stage Sensing Circuit in Resistive Nonvolatile Memories. Electronics 2020, 9, 1403. https://doi.org/10.3390/electronics9091403

Na T. Robust Offset-Cancellation Sense Amplifier for an Offset-Canceling Dual-Stage Sensing Circuit in Resistive Nonvolatile Memories. Electronics. 2020; 9(9):1403. https://doi.org/10.3390/electronics9091403

Chicago/Turabian StyleNa, Taehui. 2020. "Robust Offset-Cancellation Sense Amplifier for an Offset-Canceling Dual-Stage Sensing Circuit in Resistive Nonvolatile Memories" Electronics 9, no. 9: 1403. https://doi.org/10.3390/electronics9091403

APA StyleNa, T. (2020). Robust Offset-Cancellation Sense Amplifier for an Offset-Canceling Dual-Stage Sensing Circuit in Resistive Nonvolatile Memories. Electronics, 9(9), 1403. https://doi.org/10.3390/electronics9091403