A 2.45 GHz High Efficiency CMOS RF Energy Harvester with Adaptive Path Control

Abstract

1. Introduction

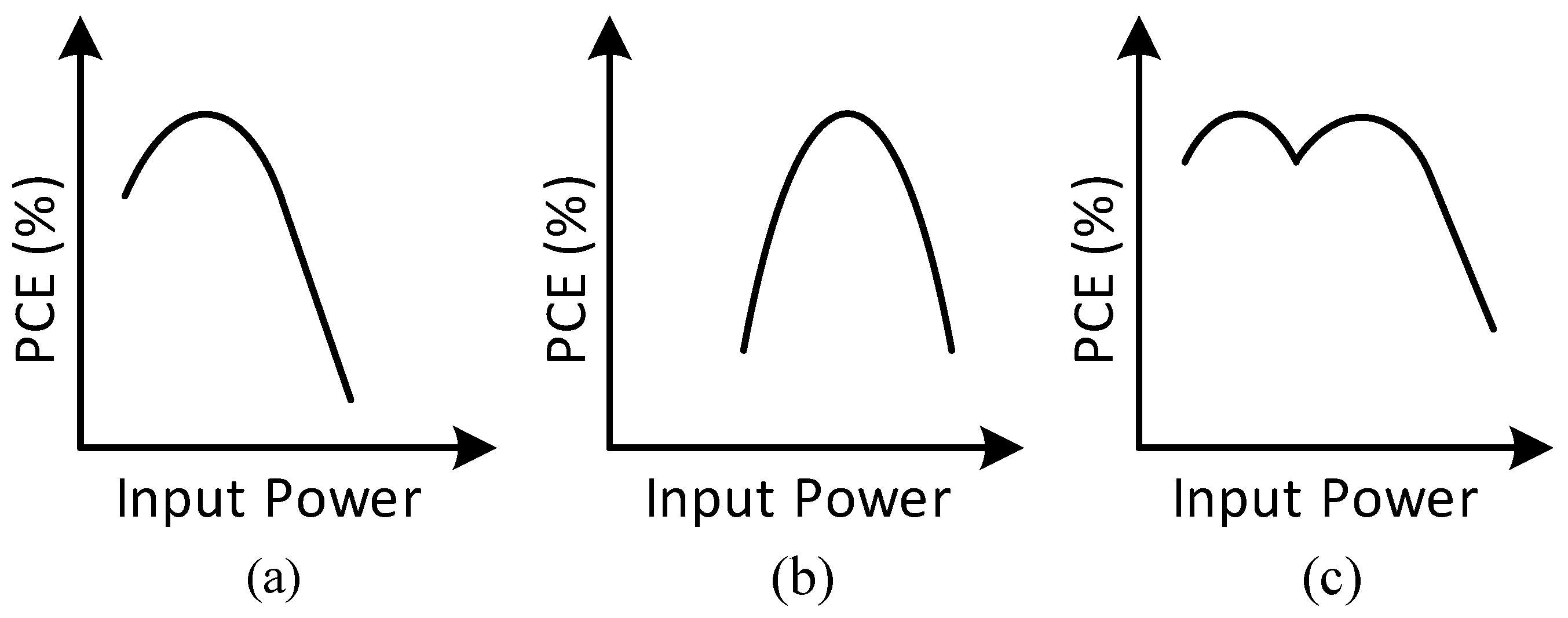

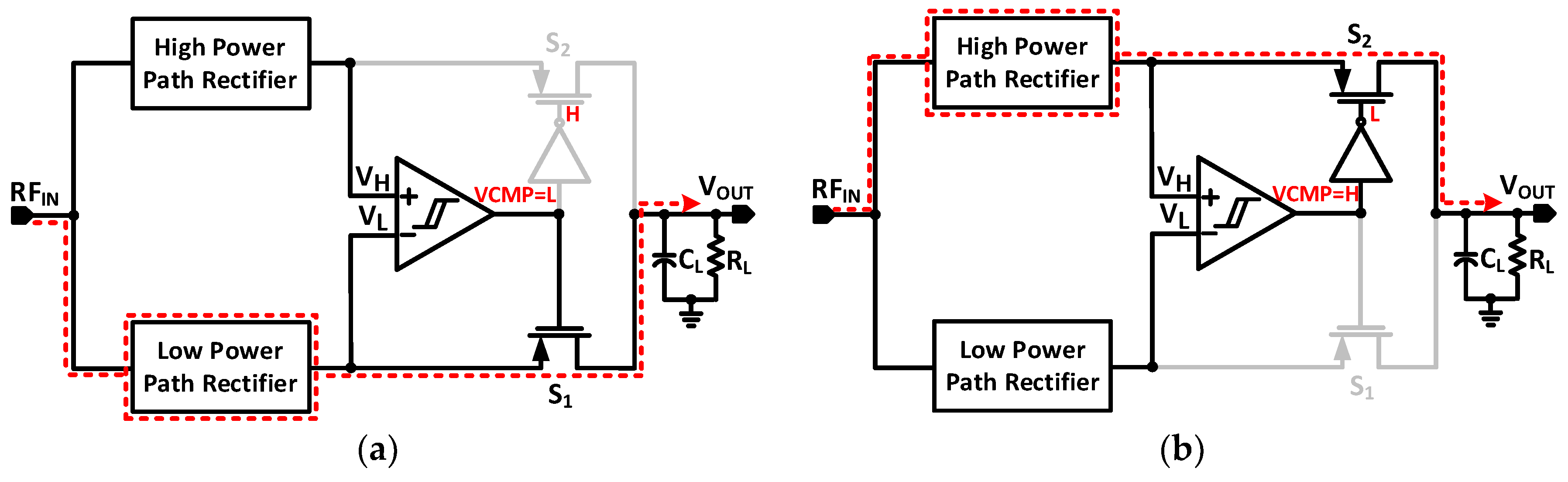

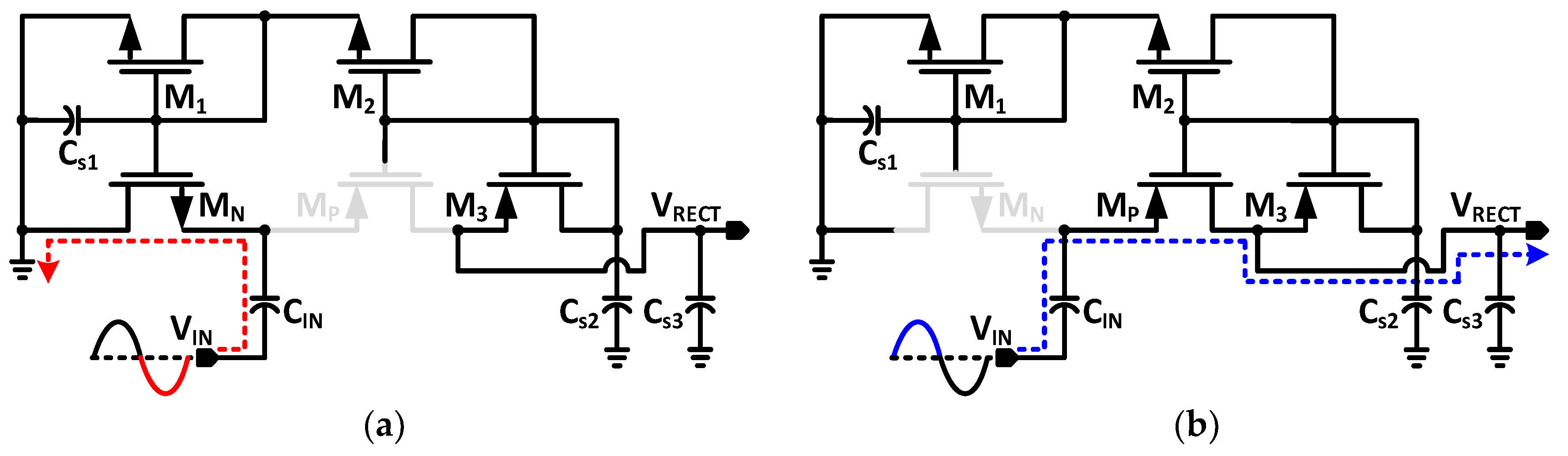

2. Proposed Reconfigurable RF-DC Converter

3. Circuit Description

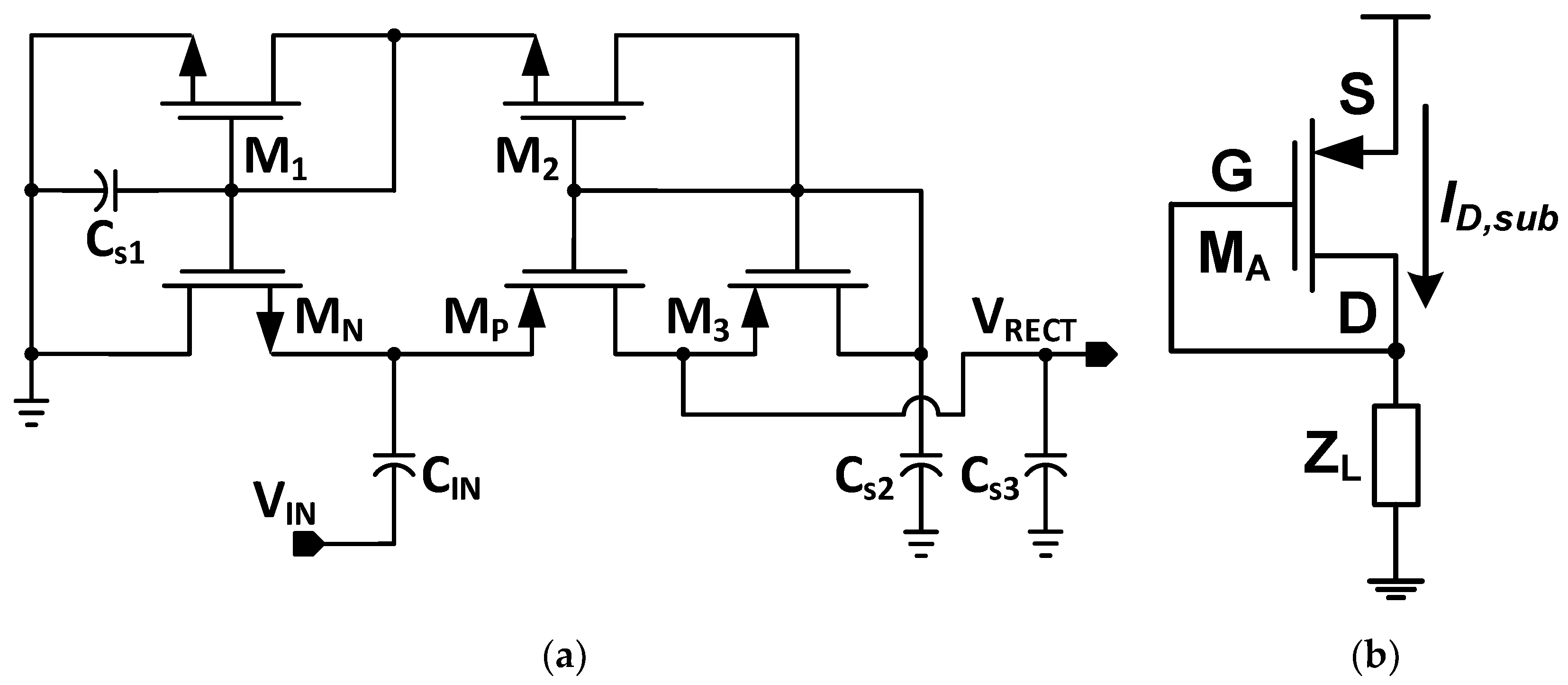

3.1. Rectifier Design

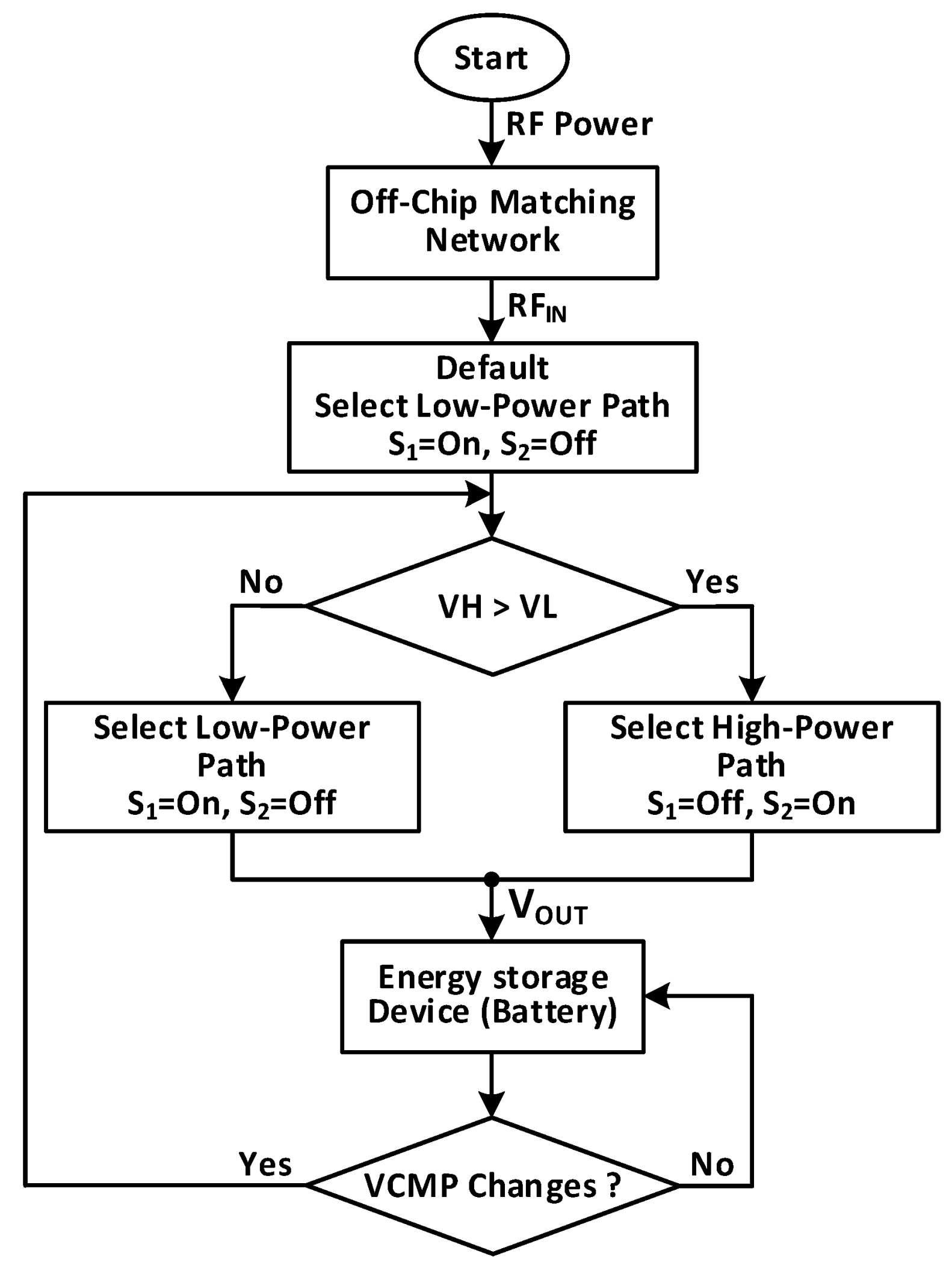

3.2. Adaptive Path Control Circuit Design

4. Measurement Results

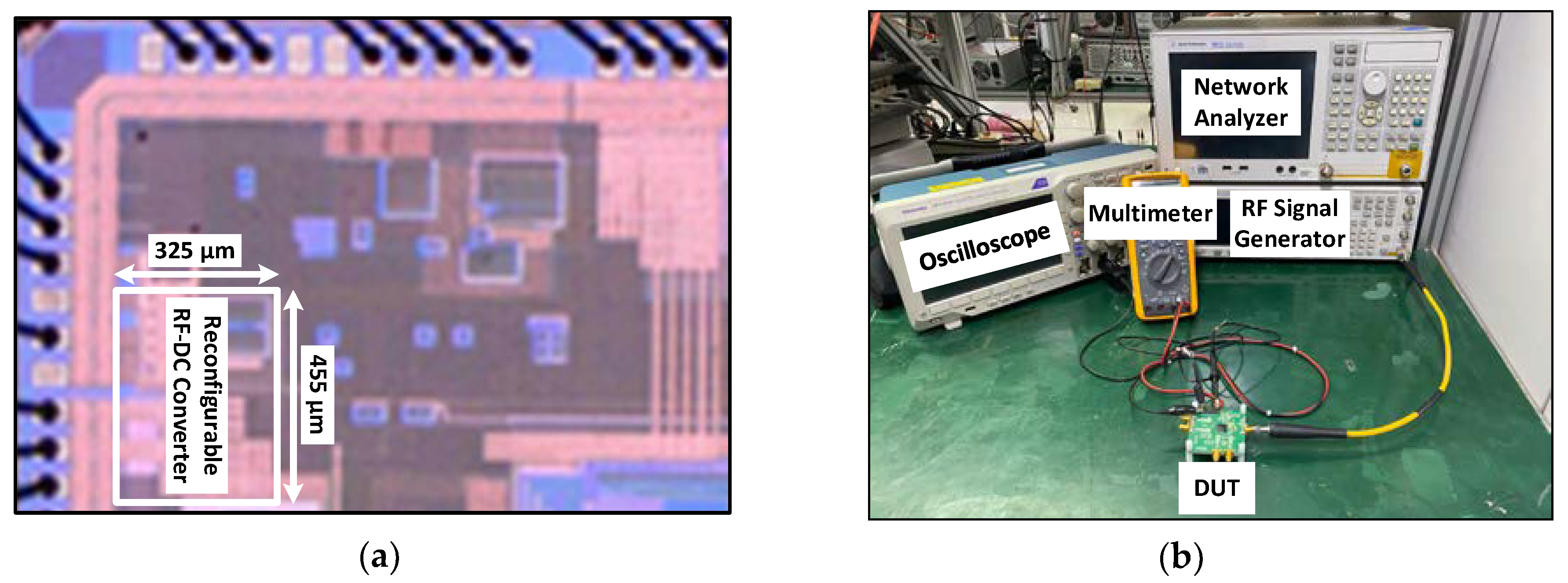

4.1. Microphotograph and Measurement Environment

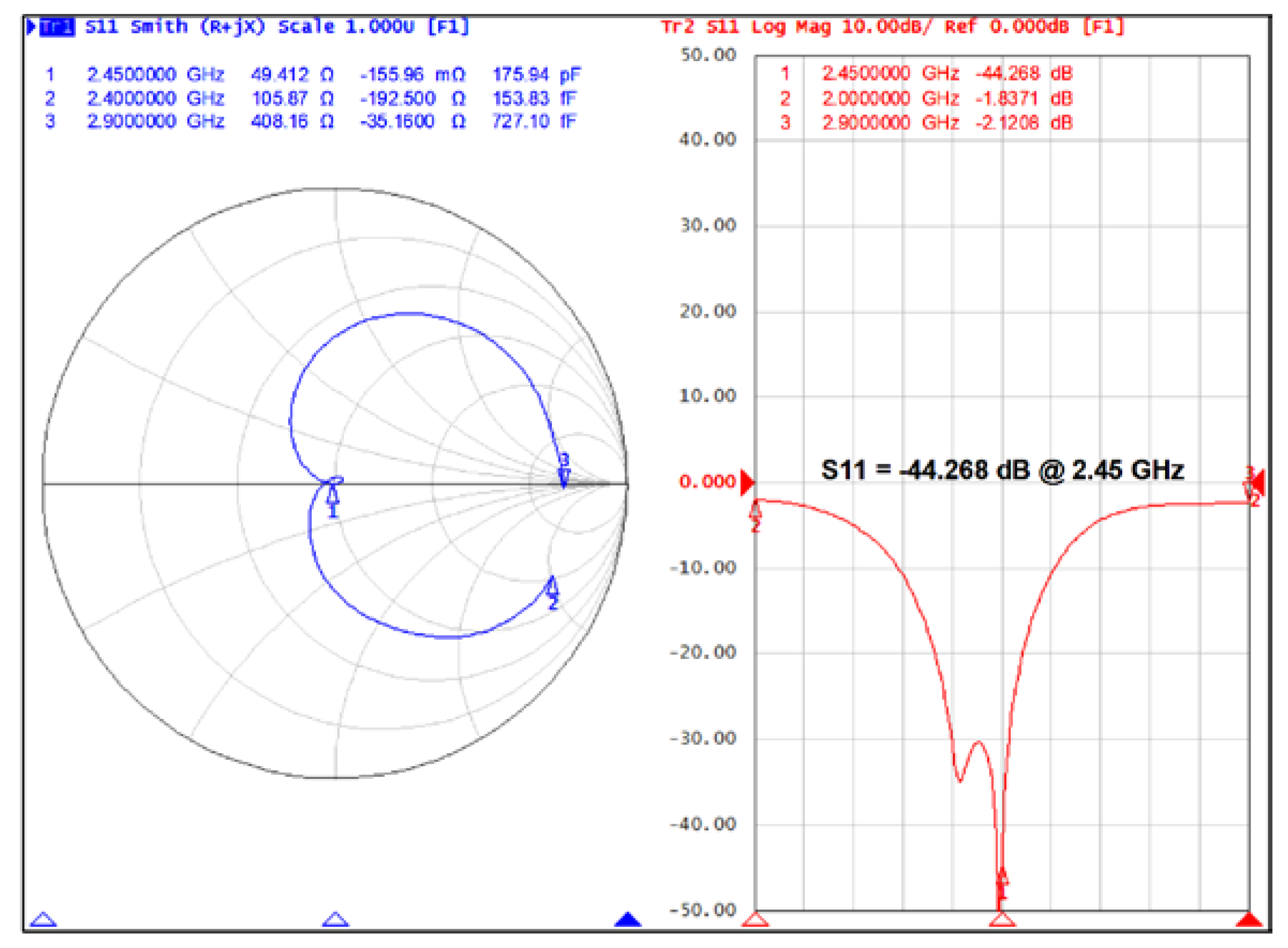

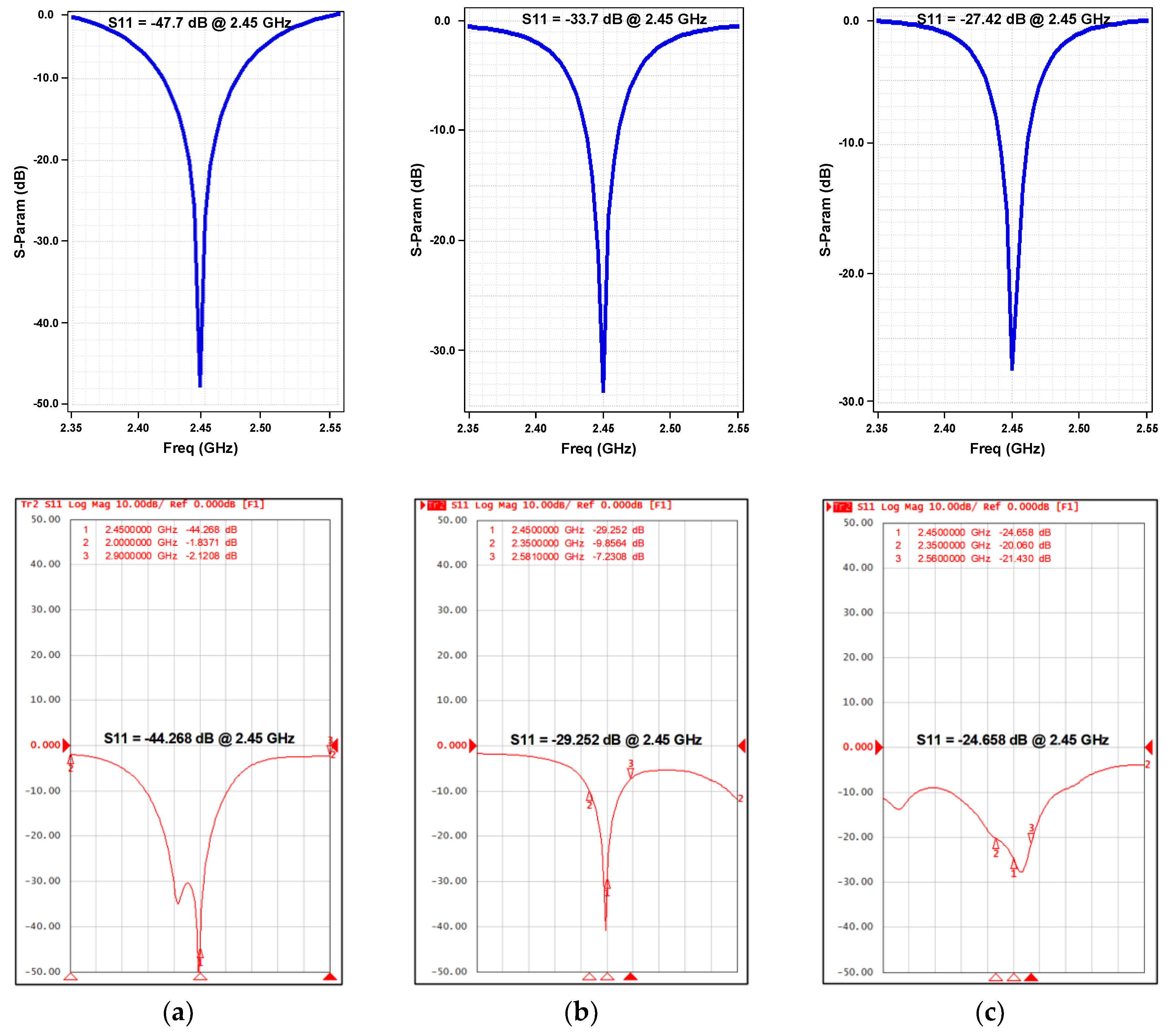

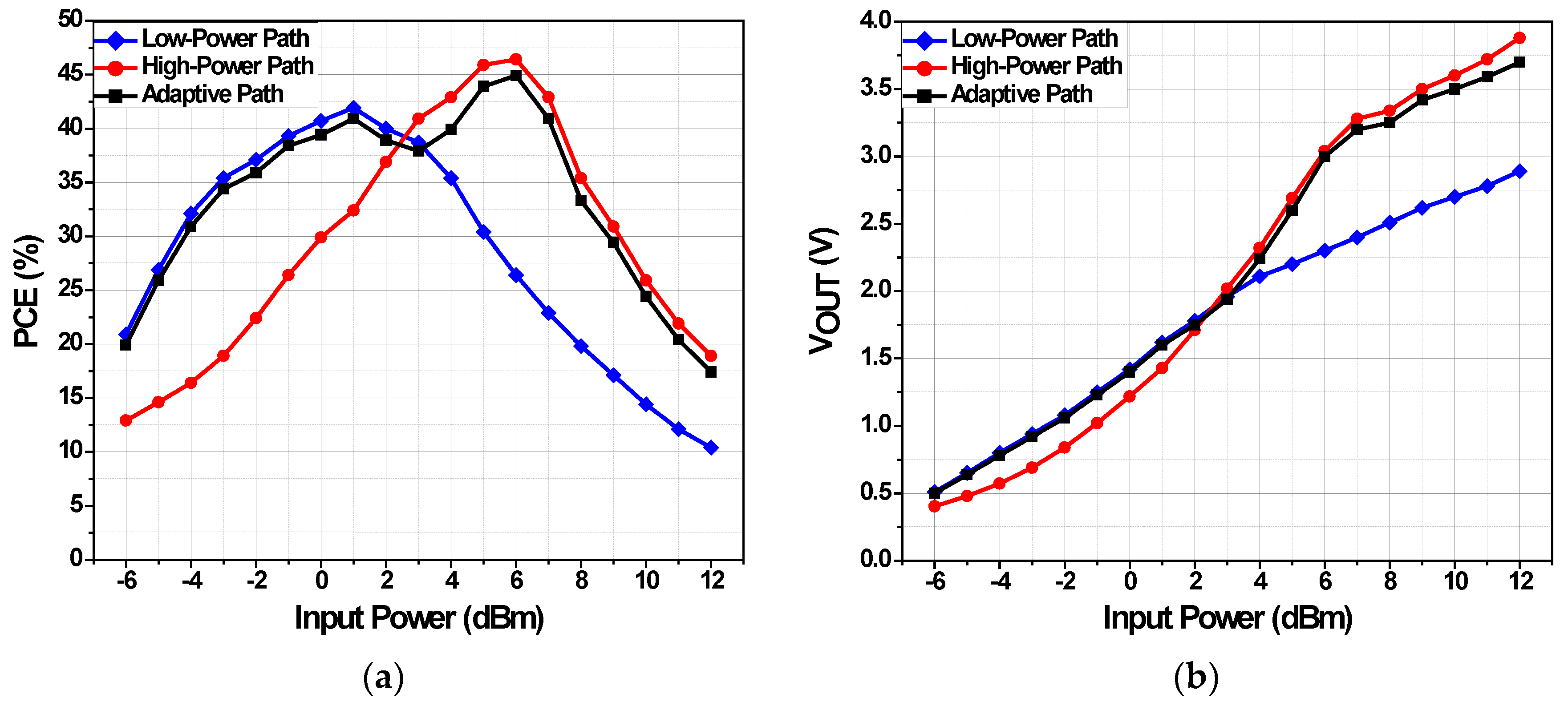

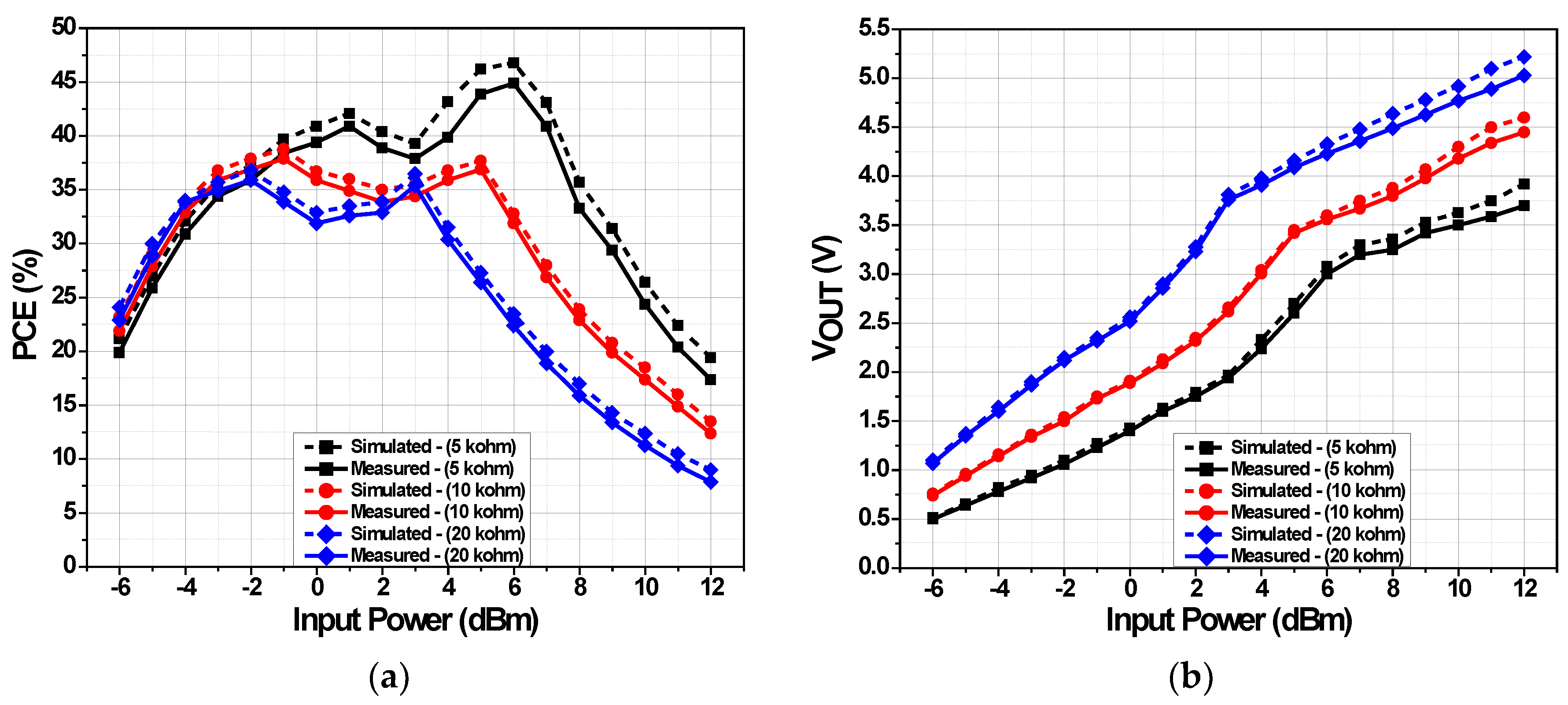

4.2. Performance Measurement

4.3. Comparison with Published Works

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Jonah, O.; Georgakopoulos, S.V. Wireless power transfer in concrete via strongly coupled magnetic resonance. J. Chem. Inf. Model. 2013, 53, 1689–1699. [Google Scholar] [CrossRef]

- Hekal, S.; Abdel-Rahman, A.B.; Jia, H.; Allam, A.; Barakat, A.; Pokharel, R.K. A novel technique for compact size wireless power transfer applications using defected ground structures. IEEE Trans. Microw. Theory Tech. 2017, 65, 591–599. [Google Scholar] [CrossRef]

- Yedavalli, P.S.; Riihonen, T.; Wnag, X.; Rabaey, J.M. Far-field RF wireless power transfer with blind adaptive beamforming for Internet of Things devices. IEEE Access 2017, 5, 1743–1752. [Google Scholar] [CrossRef]

- Xia, M.; Aissa, S. On the efficiency of far-field wireless power transfer. IEEE Trans. Signal Process. 2015, 63, 2835–2847. [Google Scholar] [CrossRef]

- Xiao, L.; Wang, P.; Niyato, D.; Kim, D.; Han, Z. Wireless networks with RF energy harvesting: A contemporary survey. IEEE Commun. Surv. Tuts 2015, 17, 757–789. [Google Scholar]

- Lu, Y.; Law, M.-K.; Sin, S.-W.; Seng-Pan, U.; Martins, R.P. A review and design of the on-chip rectifiers for RF energy harvesting. In Proceedings of the IEEE International Wireless Symposium, Shenzhen, China, 30 March–1 April 2015. [Google Scholar]

- Harouni, Z.; Cirio, L.; Osman, L.; Gharsallah, A.; Picon, O. A dual circularly polarized 2.45-GHz rectenna for wireless power transmission. IEEE Antennas Wirel. Propag. Lett. 2011, 10, 306–309. [Google Scholar] [CrossRef]

- Bito, J.; Hester, J.G.; Tentzeris, M.M. Ambient RF energy harvesting from a two-way talk radio for flexible wearable wireless sensor devices utilizing inkjet printing technologies. IEEE Trans. Microw. Theory Tech. 2015, 63, 4533–4543. [Google Scholar] [CrossRef]

- Abouzied, M.A.; Sanchez-Sinencio, E. Low-input power-level CMOS RF energy-harvesting front end. IEEE Trans. Microw. Theory Tech. 2015, 63, 3794–3805. [Google Scholar] [CrossRef]

- Ren, Y.-J.; Chang, K. 5.8-GHz circularly polarized dual-diode rectenna and rectenna array for microwave power transmission. IEEE Trans. Microw. Theory Tech. 2006, 54, 1495–1502. [Google Scholar]

- Kuhn, V.; Lahuec, C.; Seguin, F.; Person, C. A multi-band stacked RF energy harvester with RF-to-DC efficiency up to 84%. IEEE Trans. Microw. Theory Tech. 2015, 63, 1768–1778. [Google Scholar] [CrossRef]

- Abouzied, M.A.; Ravichandran, K.; Sánchez-Sinencio, E. A fully integrated reconfigurable self-startup RF energy harvesting system with storage capability. IEEE J. Solid-State Circuits 2017, 52, 704–719. [Google Scholar] [CrossRef]

- Curty, J.-P.; Joehl, N.; Krummenacher, F.; Dehollian, C.; Declercq, M.J. A model for μ-power rectifier analysis and design. IEEE Trans. Circuits Syst. I Reg. Pap. 2005, 52, 2771–2779. [Google Scholar] [CrossRef]

- FCC Codes of Regulation, Part 15 [Online]. Available online: http://www.access.gpo.gov/nara/cfr/waisidx_03/ (accessed on 20 April 2020).

- Hameed, Z.; Moez, K. A 3.2 V—15 dBm adaptive threshold-voltage compensated RF energy harvester in 130 nm CMOS. IEEE Trans. Circuits Syst. I Reg. Pap. 2015, 62, 948–956. [Google Scholar] [CrossRef]

- Li, C.-J.; Lee, T.-C. 2.4-GHz high-efficiency adaptive power. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 22, 434–438. [Google Scholar] [CrossRef]

- Dehghani, S.; Johnson, T. A 2.4-GHz CMOS class-E synchronous rectifier. IEEE Trans. Microw. Theory Tech. 2016, 64, 1655–1666. [Google Scholar] [CrossRef]

- Fan, S.; Yuan, H.; Gou, W.; Zhao, Y.; Song, C.; Huang, Y.; Zhou, J. A 2.45 GHz rectifier-booster regulator with impedance matching converters for wireless energy harvesting. IEEE Trans. Microw. Theory Tech. 2019, 67, 3833–3843. [Google Scholar] [CrossRef]

- Xu, P.; Flandre, D.; Bol, D. Analysis, modeling, and design of a 2.45-GHz RF energy harvester for SWIPT IoT smart sensors. IEEE J. Solid-State Circuits 2019, 54, 2717–2729. [Google Scholar] [CrossRef]

- Kim, S.-Y.; Abbasizadeh, H.; Rikan, B.S.; Oh, S.J.; Jang, B.G.; Park, Y.-J. A −20 to 30 dBm input power range wireless power system with a MPPT-based reconfigurable 48% efficient RF energy harvester and 82% efficient A4WP wireless power receiver with open loop delay compensation. IEEE Trans. Power Electron. 2018, 34, 6803–6817. [Google Scholar] [CrossRef]

- Khan, D.; Abbasizadeh, H.; Kim, S.-Y.; Khan, Z.H.N.; Shah, S.A.A.; Pu, Y.G.; Hwang, K.C.; Yang, Y.; Lee, M.; Lee, K.-Y.; et al. A design of ambient RF energy harvester with sensitivity of -21dBm and power efficiency of a 39.3% using internal threshold voltage compensation. Energies 2018, 11, 1258. [Google Scholar] [CrossRef]

- Khan, D.; Oh, S.J.; Shehzad, K.; Verma, D.; Khan, Z.H.N.; Pu, Y.G. A CMOS RF energy harvester with 47% peak efficiency using internal threshold voltage compensation. IEEE Micow. Wirel. Compon. Lett. 2019, 29, 415–417. [Google Scholar] [CrossRef]

- Saffari, P.; Basaligheh, A.; Moez, K. An RF-to-DC recifier with high efficiency over wide input power range for RF energy harvesting applications. IEEE Trans. Circuits Syst. I Reg. Pap. 2019, 66, 4862–4875. [Google Scholar] [CrossRef]

- Li, B.; Shao, X.; Shahshahan, N.; Goldsman, N.; Salter, T.; Metze, G. An antenna co-design dual band RF energy harvester. IEEE Trans. Circuits Syst. I Reg. Pap. 2013, 60, 3256–3266. [Google Scholar] [CrossRef]

- Lu, Y.; Dai, H.; Huang, M.; Law, M.-K.; Sin, S.-W.; Seng-Pan, U.; Martins, R.P. A wide input range dual-path CMOS rectifier for RF energy harvesting. IEEE Trans. Circuits Syst. II Exp. Briefs. 2017, 64, 166–170. [Google Scholar] [CrossRef]

- Papotto, G.; Carrara, F.; Palmisano, G. A 90-nm CMOS threshold- compensated RF energy harvester. IEEE J. Solid-State Circuits 2011, 46, 1985–1997. [Google Scholar] [CrossRef]

- Stoopman, M.; Keyrouz, S.; Visser, H.J.; Philips, K.; Serdijn, W. Co-design of a CMOS rectifier and small loop antenna for highly sensitive RF energy harvesters. IEEE J. Solid-State Circuits 2014, 49, 622–634. [Google Scholar] [CrossRef]

- Scorcioni, S.; Larcher, L.; Bertacchini, A. A reconfigurable differential CMOS RF energy scavenger with 60% peak efficiency and -21 dBm sensitivity. IEEE Microw. Wirel. Compon. Lett. 2013, 23, 155–157. [Google Scholar] [CrossRef]

- Mansour, M.M.; Ichihashi, M.; Kanaya, H. Wide-band and efficiency-improved 0.18um CMOS RF differential rectifier for wireless energy harvesting. In Proceedings of the 2019 IEEE Asia-Pacific Microwave Conference (APMC), Singapore, 10–13 December 2019; pp. 141–143. [Google Scholar]

- Lee, D.; Kim, T.; Kim, S.; Byun, K.; Kwon, K. A CMOS rectifier with 72.3% RF-to-DC conversion efficiency employing tunable impedance matching network for ambient RF energy harvesting. In Proceedings of the 2018 International SoC Design Conference (ISOCC), Daegu, Korea, 12–15 November 2018; pp. 259–260. [Google Scholar]

- Li, X.; Huang, M.; Martins, R.P. A 2.4-GHz mid-field CMOS wireless power receiver achieving 46% maximum PCE and 163-mW output power. IEEE Trans. Circuits Syst. II 2020, 67, 360–364. [Google Scholar] [CrossRef]

- Taur, Y.; Ning, T.H. Fundamentals of Modern VLSI Devices; Cambridge University Press: Cambridge, UK, 1998. [Google Scholar]

- Khan, D.; Oh, S.J.; Shehzad, K.; Basim, M.; Verma, D.; Pu, Y.G.; Lee, M.; Hwang, K.C. An efficient reconfigurable RF-DC converter with wide input power range for RF energy harvesting. IEEE Access 2020, 8, 79310–79318. [Google Scholar] [CrossRef]

| This Work | TCAS-II-20 [33] | TMTT-16 [17] | TMTT-19 [18] | JSSC-19 [19] | TPE-18 [20] | ISOCC-18 [30] | |

|---|---|---|---|---|---|---|---|

| Technology | 180 nm | 28 nm | 130 nm | Diode-Based | 65 nm | 180 nm | 130 nm |

| Frequency | 2.45 GHz | 2.40 GHz | 2.40 GHz | 2.45 GHz | 2.45 GHz | 0.90 GHz | 0.7–0.9 |

| Topology | SE | CC | Class E | RBR | CC | SE | CC |

| Technique | Dual-path | - | - | - | MPPT | MPPT | T-MN |

| Peak PCE and at different input power levels | Peak: 45% @ 6 dBm | Peak: 46% @ 25.5 dBm * | Peak: 30% @ 10 dBm | Peak: 37.5% @ 13 dBm | Peak: 48.3% @ −3 dBm | Peak: 48.2% @ 0 dBm | Peak: 72.3% @ −15 dBm |

| 20% @ −6 dBm | 20% @ 18 dBm * | 10% @ 0 dBm * | 17.5% @ 0 dBm * | 25% @ −10 dBm * | 31.8% @ −20 dBm | 40% @ −18 dBm * | |

| 20.5% @ 11 dBm | 35% @ 30 dBm * | 21% @ 18 dBm * | 35% @ 15 dBm * | 46% @ 0 dBm | 41.1% @ 20 dBm | 20% @ −5 dBm * | |

| Load | 5 kΩ | 24 Ω | - | 20 kΩ | PMU | 23 kΩ | 10 kΩ |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Khan, D.; Basim, M.; Shehzad, K.; Ain, Q.U.; Verma, D.; Asif, M.; Oh, S.J.; Pu, Y.G.; Yoo, S.-S.; Hwang, K.C.; et al. A 2.45 GHz High Efficiency CMOS RF Energy Harvester with Adaptive Path Control. Electronics 2020, 9, 1107. https://doi.org/10.3390/electronics9071107

Khan D, Basim M, Shehzad K, Ain QU, Verma D, Asif M, Oh SJ, Pu YG, Yoo S-S, Hwang KC, et al. A 2.45 GHz High Efficiency CMOS RF Energy Harvester with Adaptive Path Control. Electronics. 2020; 9(7):1107. https://doi.org/10.3390/electronics9071107

Chicago/Turabian StyleKhan, Danial, Muhammad Basim, Khuram Shehzad, Qurat Ul Ain, Deeksha Verma, Muhammad Asif, Seong Jin Oh, Young Gun Pu, Sang-Sun Yoo, Keum Cheol Hwang, and et al. 2020. "A 2.45 GHz High Efficiency CMOS RF Energy Harvester with Adaptive Path Control" Electronics 9, no. 7: 1107. https://doi.org/10.3390/electronics9071107

APA StyleKhan, D., Basim, M., Shehzad, K., Ain, Q. U., Verma, D., Asif, M., Oh, S. J., Pu, Y. G., Yoo, S.-S., Hwang, K. C., Yang, Y., & Lee, K.-Y. (2020). A 2.45 GHz High Efficiency CMOS RF Energy Harvester with Adaptive Path Control. Electronics, 9(7), 1107. https://doi.org/10.3390/electronics9071107