Reverse Conduction Loss Minimization in GaN‑Based PMSM Drive

Abstract

1. Introduction

2. Theoretical Analysis

2.1. Dead-Time Generation

2.2. Reverse Conduction Loss

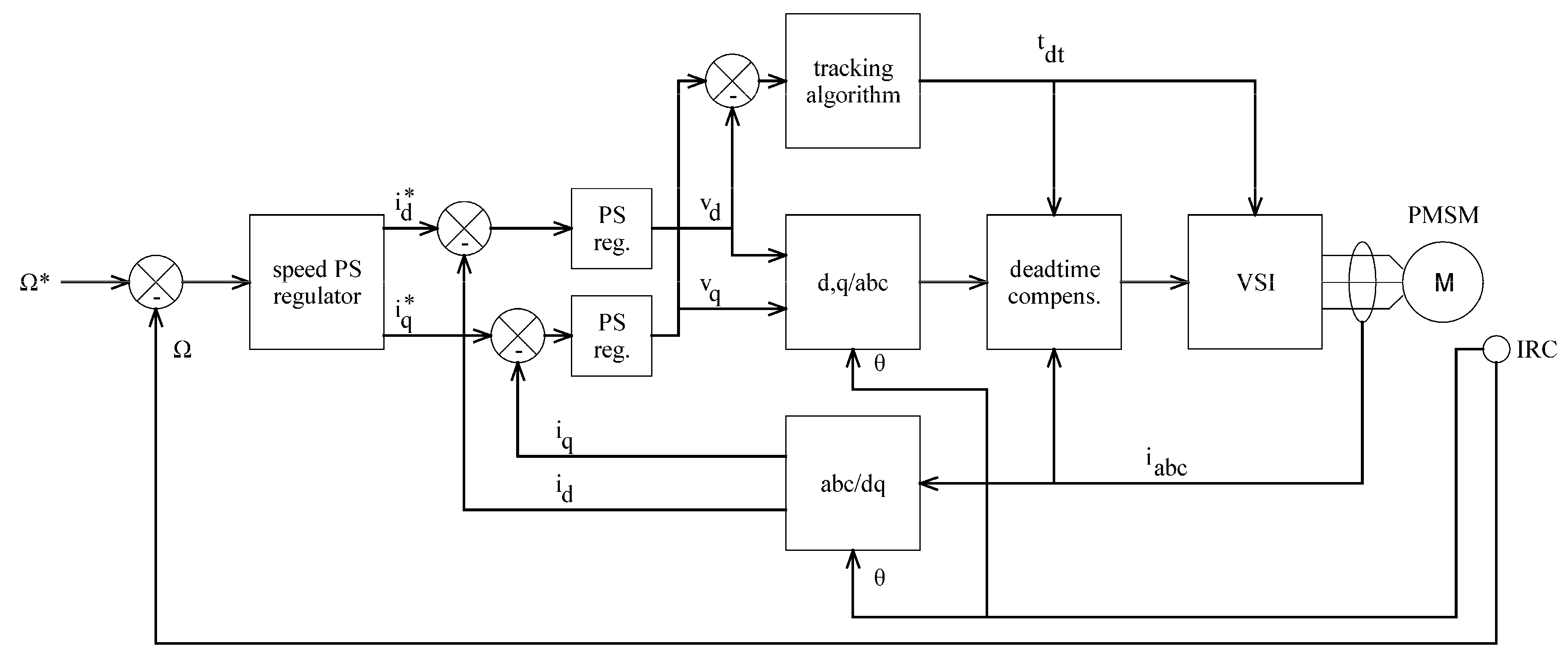

2.3. Drive Controller

2.4. Tracking Algorithm

3. Experimental Results

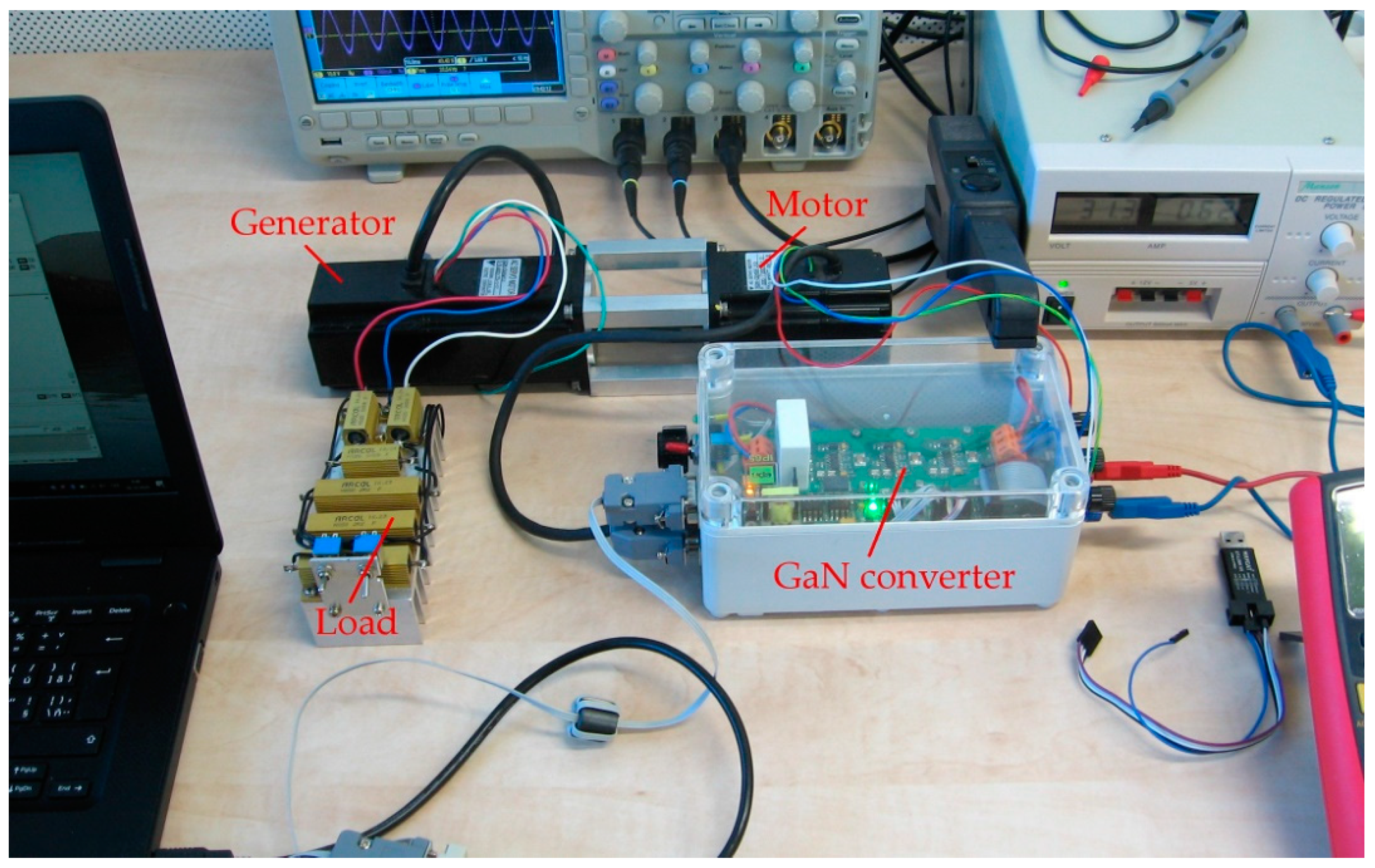

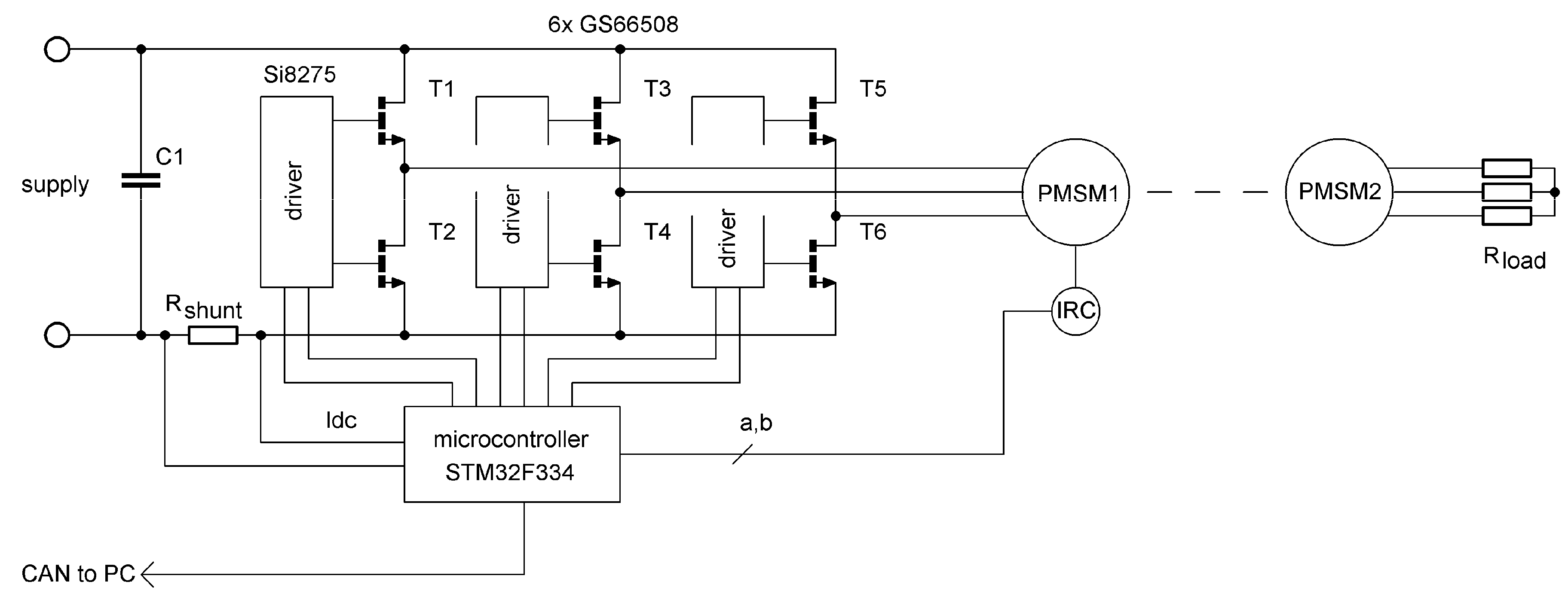

3.1. Experimental Setup

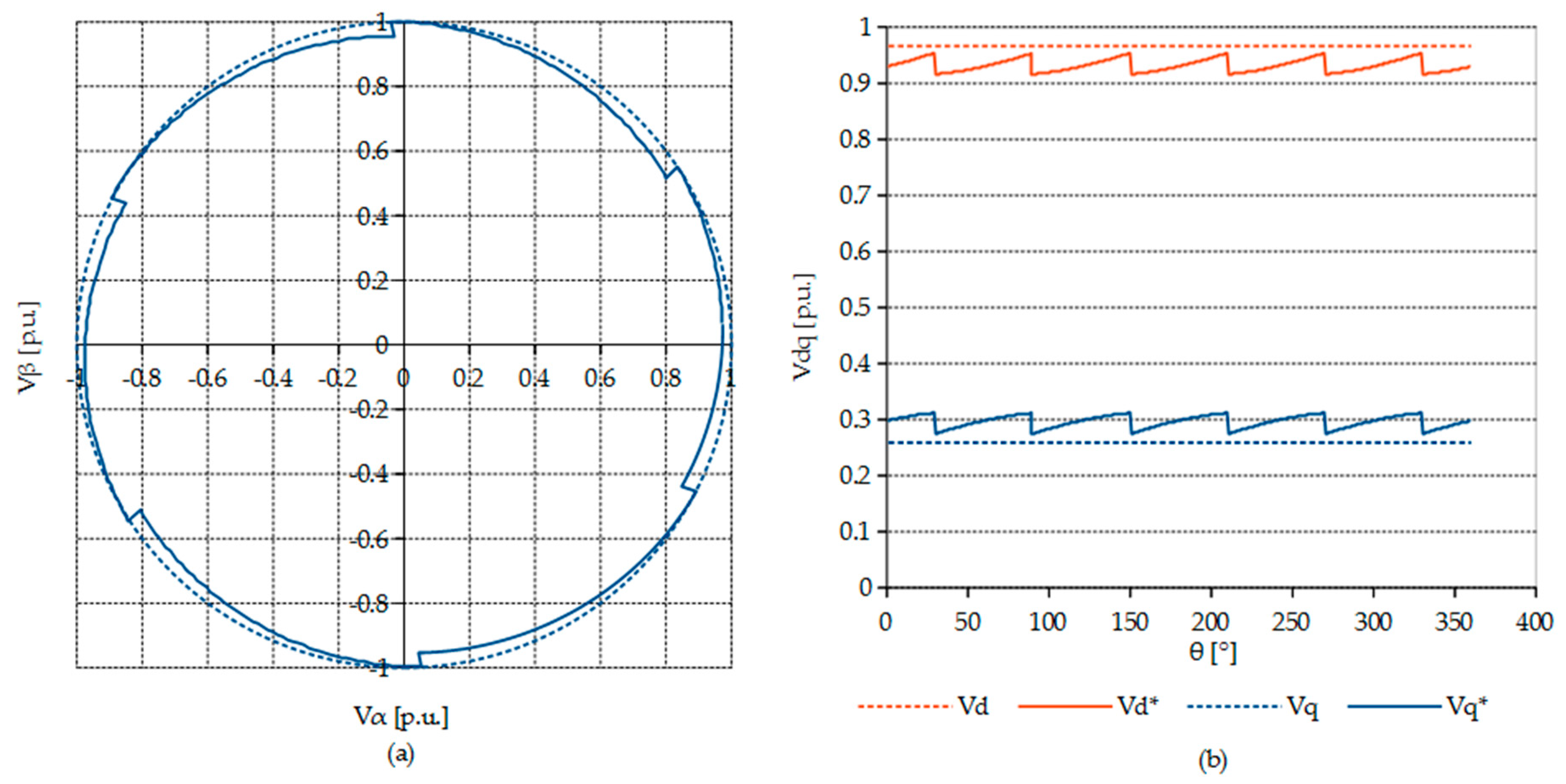

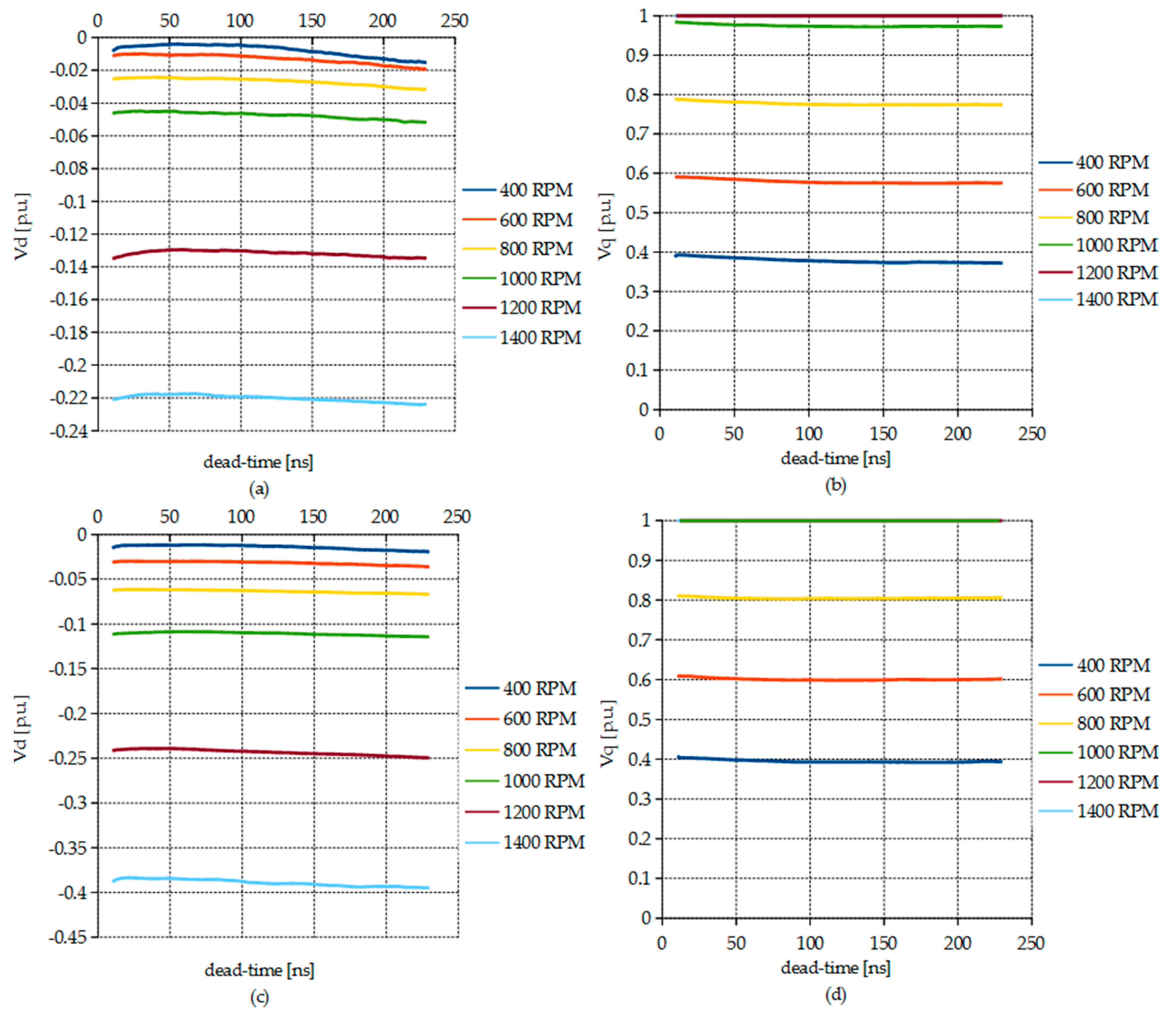

3.2. Current Controllers’ Output Change with Dead-Time

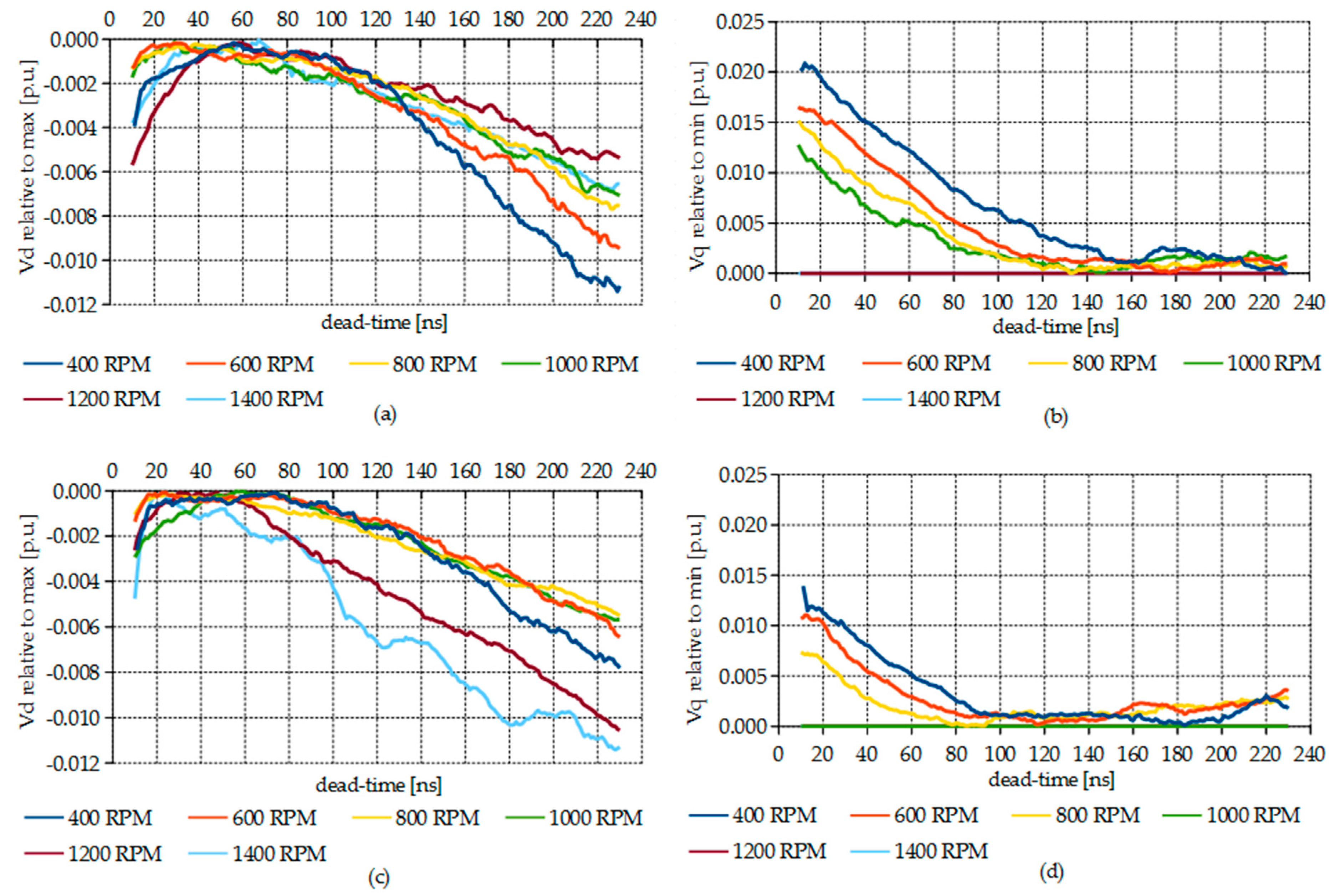

3.3. Tracking Algorithm

3.4. Dead-Time Loss Minimization

3.5. Comparison with Other Methods Mentioned in the Literature

4. Discussion

Author Contributions

Funding

Conflicts of Interest

References

- Chen, K.J.; Häberlen, O.; Lidow, A.; Tsai, C.L.; Ueda, T.; Uemoto, Y.; Wu, Y. GaN-on-Si Power Technology: Devices and Applications. IEEE Trans. Electron. Devices 2017, 64, 779–795. [Google Scholar] [CrossRef]

- Shirabe, K.; Swamy, M.M.; Kang, J.-K.; Hisatsune, M.; Wu, Y.; Kebort, D.; Honea, J. Efficiency Comparison Between Si-IGBT-Based Drive and GaN-Based Drive. IEEE Trans. Ind. Appl. 2014, 50, 566–572. [Google Scholar] [CrossRef]

- Ding, X.; Zhou, Y.; Cheng, J. A review of gallium nitride power device and its applications in motor drive. CES Trans. El. Mach. Syst. 2019, 3, 54–64. [Google Scholar] [CrossRef]

- Deboy, G.; Treu, M.; Haeberlen, O.; Neumayr, D. Si, SiC and GaN power devices: An unbiased view on key performance indicators. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016. [Google Scholar]

- Xie, R.; Wang, H.; Tang, G.; Yang, X.; Chen, K.J. An Analytical Model for False Turn-On Evaluation of High-Voltage Enhancement-Mode GaN Transistor in Bridge-Leg Configuration. IEEE Trans. Power Electron. 2017, 32, 6416–6433. [Google Scholar] [CrossRef]

- Sørensen, C.; Fogsgaard, M.L.; Christiansen, M.N.; Graungaard, M.K.; Nørgaard, J.B.; Uhrenfeldt, C.; Trintis, I. Conduction, reverse conduction and switching characteristics of GaN E-HEMT. In Proceedings of the 6th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Aachen, Germany, 22–25 June 2015. [Google Scholar]

- Lee, W.; Han, D.; Choi, W.; Sarlioglu, B. Reducing reverse conduction and switching losses in GaN HEMT-based high-speed permanent magnet brushless dc motor drive. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017. [Google Scholar]

- Williford, P.; Jones, E.A.; Yang, Z.; Chen, J.; Wang, F.; Bala, S.; Xu, J. Optimal Dead-time Setting and Loss Analysis for GaN-based Voltage Source Converter. In Proceedings of the 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018. [Google Scholar]

- Roschatt, P.M.; McMahon, R.A.; Pickering, S. Investigation of dead-time behaviour in GaN DC-DC buck converter with a negative gate voltage. In Proceedings of the 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), Seoul, Korea, 1–5 June 2015. [Google Scholar]

- Joo, D.M.; Byun, J.E.; Lee, B.K.; Kim, J.S. Adaptive delay control for synchronous rectification phase-shifted full bridge converter with GaN HEMT. Electron. Lett. 2017, 53, 1541–1542. [Google Scholar] [CrossRef]

- Schirone, L.; Macellari, M.; Pellitteri, F. Predictive dead time controller for GaN-based boost converters. IET Power Electron. 2017, 10, 421–428. [Google Scholar] [CrossRef]

- Dyer, J.; Zhang, Z.; Wang, F.; Costinett, D.; Tolbert, L.M.; Blalock, B.J. Dead-time optimization for SiC based voltage source converters using online condition monitoring. In Proceedings of the 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Albuquerque, NM, USA, 30 October–1 November 2017. [Google Scholar]

- Zhang, Y.; Chen, C.; Liu, T.; Xu, K.; Kang, Y.; Peng, H. A High Efficiency Model-Based Adaptive Dead-Time Control Method for GaN HEMTs Considering Nonlinear Junction Capacitors in Triangular Current Mode Operation. IEEE Emerg. Sel. Power Electron. 2020, 8, 124–140. [Google Scholar] [CrossRef]

- Han, D.; Sarlioglu, B. Deadtime Effect on GaN-Based Synchronous Boost Converter and Analytical Model for Optimal Deadtime Selection. IEEE Trans. Power Electron. 2016, 31, 601–612. [Google Scholar] [CrossRef]

- Abu-qahouq, J.A.; Mao, H.; Al-atrash, H.J.; Batarseh, I. Maximum Efficiency Point Tracking (MEPT) Method and Digital Dead Time Control Implementation. IEEE Trans. Power Electron. 2006, 21, 1273–1281. [Google Scholar] [CrossRef]

- Chiu, P.K.; Wang, P.Y.; Li, S.T.; Chen, C.J.; Chen, Y.T. A GaN driver IC with novel highly digitally adaptive dead-time control for Synchronous Rectifier Buck Converter. In Proceedings of the 2020 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 11–15 October 2020. [Google Scholar]

- Skarolek, P.; Lettl, J. Tracking Dead-time Algorithm for GaN DC/DC Converter. In Proceedings of the 2019 International Conference on Applied Electronics (AE), Pilsen, Czech Republic, 10–11 September 2019. [Google Scholar]

- Moradpour, M.; Serpi, A.; Gatto, G. Dead-Time Analysis of a Universal SiC-GaN-Based DC DC Converter for Plug-In Electric Vehicles. In Proceedings of the IECON 2018—44th Annual Conference of the IEEE Industrial Electronics Society, Washington, DC, USA, 21–23 October 2018. [Google Scholar]

- Spence, K.; Chang, L.; Shao, R. Robust Compensation of Dead Time in DCM for Grid Connected Bridge Inverters. In Proceedings of the 2018 IEEE International Power Electronics and Application Conference and Exposition (PEAC), Shenzhen, China, 4–7 November 2018. [Google Scholar]

- Zhou, K.; Ai, M.; Sun, D.; Jin, N.; Wu, X. Field Weakening Operation Control Strategies of PMSM Based on Feedback Linearization. Energies 2019, 12, 4526. [Google Scholar] [CrossRef]

- Lipcak, O.; Bauer, J. Analysis of Voltage Distortion and Comparison of Two Simple Voltage Compensation Methods for Sensorless Control of Induction Motor. In Proceedings of the 2019 IEEE 10th International Symposium on Sensorless Control for Electrical Drives (SLED), Turin, Italy, 9–10 September 2019. [Google Scholar]

- Park, C.-H.; Kim, D.-Y.; Yeom, H.-B.; Son, Y.-D.; Kim, J.-M. A Current Reconstruction Strategy Following the Operation Area in a 1-Shunt Inverter System. Energies 2019, 12, 1423. [Google Scholar] [CrossRef]

| Current Direction | Dead-Time Polarity | Output Duty Cycle |

|---|---|---|

| Source | Positive | |

| Source | Negative | |

| Sink | Positive | |

| Sink | Negative |

| Motor | Generator | |

|---|---|---|

| Type | SGM-02A5F | SGM-04AW12 |

| RPM | 3000 | 3000 |

| Power (W) | 200 | 400 |

| Max voltage (V) | 200 | 200 |

| Max current (A) | 2.0 | 4.0 |

| Stator resistance (Ω) | 1.35 | 1.26 |

| -axis inductance (mH) | 7.05 | 7.75 |

| -axis inductance (mH) | 7.25 | 8.05 |

| RPM | Input DC-Link Current for Various Dead-Time Values (A) | Relative Power Saved with the Tracking Algorithm (%) | |||||||

|---|---|---|---|---|---|---|---|---|---|

| 200 ns | 100 ns | 50 ns | 10 ns | Tracker on | 200 ns | 100 ns | 50 ns | 10 ns | |

| 400 | 0.1416 | 0.1409 | 0.1419 | 0.1478 | 0.1409 | −0.50 | −0.01 | −0.71 | −4.90 |

| 600 | 0.2376 | 0.2364 | 0.2373 | 0.2440 | 0.2362 | −0.59 | −0.08 | −0.47 | −3.30 |

| 800 | 0.3658 | 0.3641 | 0.3643 | 0.3750 | 0.3636 | −0.61 | −0.14 | −0.19 | −3.14 |

| 1000 | 0.5338 | 0.5310 | 0.5301 | 0.5400 | 0.5293 | −0.85 | −0.32 | −0.15 | −2.02 |

| 1200 | 0.7641 | 0.7600 | 0.7574 | 0.7700 | 0.7573 | −0.90 | −0.36 | −0.01 | −1.68 |

| 1250 | 0.8703 | 0.8656 | 0.8642 | 0.8755 | 0.8621 | −0.95 | −0.41 | −0.24 | −1.55 |

| 1300 | 0.9832 | 0.9748 | 0.9709 | 0.9830 | 0.9682 | −1.55 | −0.68 | −0.28 | −1.53 |

| 1350 | 1.0750 | 1.067 | 1.0620 | 1.0780 | 1.0580 | −1.61 | −0.85 | −0.38 | −1.89 |

| 1400 | 1.1385 | 1.1309 | 1.1258 | 1.136 | 1.118 | −1.83 | −1.15 | −0.70 | −1.61 |

| Additional Measurements | Simulation Requirements | HW | SW | Loss Minimization | |

|---|---|---|---|---|---|

| Fixed Dead-time [18] | single measurement | - | - | - | low |

| Look-Up Table [10] | dead-time map required | - | memory space | searching in the dead-time map | medium |

| Model-Based [13] | - | converter model preparation | - | converter model online calculation | high |

| Dead-Time Sensor [11] | - | - | reverse drop sampling circuit | reverse drop data acquisition | high |

| Method Proposed in This Paper | - | - | - | tracking algorithm | high |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Skarolek, P.; Frolov, F.; Lipcak, O.; Lettl, J. Reverse Conduction Loss Minimization in GaN‑Based PMSM Drive. Electronics 2020, 9, 1973. https://doi.org/10.3390/electronics9111973

Skarolek P, Frolov F, Lipcak O, Lettl J. Reverse Conduction Loss Minimization in GaN‑Based PMSM Drive. Electronics. 2020; 9(11):1973. https://doi.org/10.3390/electronics9111973

Chicago/Turabian StyleSkarolek, Pavel, Filipp Frolov, Ondrej Lipcak, and Jiri Lettl. 2020. "Reverse Conduction Loss Minimization in GaN‑Based PMSM Drive" Electronics 9, no. 11: 1973. https://doi.org/10.3390/electronics9111973

APA StyleSkarolek, P., Frolov, F., Lipcak, O., & Lettl, J. (2020). Reverse Conduction Loss Minimization in GaN‑Based PMSM Drive. Electronics, 9(11), 1973. https://doi.org/10.3390/electronics9111973