Channel Length Biasing for Improving Read Margin of the 8T SRAM at Near Threshold Operation

Abstract

1. Introduction

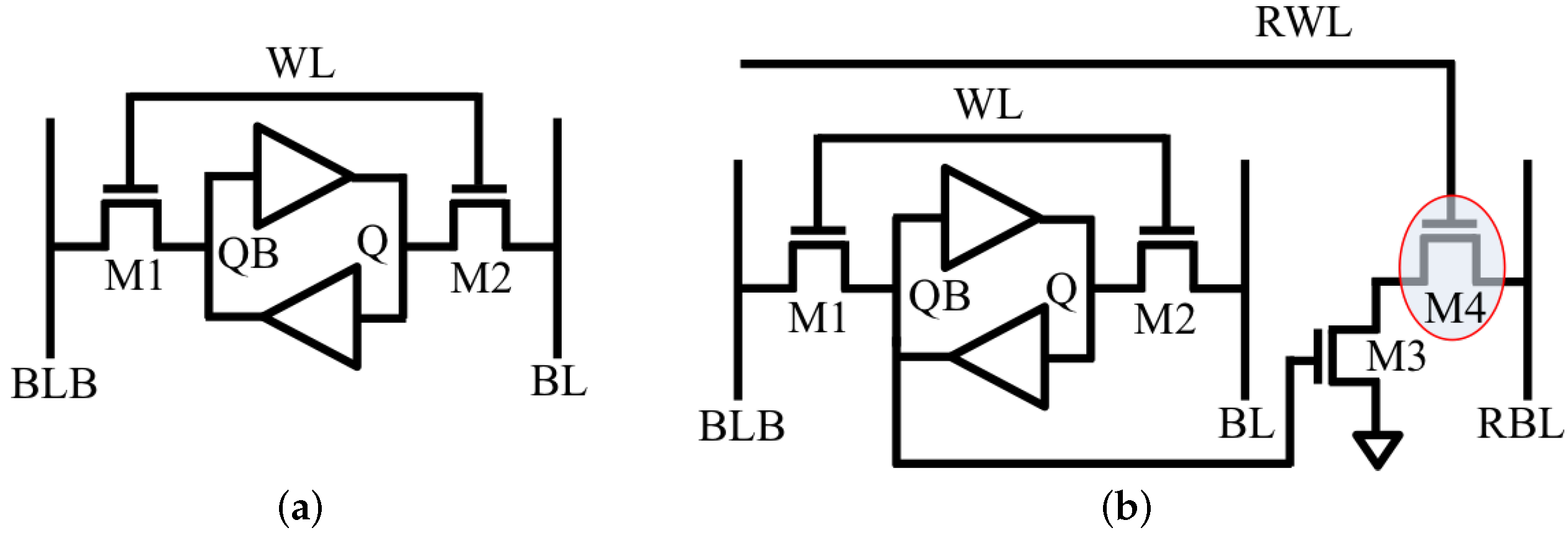

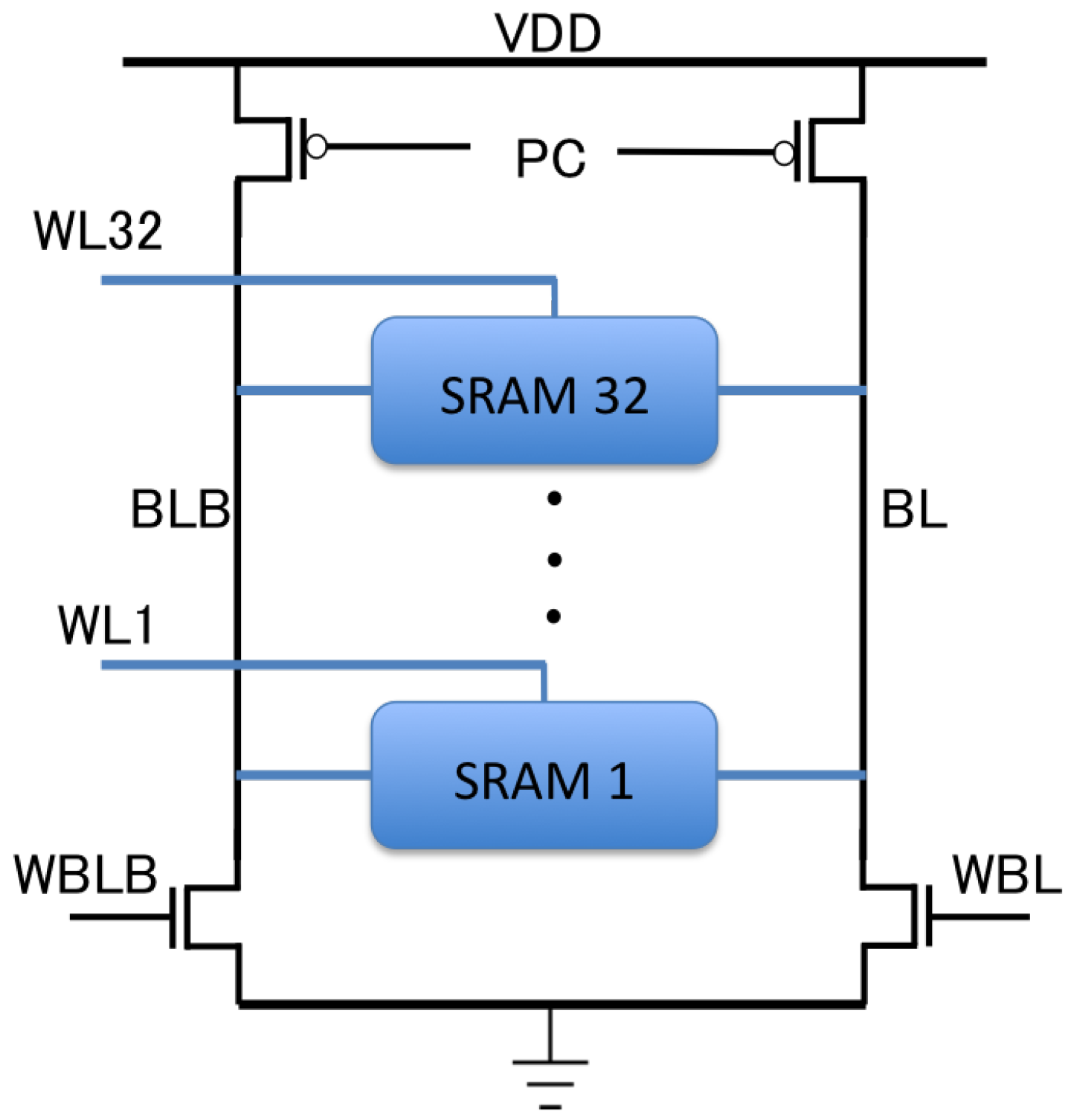

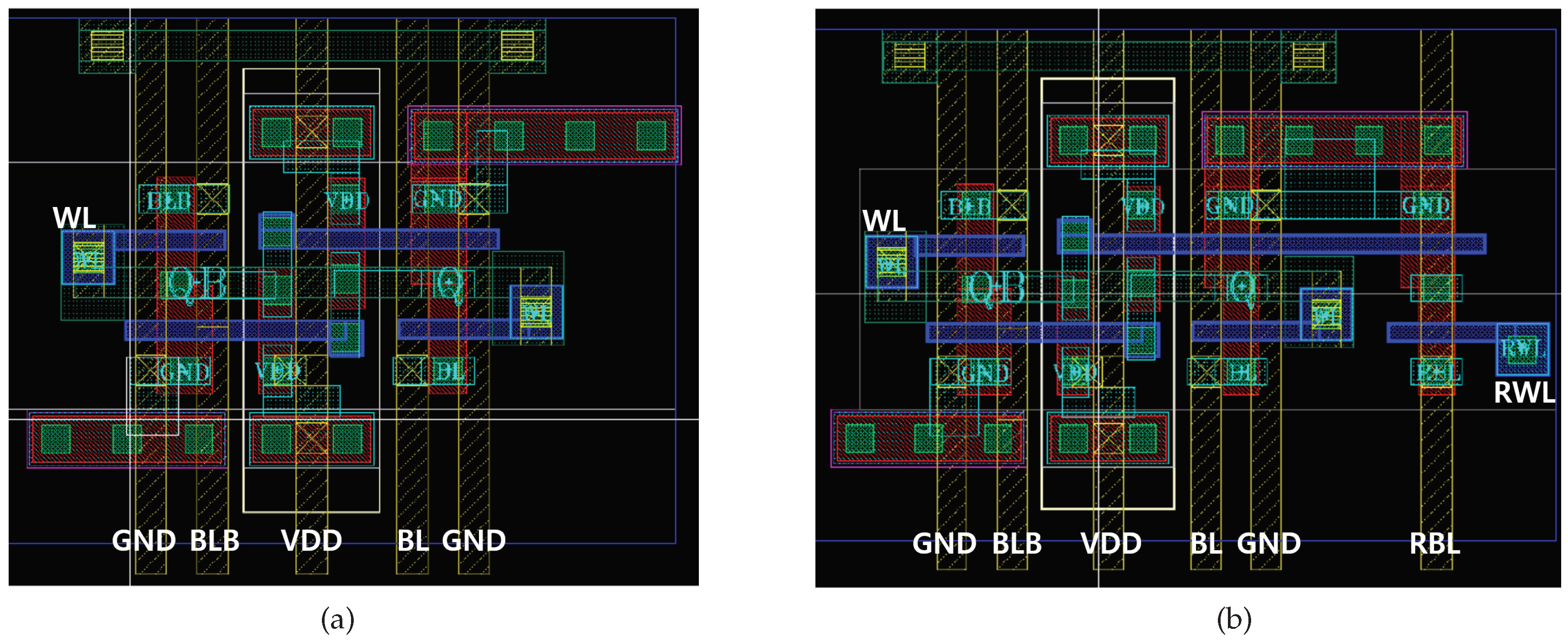

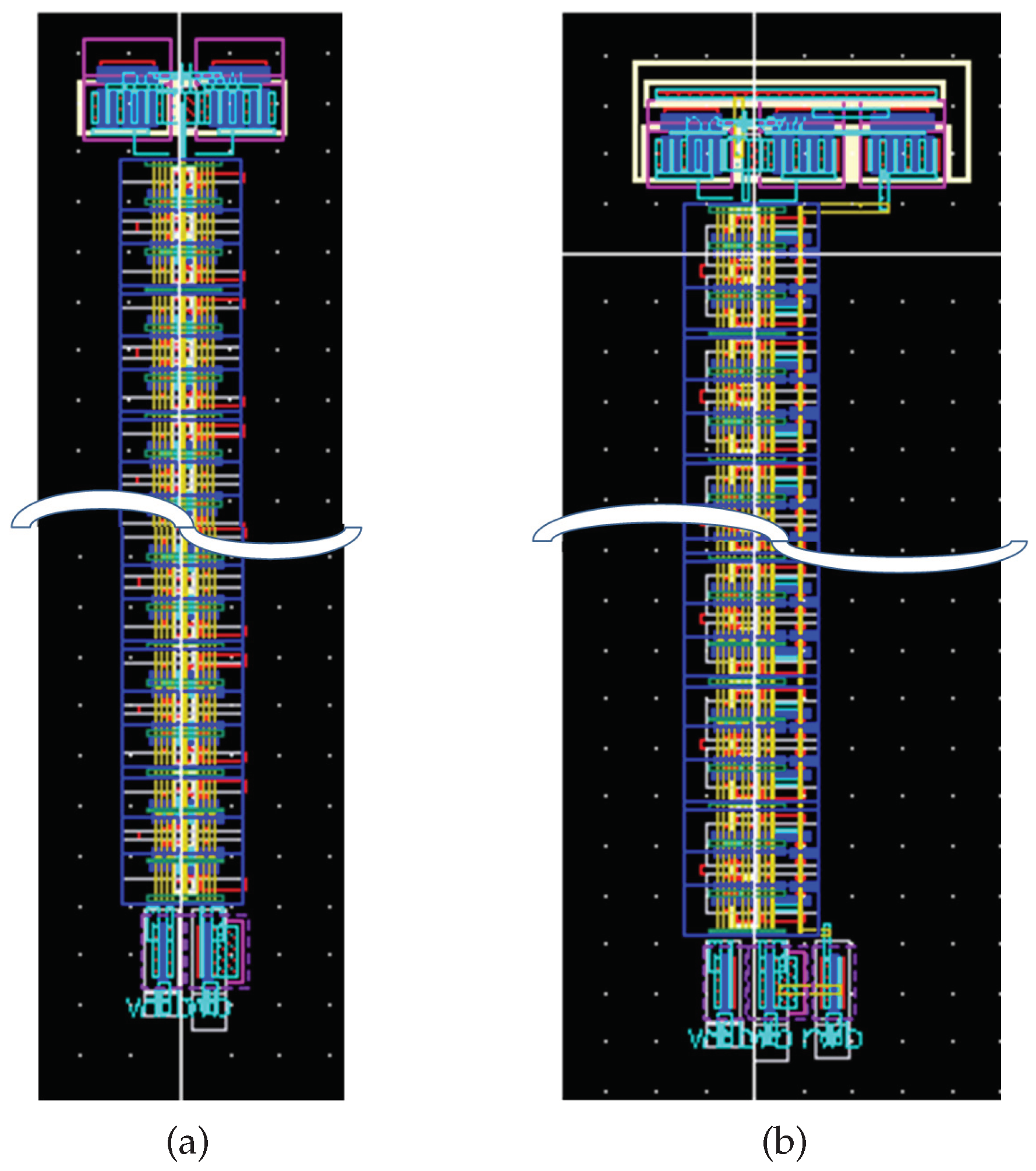

2. Operation and Design of 6T and 8T SRAM

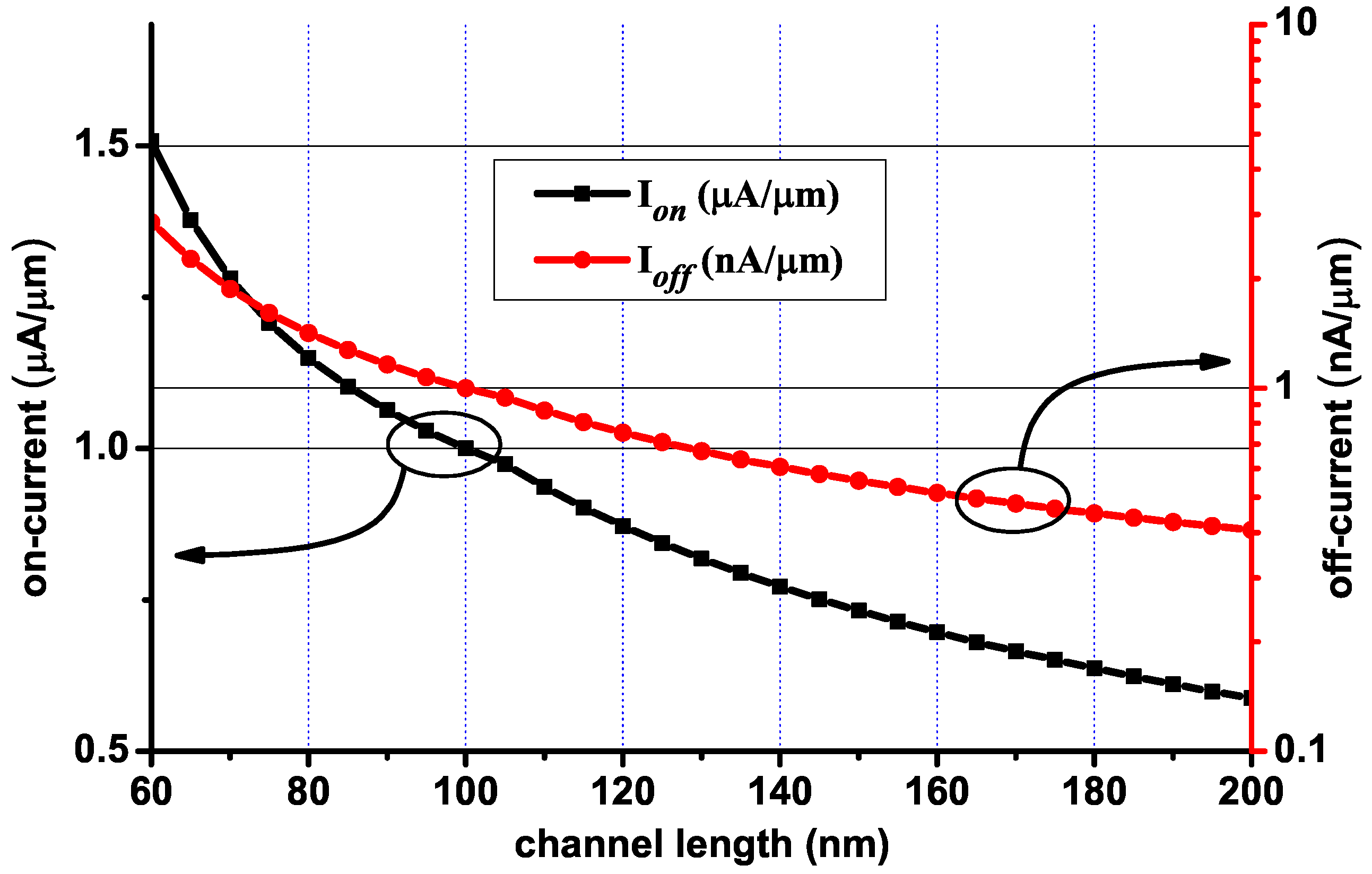

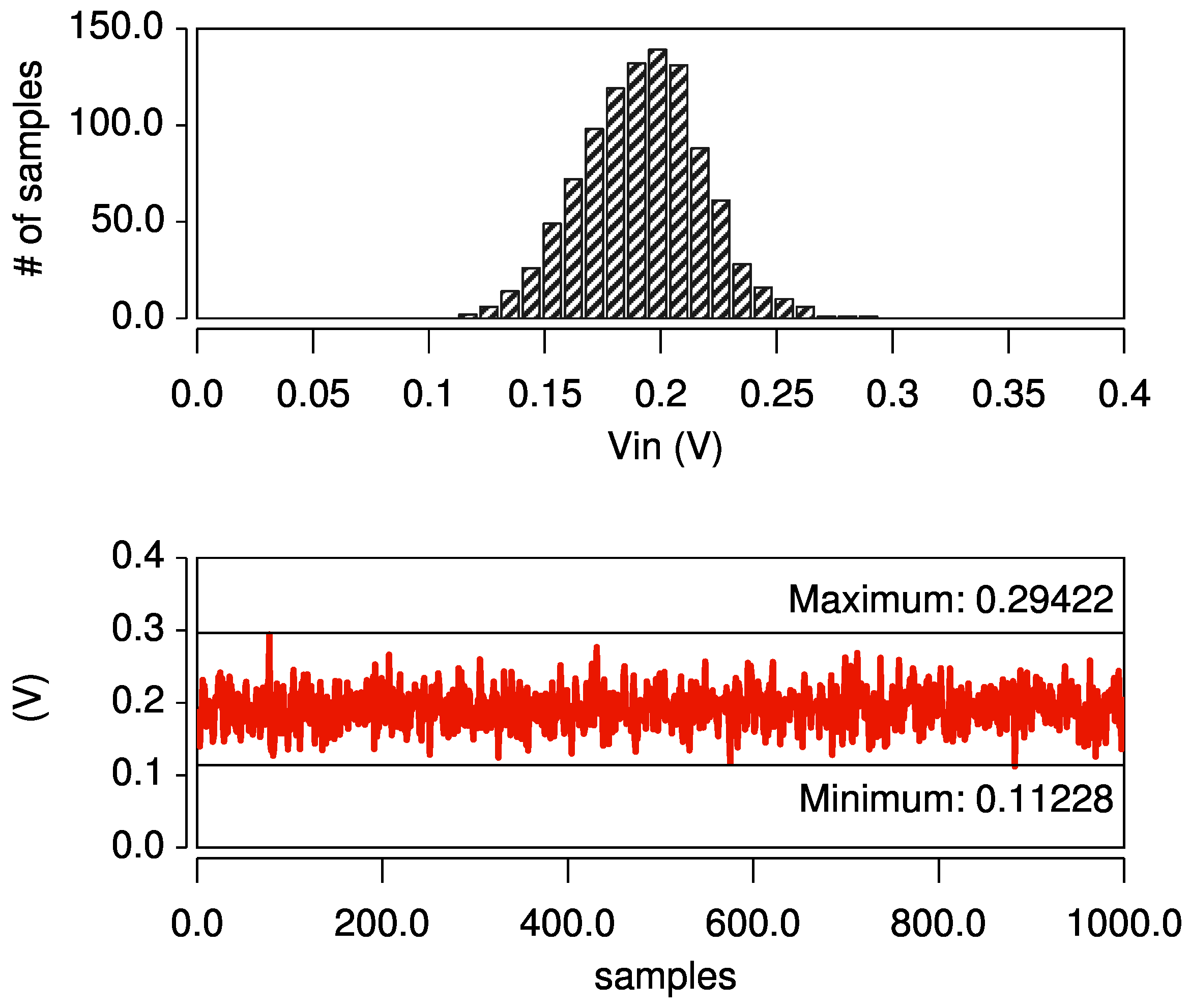

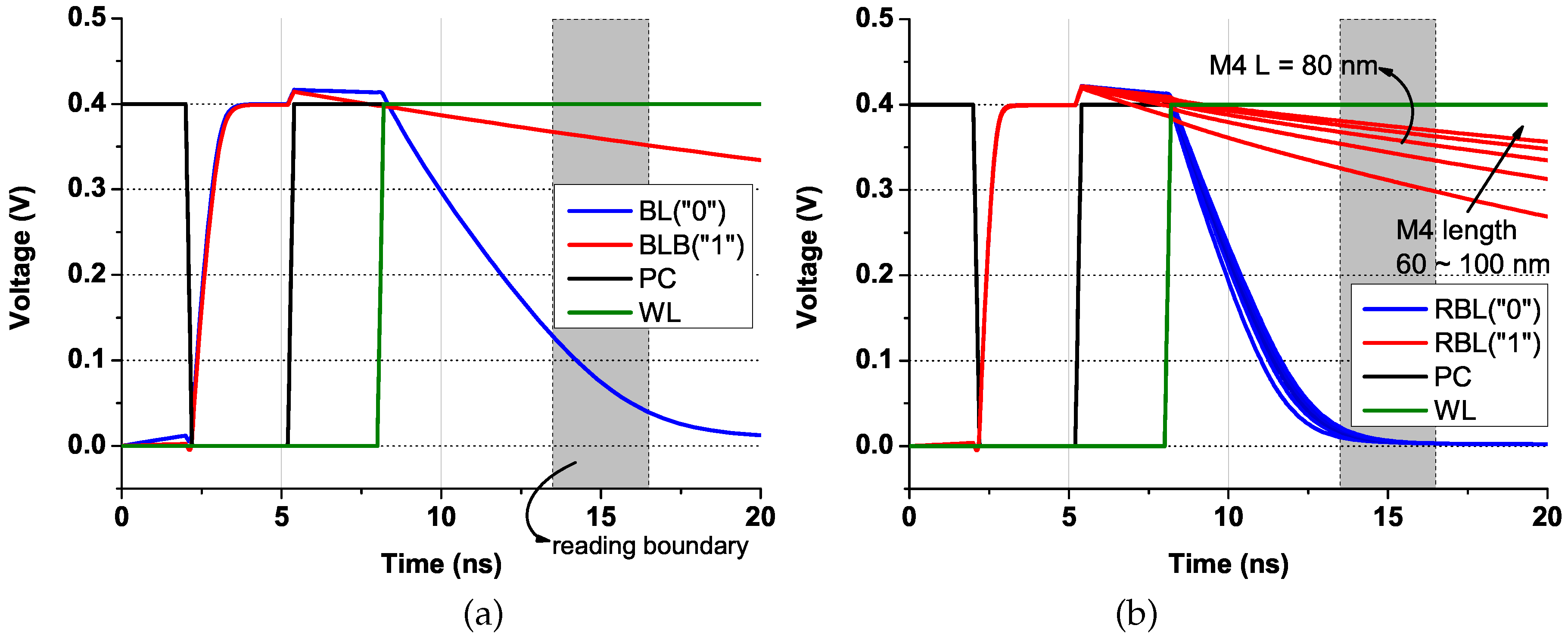

3. Channel Length Biasing for Leakage Reduction

Trip Voltage

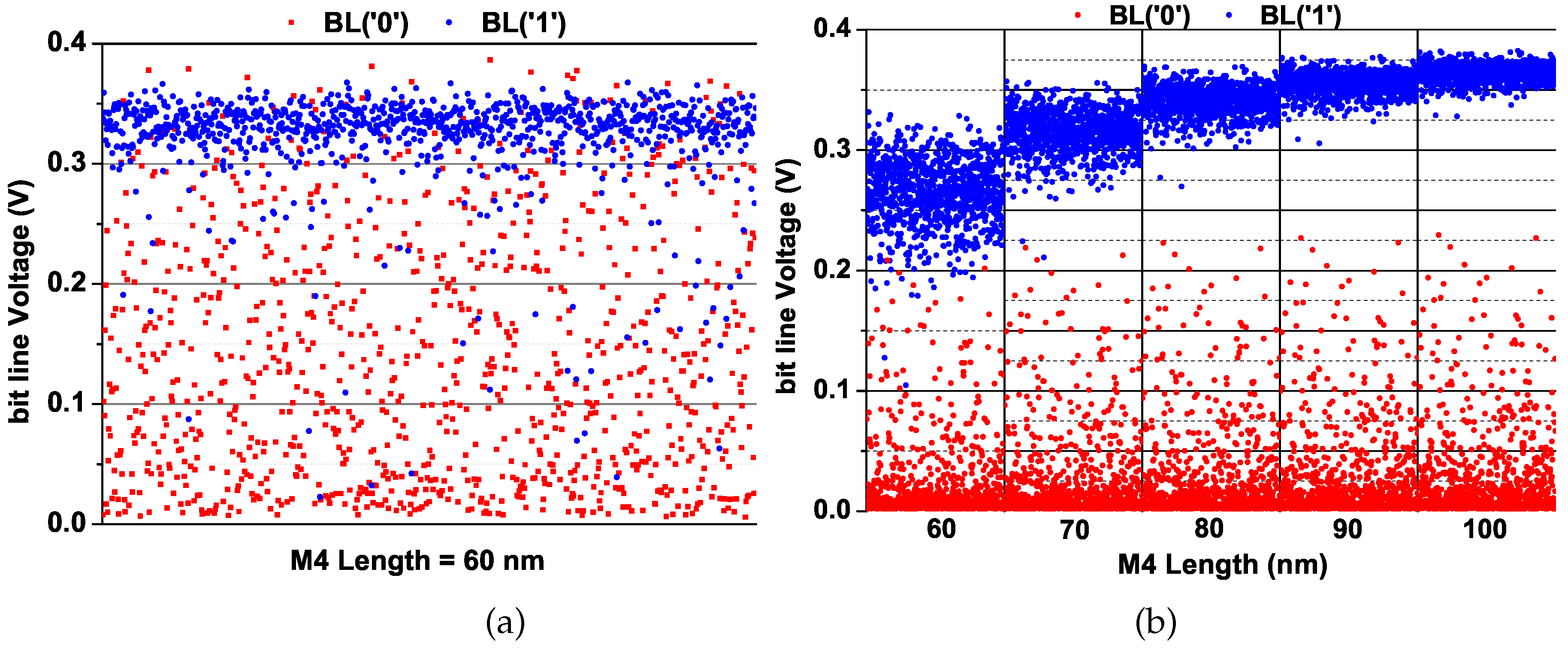

4. Simulation Result

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- De, V.; Borkar, S. Technology and design challenges for low power and high performance. In Proceedings of the 1999 International Symposium on Low Power Electronics and Design (Cat. No.99TH8477), San Diego, CA, USA, 17 August 1999; pp. 163–168. [Google Scholar]

- Zhai, B.; Blaauw, D.; Sylvester, D.; Flautner, K. Theoretical and practical limits of dynamic voltage scaling. In Proceedings of the 41st Design Automation Conference, San Diego, CA, USA, 7–11 July 2004; pp. 868–873. [Google Scholar]

- Zhai, B.; Hanson, S.; Blaauw, D.; Sylvester, D. Analysis and mitigation of variability in subthreshold design. In Proceedings of the 2005 International Symposium on Low Power Electronics and Design, San Diego, CA, USA, 8–10 August 2005; pp. 20–25. [Google Scholar]

- Chang, L.; Nakamura, Y.; Montoye, R.K.; Sawada, J.; Martin, A.K.; Kinoshita, K.; Gebara, F.H.; Agarwal, K.B.; Acharyya, D.J.; Haensch, W.; et al. A 5.3 GHz 8T-SRAM with operation down to 0.41 V in 65 nm CMOS. In Proceedings of the IEEE Symposium on VLSI Circuits, Kyoto, Japan, 14–16 June 2007; pp. 252–253. [Google Scholar]

- Dreslinski, R.G.; Wieckowski, M.; Blaauw, D.; Sylvester, D.; Mudge, T. Near-threshold computing: Reclaiming Moore’s law through energy efficient integrated circuits. Proc. IEEE 2010, 98, 253–266. [Google Scholar] [CrossRef]

- Kaul, H.; Anders, M.; Hsu, S.; Agarwal, A.; Krishnamurthy, R.; Borkar, S. Near-threshold voltage (NTV) design: Opportunities and challenges. In Proceedings of the DAC Design Automation Conference 2012, San Francisco, CA, USA, 3–7 June 2012; pp. 1153–1158. [Google Scholar]

- Chen, G.; Sylvester, D.; Blaauw, D.; Mudge, T. Yield-driven near-threshold SRAM design. IEEE TVLSI Syst. 2010, 18, 1590–1598. [Google Scholar] [CrossRef]

- Jun, J.; Song, J.; Kim, C. A Near-Threshold Voltage Oriented Digital Cell Library for High-Energy Efficiency and Optimized Performance in 65 nm CMOS Process. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 1567–1580. [Google Scholar] [CrossRef]

- Pilo, H.; Barwin, J.; Braceras, G.; Browning, C.; Burns, S.; Gabric, J.; Lamphier, S.; Miller, M.; Roberts, A.; Towler, F. An SRAM design in 65 nm and 45 nm technology nodes featuring read and write-assist circuits to expand operating voltage. In Proceedings of the 2006 Symposium on VLSI Circuits, Honolulu, HI, USA, 15–17 June 2006; pp. 15–16. [Google Scholar]

- Calhoun, B.H.; Chandrakasan, A.P. A 256-kb 65-nm sub-threshold SRAM design for ultra-low-voltage operation. IEEE JSSC 2007, 42, 680–688. [Google Scholar] [CrossRef]

- Kim, T.H.; Liu, J.; Kim, C.H. A voltage scalable 0.26 V, 64 kb 8T SRAM with Vmin lowering techniques and deep sleep mode. IEEE JSSC 2009, 44, 1785–1795. [Google Scholar]

- Verma, N.; Chandrakasan, A.P. A 65 nm 8T Sub-Vt SRAM Employing Sense-Amplifier Redundancy. In Proceedings of the 2007 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 11–15 February 2007; pp. 328–606. [Google Scholar]

- Sinangil, M.E.; Verma, N.; Chandrakasan, A.P. A reconfigurable 65 nm SRAM achieving voltage scalability from 0.25–1.2 V and performance scalability from 20kHz–200MHz. In Proceedings of the ESSCIRC 2008—34th European Solid-State Circuits Conference, Edinburgh, UK, 15–19 September 2008; pp. 282–285. [Google Scholar]

- Do, A.T.; Nguyen, T.Q.; Yeo, K.S.; Kim, T.T. Sensing Margin Enhancement Techniques for Ultra-Low-Voltage SRAMs Utilizing a Bitline-Boosting Current and Equalized Bitline Leakage. IEEE TCAS II Express Briefs 2012, 59, 868–872. [Google Scholar] [CrossRef]

- Chang, I.J.; Kim, J.; Park, S.P.; Roy, K. A 32 kb 10T sub-threshold SRAM array with bit-interleaving and differential read scheme in 90 nm CMOS. IEEE J. Solid-State Circuits 2009, 44, 650–658. [Google Scholar] [CrossRef]

- Grossar, E.; Stucchi, M.; Maex, K.; Dehaene, W. Read stability and write-ability analysis of SRAM cells for nanometer technologies. IEEE J. Solid-State Circuits 2006, 41, 2577–2588. [Google Scholar] [CrossRef]

- Pilo, H.; Barwin, C.; Braceras, G.; Browning, C.; Lamphier, S.; Towler, F. An SRAM Design in 65-nm Technology Node Featuring Read and Write-Assist Circuits to Expand Operating Voltage. IEEE J. Solid-State Circuits 2007, 42, 813–819. [Google Scholar] [CrossRef]

- Yabuuchi, M.; Nii, K.; Tsukamoto, Y.; Ohbayashi, S.; Nakase, Y.; Shinohara, H. A 45 nm 0.6 V cross-point 8T SRAM with negative biased read/write assist. In Proceedings of the 2009 Symposium on VLSI Circuits, Kyoto, Japan, 16–18 June 2009; pp. 158–159. [Google Scholar]

- Zimmer, B.; Toh, S.O.; Vo, H.; Lee, Y.; Thomas, O.; Asanovic, K.; Nikolic, B. SRAM assist techniques for operation in a wide voltage range in 28-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 853–857. [Google Scholar] [CrossRef]

- Karl, E.; Wang, Y.; Ng, Y.; Guo, Z.; Hamzaoglu, F.; Bhattacharya, U.; Zhang, K.; Mistry, K.; Bohr, M. A 4.6 GHz 162 Mb SRAM design in 22 nm tri-gate CMOS technology with integrated read and write assist circuitry. IEEE J. Solid-State Circuits 2012, 48, 150–158. [Google Scholar] [CrossRef]

- Tripathi, T.; Chauhan, D.S.; Singh, S.K. A Novel Approach to Design SRAM Cells for Low Leakage and Improved Stability. J. Low Power Electron. Appl. 2018, 8, 41. [Google Scholar] [CrossRef]

- Arnaud, F.; Boeuf, F.; Salvetti, F.; Lenoble, D.; Wacquant, F.; Regnier, C.; Morin, P.; Emonet, N.; Denis, E.; Oberlin, J.C.; et al. A Functional 0.69 μm2 Embedded 6T-SRAM bit cell for 65 nm CMOS platform. In Proceedings of the 2003 Symposium on VLSI Technology, Kyoto, Japan, 10–12 June 2003; pp. 65–66. [Google Scholar]

- Sakurai, T. Closed-form expressions for interconnection delay, coupling, and crosstalk in VLSIs. IEEE TED 1993, 40, 118–124. [Google Scholar] [CrossRef]

- Constantinescu, C. Trends and challenges in VLSI circuit reliability. IEEE Micro 2003, 23, 14–19. [Google Scholar] [CrossRef]

- Roy, K.; Mukhopadhyay, S.; Mahmoodi-Meimand, H. Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits. Proc. IEEE 2003, 91, 305–327. [Google Scholar] [CrossRef]

- Gupta, P.; Kahng, A.B.; Sharma, P.; Sylvester, D. Gate-length biasing for runtime-leakage control. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2006, 25, 1475–1485. [Google Scholar] [CrossRef]

| Best Leakage Pattern | Worst Leakage Pattern | |||

|---|---|---|---|---|

| 1∼31th | 32th | 1∼31th | 32th | |

| Q | 1 | 1 | 0 | 1 |

| QB | 0 | 0 | 1 | 0 |

| Transistors | Width (nm)/Length (nm) |

|---|---|

| M1 | 120/60 |

| M2 | 120/60 |

| M3 (8T only) | 180/60 |

| M4 (8T only) | 120/60–100 (L varies) |

| Inverter NMOS | 180/60 |

| Inverter PMOS | 120/60 |

| Data | 6T | 8T | 8T | 8T | 8T | 8T |

|---|---|---|---|---|---|---|

| Value | (L = 60 nm) | (L = 70 nm) | (L = 80 nm) | (L = 90 nm) | (L = 100 nm) | |

| ‘0’ | 56.5% | 4.4% | 5.2% | 5.3% | 5.8% | 5.8% |

| ‘1’ | 10.9% | 91.9% | 17.1% | 0.2% | 0.0% | 0.0% |

| average | 33.7% | 48.2% | 11.2% | 2.8% | 2.9% | 2.9% |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chang, I.J.; Kang, Y.; Kim, Y. Channel Length Biasing for Improving Read Margin of the 8T SRAM at Near Threshold Operation. Electronics 2019, 8, 611. https://doi.org/10.3390/electronics8060611

Chang IJ, Kang Y, Kim Y. Channel Length Biasing for Improving Read Margin of the 8T SRAM at Near Threshold Operation. Electronics. 2019; 8(6):611. https://doi.org/10.3390/electronics8060611

Chicago/Turabian StyleChang, Ik Joon, Yesung Kang, and Youngmin Kim. 2019. "Channel Length Biasing for Improving Read Margin of the 8T SRAM at Near Threshold Operation" Electronics 8, no. 6: 611. https://doi.org/10.3390/electronics8060611

APA StyleChang, I. J., Kang, Y., & Kim, Y. (2019). Channel Length Biasing for Improving Read Margin of the 8T SRAM at Near Threshold Operation. Electronics, 8(6), 611. https://doi.org/10.3390/electronics8060611