A 5GS/s 8-bit ADC with Self-Calibration in 0.18 μm SiGe BiCMOS Technology

Abstract

:1. Introduction

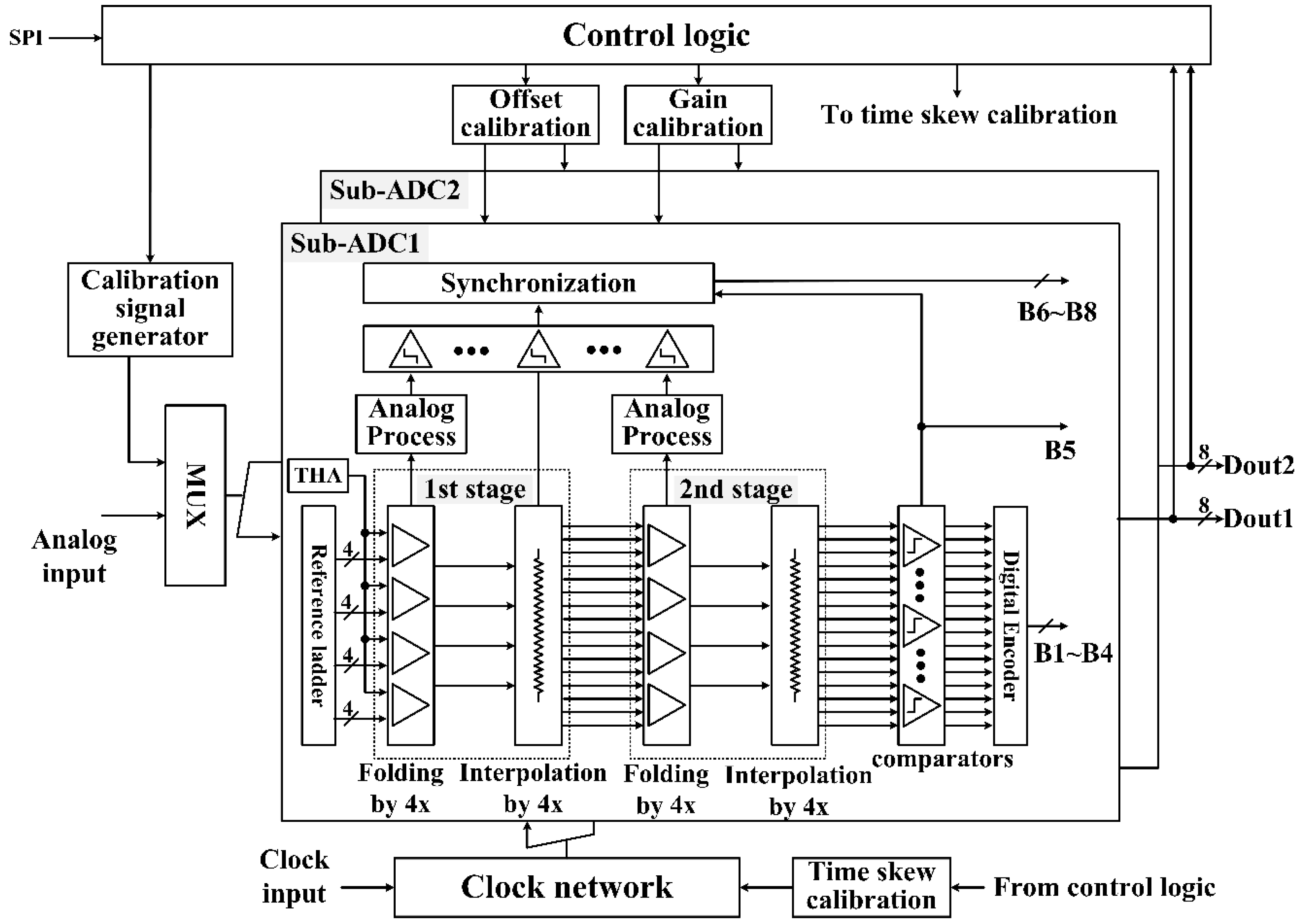

2. Proposed Architecture

3. Circuit Design

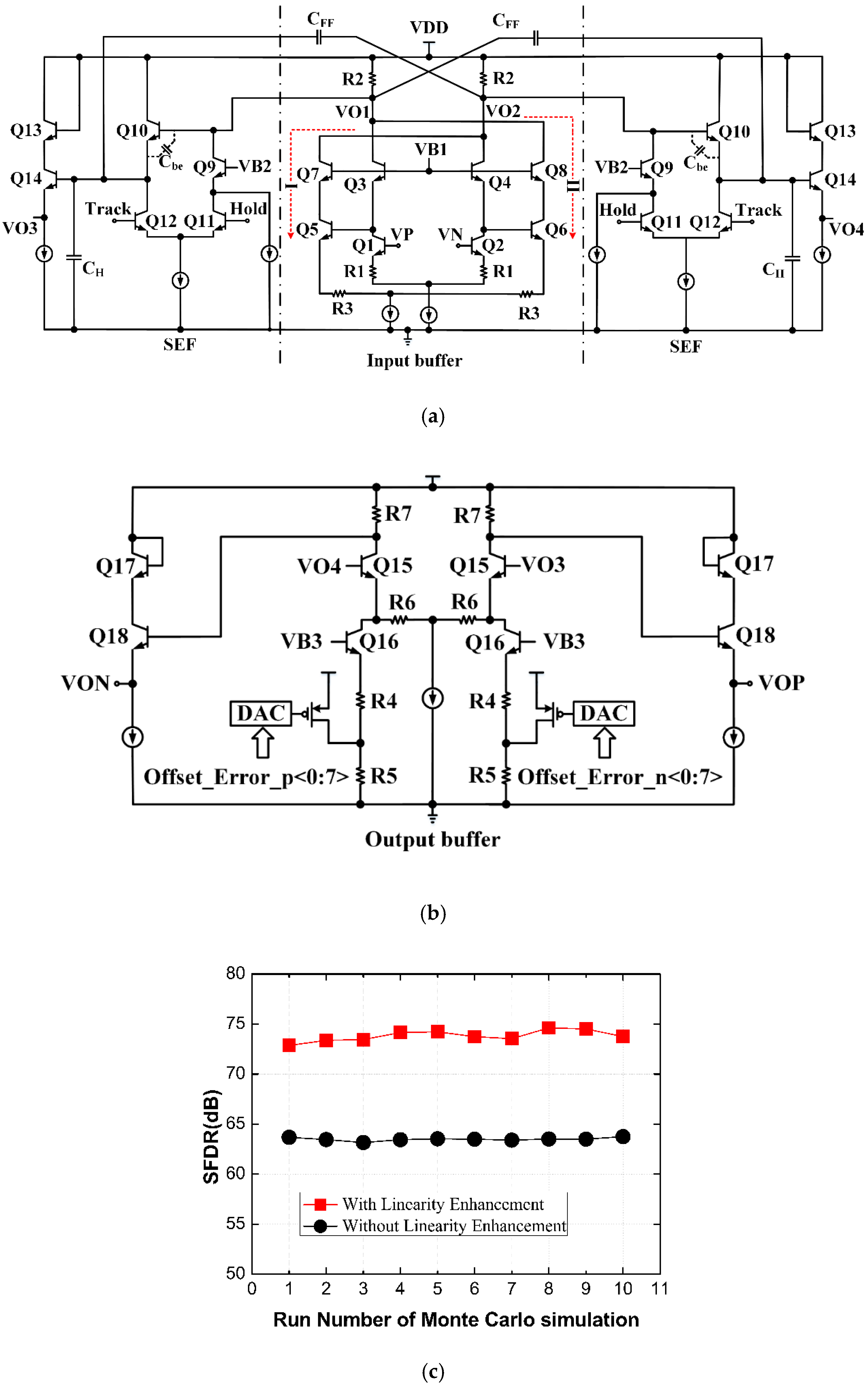

3.1. Track-and-Hold Amplifier

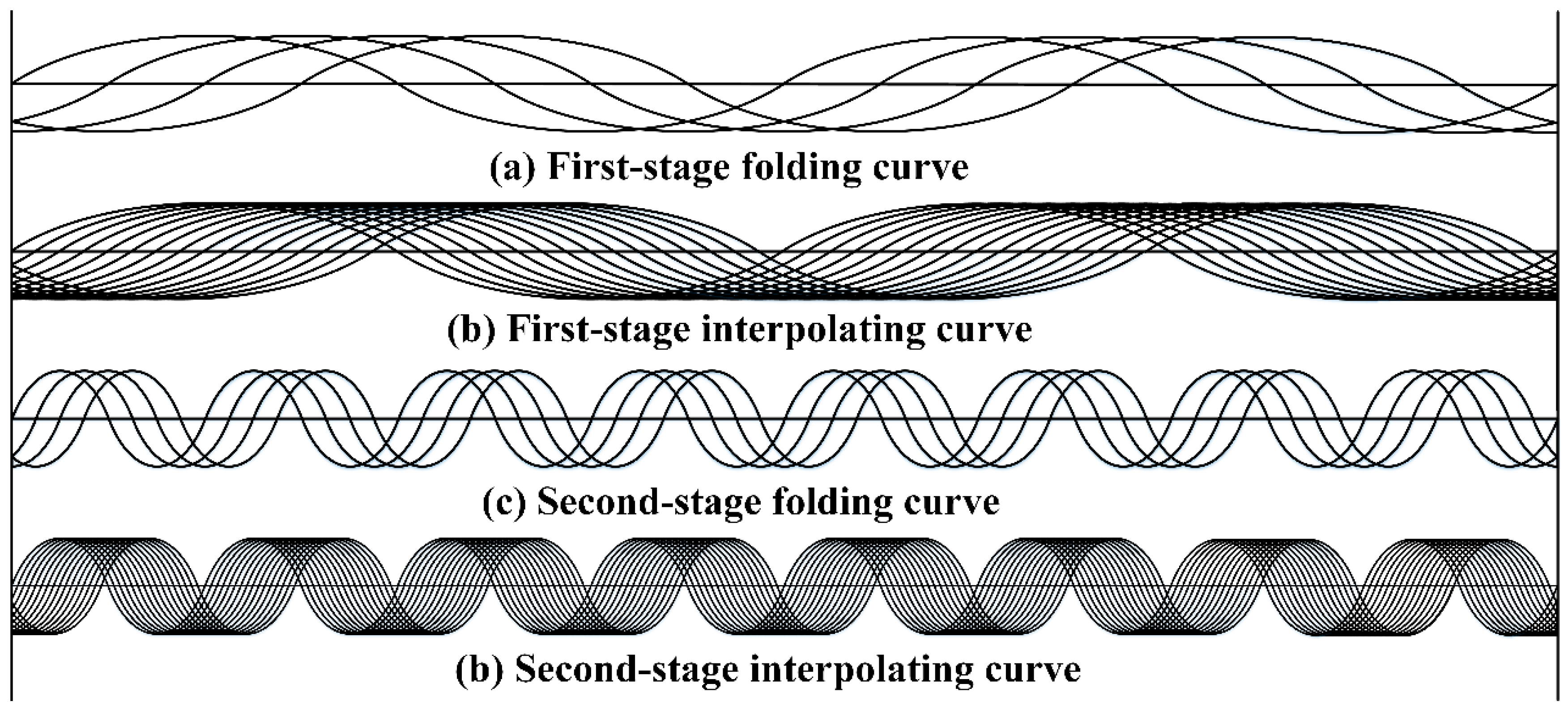

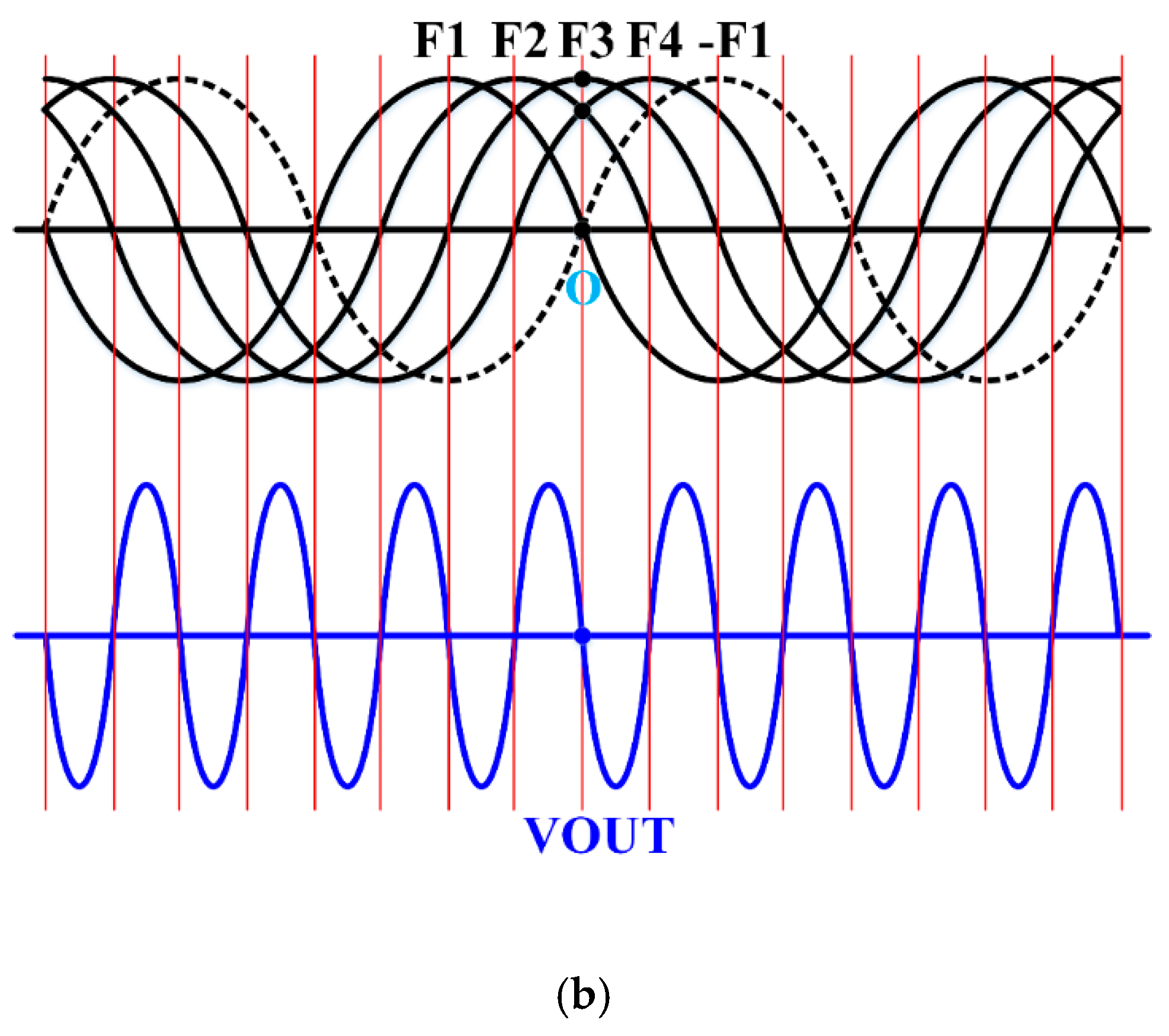

3.2. Folding and Interpolating Circuits

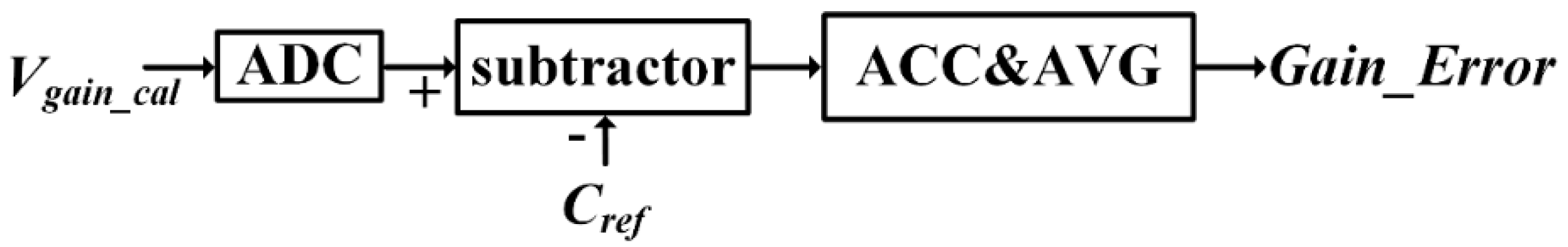

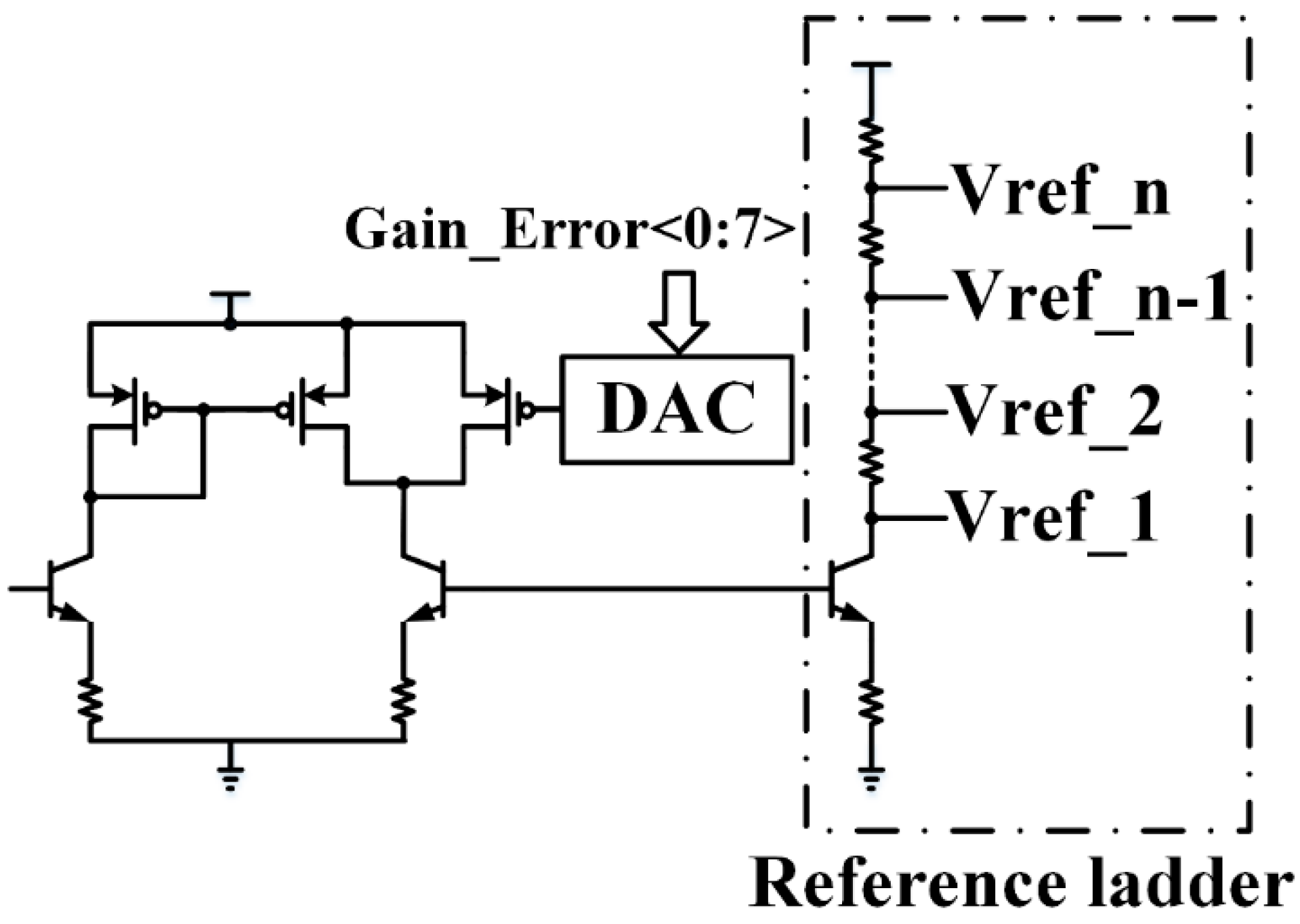

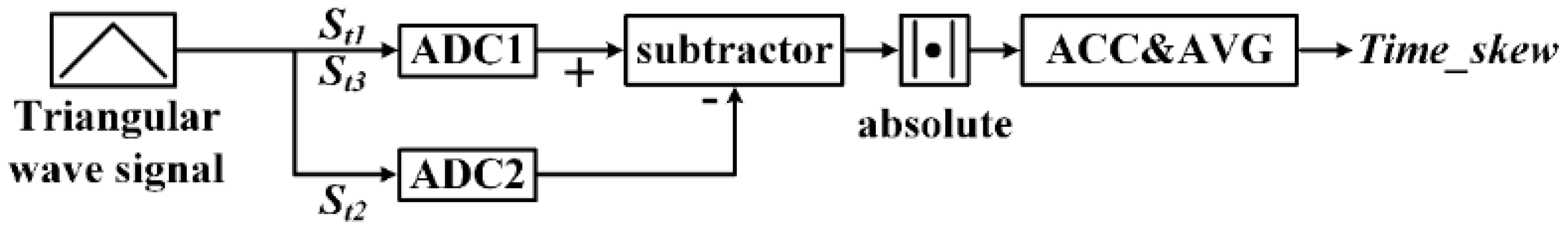

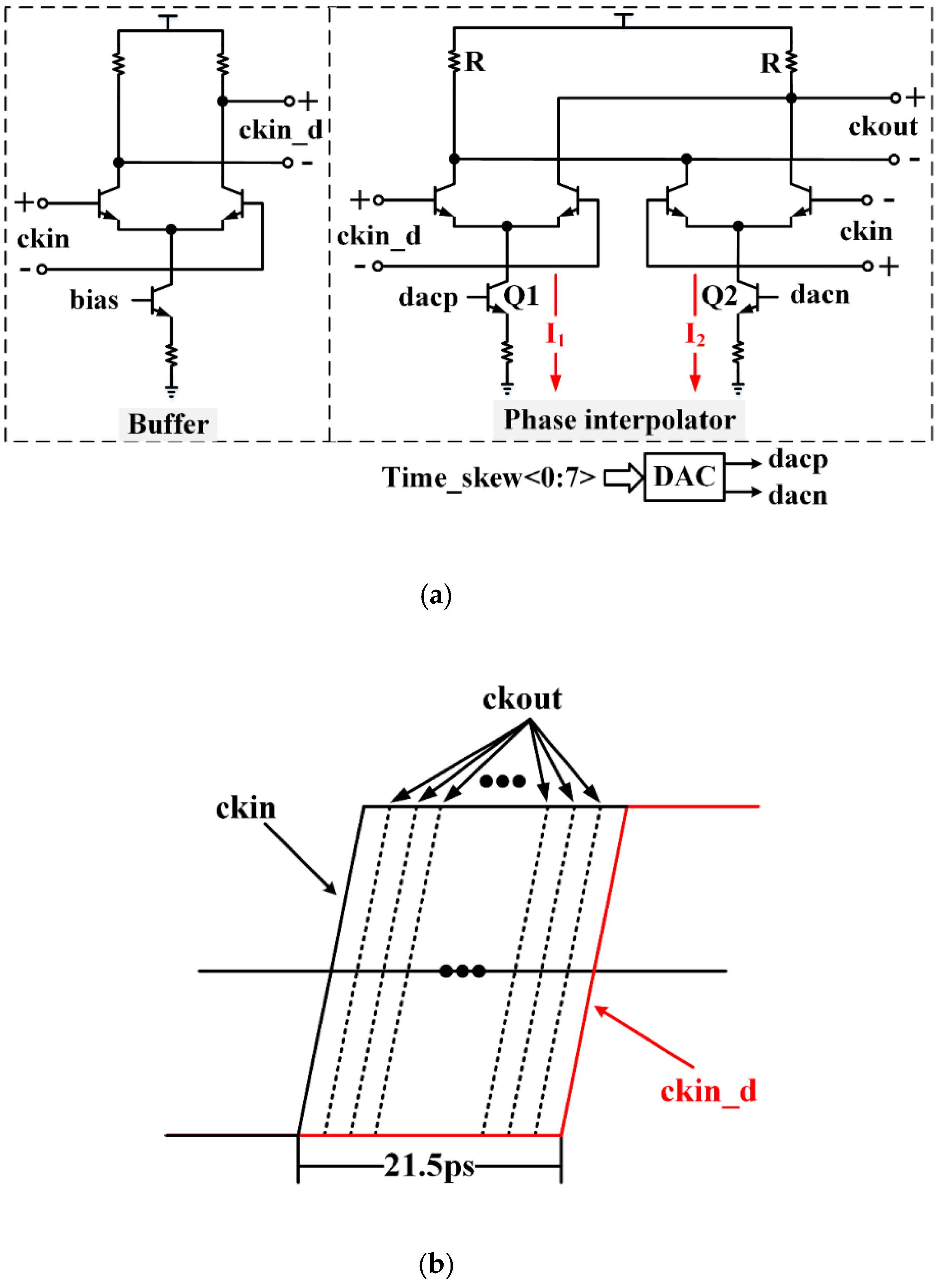

4. Self-Calibration Technique

5. Measured results

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Lee, J.; Weiner, J.; Chen, Y.-K. A 20-GS/s 5-b SiGe ADC for 40-Gb/s Coherent Optical Links. IEEE Trans. Circuits Syst. I 2010, 57, 2665–2674. [Google Scholar] [CrossRef]

- Ritter, P.; Le Tual, S.; Allard, B.; Möller, M. Design Considerations for a 6 Bit 20 GS/s SiGe BiCMOS Flash ADC Without Track-and-Hold. IEEE J. Solid-State Circuits 2014, 49, 1886–1894. [Google Scholar] [CrossRef]

- Du, X.-Q.; Grozing, M.; Buck, M.; Berroth, M. A 40GS/s 4 bit SiGe BiCMOS flash ADC. In Proceedings of the 2017 IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM), Miami, FL, USA, 19–21 October 2017. [Google Scholar]

- Fang, J.; Thirunakkarasu, S.; Yu, X.; Silva-Rivas, F.; Zhang, C.; Singor, F.; Abraham, J. A 5-GS/s 10-b 76-mW Time-Interleaved SAR ADC in 28 nm CMOS. IEEE Trans. Circuits Syst. I 2017, 64, 1–11. [Google Scholar] [CrossRef]

- Kull, L.; Toifl, T.; Schmatz, M.; Francese, P.A.; Menolfi, C.; Braendli, M.; Kossel, M.; Morf, T.; Andersen, T.M.; Leblebici, Y. A 3.1 mW 8b 1.2 GS/s Single-Channel Asynchronous SAR ADC With Alternate Comparators for Enhanced Speed in 32 nm Digital SOI CMOS. IEEE J. Solid-State Circuits 2013, 48, 3049–3058. [Google Scholar] [CrossRef]

- Lin, C.-Y.; Wei, Y.-H.; Lee, T.-C. A 10-bit 2.6-GS/s Time-Interleaved SAR ADC With a Digital-Mixing Timing-Skew Calibration Technique. IEEE J. Solid-State Circuits 2018, 53, 1508–1517. [Google Scholar] [CrossRef]

- Buck, M.; Grozing, M.; Bieg, R.; Digel, J.; Du, X.-Q.; Thomas, P.; Berroth, M.; Epp, M.; Rauscher, J.; Schlumpp, M. A 6-GS/s 9.5-b Single-Core Pipelined Folding-Interpolating ADC With 7.3 ENOB and 52.7-dBc SFDR in the Second Nyquist Band in 0.25-µm SiGe-BiCMOS. IEEE Trans. Microwave Theory Techn. 2017, 65, 414–422. [Google Scholar] [CrossRef]

- Kuo, W.-M.L.; Lu, Y.; Floyd, B.; Haugerud, B.; Sutton, A.; Krithivasan, R.; Cressler, J.; Gaucher, B.; Marshall, P.; Reed, R.; et al. Proton radiation response of monolithic Millimeter-wave transceiver building blocks implemented in 200 GHz SiGe technology. IEEE Trans. Nucl. Sci. 2004, 51, 3781–3787. [Google Scholar]

- Fleetwood, Z.E.; Kenyon, E.W.; Lourenco, N.E.; Jain, S.; Zhang, E.X.; England, T.D.; Cressler, J.D.; Schrimpf, R.D.; Fleetwood, D.M. Advanced SiGe BiCMOS Technology for Multi-Mrad Electronic Systems. IEEE Trans. Device Mater. Relib. 2014, 14, 844–848. [Google Scholar] [CrossRef]

- Petrosyants, K.O.; Kozhukhov, M.V. Physical TCAD Model for Proton Radiation Effects in SiGe HBTs. IEEE Trans. Nucl. Sci. 2016, 63, 2016–2021. [Google Scholar] [CrossRef]

- Leroy, M.R.; Raman, S.; Chu, M.; Kim, J.-W.; Guo, J.-R.; Zhou, K.; You, C.; Clarke, R.; Goda, B.; McDonald, J.F.; et al. High-Speed Reconfigurable Circuits for Multirate Systems in SiGe HBT Technology. Proc. IEEE 2015, 103, 1181–1196. [Google Scholar] [CrossRef]

- Lal, D.; Ali, A.M.A.; Ricketts, D.S. Analysis and Comparison of High-Resolution GS/s Samplers in Advanced BiCMOS and CMOS. IEEE Trans. Circuits and Sys. II Express Briefs 2018, 65, 532–536. [Google Scholar] [CrossRef]

- Jiang, F.; Wu, D.; Zhou, L.; Wu, J.; Jin, Z.; Liu, X. An 8-bit 1 GS/s folding and interpolating ADC with a base-4 architecture. Analog Integr. Circuits Signal Process. 2013, 76, 139–146. [Google Scholar] [CrossRef]

- Li, Y.; Sanchez-Sinencio, E. A wide input bandwidth 7-bit 300-msample/s folding and current-mode interpolating adc. IEEE J. Solid-State Circuits 2003, 38, 1405–1410. [Google Scholar]

- Halder, S.; Gustat, H.; Scheytt, C. An 8 Bit 10 GS/s 2Vpp Track and Hold Amplifier in SiGe BiCMOS Technology. In Proceedings of the 2010 Proceedings of ESSCIRC, Montreux, Switzerland, 19–21 September 2006. [Google Scholar]

- Avitabile, G.; Cascella, D.; Cannone, F.; Coviello, G. Low distortion input buffer for high resolution GS/s rate track-and-hold amplifiers. Electron. Lett. 2012, 48, 755. [Google Scholar] [CrossRef]

- Fung, Q.; Fomani, A.A.; Feng, Y.; Ng, W.T. Design of a 2-GSample/s Track-and-Hold Amplifier implemented in a 60-GHz SiGe BiCMOS Process. In Proceedings of the 2007 IEEE Conference on Electron Devices and Solid-State Circuits, Tainan, Taiwan, 20–22 December 2007. [Google Scholar]

- Wu, D.; Jiang, F.; Zhou, L.; Wu, J.; Huang, Y.; Jin, Z.; Liu, X. A 4GS/s 8bit ADC fabricated in 0.35µm SiGe BiCMOS technology. In Proceedings of the 2013 IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM), Bordeaux, France, 30 September–3 Octomber 2013. [Google Scholar]

- Taft, R.; Menkus, C.; Tursi, M.; Hidri, O.; Pons, V. A 1.8-V 1.6-GSample/s 8-b self-calibrating folding ADC with 7.26 ENOB at Nyquist frequency. IEEE J. Solid-State Circuits 2004, 39, 2107–2115. [Google Scholar] [CrossRef]

- Van de Grift, R.; Rutten, I.W.J.M.; van der Veen, M. An 8-bit video ADC incorporating folding and interpolation techniques. IEEE J. Solid-State Circuits 1987, 22, 944–953. [Google Scholar] [CrossRef]

- Vessal, F.; Salama, C. An 8-bit 2-Gsample/s folding-interpolating analog-to-digital converter in SiGe technology. IEEE J. Solid-State Circuits 2004, 39, 238–241. [Google Scholar] [CrossRef]

- Jiang, F.; Wu, D.; Zhou, L.; Huang, Y.; Wu, J.; Jin, Z.; Liu, X. A wideband calibration-free 1.5-GS/s 8-bit analog-to-digital converter with low latency. Analog Integr Circ Sig Process 2014, 81, 341–348. [Google Scholar] [CrossRef]

- Vorenkamp, P.; Roovers, R. A 12-b, 60-MSample/s cascaded folding and interpolating ADC. IEEE J. Solid-State Circuits 1997, 32, 1876–1886. [Google Scholar] [CrossRef]

- Razzaghi, A.; Tam, S.-W.; Kalkhoran, P.; Wang, Y.; Kuan, C.-Y.; Nissim, B.; Vu, L.D.; Chang, M.-C.F. A single-channel 10b 1GS/s ADC with 1-cycle latency using pipelined cascaded folding. In Proceedings of the 2008 IEEE Bipolar/BiCMOS Circuits and Technology Meeting, Monteray, CA, USA, 13–15 October 2008. [Google Scholar]

- Nakajima, Y.; Sakaguchi, A.; Ohkido, T.; Kato, N.; Matsumoto, T.; Yotsuyanagi, M. A Background Self-Calibrated 6b 2.7 GS/s ADC With Cascade-Calibrated Folding-Interpolating Architecture. IEEE J. Solid-State Circuits 2010, 45, 707–718. [Google Scholar] [CrossRef]

- Miki, T.; Ozeki, T.; Naka, J.-I. A 2-GS/s 8-bit Time-Interleaved SAR ADC for Millimeter-Wave Pulsed Radar Baseband SoC. IEEE J. Solid-State Circuits 2017, 52, 2712–2720. [Google Scholar] [CrossRef]

- Kundu, S.; Alpman, E.; Lu, J.H.-L.; Lakdawala, H.; Paramesh, J.; Jung, B.; Zur, S.; Gordon, E. A 1.2 V 2.64 GS/s 8 bit 39 mW Skew-Tolerant Time-interleaved SAR ADC in 40 nm Digital LP CMOS for 60 GHz WLAN. IEEE Trans. Circuits Syst. I 2015, 62, 1929–1939. [Google Scholar] [CrossRef]

- Hsu, C.-C.; Huang, F.-C.; Shih, C.-Y.; Huang, C.-C.; Lin, Y.-H.; Lee, C.-C.; Razavi, B. An 11b 800MS/s Time-Interleaved ADC with Digital Background Calibration. In Proceedings of the 2007 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, San Francisco, CA, USA, 11–15 February 2007. [Google Scholar]

- Doris, K.; Janssen, E.; Nani, C.; Zanikopoulos, A.; Van Der Weide, G. A 480 mW 2.6 GS/s 10b Time-Interleaved ADC With 48.5 dB SNDR up to Nyquist in 65 nm CMOS. IEEE J. Solid-State Circuits 2011, 46, 2821–2833. [Google Scholar] [CrossRef]

- Kertis, R.A.; Humble, J.S.; Daun-Lindberg, M.A.; Philpott, R.A.; Fritz, K.E.; Schwab, D.J.; Prairie, J.F.; Gilbert, B.K.; Daniel, E.S. A 20 GS/s 5-Bit SiGe BiCMOS Dual-Nyquist Flash ADC With Sampling Capability up to 35 GS/s Featuring Offset Corrected Exclusive-Or Comparators. IEEE J. Solid-State Circuits 2009, 44, 2295–2311. [Google Scholar] [CrossRef]

- El-Chammas, M.; Murmann, B. A 12-GS/s 81-mW 5-bit Time-Interleaved Flash ADC With Background Timing Skew Calibration. IEEE J. Solid-State Circuits 2011, 46, 838–847. [Google Scholar] [CrossRef]

- Agazzi, O.E.; Hueda, M.R.; Crivelli, D.E.; Carrer, H.S.; Nazemi, A.; Luna, G.; Ramos, F.; Lopez, R.; Grace, C.; Kobeissy, B.; et al. A 90 nm CMOS DSP MLSD Transceiver With Integrated AFE for Electronic Dispersion Compensation of Multimode Optical Fibers at 10 Gb/s. IEEE J. Solid-State Circuits 2008, 43, 2939–2957. [Google Scholar] [CrossRef]

- Chan, B.; Oyama, B.; Monier, C.; Gutierrez-Aitken, A. An Ultra-Wideband 7-Bit 5-Gsps ADC Implemented in Submicron InP HBT Technology. IEEE J. Solid-State Circuits 2008, 43, 2187–2193. [Google Scholar] [CrossRef]

| Parameter | [1] | [8] | [11] | [33] | This work |

|---|---|---|---|---|---|

| Technology | 0.25 µm SiGe | 0.35 µm SiGe | 47 GHz SiGe | 0.8 µm InP | 0.18 µm SiGe |

| Architecture | F&I | TI F&I | F&I | F&I | TI F&I |

| Sample frequency (GS/s) | 6 | 4 | 2 | 5 | 5 |

| Resolution (bits) | 9.5 | 8 | 8 | 7 | 8 |

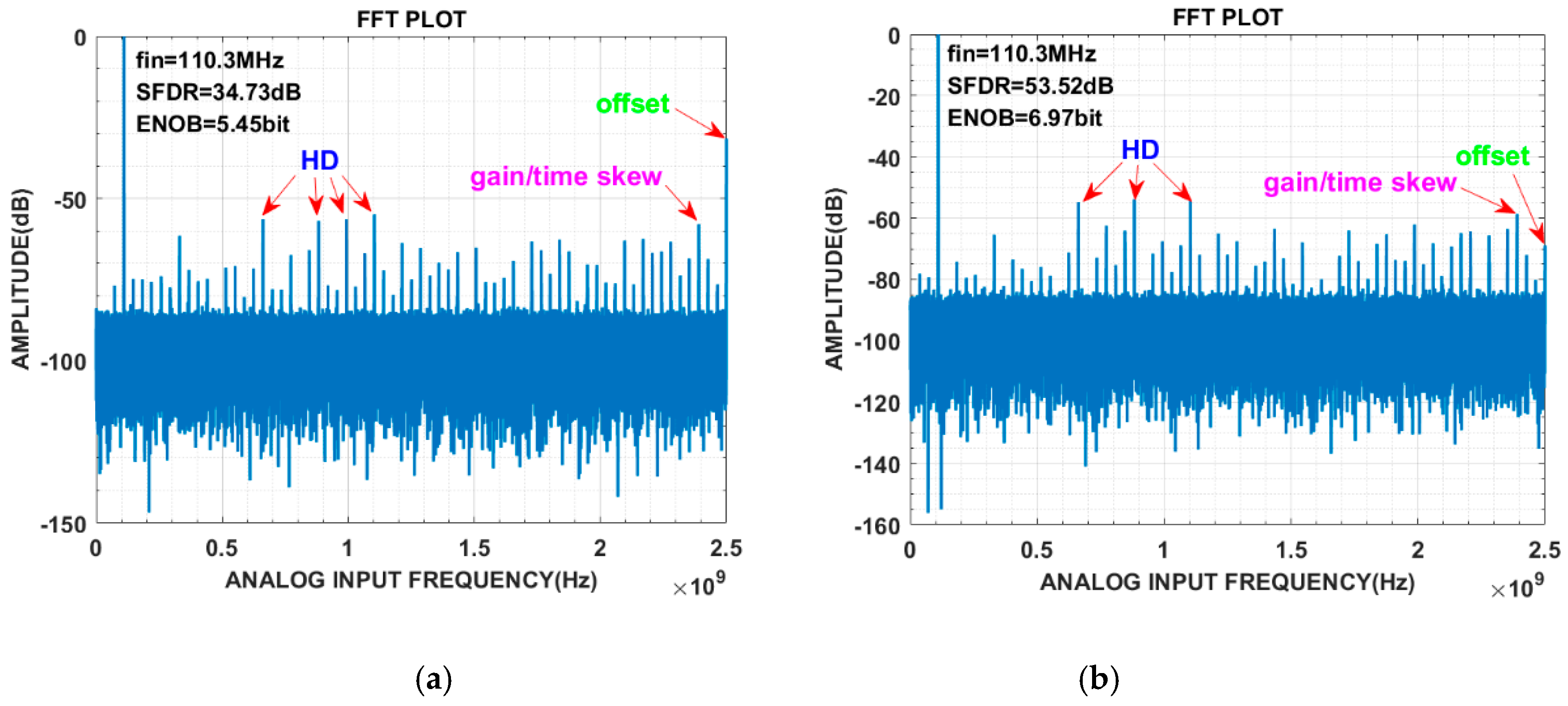

| ENOB (bits) @Nyquist frequency | 7.3 | 5.5 | 6.2 | 5.7 | 5.8 |

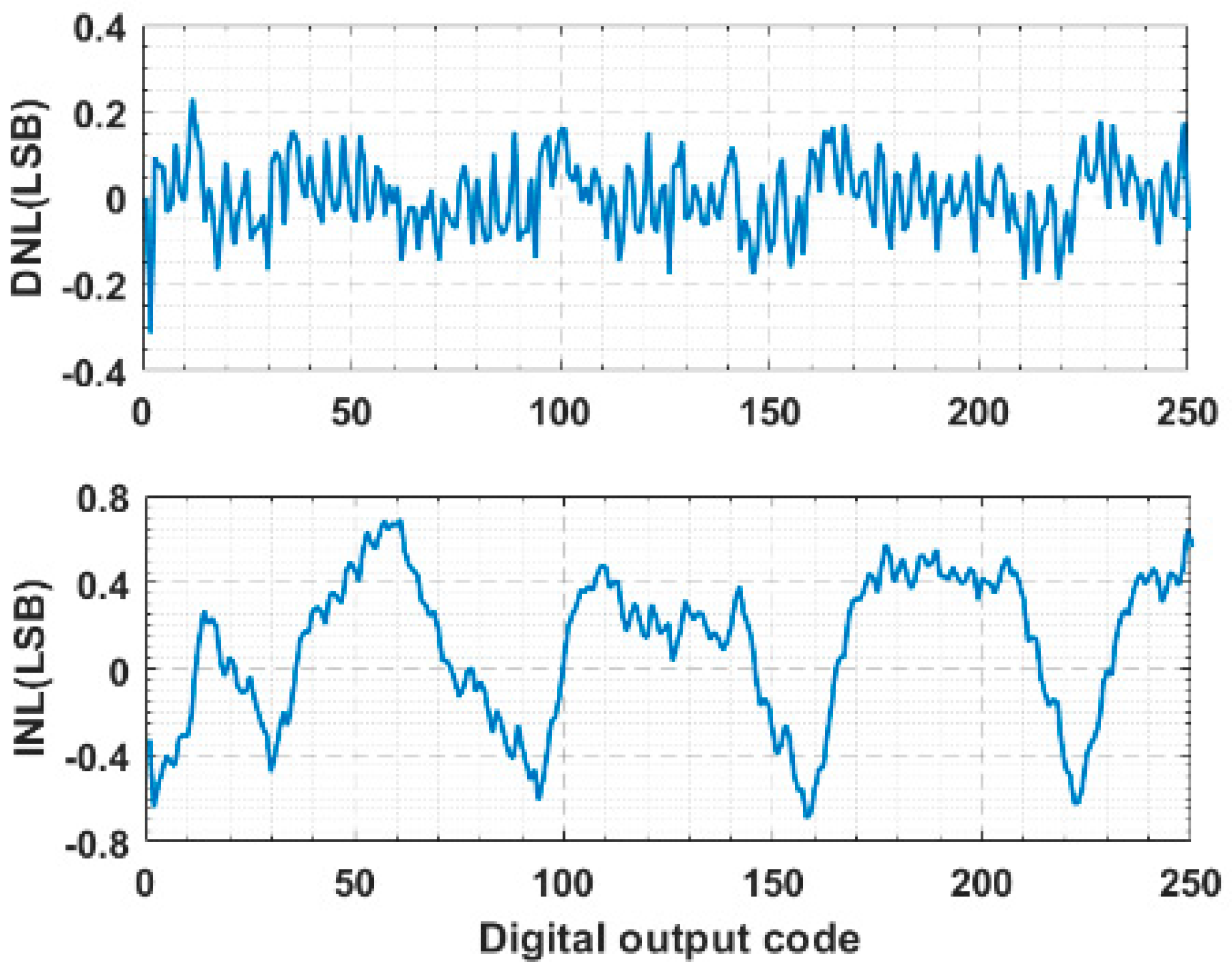

| DNL/INL (LSB) | 1.2/3.5 | 0.3/0.8 | 0.5/1.0 | N.A. | 0.31/0.68 |

| Core power (W) | 10.2 | 3.0 | 3 | 8.4 | 2.8 |

| FoM (pJ/conv.step) 1 | 10.8 | 16.5 | 12 | 32 | 10 |

| Calibration | no | yes | no | no | yes |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, D.; Luan, J.; Guo, X.; Zhou, L.; Wu, D.; Liu, H.; Ding, H.; Wu, J.; Liu, X. A 5GS/s 8-bit ADC with Self-Calibration in 0.18 μm SiGe BiCMOS Technology. Electronics 2019, 8, 253. https://doi.org/10.3390/electronics8020253

Wang D, Luan J, Guo X, Zhou L, Wu D, Liu H, Ding H, Wu J, Liu X. A 5GS/s 8-bit ADC with Self-Calibration in 0.18 μm SiGe BiCMOS Technology. Electronics. 2019; 8(2):253. https://doi.org/10.3390/electronics8020253

Chicago/Turabian StyleWang, Dong, Jian Luan, Xuan Guo, Lei Zhou, Danyu Wu, Huasen Liu, Hao Ding, Jin Wu, and Xinyu Liu. 2019. "A 5GS/s 8-bit ADC with Self-Calibration in 0.18 μm SiGe BiCMOS Technology" Electronics 8, no. 2: 253. https://doi.org/10.3390/electronics8020253

APA StyleWang, D., Luan, J., Guo, X., Zhou, L., Wu, D., Liu, H., Ding, H., Wu, J., & Liu, X. (2019). A 5GS/s 8-bit ADC with Self-Calibration in 0.18 μm SiGe BiCMOS Technology. Electronics, 8(2), 253. https://doi.org/10.3390/electronics8020253