Low Cost Autonomous Lock-In Amplifier for Resistance/Capacitance Sensor Measurements

Abstract

:1. Introduction

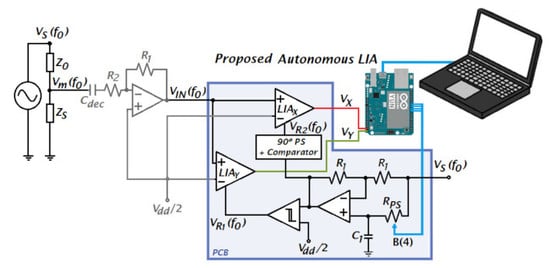

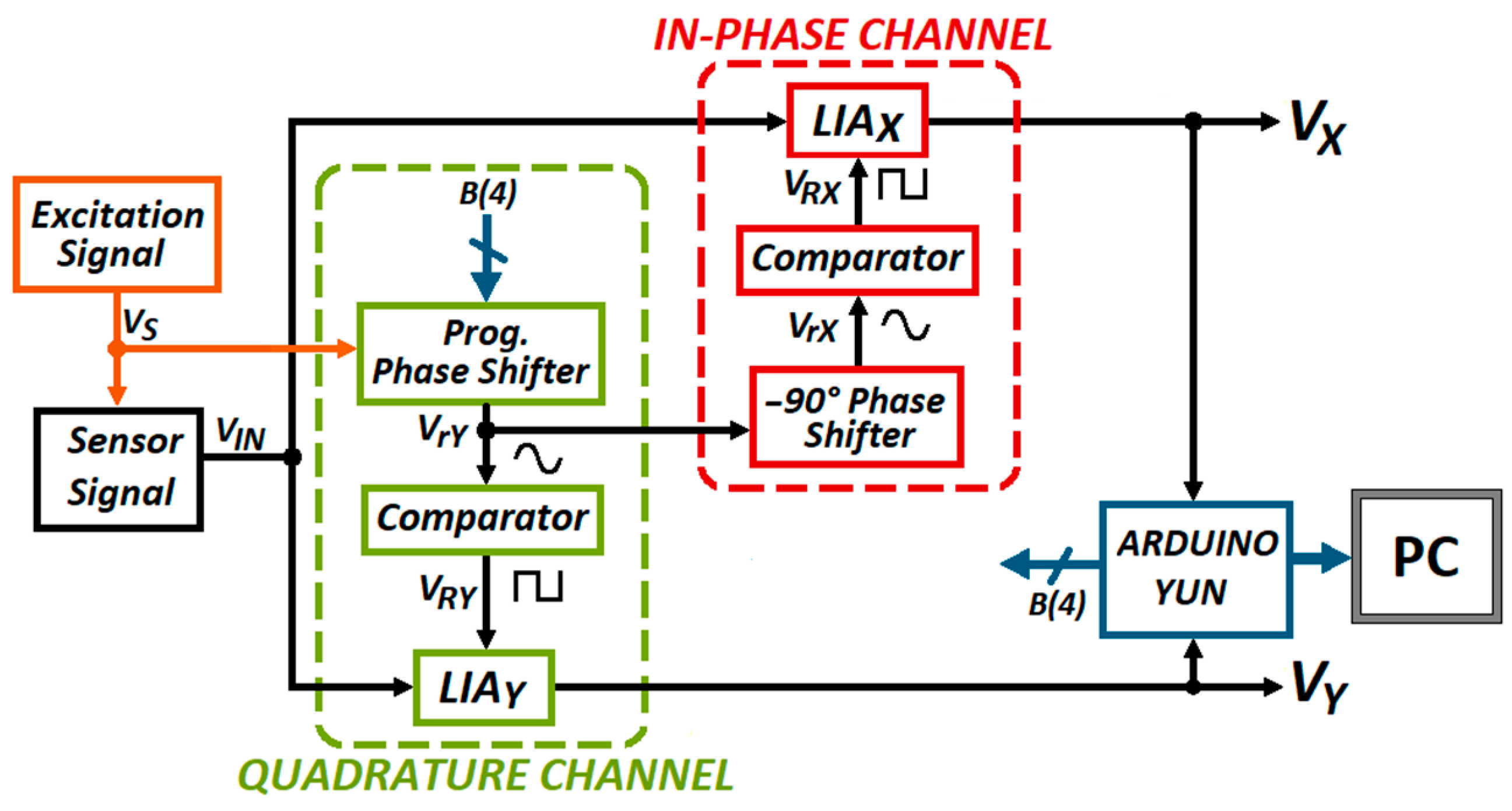

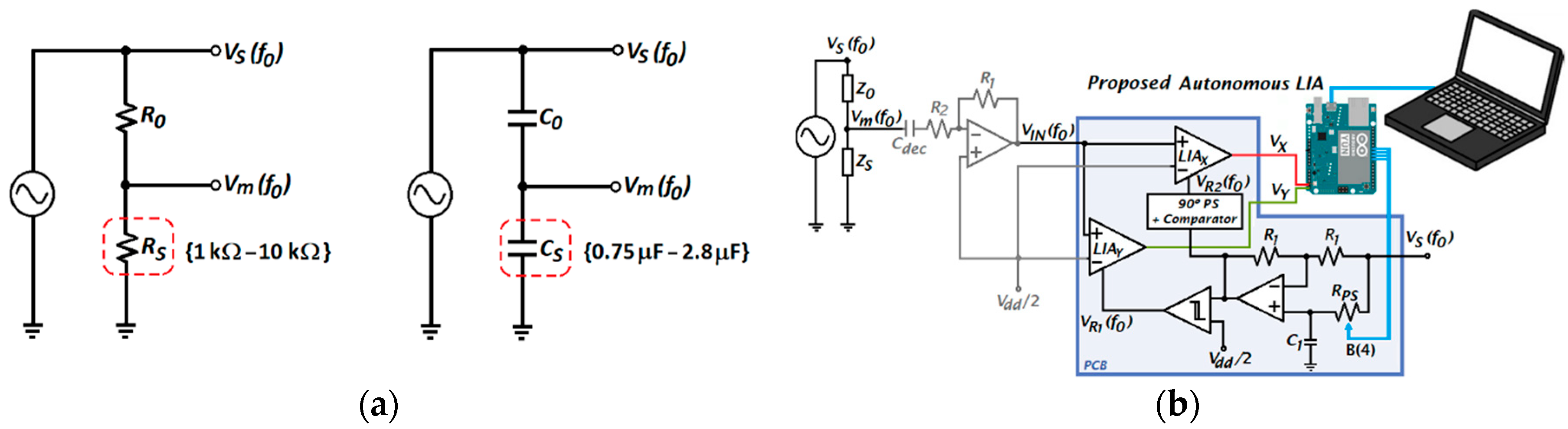

2. Proposed Lock-In Architecture

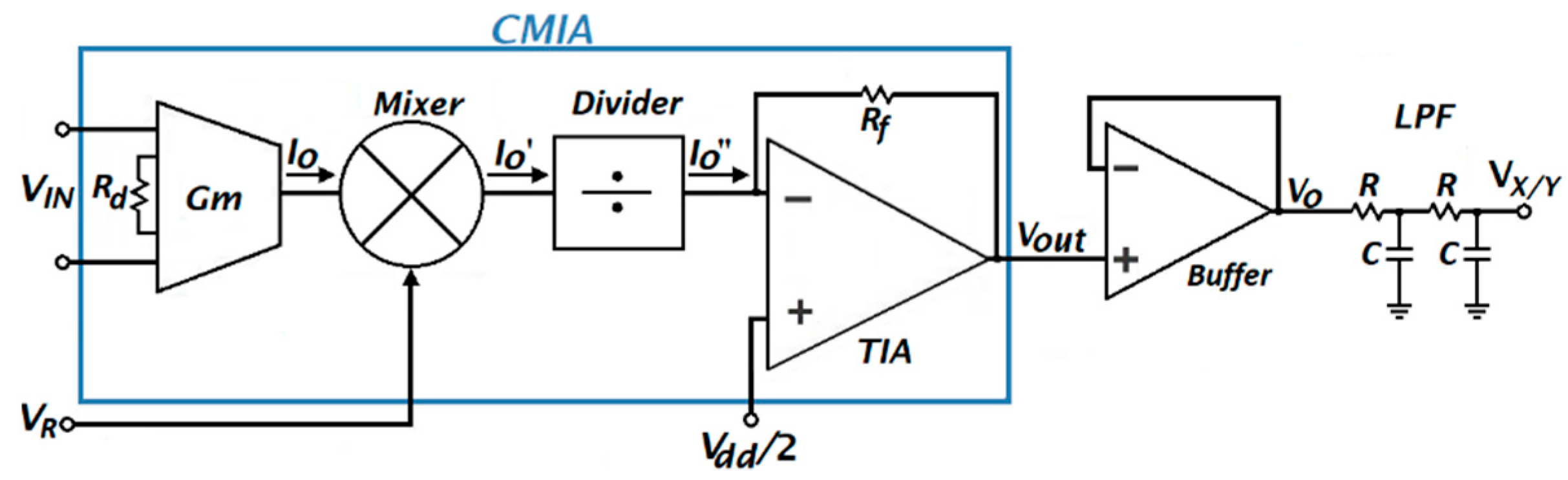

2.1. Lock-In Amplifier

- Transconductor: The input stage consists of a source degenerated differential pair with a negative feedback gm-boosting circuit as shown in Figure 3a. M1 transistors work as source followers, buffering the input signal to the degeneration resistor Rd. Thus, the VIN signal is converted into current (IAC = VIN/Rd) in a linear way and copied out by loading the A nodes with the output mirror branches with cascode transistors to improve the current copy, resulting in the IO signal.

- Mixer: The phase-sensitive detection is performed in the current domain using a class AB current follower; the direction of the current IO is controlled by the square reference signal VR connected to the cascode transistors which act as switches. The fully rectified output current is I’O = (−1)VR ∙ IO, with VR = (0,1).

- Current Divider: To provide gain programmability to the CMIA, a 3-bit current divider based on an R-2R ladder implemented with PMOS transistors in the triode region was used, achieving a highly linear current-division [35], according to:

- Transimpedance Amplifier: A single stage differential amplifier with a feedback resistor Rf = 100 kΩ converts back the signal into voltage domain. A compensation capacitor CC = 500 fF is used to ensure stability. The transfer function for the complete CMIA is:

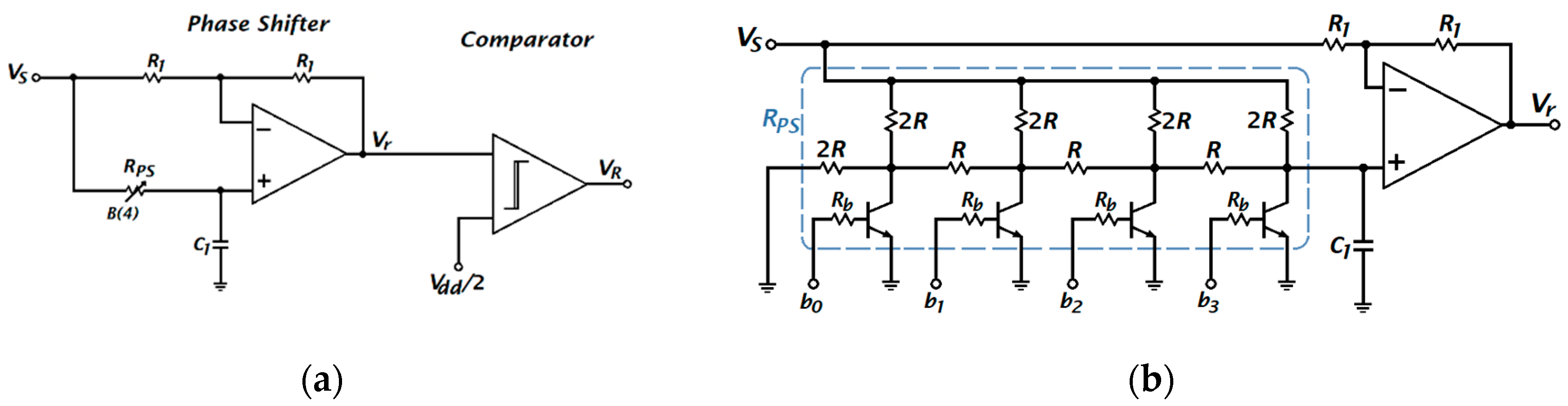

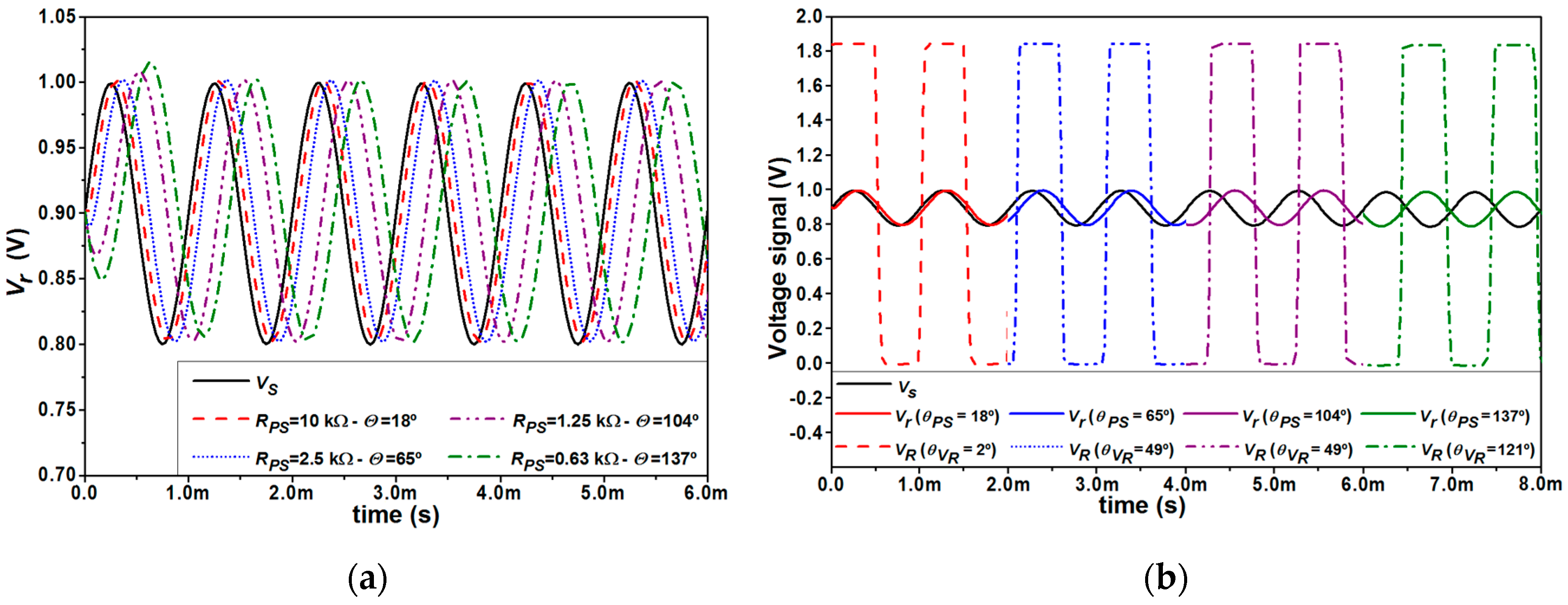

2.2. Phase Shifter

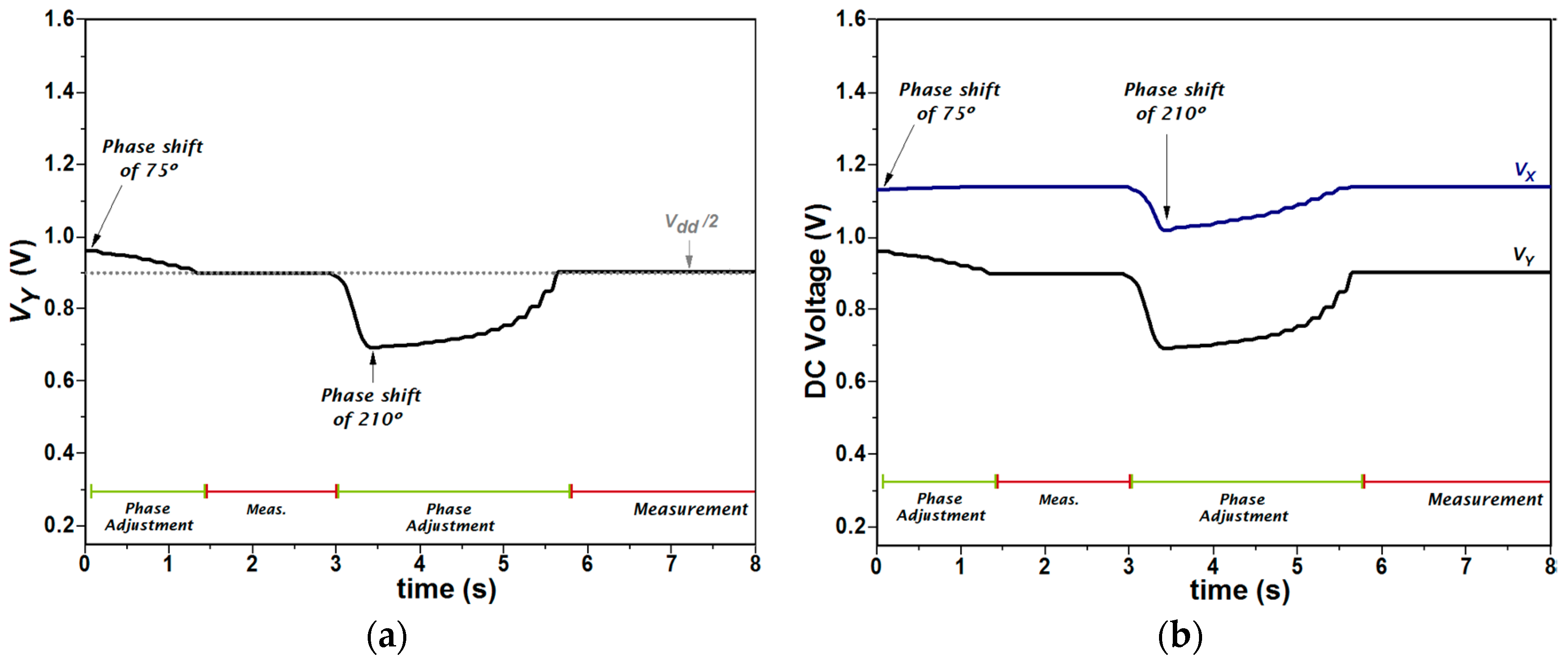

2.3. Phase Alignment and Data Transmission Interface

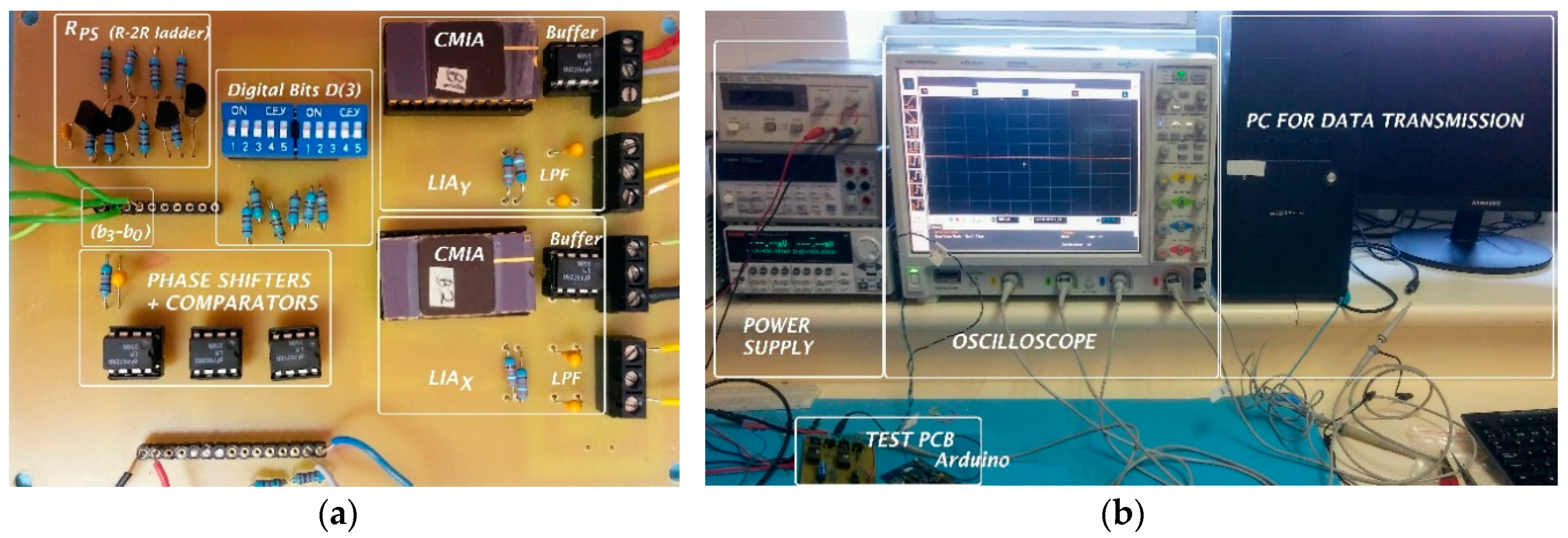

3. Experimental Results

3.1. Autonomous Lock-In Performance

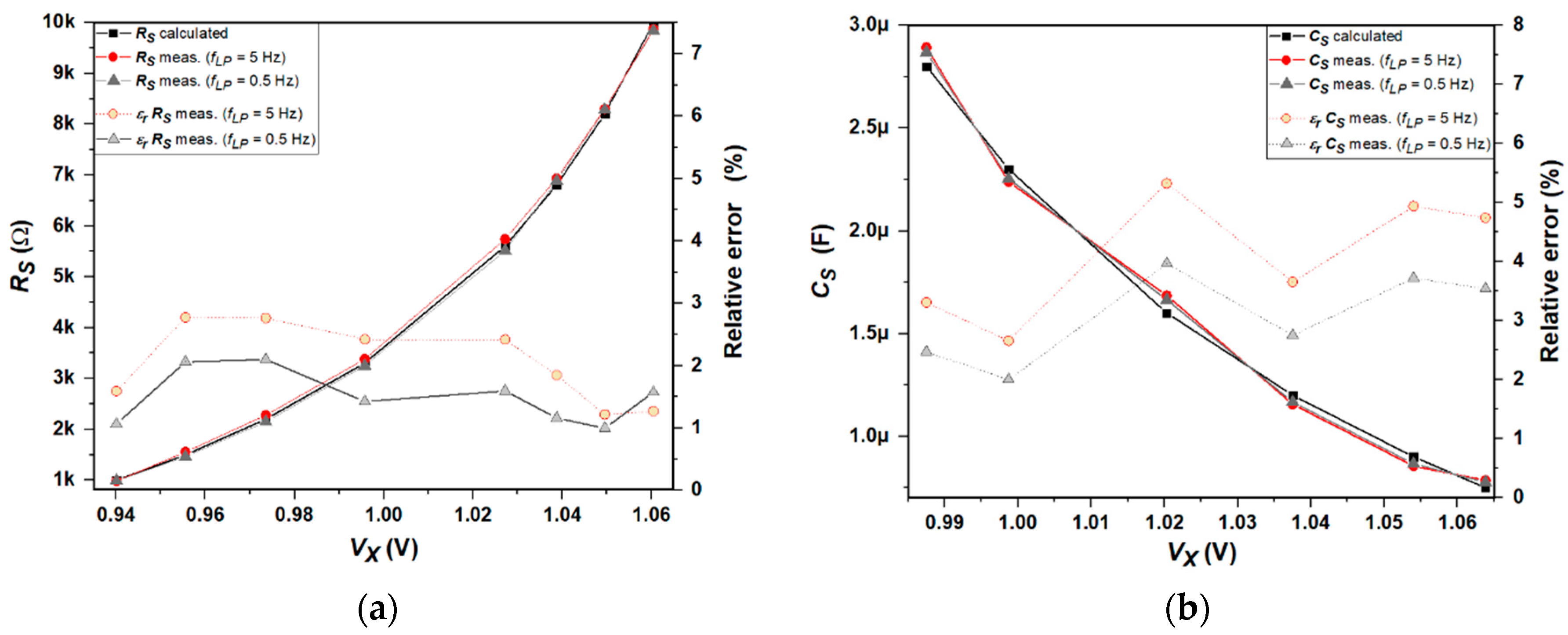

3.2. Impedance Measurements

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References and Note

- Alavi, A.H.; Jiao, P.; Buttlar, W.G.; Lainef, N. Internet of things-enabled smart cities: State-of-the-art and future trends. Measurement 2018, 129, 589–606. [Google Scholar] [CrossRef]

- Ghallab, Y.H.; Ismail, Y. CMOS Based Lab-on-Chip: Applications, Challenges and Future Trends. IEEE Circuits Syst. Mag. 2014, 14, 27–47. [Google Scholar] [CrossRef]

- Bayo Monton, J.L.; Martínez-Millana, A.; Han, W.; Fernandez Llatas, C.; San, Y.; Traver, V. Wearable Sensors Integrated with Internet of Things for Advancing eHealth Care. Sensors 2018, 18, 1851. [Google Scholar] [CrossRef] [PubMed]

- Cavaliere, A.; Carotenuto, F.; Di Gennaro, F.; Gioli, B.; Gualtieri, G.; Martelli, F.; Matese, A.; Toscano, P.; Vagnoli, C.; Zaldei, A. Development of Low-Cost Air Quality Stations for Next Generation Monitoring Networks: Calibration and Validation of PM2.5 and PM10 Sensors. Sensors 2018, 18, 2843. [Google Scholar] [CrossRef]

- Idrees, Z.; Zou, Z.; Zheng, L. Edge Computing Based IoT Architecture for Low Cost Air Pollution Monitoring Systems: A Comprehensive System Analysis, Design, Considerations & Development. Sensors 2018, 18, 3021. [Google Scholar]

- Durán, C.; Benjumea, J.; Carrillo, J. Response Optimization of a Chemical Gas Sensor Array using Temperature Modulation. Electronics 2018, 7, 54. [Google Scholar] [CrossRef]

- Beddows, P.A.; Mallon, E.K. Cave Pearl Data Logger: A Flexible Arduinos-Based Logging Platform for Long-Term Monitoring in Harsh Environments. Sensors 2018, 18, 530. [Google Scholar] [CrossRef]

- Zhang, Z.; Cao, S.; Wang, Y. A Long-Range 2.4G Network System and Scheduling Scheme for Aquatic Environmental Monitoring. Electronics 2018, 8, 909. [Google Scholar] [CrossRef]

- Alburquerque de Castro, B.; Guimaraes Baptista, F.; Ciampa, F. New signal processing approach for structural health monitoring in noisy environments based on impedance measurements. Measurement 2019, 137, 155–167. [Google Scholar] [CrossRef]

- Meade, M.L. Lock-in Amplifiers: Principles and Applications; Electronic, Ed.; Peter Peregrinus Ltd.: London, UK, 2013; Available online: https://sites.google.com/site/lockinamplifiers/ (accessed on 9 October 2019).

- About Lock-in Amplifiers, appl. Notes no. 3, Stanford Res. Sys. Datasheets, 1999.

- Lock-in Amplifier HF2LI, Zurich Instruments. Available online: https://www.zhinst.com/products/hf2li (accessed on 9 October 2019).

- Analog Lock-in Amplifier SR124, Stanford Research Systems. Available online: https://www.thinksrs.com/downloads/pdfs/manuals/SR124m.pdf (accessed on 9 October 2019).

- Dither Lock-in Amplifier 082218. IMRA America, Inc. Available online: https://www.imra.com/wp-content/uploads/2018/08/DLA-datasheet-082218.pdf (accessed on 9 October 2019).

- Synchronous Demodulator and Configurable Analog Filter ADA2200 Analog Devices. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/ADA2200.pdf (accessed on 15 November 2019).

- Díaz Michelena, M.; Cobos, P.; Aroca, C. Lock-in Amplifiers for AMR Sensors. Sens. Actuators A Phys. 2015, 222, 149–159. [Google Scholar] [CrossRef]

- Marshchner, U.; Gratz, H.; Jettkant, B.; Ruwisch, D.; Woldt, G.; Fischer, W.J.; Clasbrummel, B. Integration of a wireless lock-in measurement of hip prosthesis vibrations for loosening detection. Sens. Actuators A Phys. 2009, 156, 145–154. [Google Scholar] [CrossRef]

- Hu, A.; Chodavarapu, V.P. CMOS optoelectronic lock-in amplifier with integrated phototransistor array. IEEE Trans. Biomed. Circuits Syst. 2010, 4, 274–280. [Google Scholar] [CrossRef]

- Maya Hernández, P.M.; Álvarez Simón, L.C.; Sanz Pascual, M.T.; Calvo, B. An Integrated Low-Power Lock-in Amplifiers and Its Application to Gas Detection. Sensors 2014, 14, 15880–15899. [Google Scholar] [CrossRef]

- Azzolini, C.; Magnanini, A.; Tonelli, M.; Chiorboli, G.; Morandi, C. Integrated Lock-in Amplifier for Contactless Interface to Magnetically Stimulated Mechanical Resonators. In Proceedings of the IEEE International Conference on Design and Technology of Integrated Systems in Nanoscale Era, Tozeur, Tunisia, 25–27 March 2008. [Google Scholar]

- Pallás Areny, R. Sensores y Acondicionadores de Señal; Cuarta, E.D., Marcombo, S.A., Boixareu, E., Eds.; Marcombo: Barcelona, Spain, 2003. [Google Scholar]

- Meijer, G. Smart Sensor Systems; Gerard, C.M., Meijer, G., Eds.; John Wiley & Sons, Ltd.: Chichester, West Sussex, UK, 2008. [Google Scholar]

- Vera, S.D.; Bayo, A.; Medrano, N.; Calvo, B.; Celma, S. A Programmable Plug & Play Sensor Interface for WSN Applications. Sensors 2011, 11, 9009–9032. [Google Scholar]

- Ruzza, G.; Guerriero, L.; Revellino, P.; Guadagno, F.M. Thermal Compensation of Low-Cost MEMS Accelerometers for Tilt Measurements. Sensors 2018, 18, 2536. [Google Scholar] [CrossRef]

- Molina Cantero, A.J.; Castro García, J.A.; Lebrato Vázquez, C.; Gómez Gonzalez, I.M.; Merino Monge, M. Real Time Processing Library for Open Source Hardware Biomedical Sensors. Sensors 2018, 18, 1033. [Google Scholar] [CrossRef]

- Moe, A.E.; Marx, S.R.; Bhinderwala, I.; Wilson, D.N. A Miniaturized Lock-in Amplifier Design Suitable for Impedance Measurement Cells. In Proceedings of the IEEE Sensors, Vienna, Austria, 24–27 October 2004; pp. 215–218. [Google Scholar]

- Xu, J.; Meynants, G.; Merken, P. Low-Power Lock-In Amplifier for Complex Impedance Measurement. In Proceedings of the 2009 3rd International Workshop on Advances in Sensors and Interfaces, Trani, Italy, 25–26 June 2009; pp. 110–114. [Google Scholar]

- Min, M.; Parve, T. Improvement of Lock-in Electrical Bio-Impedance Analyzer for Implantable Medical Devices. IEEE Trans. Instrum. Meas. 2007, 56, 968–974. [Google Scholar] [CrossRef]

- Yúfera, A.; Rueda, A.; Muñoz, J.M.; Doldán, R.; Leger, G.; Rodriguez Villegas, E.O. A Tissue Impedance Measurement Chip for Myocardial Ischemia Detection. IEEE Trans. Circuits Syst. I Regul. Pap. 2005, 52, 2620–2628. [Google Scholar] [CrossRef]

- García Romeo, D.; Calvo, B.; Medrano, N.; Pina, M.P.; Almazán, F.; Pellejero, I.; Urbiztondo, M.; Sesé, J.; Santamaría, J. Portable Lock-In Amplifier for microcantilever based sensor array. Application to Explosives Detection using Co-BEA type zeolites as sensing materials. In Proceedings of the IEEE Sensors, Valencia, Spain, 2–5 November 2014. [Google Scholar]

- García Romeo, D.; Valero, M.R.; Medrano, N.; Calvo, B.; Celma, S. A High Performance LIA-Based Interface for Battery Powered Sensing Devices. Sensors 2015, 15, 25260–25276. [Google Scholar] [CrossRef]

- Ye, W.L.; Zheng, C.T.; Cheng, X.Y.; Wu, F.P.; Chen, M.M.; Wang, Y.D. Mid-infrared ppm-level methane detection device using small-size absorption pool and dual-channel lock-in amplifier. Infrared Phys. Technol. 2015, 71, 339–346. [Google Scholar] [CrossRef]

- Maya Hernández, P.M.; Sanz Pascual, M.T.; Calvo, B. CMOS Low-Power Lock-In Amplifiers with Signal Rectification in Current Domain. IEEE Trans. Instrum. Meas. 2015, 64, 1858–1867. [Google Scholar] [CrossRef]

- Dual Operational Amplifier HA17458 Hitachi. Available online: http://www.datasheetcatalog.com/datasheets_pdf/H/A/1/7/HA17458.shtml (accessed on 9 October 2019).

- Bult, K.; Geelen, G.J.G.M. An inherently linear and compact MOST-only current division technique. IEEE J. Solid State Circuits 1992, 27, 1730–1735. [Google Scholar] [CrossRef]

- Maya Hernández, P.M.; Calvo, B.; Sanz Pascual, M.T. Ultralow-Power Synchronous Demodulation for Low-Level Sensor Signal Detection. IEEE Trans. Instrum. Meas. 2019, 68, 3514–3523. [Google Scholar] [CrossRef]

- Maya Hernández, P.M.; Sanz Pascual, M.T.; Calvo, B. Micropower CMOS Lock-In Amplifier for Portable Applications. IET Electron. Lett. 2016, 52, 828–830. [Google Scholar] [CrossRef]

- Minaei, S.; Yuce, E. High input impedance NMOS-based phase shifter with minimum number of passive elements. Circuits Syst. Signal Process. 2012, 31, 51–60. [Google Scholar] [CrossRef]

- Yuce, E. A novel CMOS-Based Voltage-Mode First-Order phase shifter employing a grounded capacitor. Circuits Syst. Signal Process. 2010, 29, 235–245. [Google Scholar] [CrossRef]

- Zumbahlen, H. Allpass Filters; Analog Devices, Inc. Mini Tutorial MT-202: Norwood, MA, USA, 2012; pp. 1–2. [Google Scholar]

- De Graaf, G.; Wolffenbuttel, R.F. Lock-in amplifier techniques for low-frequency modulated sensor applications. In Proceedings of the 2012 IEEE International Instrumentation and Measurement Technology Conference Proceedings, Graz, Austria, 13–16 May 2012; pp. 1745–1749. [Google Scholar]

- Jafari, H.M.; Soleymani, L.; Genov, R. 16-Channel CMOS Impedance Spectroscopy DNA Analyzer with Dual-Slope Multiplying ADCs. IEEE Trans. Biomed. Circuits Syst. 2012, 6, 468–478. [Google Scholar] [CrossRef]

- Liu, X.; Lin, L.; Mason, A.J. High-throughput impedance spectroscopy biosensor array chip. Philos. Trans. R. Soc. A Lond. Math. Phys. Eng. Sci. 2014, 372, 20130107. [Google Scholar] [CrossRef]

- Manickham, A.; Chevalier, A.; McDermott, M.; Ellington, A.D.; Hassibi, A. A CMOS Electrochemical Impedance Spectroscopy (EIS) Biosensor Array. IEEE Trans. Biomed. Circuits Syst. 2010, 4, 379–390. [Google Scholar] [CrossRef]

- BJT Transistor 2N2222A. Available online: http://web.mit.edu/6.101/www/reference/2N2222A.pdf (accessed on 9 October 2019).

- Arduino YUN Platform. Available online: https://www.jameco.com/jameco/products/prodds/2193441.pdf (accessed on 9 October 2019).

- Mumtaz, Z.; Ullah, S.; Ilyas, Z.; Aslam, N.; Iqbal, S.; Liu, S.; Meo, J.A.; Madni, H.A. An Automation System for Controlling Streetlights and Monitoring Objects Using Arduino. Sensors 2018, 18, 3178. [Google Scholar] [CrossRef]

- Yazicioglu, R.F.; Merken, P.; Puers, R.; Van Hoof, C. A 60 µV 60 nV/√Hz Readout Front-End for Portable Biopotential Acquisition Systems. IEEE J. Solid State Circuits 2007, 42, 1100–1110. [Google Scholar] [CrossRef]

- Hsu, Y.P.; Liu, Z.; Hella, M.M. A 1.8 µW–65 dB THD ECG Acquisition Front-End IC Using a Bandpass Instrumentation Amplifier with Class-AB Output configuration. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 1859–1863. [Google Scholar] [CrossRef]

- De Marcellis, A.; Ferri, G.; D’Amico, A.; Di Natale, C.; Martinelli, E. A Fully-Analog Lock-In Amplifier with Automatic Phase Alignment for Accurate Measurements of ppb Gas Concentrations. IEEE Sens. J. 2012, 12, 1377–1383. [Google Scholar] [CrossRef]

- De Marcellis, A.; Ferri, G.; D’Amico, A. One-Decade Frequency Range, In-Phase Auto-Aligned 1.8 V 2 mW Fully Analog CMOS Integrated Lock-In Amplifier for Small/Noisy Signal Detection. IEEE Sens. J. 2016, 16, 5690–5701. [Google Scholar] [CrossRef]

| Parameters | Integrated CMIA |

|---|---|

| CMOS Technology | 180 nm |

| Power Supply | 1.8 V |

| Gain | 25–42 dB |

| Bandwidth | 125 kHz |

| Input Voltage Range | 4.5–17 mV |

| Dynamic Reserve | 35.5 dB |

| Resolution | 25 µV |

| THD (0.3 Vpp at 1 kHz) | −54.6 dB |

| Input referred noise (at 1 kHz) | 5.9 nV/Hz1/2 |

| Power Consumption | 417 µW |

| Integrated Area | 0.013 mm2 |

| Digital Word | Theory | Measured | Phase Error | |||

|---|---|---|---|---|---|---|

| dec | b3, b2, b1, b0 | RPS (kΩ) | θVR (deg) | RPS (kΩ) | θVR (deg) | εap (deg) |

| 00 | 0, 0, 0, 0 | 10.0 | 2.1 | 10.1 | 2.0 | 0.1 |

| 01 | 0, 0, 0, 1 | 9.38 | 3.3 | 9.50 | 3.0 | 0.2 |

| 02 | 0, 0, 1, 0 | 8.75 | 4.4 | 9.00 | 4.0 | 0.4 |

| 03 | 0, 0, 1, 1 | 8.13 | 6.2 | 8.20 | 6.0 | 0.2 |

| 04 | 0, 1, 0, 0 | 7.50 | 8.0 | 7.48 | 8.0 | 0.0 |

| 05 | 0, 1, 0, 1 | 6.88 | 10.1 | 6.90 | 10.0 | 0.1 |

| 06 | 0, 1, 1, 0 | 6.25 | 12.6 | 6.38 | 12.0 | 0.6 |

| 07 | 0, 1, 1, 1 | 5.63 | 15.6 | 5.73 | 15.0 | 0.6 |

| 08 | 1, 0, 0, 0 | 5.00 | 19.3 | 5.05 | 19.0 | 0.3 |

| 09 | 1, 0, 0, 1 | 4.38 | 23.9 | 4.50 | 23.0 | 0.9 |

| 10 | 1, 0, 1, 0 | 3.75 | 36.0 | 3.84 | 35.0 | 1.0 |

| 11 | 1, 0, 1, 1 | 3.13 | 37.9 | 3.20 | 37.0 | 0.9 |

| 12 | 1, 1, 0, 0 | 2.50 | 49.0 | 2.55 | 48.0 | 1.0 |

| 13 | 1, 1, 0, 1 | 1.88 | 64.5 | 1.90 | 63.0 | 1.5 |

| 14 | 1, 1, 1, 0 | 1.25 | 87.8 | 1.22 | 89.0 | 1.2 |

| 15 | 1, 1, 1, 1 | 0.63 | 120.8 | 0.64 | 120.0 | 0.8 |

| Phase Shift | Ideal Value (V) | Measured Value (V) | εrV (%) | |||

|---|---|---|---|---|---|---|

| VX | VY | VX | VY | VX | VY | |

| 0° | 1.141 | 0.900 | 1.140 | 0.904 | 0.1 | 0.5 |

| 75° | 1.141 | 0.900 | 1.139 | 0.900 | 0.2 | 0.0 |

| 180° | 1.141 | 0.900 | 1.140 | 0.904 | 0.1 | 0.5 |

| 210° | 1.141 | 0.900 | 1.139 | 0.906 | 0.2 | 0.7 |

| Parameters | This Work | [26]’04 | [20]’08 | [27]’09 | [18]’10 | [50]’12 | [31]’15 | [51]’16 |

|---|---|---|---|---|---|---|---|---|

| Implementation | CMOS 180 nm & Discrete components | Discrete components | CMOS 350 nm | CMOS 180 nm | CMOS 350 nm | Discrete components | CMOS 180 nm | CMOS 350 nm & Discrete components |

| Power Supply | 1.8 VLIAs 3.3 VOAs | n.a. | 3.3 V | 1.8 V | 3.3 V | 5 V | 1.8 V | 1.8 V |

| LPF implementation | RC external | External | RC external | SC internal | Gm-C internal | RC external | RC external | RC external |

| Gain | 25–42 dB | n.a. | 108 dB | −12–0 dB | 120 dBΩ | 112 dB | 0–40 dB | 106 dB |

| BW | 125 kHz | 10 MHz | 800 kHz | 100 kHz | 13–25 kHz | n.a. | 1 MHz | 2.5–25 Hz |

| Freq. op. | 1 kHz | 100 kHz | 30 kHz | 1 kHz | 20 kHz | 77 Hz | 10–100 kHz | 11 Hz |

| Input range | 4.5–17 mV | n.a. | 1 µV | 3 mV | n.a. | 0.002–7 mV | 0.2–14 mV | 35–700 nV |

| Resolution | 25 µV | n.a. | n.a. | n.a. | n.a. | 200 nV | 1 µV | 12.5 nV |

| Dynamic Reserve | 35.5 dB | n.a. | n.a. | n.a. | 1.31 dB | n.a. | 39 dB | 34 dB |

| Sensor Sensitivity | 16.3 µV/Ω 37 kV/F | n.a. | n.a. | 4.2 µV/Ω 75 MV/F | n.a. | n.a. | n.a. | n.a. |

| Sensor Range | 1–10 kΩ 0.75–2.8 µF | 20–220 Ω 0.15–1 µF | n.a. | 10–40 kΩ 0.5–1.8 nF | n.a. | n.a. | n.a. | n.a. |

| LIA config. | Single & Dual Phase | Dual Phase | Dual Phase | Dual Phase | Single Phase | Single Phase | Dual Phase | Single Phase |

| Phase Calibration | Included | Not included | External Adjust | Not Needed | Included | Included | Not Needed | Included |

| Phase Cal. Error εap | <1.5° | n.a. | n.a. | n.a. | n.a. | n.a. | n.a. | n.a. |

| Phase Cal. Time | <2.5 s | n.a. | n.a. | n.a. | n.a. | 25–80 s | n.a. | 1 s |

| Silicon Area | 0.026 mm2 | n.a. | 2.5 mm2 | 2 mm2 | 1.5 mm2 | n.a. | 0.048 mm2 | 8 mm2 |

| Power Consumption | 834 µW a 7 mW b | n.a. | 110 mW a | 2 mW a | 13 mW a | n.a. | 3.5 mW a | 2 mW b |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Maya, P.; Calvo, B.; Sanz-Pascual, M.T.; Osorio, J. Low Cost Autonomous Lock-In Amplifier for Resistance/Capacitance Sensor Measurements. Electronics 2019, 8, 1413. https://doi.org/10.3390/electronics8121413

Maya P, Calvo B, Sanz-Pascual MT, Osorio J. Low Cost Autonomous Lock-In Amplifier for Resistance/Capacitance Sensor Measurements. Electronics. 2019; 8(12):1413. https://doi.org/10.3390/electronics8121413

Chicago/Turabian StyleMaya, Paulina, Belén Calvo, María Teresa Sanz-Pascual, and Javier Osorio. 2019. "Low Cost Autonomous Lock-In Amplifier for Resistance/Capacitance Sensor Measurements" Electronics 8, no. 12: 1413. https://doi.org/10.3390/electronics8121413

APA StyleMaya, P., Calvo, B., Sanz-Pascual, M. T., & Osorio, J. (2019). Low Cost Autonomous Lock-In Amplifier for Resistance/Capacitance Sensor Measurements. Electronics, 8(12), 1413. https://doi.org/10.3390/electronics8121413