A Comprehensive Comparison of EMI Immunity in CMOS Amplifier Topologies

Abstract

1. Introduction

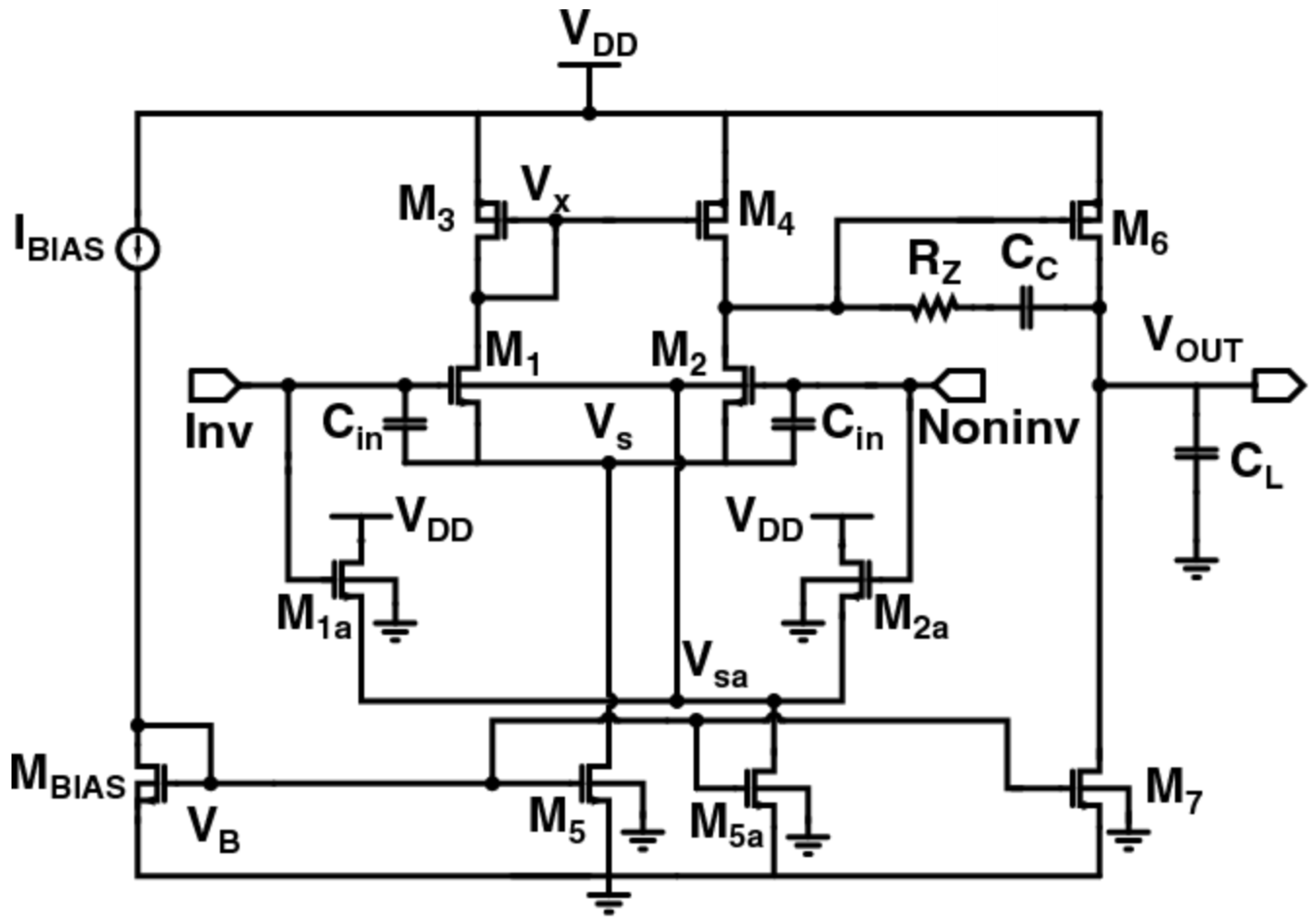

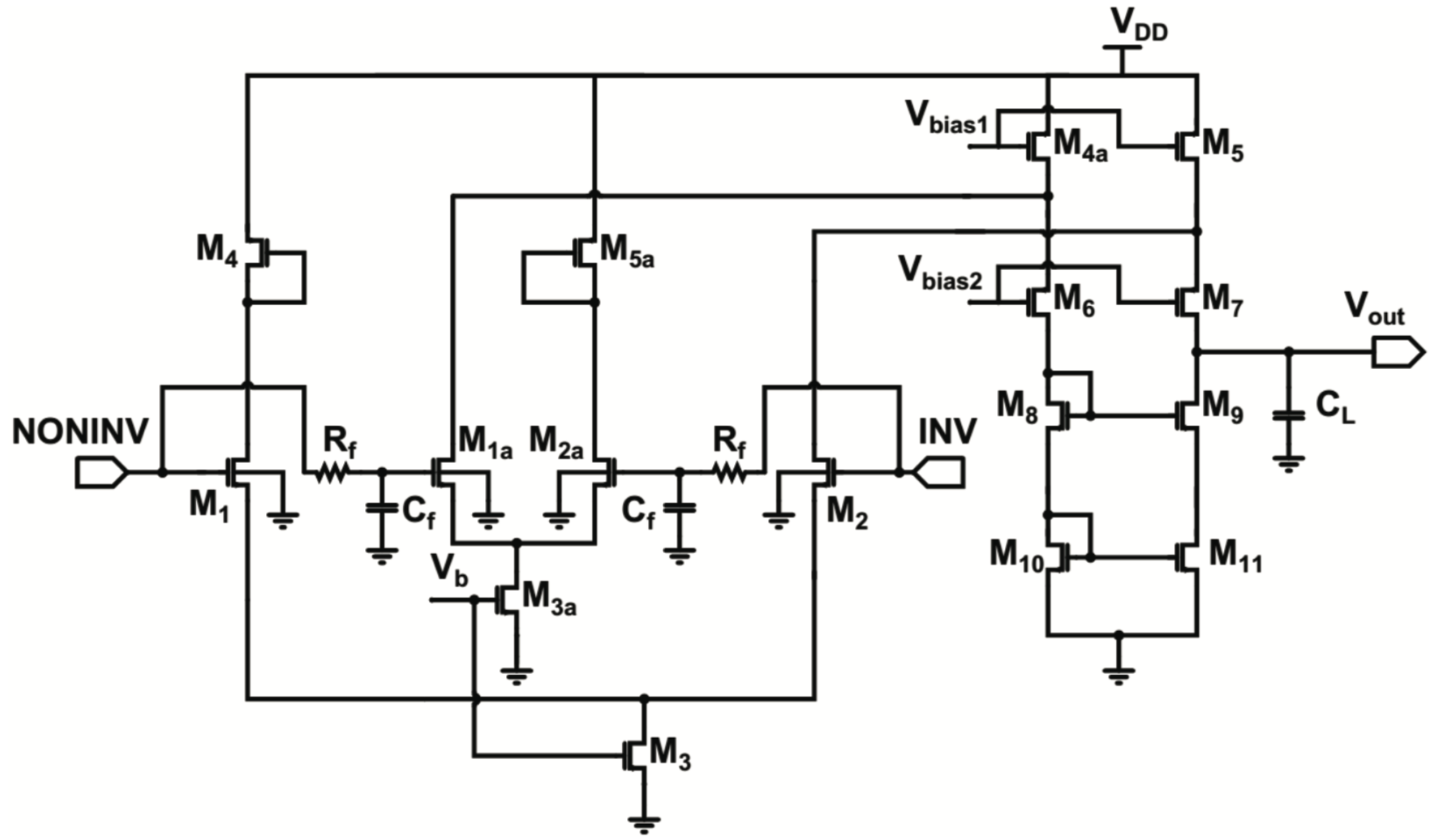

2. CMOS Miller Amplifiers

2.1. Compared Topologies and Their AC Characteristics

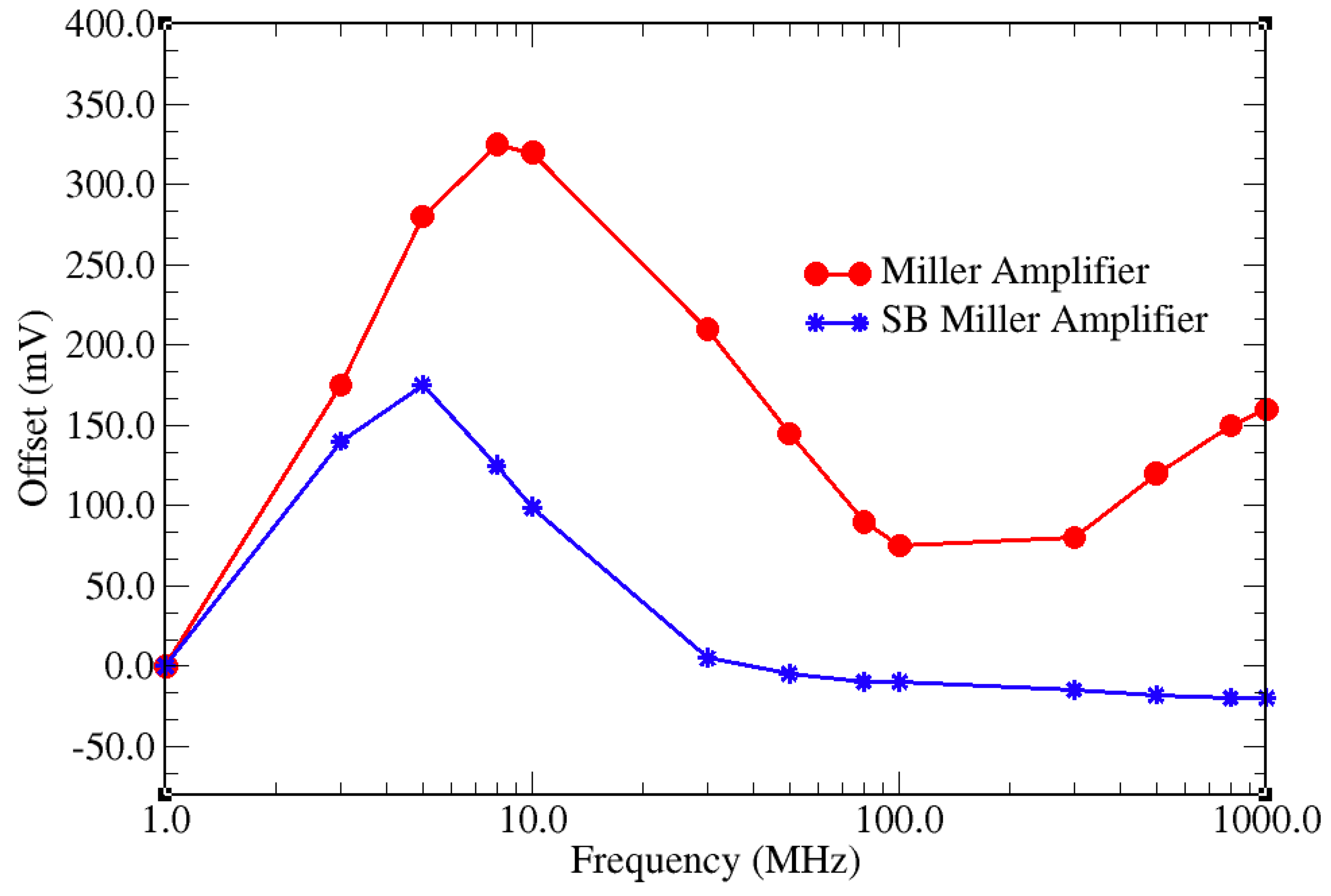

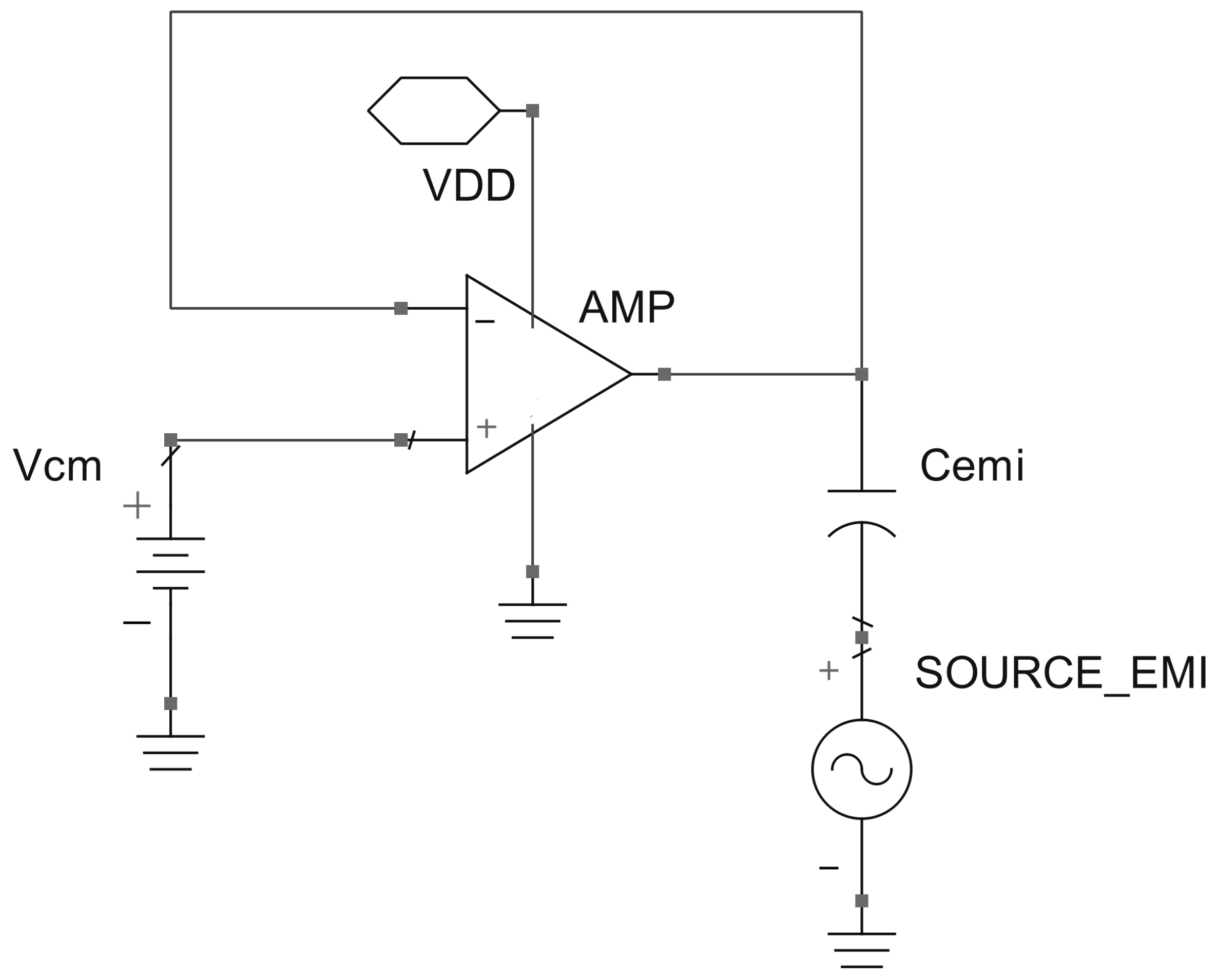

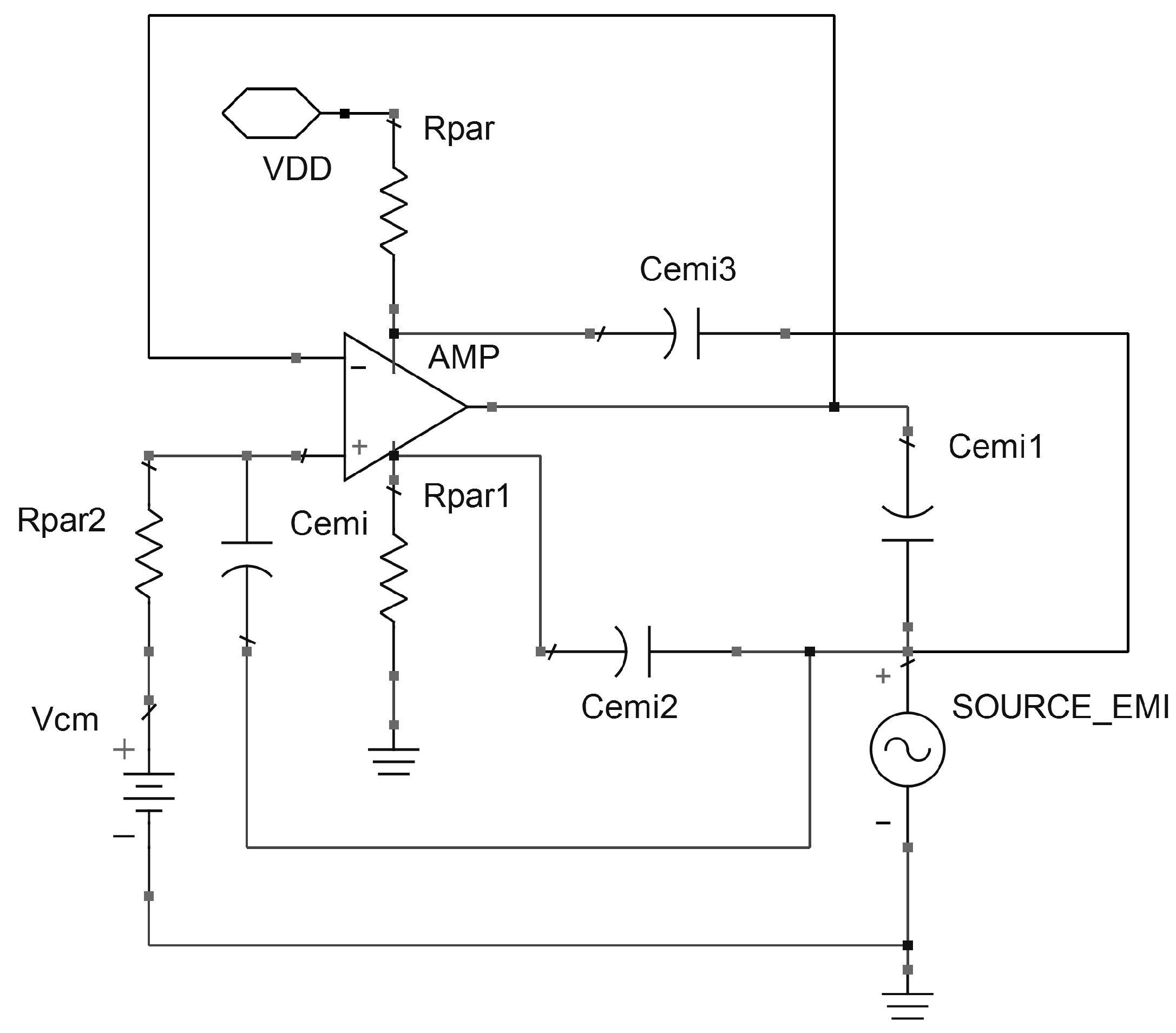

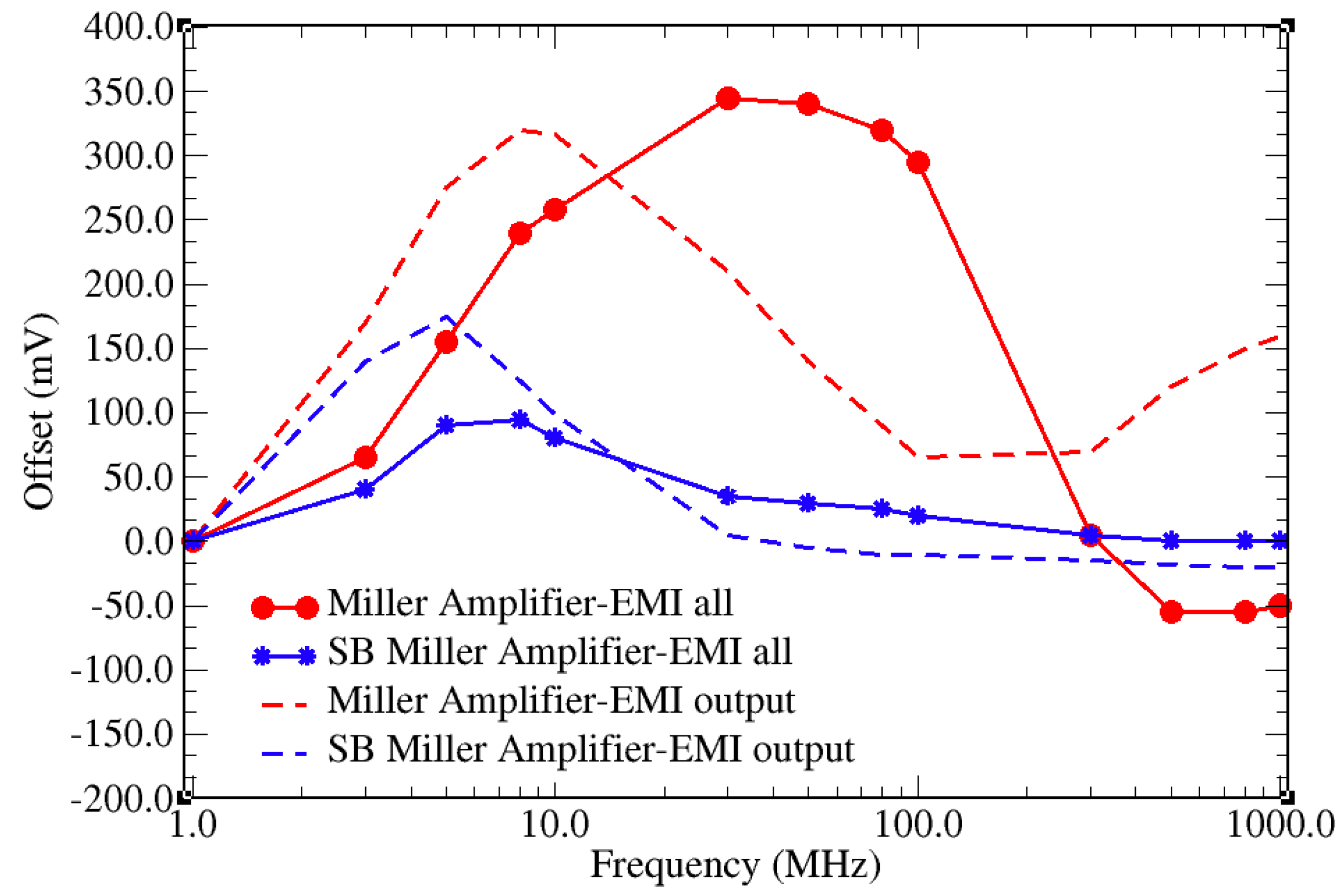

2.2. Susceptibility to EMI sDirectly Injected

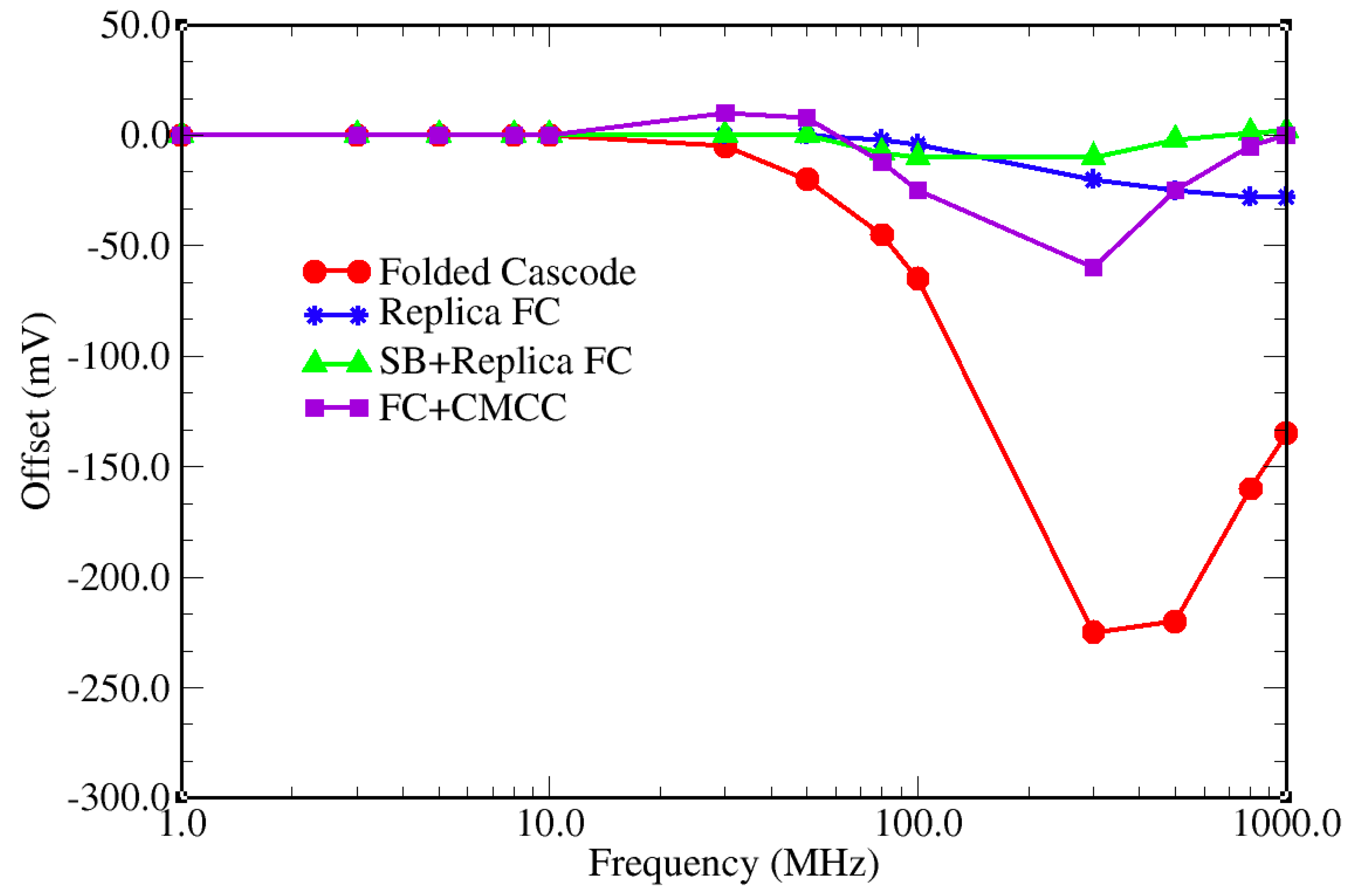

2.3. Susceptibility to EMI Coupled from the Ground Plane

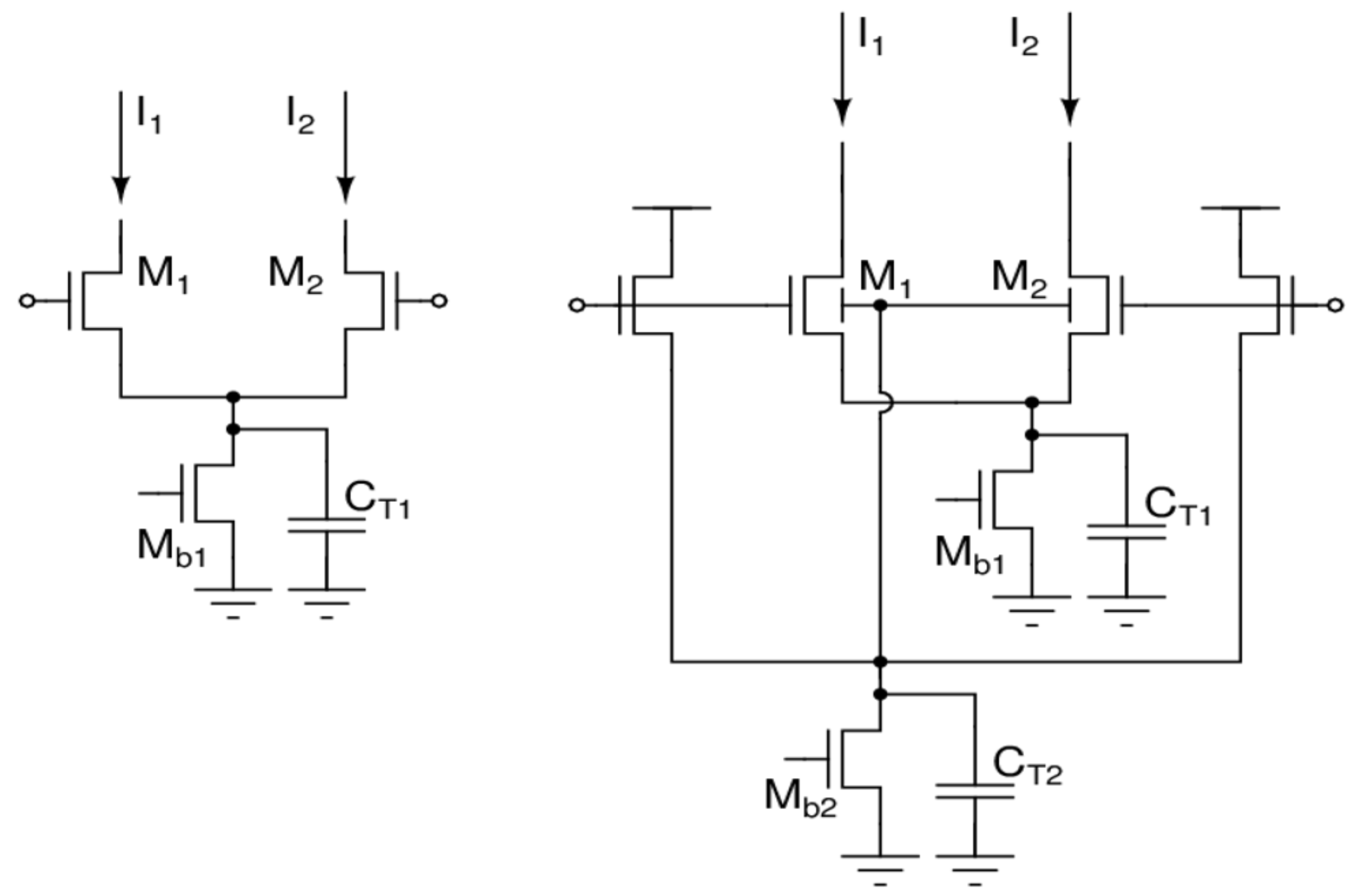

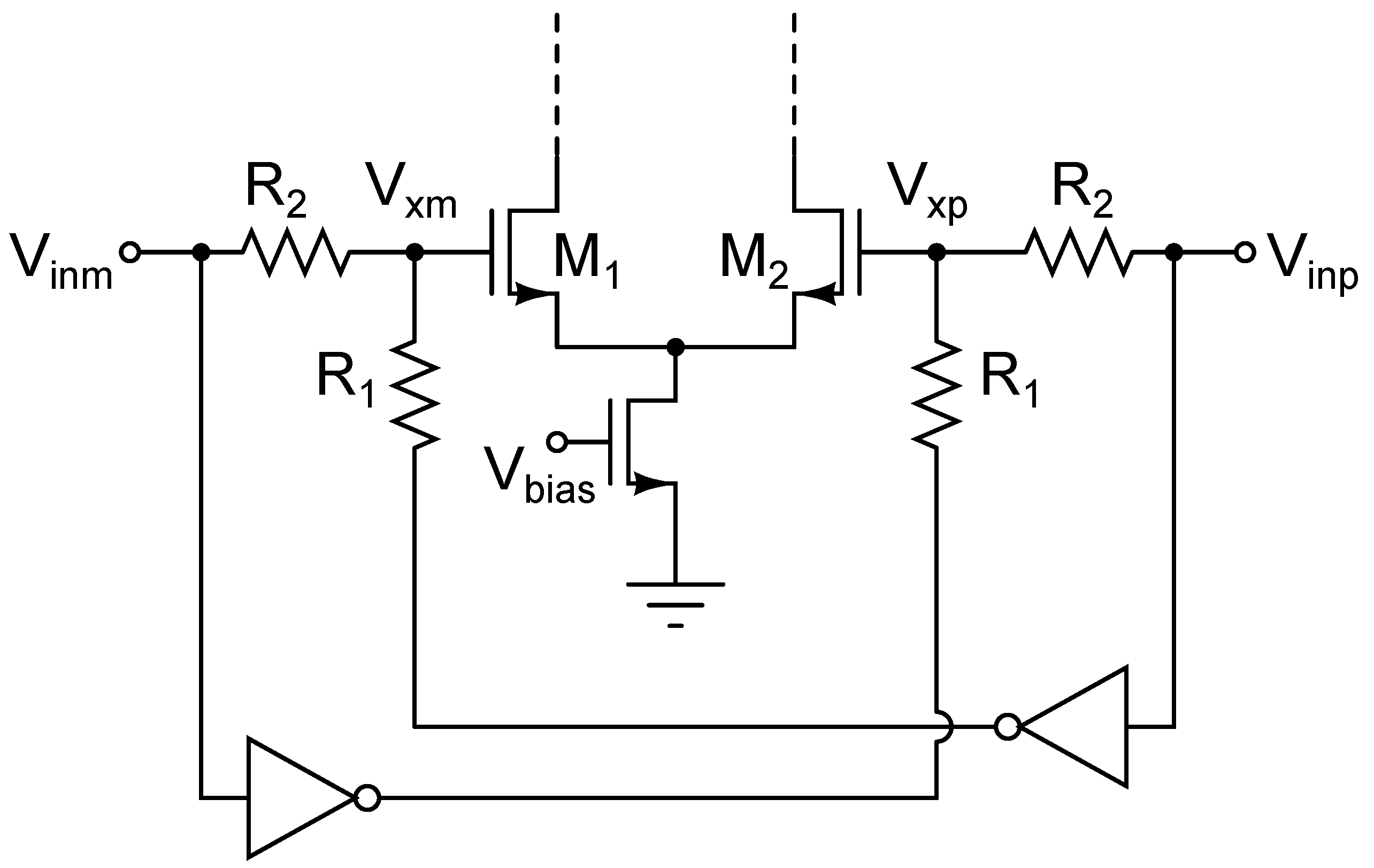

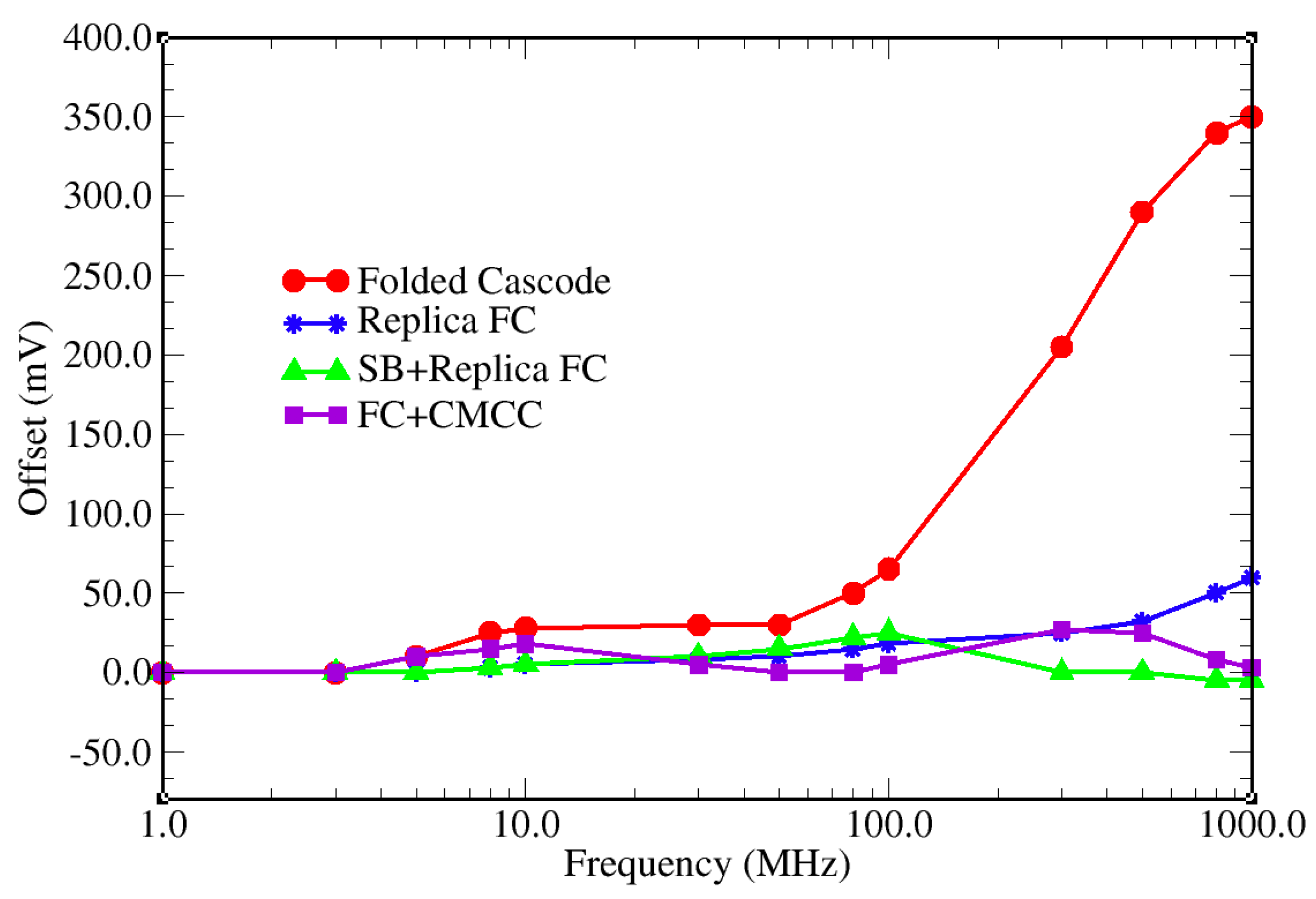

3. Folded Cascode Amplifiers

Compared Topologies and Their AC Characteristics

4. The Effect of the Voltage Buffer

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| EMI | Electromagnetic interference |

| CMOS | Complementary metal oxide semiconductor |

| UMC | United Microelectronics Corporation |

| GBW | Gain bandwidth |

| PCB | Printed circuit board |

| SB | Source-buffered |

| FC | Folded cascode |

| CMCC | Common mode cancellation circuit |

References

- Redouté, J.-M.; Steyaert, M. EMC of Analog Integrated Circuits; Springer: Basel, Switzerland, 2010. [Google Scholar]

- Fiori, F. EMI-Induced Distortion of Baseband Signals in Current Feedback Instrumentation Amplifiers. IEEE Trans. Electromagn. Compat. 2018, 60, 605–612. [Google Scholar] [CrossRef]

- Ramdani, M.; Sicard, E.; Boyer, A.; Dhia, S.B.; Whalen, J.J.; Hubing, T.H.; Coenen, M.; Wada, O. The Electromagnetic Compatibility of Integrated Circuits-Past, Present and Future. IEEE Trans. Electromagn. Compat. 2009, 51, 78–100. [Google Scholar] [CrossRef]

- Lavarda, A.; Petruzzi, L.; Radez, N.; Deutschmann, B. On the Robustness of CMOS-Chopped Operational Amplifiers to Conducted Electromagnetic Interferences. IEEE Trans. Electromagn. Compat. 2018, 60, 478–486. [Google Scholar] [CrossRef]

- Masetti, G.; Graffi, S.; Golzio, D.; Kovács-Vajna, Z.M. Failures induced on Analog Integrated Circuits from Conveyed electromagnetic Interferences: A Review. Microelectron. Reliab. 1996, 36, 955–972. [Google Scholar] [CrossRef]

- Dhia, S.B.; Ramdani, M.; Sicard, E. Electromagnetic Compatibility of Integrated Circuits; Springer: Basel, Switzerland, 2006. [Google Scholar]

- Yu, J.; Amer, A.; Sanchez-Sinencio, E. Electromagnetic Interference Resisting Operational Amplifier. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 1917–1927. [Google Scholar] [CrossRef]

- S, A.K.P.N.; Redouté, J.-M.; Baghini, M.S. A Generic EMI-Immune Technique for Differential Amplifiers With Single-Ended Output. IEEE Trans. Electromagn. Compat. 2018, 60, 958–964. [Google Scholar]

- Fiori, F. Design of an Operational Amplifier Input Stage Immune to EMI. IEEE Trans. Electromagn. Compat. 2007, 49, 834–839. [Google Scholar] [CrossRef]

- Richelli, A. EMI Susceptibility Issue in Analog Front-End for Sensor Applications. J. Sens. 2016. [Google Scholar] [CrossRef][Green Version]

- Boyapati, S.; Redouté, J.-M.; Baghini, M.S. Modeling and Design of EMI Immune OpAmp’s in 0.18 μm CMOS Technology. IEEE Trans. Electromagn. Compat. 2016, 58, 1609–1616. [Google Scholar] [CrossRef]

- Chahine, I.; Kadi, M.; Gaboriaud, E.; Louis, A.; Mazari, B. Characterization and Modeling of the Susceptibility of integrated Circuits to Conducted Electromagnetic Disturbances Up to 1 GHz. IEEE Trans. Electromagn. Compat. 2008, 50, 285–293. [Google Scholar] [CrossRef]

- Ceperic, V.; Baric, A. Modeling of Electromagnetic Immunity of Integrated Circuits by Artificial Neural Networks. In Proceedings of the International Symposium on Electromagnetic Compatibility, Zurich, Switzerland, 12–16 January 2009. [Google Scholar]

- Gil, I.; Fernandez-Garcia, R. Characterization and modelling of EMI susceptibility in integrated circuits at high frequencies. In Proceedings of the International Symposium on Electromagnetic Compatibility, Rome, Italy, 17–21 September 2012. [Google Scholar]

- Fiori, F.; Crovetti, P.S. Prediction of high-power EMI effects in CMOS operational amplifiers. IEEE Trans. Electromagn. Compat. 2006, 48, 153–160. [Google Scholar] [CrossRef]

- Richelli, A.; Delaini, G.; Grassi, M.; Redouté, J.-M. Susceptibility of Operational Amplifiers to Conducted EMI Injected Through the Ground Plane into Their Output Terminal. IEEE Trans. Reliab. 2016, 65, 1369–1379. [Google Scholar] [CrossRef]

- Richelli, A.; Colalongo, L.; Toninelli, L.; Rusu, I.; Redouté, J.-M. Measurements of EMI susceptibility of precision voltage references. In Proceedings of the EMCCompo 2017, St. Petersburg, Russia, 4–8 July 2017. [Google Scholar]

- Boyapati, S.; Redouté, J.-M.; Baghini, M.S. A Robust CMOS Miller OpAmp with High EMI-Immunity. In Proceedings of the EMC Europe 2017, Angers, France, 4–7 September 2017. [Google Scholar]

- Boyapati, S.; Redouté, J.-M.; Baghini, M.S. A Highly EMI-Immune Folded Cascode OpAmp in 0.18 μm CMOS Technology. In Proceedings of the EMC Europe 2016, Wroclaw, Poland, 5–9 September 2016. [Google Scholar]

- Richelli, A.; Redouté, J.-M. Increasing the EMI immunity of CMOS operational amplifiers using an on-chip common-mode cancellation circuit. In Proceedings of the EMC Europe 2014, Gothenburg, Sweden, 1–4 September 2014. [Google Scholar]

- Grassi, M.; Redouté, J.-M.; Richelli, A. Increased EMI immunity in CMOS operational amplifiers using an integrated common-mode cancellation circuit. In Proceedings of the EMC Europe 2015, Dresden, Germany, 16–22 August 2015. [Google Scholar]

- Richelli, A.; Kennedy, S.; Redouté, J.-M. An EMI-Resistant Common-Mode Cancelation Differential Input Stage in UMC 180 nm CMOS. IEEE Trans. Electromagn. Compat. 2017, 59, 2049–2051. [Google Scholar] [CrossRef]

- Richelli, A.; Redouté, J.-M. A Methodological Approach to EMI Resistant Analog Integrated Circuit Design. IEEE EMC Mag. 2015, 4, 92–100. [Google Scholar]

- Redouté, J.-M.; Steyaert, M. EMI Resistant CMOS Differential Input Stages. IEEE Trans. Circuits Syst. I 2010, 57, 323–331. [Google Scholar] [CrossRef]

- Richelli, A.; Matig-a, G.; Redouté, J.-M. Design of a folded cascode opamp with increased immunity to conducted electromagnetic interference in 0.18 μm CMOS. Microelectron. Reliab. 2015, 55, 654–661. [Google Scholar] [CrossRef]

| Miller | SB Miller | |

|---|---|---|

| Gain | 65.8 dB | 65.8 dB |

| 19.5 kHz | 19.7 kHz | |

| GBW | 32.4 MHz | 32.3 MHz |

| Phase margin | 65.7° | 65.8° |

| Power consumption | 540 W | 620 W |

| Miller | SB Miller | |

|---|---|---|

| M1, M2 | 20/0.5 | 20/0.5 |

| M3, M4 | 80/0.5 | 80/0.5 |

| M5, | 60/1 | 60/1 |

| M6 | 60/0.5 | 60/0.5 |

| M7 | 20/0.5 | 20/0.5 |

| , | 10/0.5 | |

| 50/0.5 |

| FC | Replica | SB Improved | FC + CMCC | |

|---|---|---|---|---|

| Gain | 60.9 dB | 61.8 dB | 61.2 dB | 66.6 dB |

| 21.6 kHz | 19.6 kHz | 19.9 kHz | 21.6 kHz | |

| GBW | 23.9 MHz | 12.4 MHz | 11.3 MHz | 42.7 MHz |

| Phase margin | 85° | 84° | 84° | 60° |

| Power consumption | 1 mW | 1.3 mW | 1.5 mW | 1.2 mW |

| Replica FC | SB + Replica FC | |

|---|---|---|

| M1, M2 | 20/0.5 | 20/0.5 |

| , | 20/0.5 | 15/0.5 |

| M3, | 6.05/0.5 | 6.05/0.5 |

| M4, M5 | 42.5/0.6 | 42.5/0.6 |

| , | 42.5/0.6 | 42.5/0.6 |

| M6, M7 | 2.5/0.34 | 2.5/0.34 |

| M8, M9 | 4.75/0.34 | 4.75/0.34 |

| M10, M11 | 4.75/0.34 | 4.75/0.34 |

| , | 20/0.5 | |

| 6.05/0.5 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Becchetti, S.; Richelli, A.; Colalongo, L.; Kovacs-Vajna, Z. A Comprehensive Comparison of EMI Immunity in CMOS Amplifier Topologies. Electronics 2019, 8, 1181. https://doi.org/10.3390/electronics8101181

Becchetti S, Richelli A, Colalongo L, Kovacs-Vajna Z. A Comprehensive Comparison of EMI Immunity in CMOS Amplifier Topologies. Electronics. 2019; 8(10):1181. https://doi.org/10.3390/electronics8101181

Chicago/Turabian StyleBecchetti, Simone, Anna Richelli, Luigi Colalongo, and Zsolt Kovacs-Vajna. 2019. "A Comprehensive Comparison of EMI Immunity in CMOS Amplifier Topologies" Electronics 8, no. 10: 1181. https://doi.org/10.3390/electronics8101181

APA StyleBecchetti, S., Richelli, A., Colalongo, L., & Kovacs-Vajna, Z. (2019). A Comprehensive Comparison of EMI Immunity in CMOS Amplifier Topologies. Electronics, 8(10), 1181. https://doi.org/10.3390/electronics8101181