Investigation of Temperature-Dependent Gate Degradation in Normally-Off AlGaN/GaN High-Electron-Mobility Transistor p-GaN

Abstract

1. Introduction

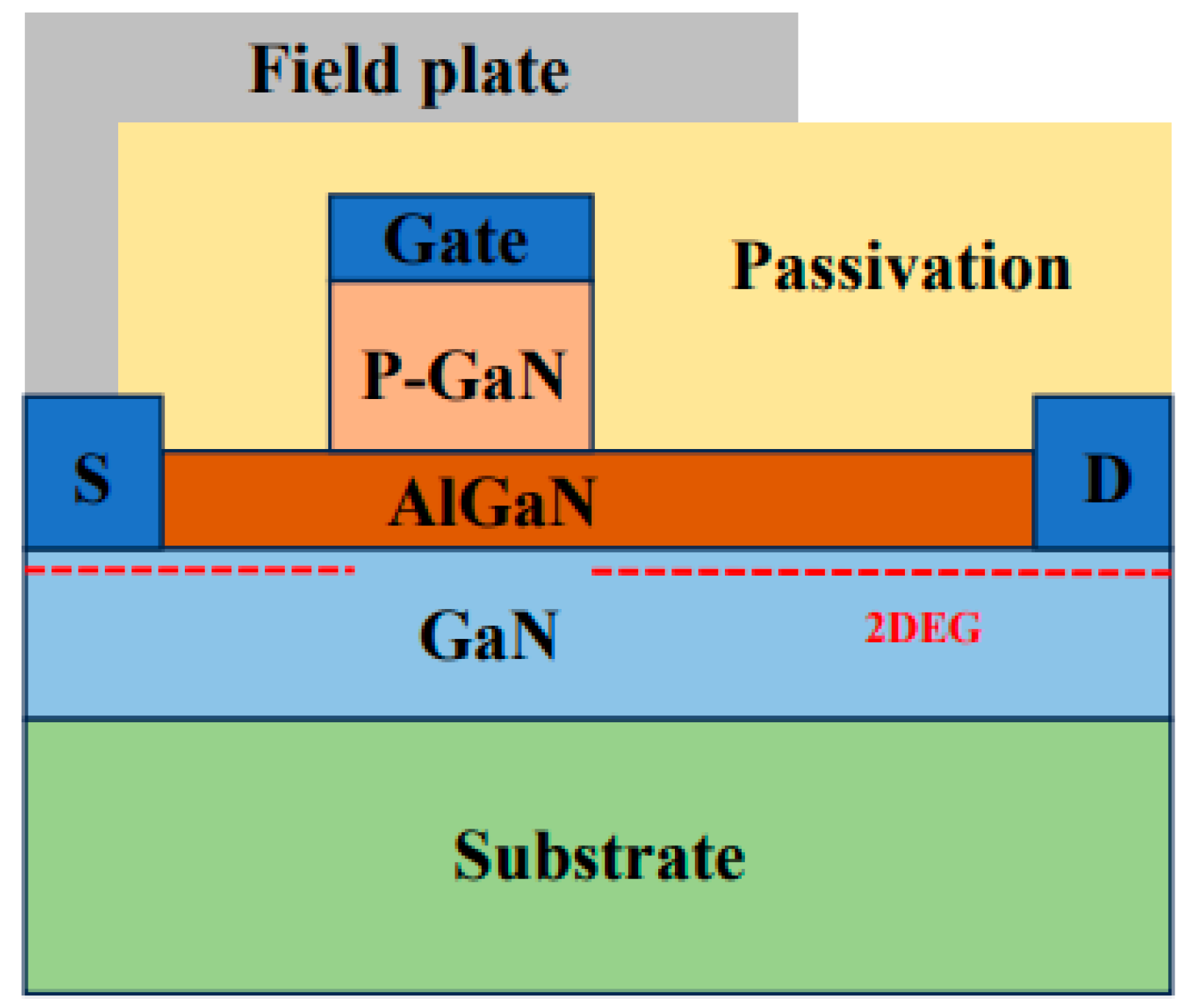

2. Materials and Methods

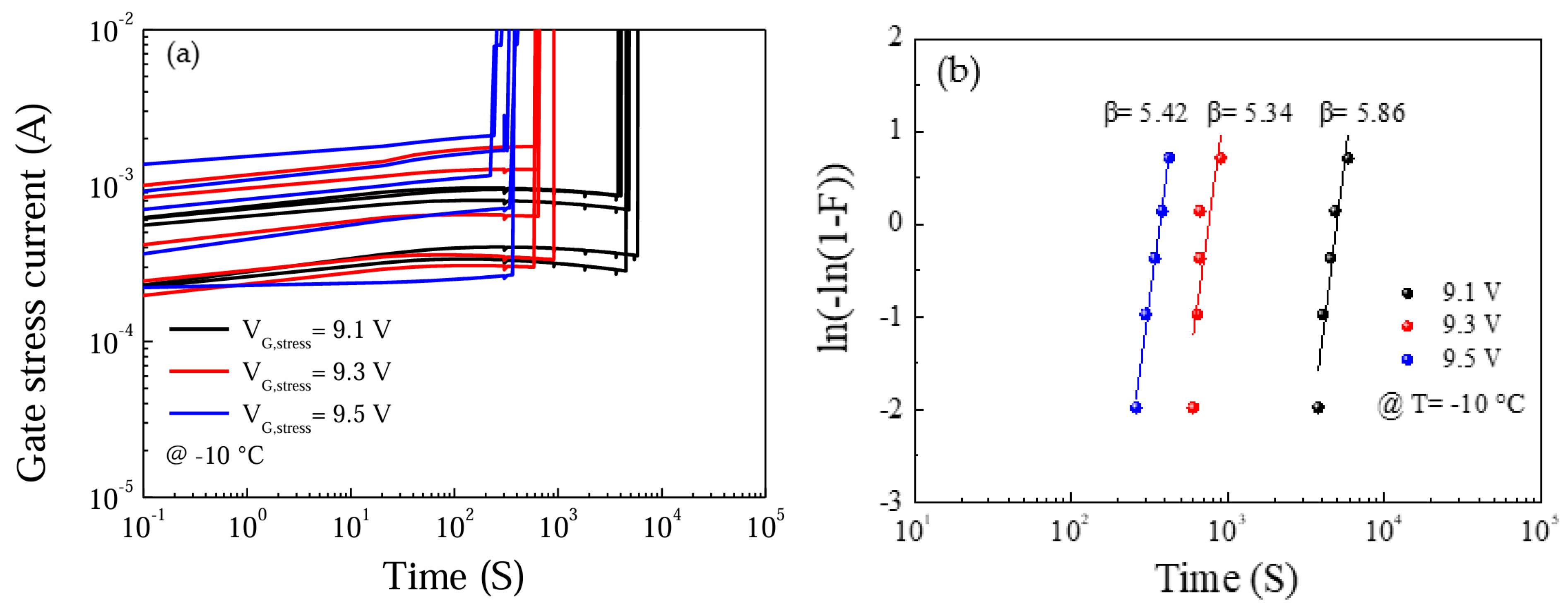

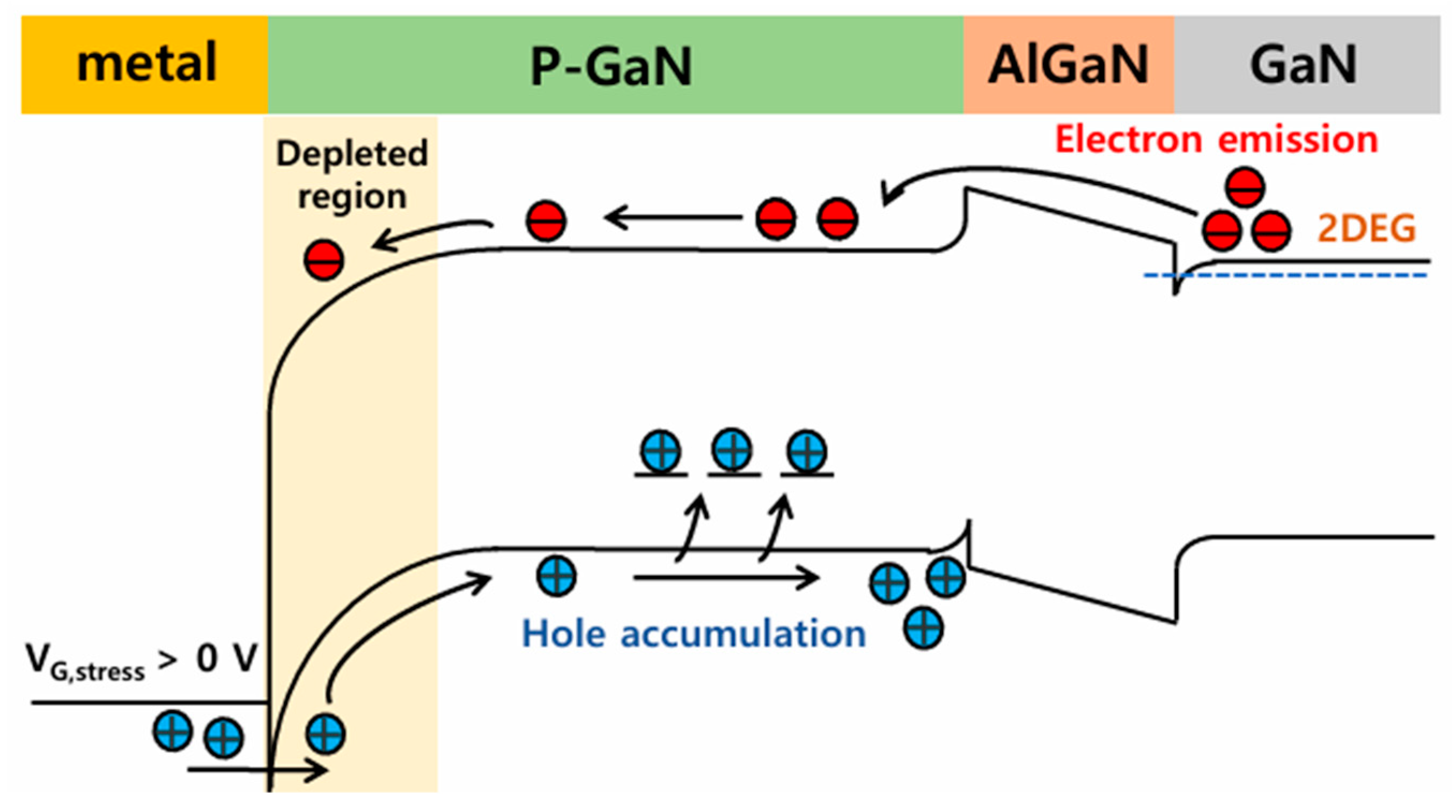

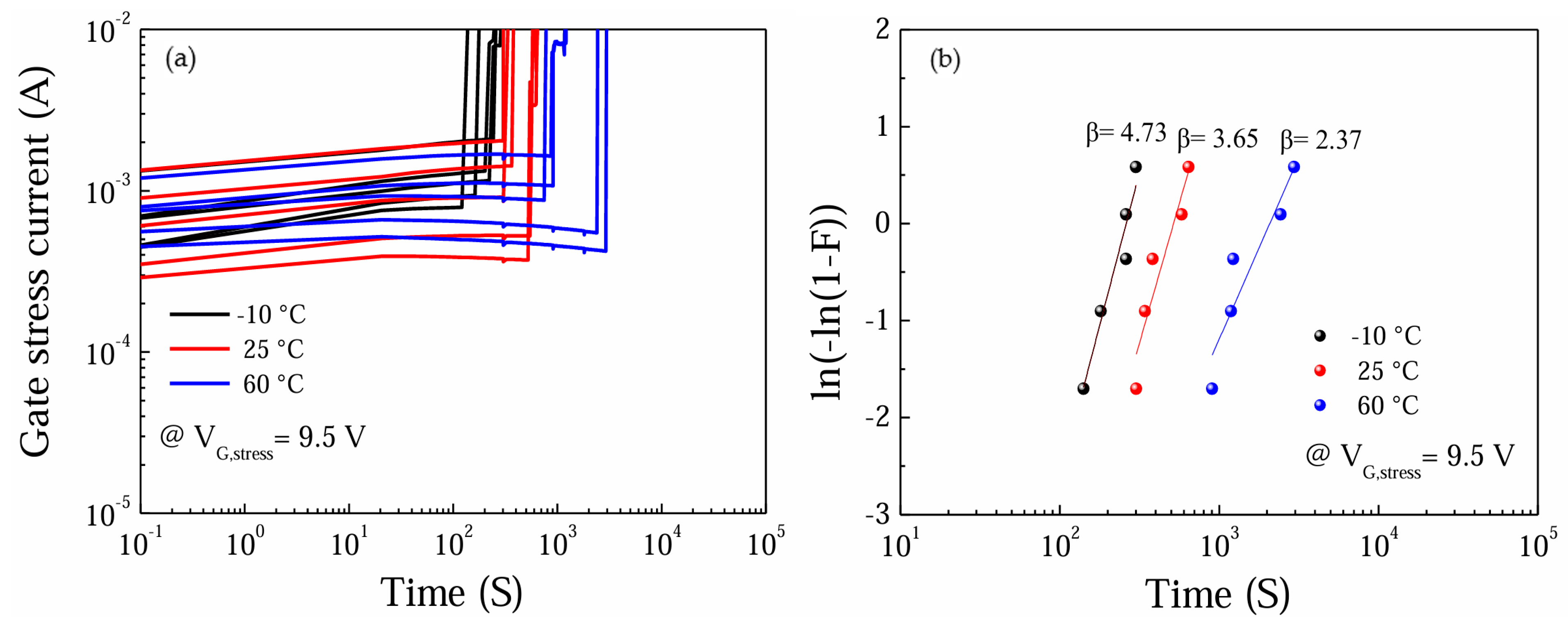

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Ambacher, O.; Foutz, B.; Smart, J.; Shealy, J.R.; Weimann, N.G.; Chu, K.; Murphy, M.; Sierakowski, A.J.; Schaff, W.J.; Eastman, L.F.; et al. Two-dimensional electron gases induced by spontaneous and piezoelectric polarization in undoped and doped AlGaN/GaN heterostructures. J. Appl. Phys. 1999, 87, 334–344. [Google Scholar] [CrossRef]

- Ambacher, O.; Smart, J.; Shealy, J.R.; Weimann, N.G.; Chu, K.; Murphy, M.; Schaff, W.J.; Eastman, L.F.; Dimitrov, R.; Wittmer, L.; et al. Two-dimensional electron gases induced by spontaneous and piezoelectric polarization charges in N- and Ga-face AlGaN/GaN heterostructures. J. Appl. Phys. 1999, 85, 3222–3233. [Google Scholar] [CrossRef]

- Hassan, A.; Savaria, Y.; Sawan, M. GaN Integration Technology, an Ideal Candidate for High-Temperature Applications: A Review. IEEE Access 2018, 6, 78790–78802. [Google Scholar] [CrossRef]

- Haziq, M.; Falina, S.; Manaf, A.A.; Kawarada, H.; Syamsul, M. Challenges and opportunities for high-power and high-frequency AlGaN/GaN high-electron-mobility transistor (HEMT) applications: A review. Micromachines 2022, 13, 2133. [Google Scholar] [CrossRef] [PubMed]

- Greco, G.; Iucolano, F.; Roccaforte, F. Review of technology for normally-off HEMTs with p-GaN gate. Mater. Sci. Semicond. Proc. 2018, 78, 96–106. [Google Scholar] [CrossRef]

- Hilt, O.; Knauer, A.; Brunner, F.; Bahat-Treidel, E.; Wurfl, J. Normally-off AlGaN/GaN HFET with p-type GaN Gate and AlGaN Buffer. In Proceedings of the 2010 22nd International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Hiroshima, Japan, 6–10 June 2010; pp. 347–350. [Google Scholar]

- Hwang, I.; Kim, J.; Choi, H.S.; Choi, H.; Lee, J.; Kim, K.Y.; Park, J.-B.; Lee, J.C.; Ha, J.; Oh, J.; et al. p-GaN Gate HEMTs With Tungsten Gate Metal for High Threshold Voltage and Low Gate Current. IEEE Electron Device Lett. 2013, 34, 202–204. [Google Scholar] [CrossRef]

- Zhou, G.; Zeng, F.; Jiang, Y.; Jiang, Q.W.L. Determination of the Gate Breakdown Mechanism in p-GaN Gate HEMTs by Multiple-Gate-Sweep Measurements. IEEE Electron Device Lett. 2021, 68, 1518–1523. [Google Scholar] [CrossRef]

- Meneghini, M.; Rossetto, I.; Rizzato, V.; Stoffels, S.; Van Hove, M.; Posthuma, N.; Wu, T.-L.; Marcon, D.; Decoutere, S.; Meneghesso, G.; et al. Gate Stability of GaN-Based HEMTs with P-Type Gate. Electronics 2016, 5, 14. [Google Scholar] [CrossRef]

- Wang, C.; Hua, M.; Yang, S.; Zhang, L.; Chen, K.J. E-mode p-n Junction/AlGaN/GaN HEMTs with Enhanced Gate Reliability. In Proceedings of the 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020; pp. 14–17. [Google Scholar] [CrossRef]

- Ťapajna, M.; Hilt, O.; Bahat-Treidel, E.; Würfl, J.; Kuzmík, J. Gate Reliability Investigation in Normally-Off p-Type-GaN Cap/AlGaN/GaN HEMTs Under Forward Bias Stress. IEEE Electron Device Lett. 2016, 37, 385–388. [Google Scholar] [CrossRef]

- Millesimo, M.; Fiegna, C.; Posthuma, N.; Borga, M.; Bakeroot, B.; Decoutere, S.; Tallarico, A.N. High-Temperature Time-Dependent Gate Breakdown of p-GaN HEMTs. IEEE Trans. Electron Devices 2021, 68, 5701–5706. [Google Scholar] [CrossRef]

- He, J.; Wei, J.; Yang, S.; Hua, M.; Zhong, K.; Chen, K.J. Temperature-Dependent Gate Degradation of p-GaN Gate HEMTs under Static and Dynamic Positive Gate Stress. In Proceedings of the 2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 19–23 May 2019; pp. 295–298. [Google Scholar] [CrossRef]

- Rossetto, I.; Meneghini, M.; Hilt, O.; Bahat-Treidel, E.; De Santi, C.; Dalcanale, S.; Wuerfl, J.; Zanoni, E.; Meneghesso, G. Time-Dependent Failure of GaN-on-Si Power HEMTs With p-GaN Gate. IEEE Trans. Electron Devices 2016, 63, 2334–2339. [Google Scholar] [CrossRef]

- GS-065-004-1-L. Datasheet. GaN Systems. 2022. Available online: http://www.gansystems.com (accessed on 1 August 2024).

- Chae, M.; Kim, H. Investigation of the Gate Degradation Induced by Forward Gate Voltage Stress in p-GaN Gate High Electron Mobility Transistors. Micromachines 2023, 14, 977. [Google Scholar] [CrossRef] [PubMed]

- Bhattacharya, P.; Bhattacharjee, R. A study on Weibull distribution for estimating the parameters. Wind Eng. 2009, 33, 469–476. [Google Scholar] [CrossRef]

- Wu, T.-L.; Marcon, D.; You, S.; Posthuma, N.; Bakeroot, B.; Stoffels, S.; Van Hove, M.; Groeseneken, G.; Decoutere, S. Forward Bias Gate Breakdown Mechanism in Enhancement-Mode p-GaN Gate AlGaN/GaN High-Electron Mobility Transistors. IEEE Electron Device Lett. 2015, 36, 1001–1003. [Google Scholar] [CrossRef]

- Tallarico, A.N.; Stoffels, S.; Magnone, P.; Posthuma, N.; Sangiorgi, E.; Decoutere, S.; Fiegna, C. Investigation of the p-GaN Gate Breakdown in Forward-Biased GaN-Based Power HEMTs. IEEE Electron Device Lett. 2017, 38, 99–102. [Google Scholar] [CrossRef]

- Masin, F.; Meneghini, M.; Canato, E.; De Santi, C.; Stockman, A.; Zanoni, E.; Moens, P.; Meneghesso, G. Positive temperature dependence of time-dependent breakdown of GaN-on-Si E-mode HEMTs under positive gate stress. Appl. Phys. Lett. 2019, 115, 052103. [Google Scholar] [CrossRef]

- He, J.; Wei, J.; Li, Y.; Zheng, Z.; Yang, S.; Huang, B.; Chen, K.J. Characterization and analysis of low-temperature time-to-failure behavior in forward-biased Schottky-type p-GaN gate HEMTs. Appl. Phys. Lett. 2020, 116, 223502. [Google Scholar] [CrossRef]

- He, J.; Wei, J.; Zheng, Z.; Yang, S.; Li, Y.; Huang, B.; Chen, K.J. Low-Temperature Accelerated Gate Reliability of Schottky-type p-GaN Gate HEMTs. In Proceedings of the 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020; pp. 290–293. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yoon, J.; Kim, H. Investigation of Temperature-Dependent Gate Degradation in Normally-Off AlGaN/GaN High-Electron-Mobility Transistor p-GaN. Electronics 2025, 14, 1764. https://doi.org/10.3390/electronics14091764

Yoon J, Kim H. Investigation of Temperature-Dependent Gate Degradation in Normally-Off AlGaN/GaN High-Electron-Mobility Transistor p-GaN. Electronics. 2025; 14(9):1764. https://doi.org/10.3390/electronics14091764

Chicago/Turabian StyleYoon, Jeonghyeok, and Hyungtak Kim. 2025. "Investigation of Temperature-Dependent Gate Degradation in Normally-Off AlGaN/GaN High-Electron-Mobility Transistor p-GaN" Electronics 14, no. 9: 1764. https://doi.org/10.3390/electronics14091764

APA StyleYoon, J., & Kim, H. (2025). Investigation of Temperature-Dependent Gate Degradation in Normally-Off AlGaN/GaN High-Electron-Mobility Transistor p-GaN. Electronics, 14(9), 1764. https://doi.org/10.3390/electronics14091764