Surge Current Capability and Failure Modes of 650 V p-GaN Gate HEMTs: A Multiphysics Study on Thermal–Electrical Coupling Effects

Abstract

1. Introduction

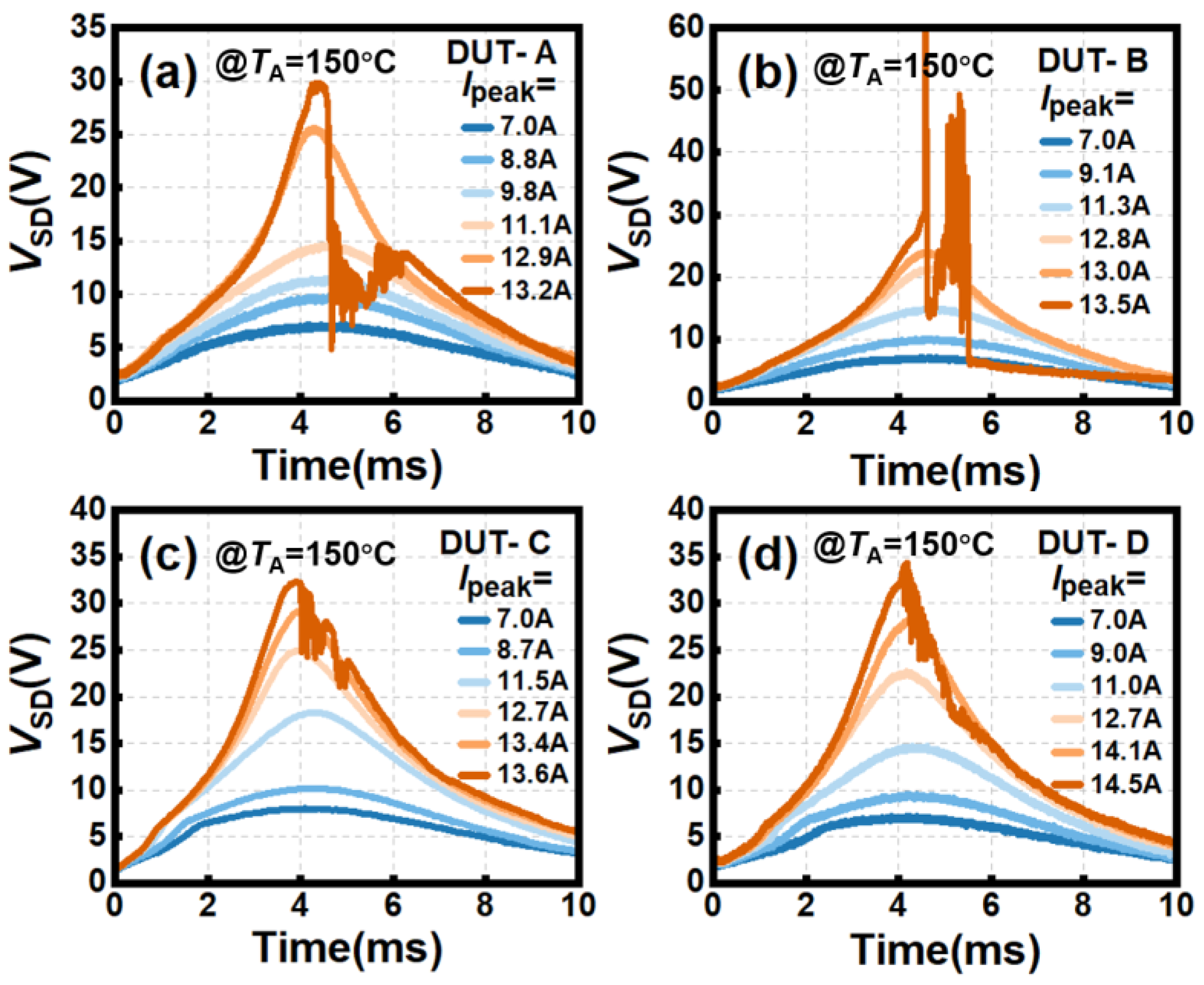

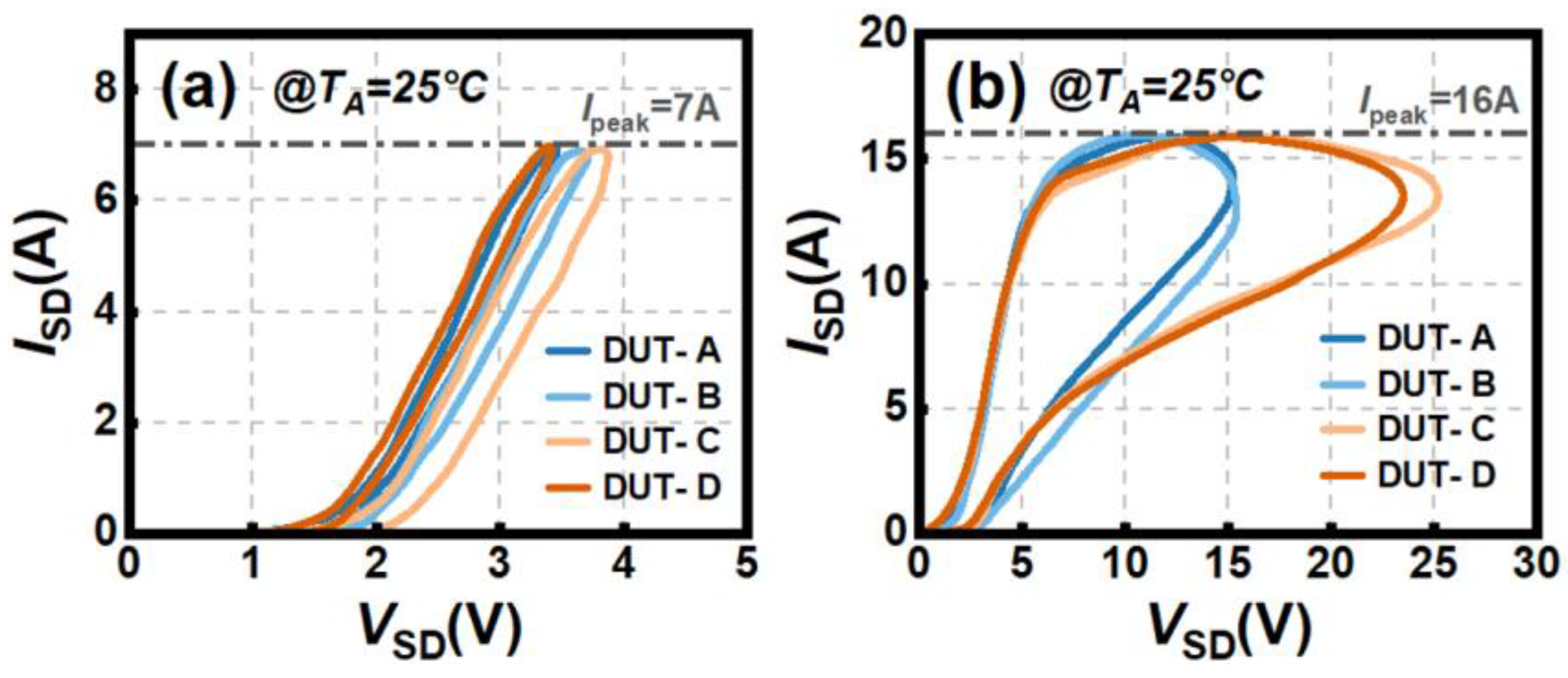

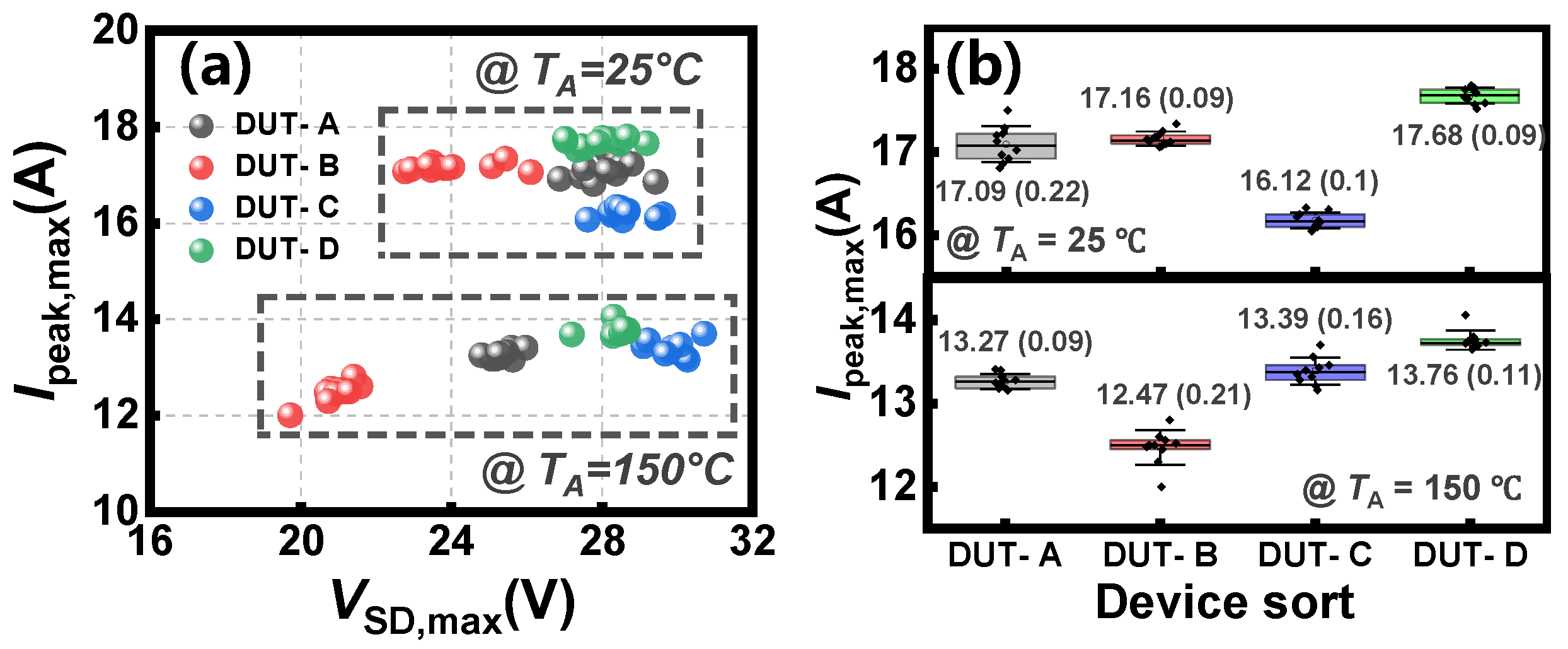

2. Surge Current Test and Results

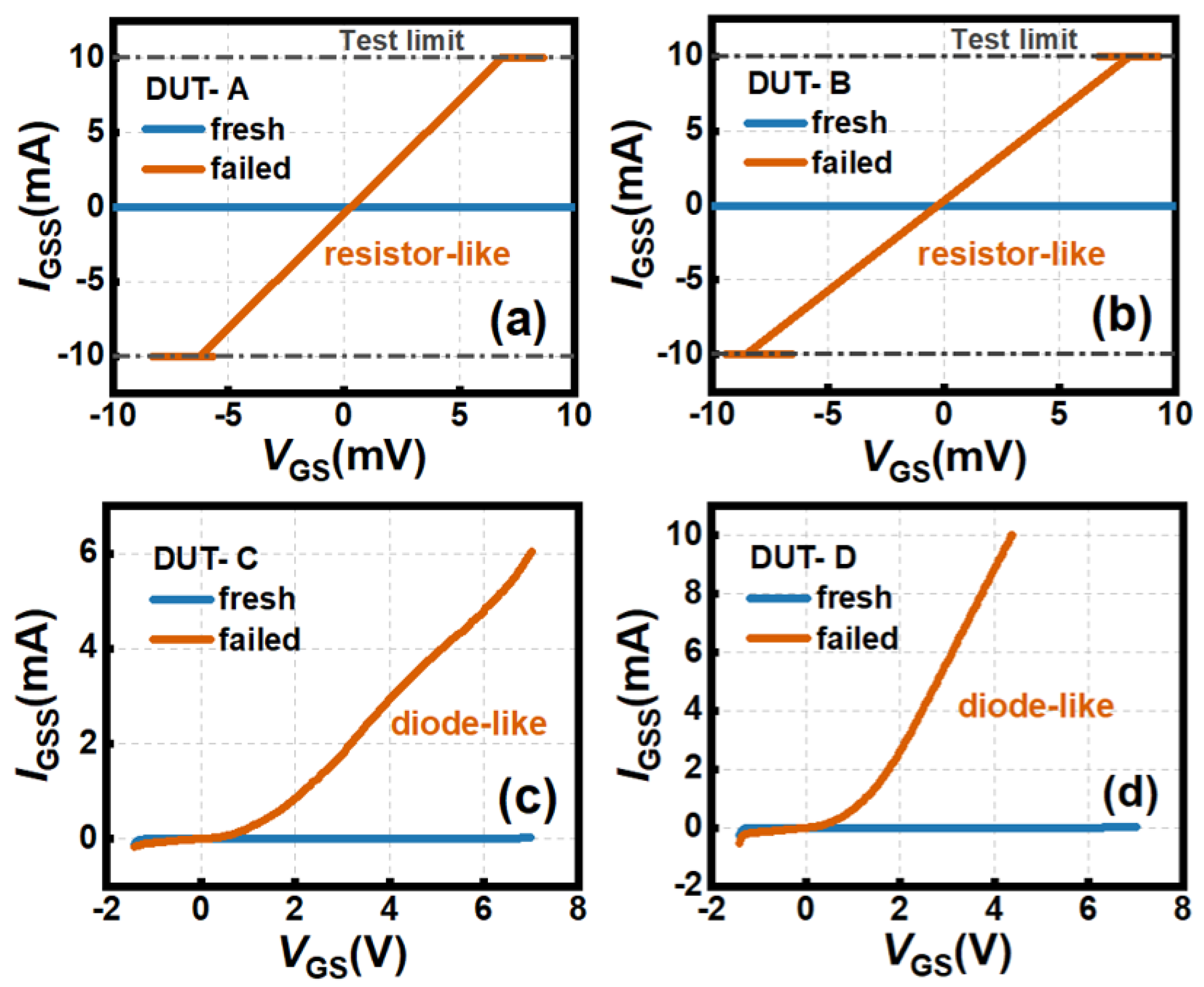

3. Device Failure Mode Analysis

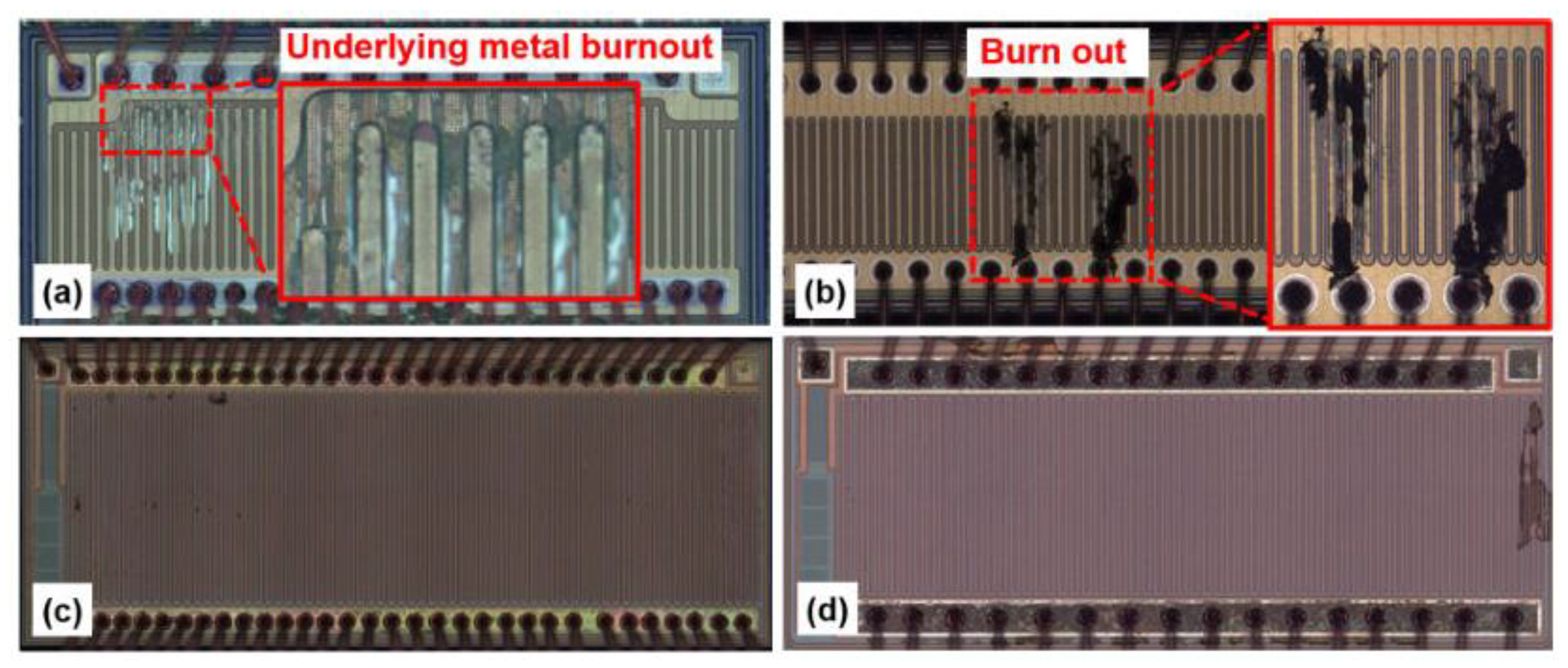

3.1. Failure Mode I

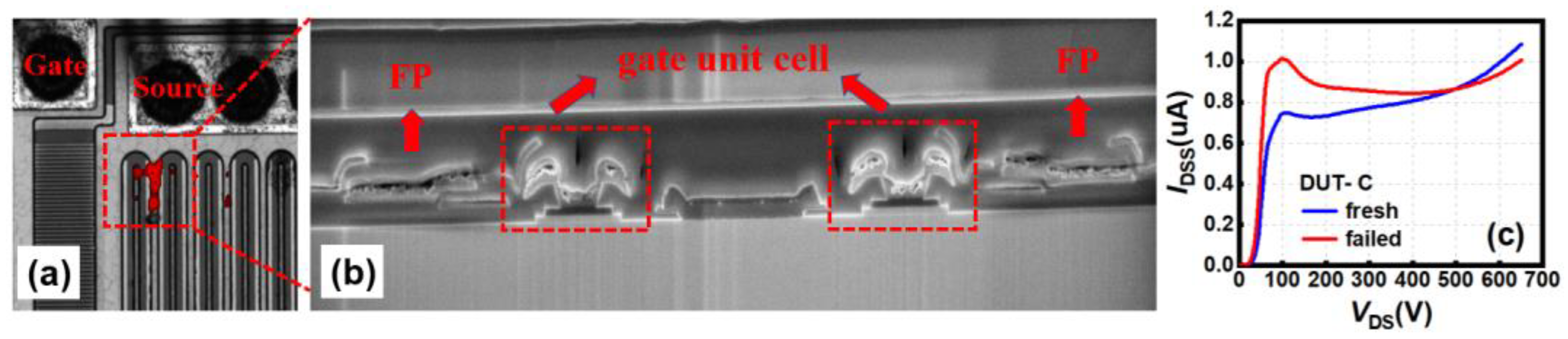

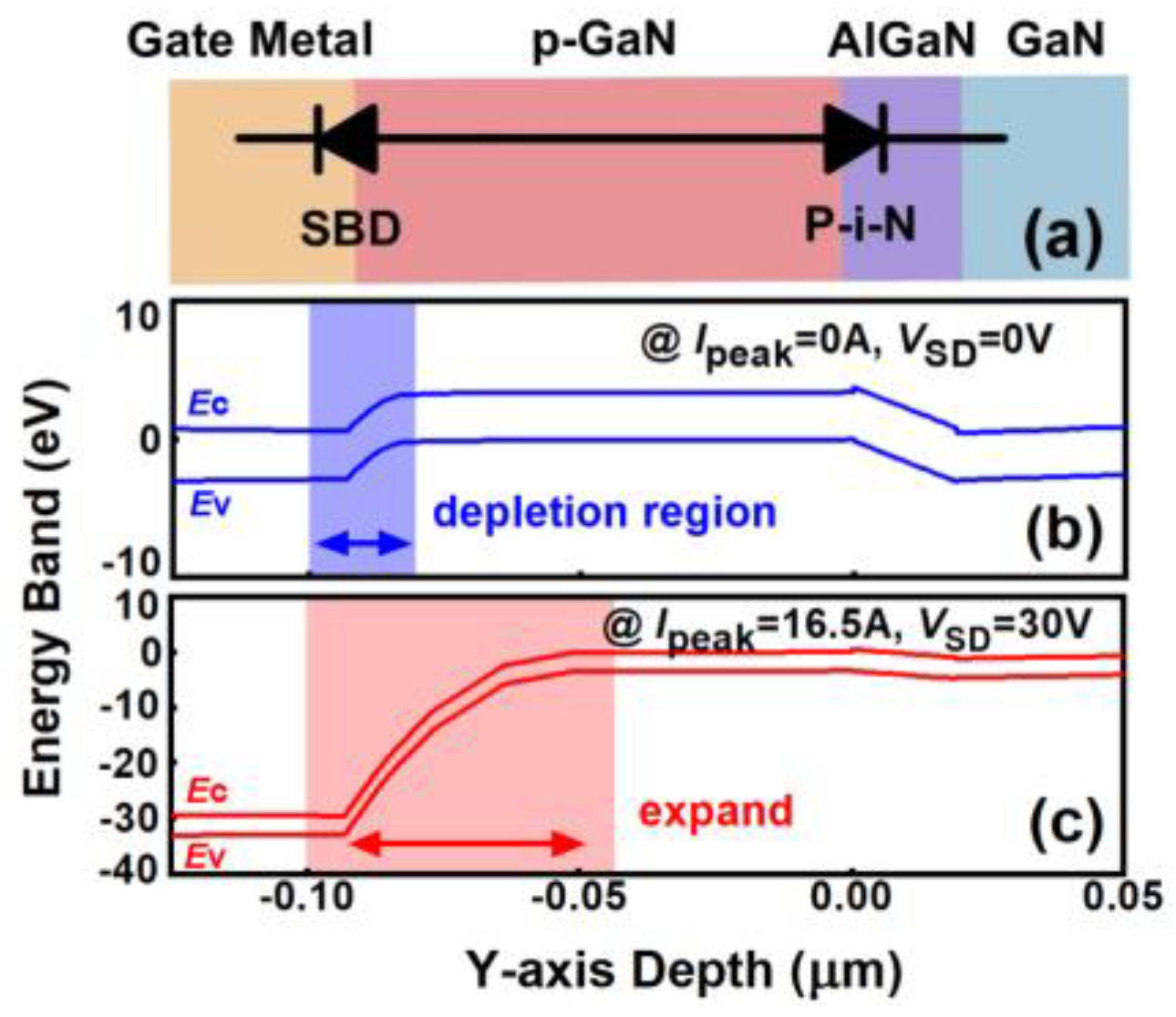

3.2. Failure Mode II

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Chen, K.J.; Häberlen, O.; Lidow, A.; Tsai, C.L.; Ueda, T.; Uemoto, Y. GaN-on-Si Power Technology: Devices and Applications. IEEE Trans. Electron Device 2017, 64, 779–795. [Google Scholar] [CrossRef]

- Chow, T.P. Progress in high voltage SiC and GaN power switching devices. Mater. Sci. Forum 2014, 778–780, 1077–1082. [Google Scholar]

- Sayadi, L.; Iannaccone, G.; Sicre, S.; Häberlen, O.; Curatola, G. Threshold Voltage Instability in p-GaN Gate AlGaN/GaN HFETs. IEEE Trans. Electron Device 2018, 65, 2454–2460. [Google Scholar]

- He, J.; Tang, G.; Chen, K.J. VTH Instability of p-GaN Gate HEMTs Under Static and Dynamic Gate Stress. IEEE Electron Device Lett. 2018, 39, 1576–1579. [Google Scholar] [CrossRef]

- Wang, H.; Wei, J.; Xie, R.; Liu, C.; Tang, G.; Chen, K.J. Maximizing the Performance of 650-V p-GaN Gate HEMTs: Dynamic RON Characterization and Circuit Design Considerations. IEEE Trans. Power Electron. 2017, 32, 5539–5549. [Google Scholar] [CrossRef]

- Zhong, K.; Wei, J.; He, J.; Feng, S.; Wang, Y.; Yang, S.; Chen, K.J. IG- and VGS-Dependent Dynamic RON Characterization of Commercial High-Voltage p-GaN Gate Power HEMTs. IEEE Trans. Ind. Electron. 2022, 69, 8387–8395. [Google Scholar] [CrossRef]

- Bao, Q.; Yang, S.; Sheng, K. UIS Withstanding Capability of GaN E-HEMTs with Schottky and Ohmic p-GaN contact. In Proceedings of the International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020. [Google Scholar]

- Li, S.; Liu, S.; Zhang, C.; Qian, L.; Ge, C.; Xin, S.; Sun, W.; Yang, Z.; Zhu, Y.; Ni, L. Understanding Electrical Parameter Degradations of P-GaN HEMT Under Repetitive Short-Circuit Stresses. IEEE Trans. Power Electron. 2021, 36, 12173–12176. [Google Scholar] [CrossRef]

- Li, H.; Wang, J.; Ren, N.; Xu, H. Investigation of 1200 V SiC MOSFETs’ Surge Reliability. Micromachines 2019, 10, 485. [Google Scholar] [CrossRef] [PubMed]

- Mihaila, A.; Liu, C.; Romano, G.; Bianda, E.; Wirths, S.; Arango, Y.; Knoll, L.; Baschnagel, A.; Boksteen, B. Surge current capability of 6.5kV-rated SiC MOSFETs. In Proceedings of the International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020. [Google Scholar]

- Liu, J.; Zhang, R.; Xiao, M.; Pidaparthi, S.; Cui, H.; Edwards, A.; Baubutr, L.; Drowley, C.; Zhang, Y. Surge Current and Avalanche Ruggedness of 1.2-kV Vertical GaN p-n Diodes. IEEE Trans. Power Electron. 2021, 36, 10959–10964. [Google Scholar] [CrossRef]

- Liu, Y.; Yang, S.; Han, S.; Sheng, K. Investigation of Surge Current Capability of GaN E-HEMTs in The Third Quadrant: The Impact of P-GaN Contact. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 1465–1474. [Google Scholar]

- Liu, Y.; Han, S.; Yang, S.; Sheng, K. Surge Current Capability of GaN E-HEMTs in Reverse Conduction Mode. In Proceedings of the International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 19–23 May 2019. [Google Scholar]

- Wang, X.; Chen, W.; Sun, R.; Liu, C.; Xia, Y.; Xin, Y.; Xu, X.; Wang, F.; Chen, X.; Chen, Y.; et al. Degradation Behavior and Mechanism of GaN HEMTs with P-Type Gate in the Third Quadrant Under Repetitive Surge Current Stress. IEEE Trans. Electron Device 2022, 69, 5733–5741. [Google Scholar] [CrossRef]

- Wang, X.; Chen, W.; Sun, R.; Liu, C.; Chen, X.; Xia, Y.; Xu, X.; Wang, Z.; Luo, P.; Zhang, Y.; et al. Failure Behavior and Mechanism of p-GaN Gate AlGaN/GaN HEMTs in the Third Quadrant Under Repetitive Surge Current Stress. IEEE Trans. Electron Device 2024, 71, 1694–1701. [Google Scholar] [CrossRef]

- Wang, X.; Sun, R.; Xia, Y.; Liu, C.; Chen, X.; Chen, W.; Zhang, B. Gate Damage Mechanism of Schottky-Type p-GaN Gate HEMTs in Reverse Conduction Mode Under Surge Current Stress. In Proceedings of the International Symposium on Power Semiconductor Devices and ICs (ISPSD), Bremen, Germany, 2–6 June 2024. [Google Scholar]

- GS-065-011-1-L. Available online: https://gansystems.com/ (accessed on 1 November 2024).

- GNP1150TCA-Z. Available online: https://rohm.com/ (accessed on 1 November 2024).

- GAN190-650EBE. Available online: https://nexperia.com/ (accessed on 1 November 2024).

- INN700DA190B. Available online: https://innoscience.com/ (accessed on 1 November 2024).

- Black, J.R. Electromigration—A brief survey and some recent results. IEEE Trans. Electron Device 1969, 16, 338–347. [Google Scholar]

| Parameters | DUT-A [17] | DUT-B [18] | DUT-C [19] | DUT-D [20] |

|---|---|---|---|---|

| Voltage Rating (V) | 650 | 650 | 650 | 700 |

| Current Rating (A) | 11 | 11 | 11.5 | 11.5 |

| Typical RDS_ON (mΩ) | 150 | 150 | 138 | 138 |

| p-GaN gate type | Schottky | Schottky | Schottky | Schottky |

| Parameters | DUT-A | DUT-B | DUT-C | DUT-D |

|---|---|---|---|---|

| VTH (V) | 1.44 (initial) | 1.5 (initial) | 1.7 (initial) | 1.61 (initial) |

| 1.47 (16.9 A) | 1.51 (17.3 A) | 1.68 (17.2 A) | 1.34 (17.5 A) | |

| RDS_ON (mΩ) | 179.3 (initial) | 201.2 (initial) | 196.4 (initial) | 198.1 (initial) |

| 188.8 (16.9 A) | 220.6 (17.3 A) | 197.8 (17.2 A) | 186.2 (17.5 A) | |

| IGSS (μA) | 41 (initial) | 76 (initial) | 75 (initial) | 44 (initial) |

| 140 (16.9 A) | 99 (17.3 A) | 3500 (17.2 A) | 2070 (17.5 A) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, K.; Peng, R.; Huang, S.; Wang, L.; Zhu, J.; Duan, E.; Zhang, B.; Zhou, Q. Surge Current Capability and Failure Modes of 650 V p-GaN Gate HEMTs: A Multiphysics Study on Thermal–Electrical Coupling Effects. Electronics 2025, 14, 1321. https://doi.org/10.3390/electronics14071321

Chen K, Peng R, Huang S, Wang L, Zhu J, Duan E, Zhang B, Zhou Q. Surge Current Capability and Failure Modes of 650 V p-GaN Gate HEMTs: A Multiphysics Study on Thermal–Electrical Coupling Effects. Electronics. 2025; 14(7):1321. https://doi.org/10.3390/electronics14071321

Chicago/Turabian StyleChen, Kuangli, Rong Peng, Shuting Huang, Long Wang, Jianggen Zhu, Enchuan Duan, Bo Zhang, and Qi Zhou. 2025. "Surge Current Capability and Failure Modes of 650 V p-GaN Gate HEMTs: A Multiphysics Study on Thermal–Electrical Coupling Effects" Electronics 14, no. 7: 1321. https://doi.org/10.3390/electronics14071321

APA StyleChen, K., Peng, R., Huang, S., Wang, L., Zhu, J., Duan, E., Zhang, B., & Zhou, Q. (2025). Surge Current Capability and Failure Modes of 650 V p-GaN Gate HEMTs: A Multiphysics Study on Thermal–Electrical Coupling Effects. Electronics, 14(7), 1321. https://doi.org/10.3390/electronics14071321