A 0.81–1.46 ppm/∘C High-Order Segmented Curvature-Compensation Bandgap Reference with Dynamic Element Matching Offset Cancellation for a Battery Management System

Abstract

1. Introduction

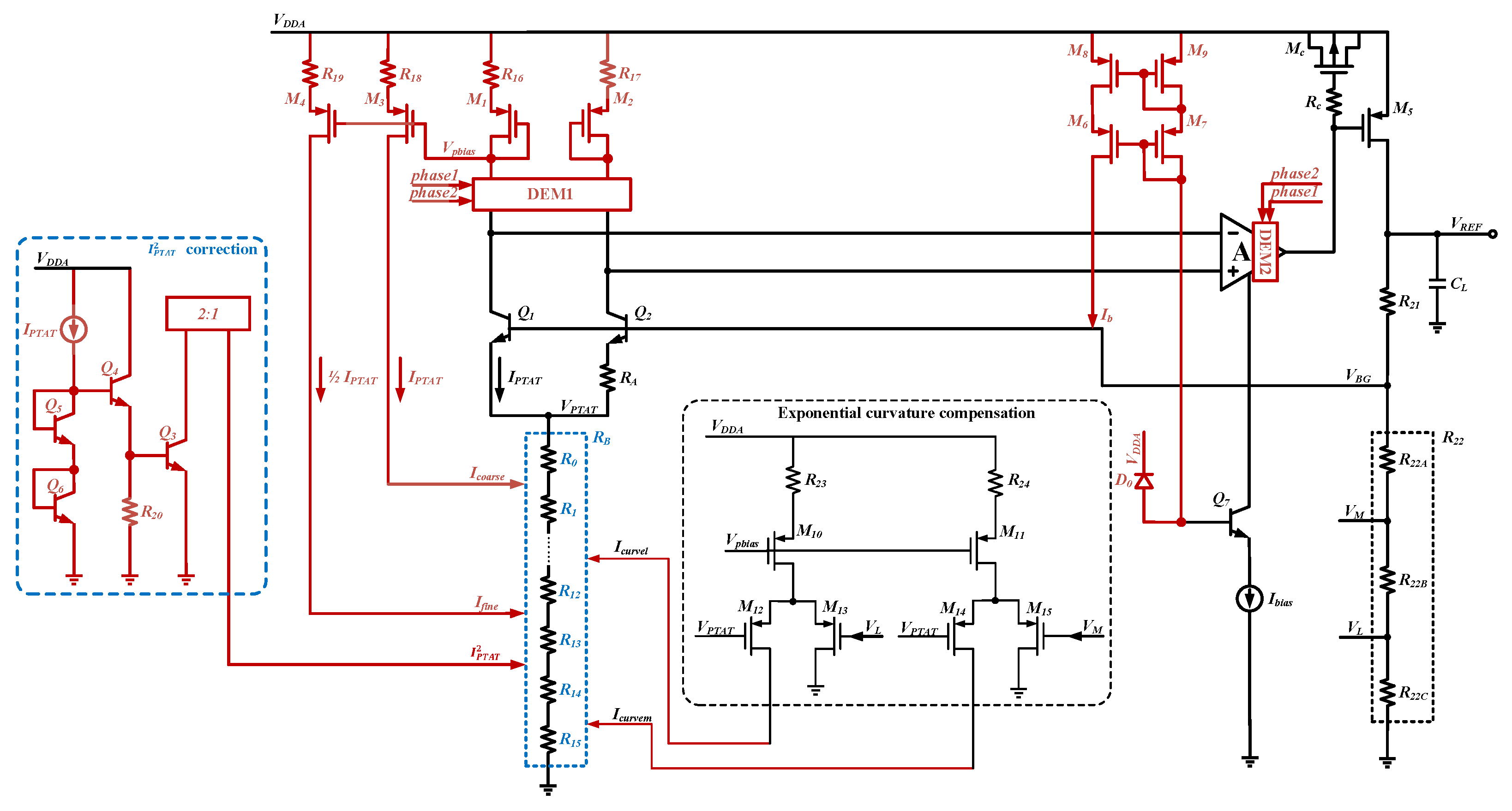

2. Proposed Design and Architecture

2.1. Proposed High-Order Segmented Curvature Compensation

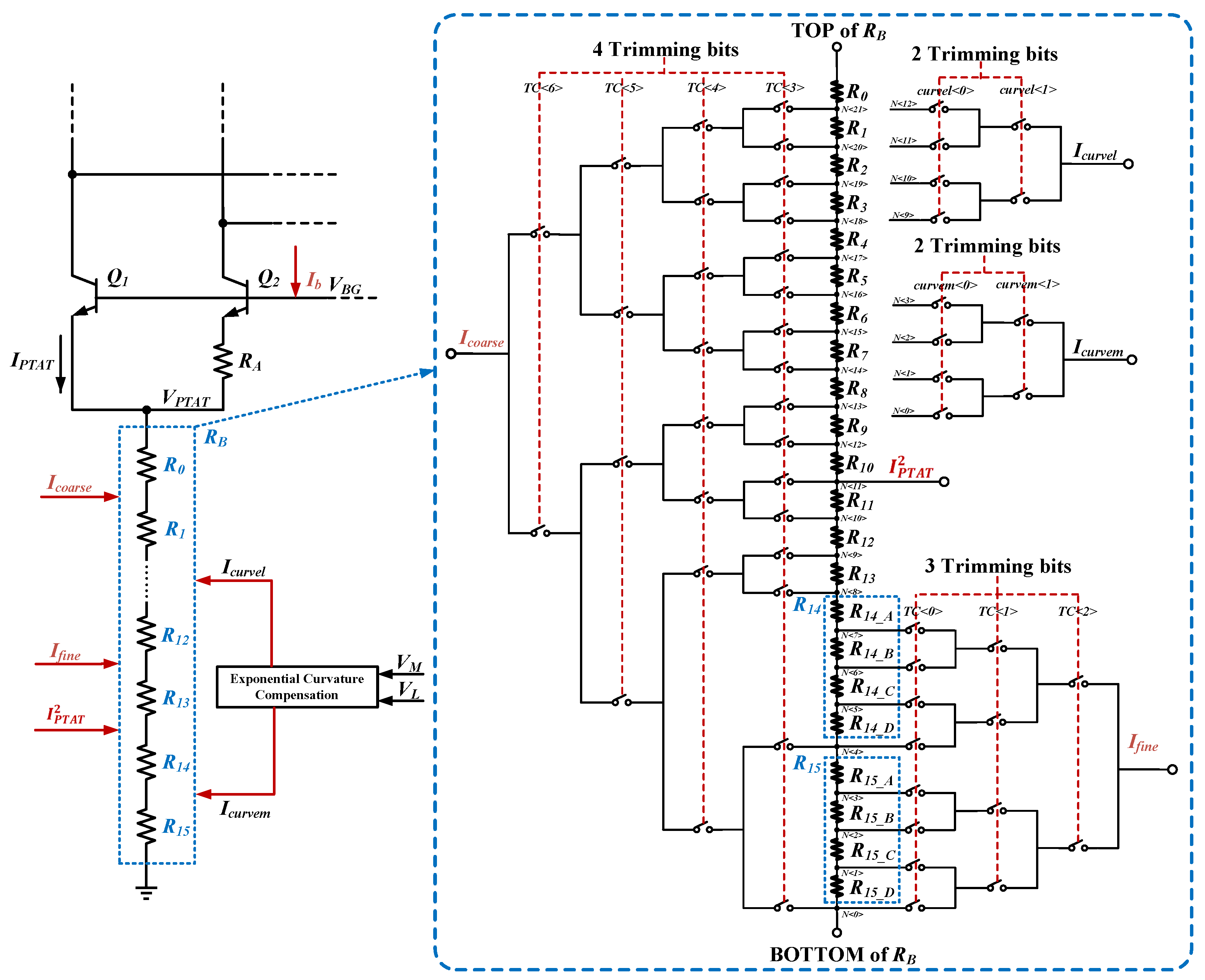

2.2. Trimming Scheme Implementation

2.3. DEM Offset Cancellation

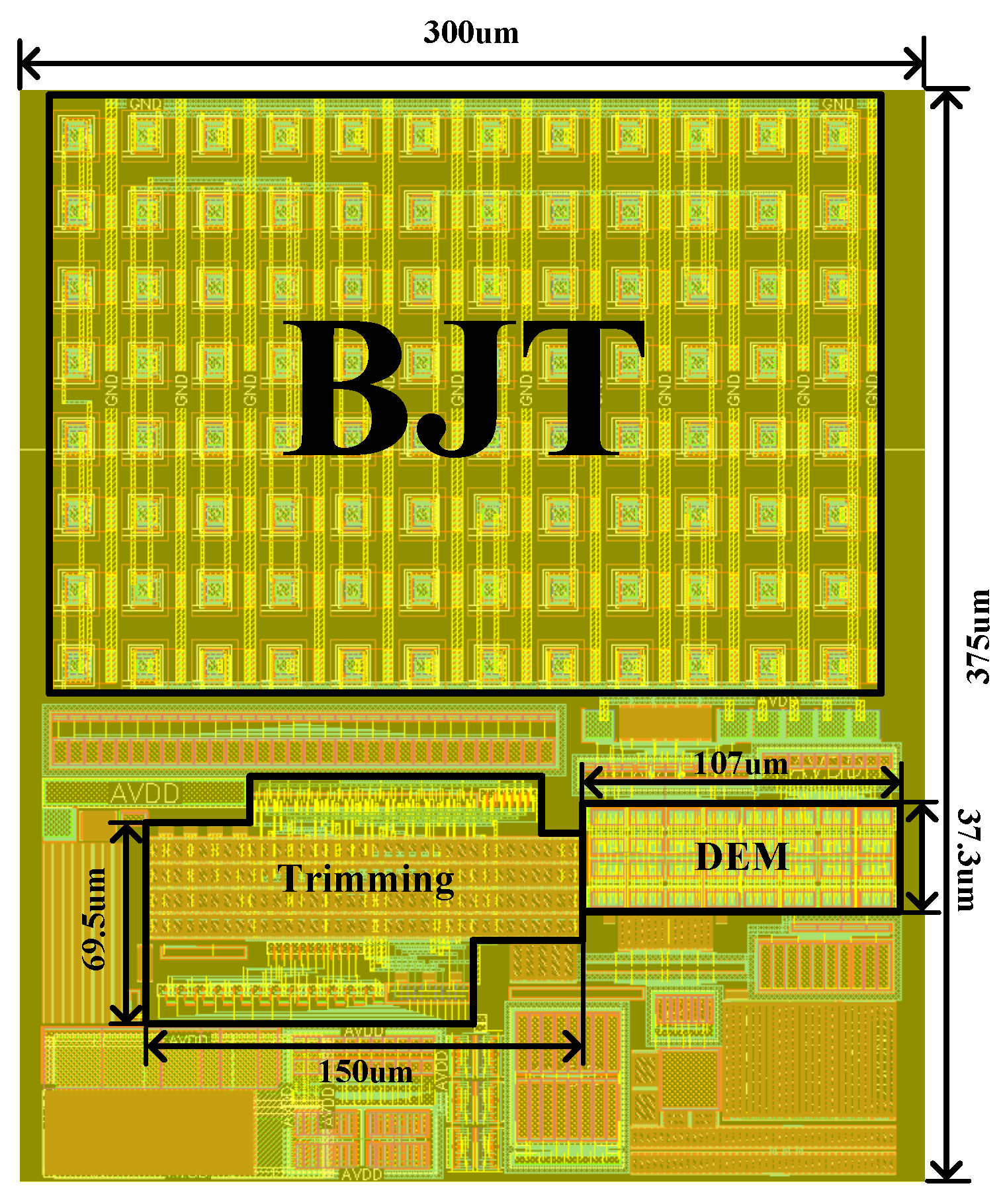

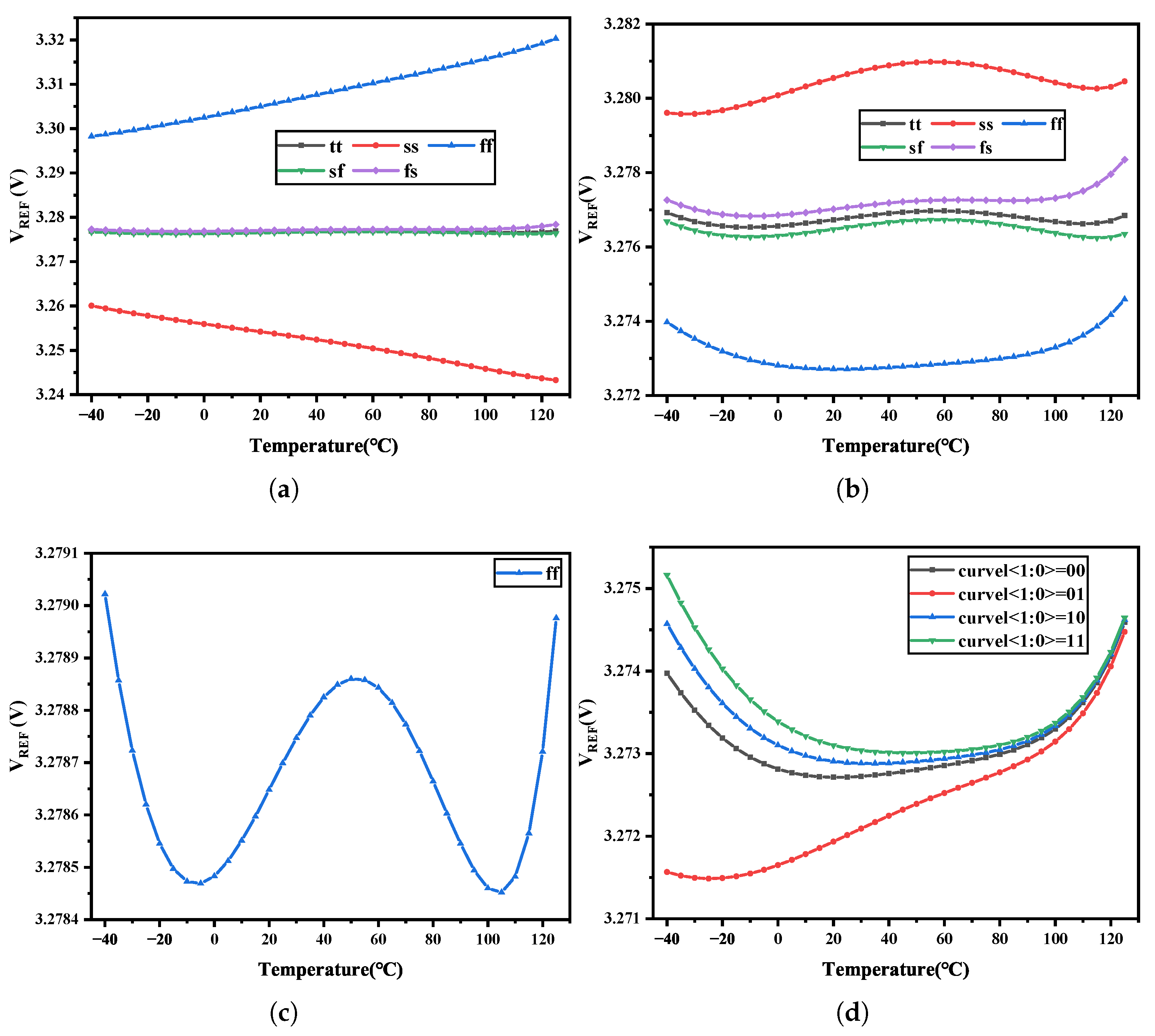

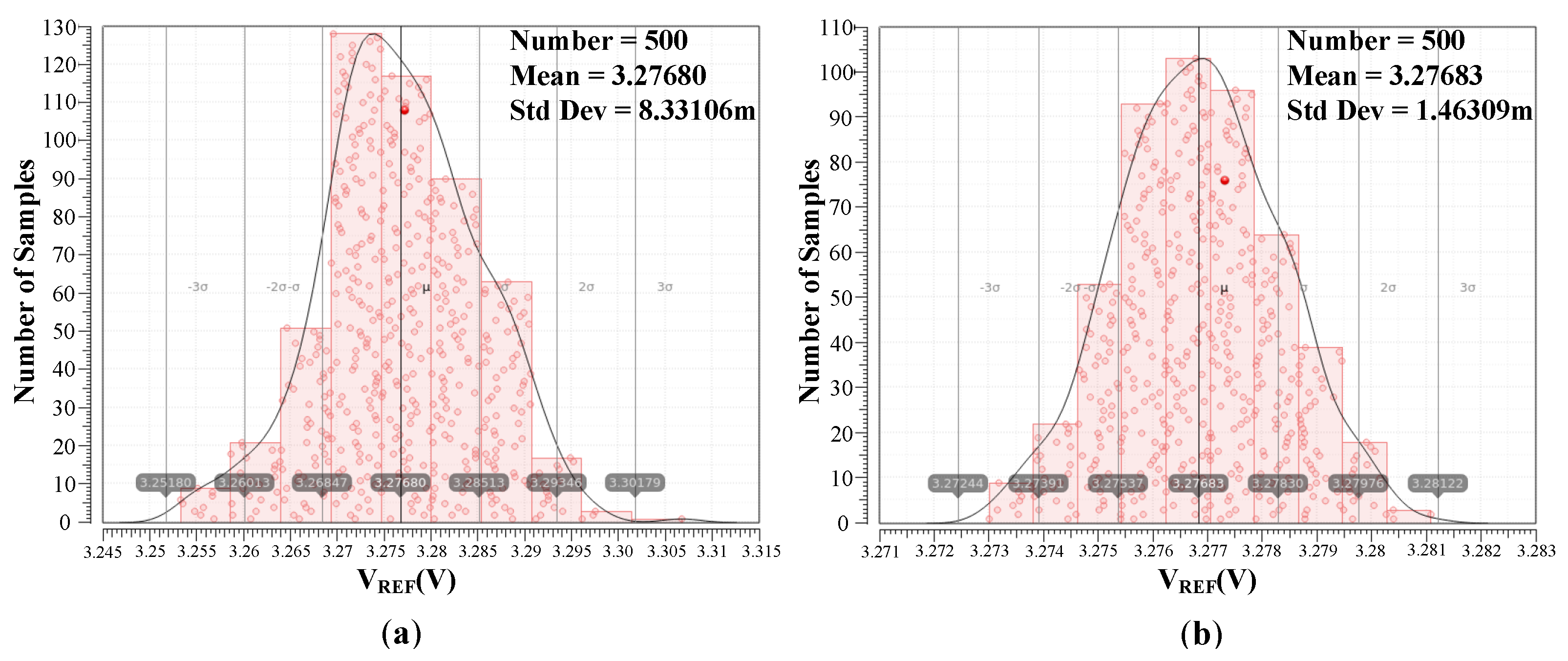

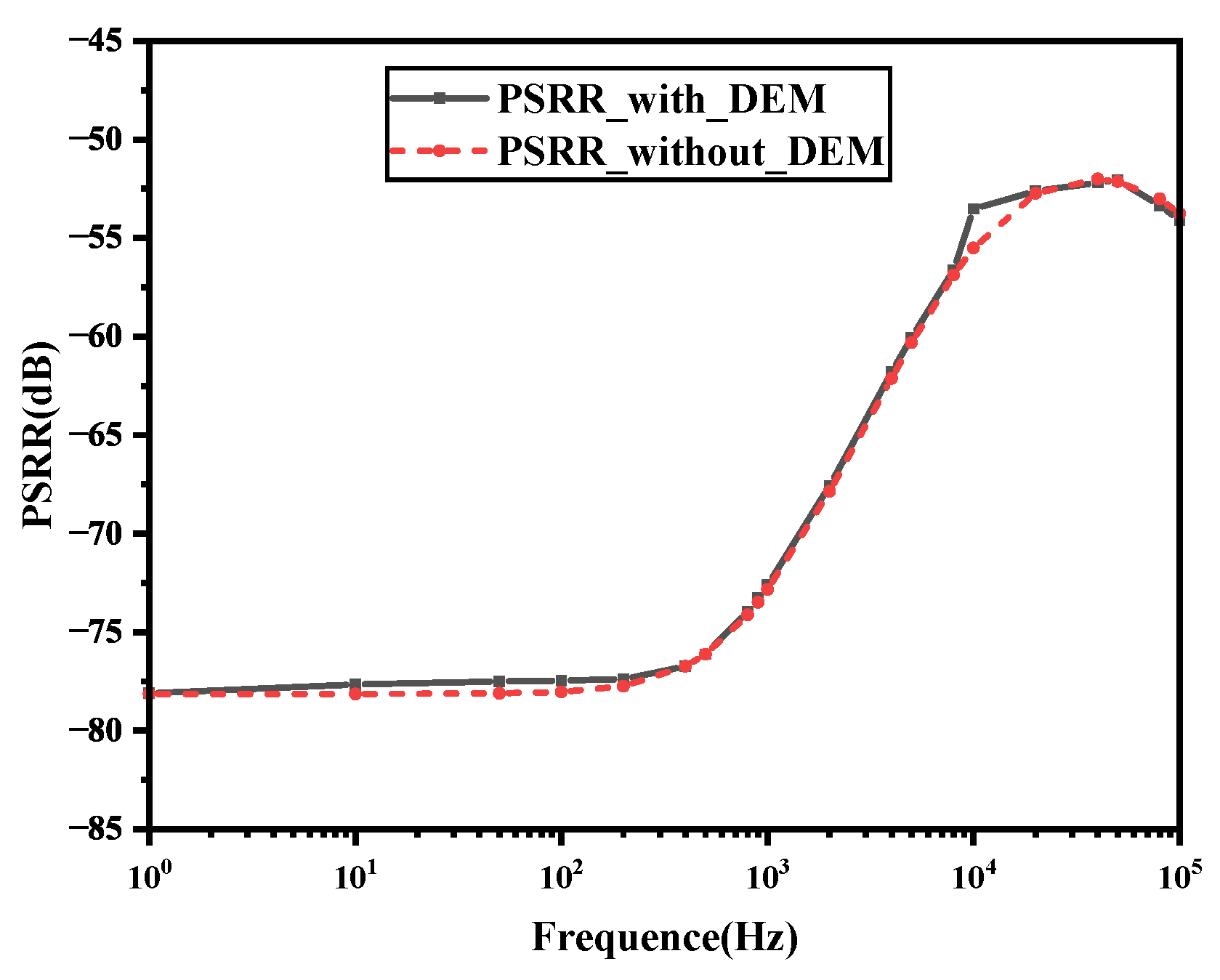

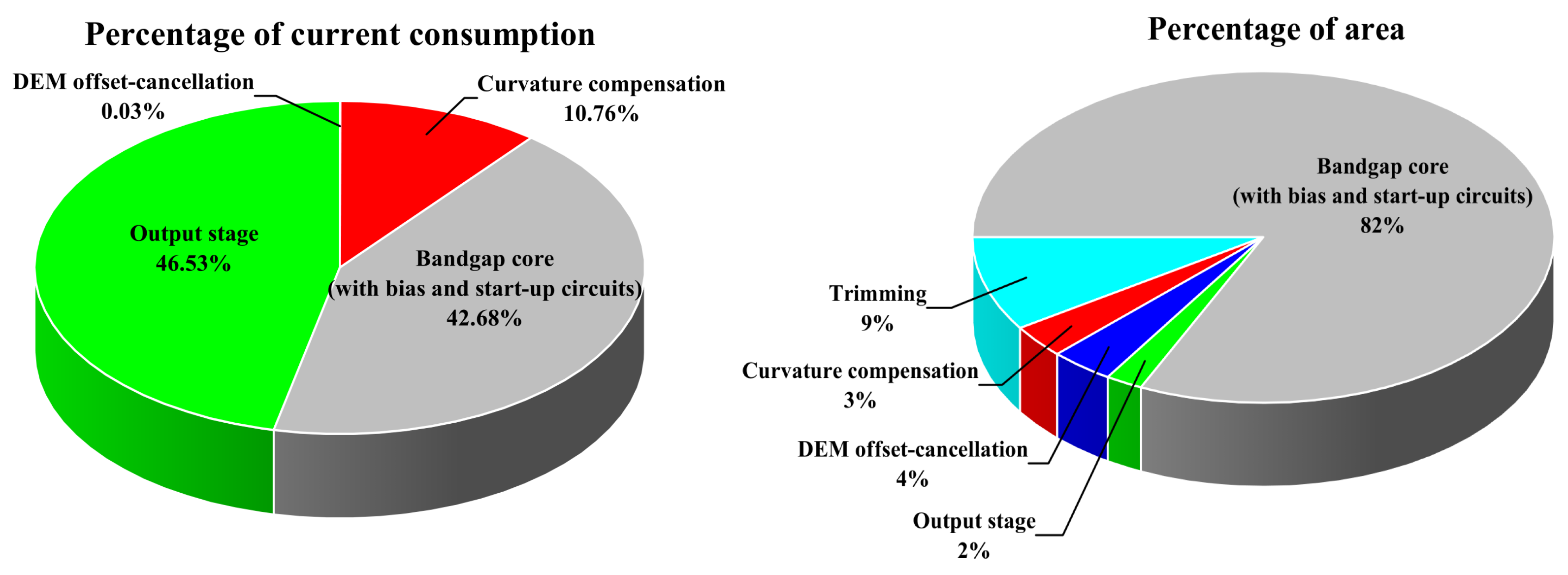

3. Simulation Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Zhu, G.; Yang, Y.; Zhang, Q. A 4.6-ppm/°C High-Order Curvature Compensated Bandgap Reference for BMIC. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1492–1496. [Google Scholar] [CrossRef]

- Boo, J.H.; Cho, K.I.; Kim, H.J.; Lim, J.G.; Kwak, Y.S.; Lee, S.H.; Ahn, G.C. A Single-Trim Switched Capacitor CMOS Bandgap Reference with a 3σ Inaccuracy of +0.02%, −0.12% for Battery-Monitoring Applications. IEEE J. Solid State Circuits 2021, 56, 1197–1206. [Google Scholar] [CrossRef]

- Liu, L.; Liao, X.; Mu, J. A 3.6μVrms Noise, 3 ppm/°C TC Bandgap Reference with Offset/Noise Suppression and Five-Piece Linear Compensation. IEEE Trans. Circuits Syst. Regul. Pap. 2019, 66, 3786–3796. [Google Scholar] [CrossRef]

- Chi-Wa, U.; Law, M.K.; Martins, R.P.; Lam, C.S. Sub-μW Auto-Calibration Bandgap Voltage Reference with 1σ Inaccuracy of ± 0.12. IEEE J. Solid State Circuits 2024, 59, 540–550. [Google Scholar] [CrossRef]

- Vulligaddala, V.B.; Adusumalli, R.; Singamala, S.; Srinivas, M.B. A Digitally Calibrated Bandgap Reference with 0.06% Error for Low-Side Current Sensing Application. IEEE J. Solid State Circuits 2018, 53, 2951–2957. [Google Scholar] [CrossRef]

- Lam, Y.H.; Ki, W.H. CMOS Bandgap References with Self-Biased Symmetrically Matched Current–Voltage Mirror and Extension of Sub-1-V Design. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2010, 18, 857–865. [Google Scholar] [CrossRef]

- Lee, I.; Kim, G.; Kim, W. Exponential curvature-compensated BiCMOS bandgap references. IEEE J. Solid State Circuits 1994, 29, 1396–1403. [Google Scholar] [CrossRef]

- Perry, R.T.; Lewis, S.H.; Brokaw, A.P.; Viswanathan, T.R. A 1.4 V Supply CMOS Fractional Bandgap Reference. IEEE J. Solid State Circuits 2007, 42, 2180–2186. [Google Scholar] [CrossRef]

- Ge, G.; Zhang, C.; Hoogzaad, G.; Makinwa, K.A.A. A Single-Trim CMOS Bandgap Reference with a 3σ Inaccuracy of ±0.15% From −40∘C to 125∘C. IEEE J. Solid State Circuits 2011, 46, 2693–2701. [Google Scholar] [CrossRef]

- Chen, K.; Petruzzi, L.; Hulfachor, R.; Onabajo, M. A 1.16-V 5.8-to-13.5-ppm/°C Curvature-Compensated CMOS Bandgap Reference Circuit With a Shared Offset-Cancellation Method for Internal Amplifiers. IEEE J. Solid State Circuits 2021, 56, 267–276. [Google Scholar] [CrossRef]

- Park, P.; Lee, J.; Cho, S. 3.1 A PVT-Insensitive Sub-Ranging Current Reference Achieving 11.4 ppm/°C from −20 °C to 125 °C. In Proceedings of the 2024 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 19–23 February 2024; Volume 67, pp. 54–56. [Google Scholar] [CrossRef]

- Zhou, Z.K.; Shi, Y.; Wang, Y.; Li, N.; Xiao, Z.; Wang, Y.; Liu, X.; Wang, Z.; Zhang, B. A Resistorless High-Precision Compensated CMOS Bandgap Voltage Reference. IEEE Trans. Circuits Syst. Regul. Pap. 2019, 66, 428–437. [Google Scholar] [CrossRef]

- Huang, S.; Li, M.; Li, H.; Yin, P.; Shu, Z.; Bermak, A.; Tang, F. A Sub-1 ppm/°C Bandgap Voltage Reference with High-Order Temperature Compensation in 0.18 μm CMOS Process. IEEE Trans. Circuits Syst. Regul. Pap. 2022, 69, 1408–1416. [Google Scholar] [CrossRef]

- Hunter, B.L.; Matthews, W.E. A ± 3 ppm/°C Single-Trim Switched Capacitor Bandgap Reference for Battery Monitoring Applications. IEEE Trans. Circuits Syst. Regul. Pap. 2017, 64, 777–786. [Google Scholar] [CrossRef]

- Liao, X.; Zhang, Y.; Zhang, S.; Liu, L. A 3.0 μ Vrms, 2.4 ppm/°C BGR with Feedback Coefficient Enhancement and Bowl-Shaped Curvature Compensation. IEEE Trans. Circuits Syst. Regul. Pap. 2024, 71, 2424–2433. [Google Scholar] [CrossRef]

- Enz, C.; Temes, G. Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization. Proc. IEEE 1996, 84, 1584–1614. [Google Scholar] [CrossRef]

- Duan, Q.; Roh, J. A 1.2-V 4.2-ppm/∘C High-Order Curvature-Compensated CMOS Bandgap Reference. IEEE Trans. Circuits Syst. Regul. Pap. 2015, 62, 662–670. [Google Scholar] [CrossRef]

- Fu, X.; Colombo, D.M.; Yin, Y.; El-Sankary, K. Low Noise, High PSRR, High-Order Piecewise Curvature Compensated CMOS Bandgap Reference. IEEE Access 2022, 10, 110970–110982. [Google Scholar] [CrossRef]

- Zhang, Z.; Zhan, C.; Wang, L.; Law, M.K. A −40 °C–125 °C 0.4-μA Low-Noise Bandgap Voltage Reference with 0.8-mA Load Driving Capability Using Shared Feedback Resistors. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 4033–4037. [Google Scholar] [CrossRef]

| Corner | Before Trimming (ppm/°C) | After Trimming (ppm/°C) |

|---|---|---|

| tt | 0.81 | 0.81 |

| ss | 31.05 | 1.46 |

| ff | 40.72 | 1.06 |

| sf | 0.9 | 0.9 |

| fs | 2.81 | 1.19 |

| Specification | This Work * | [1] | [2] | [9] | [10] | [14] | [18] |

|---|---|---|---|---|---|---|---|

| Year | 2024 | 2019 | 2021 | 2011 | 2021 | 2017 | 2022 |

| Application | BMS | BMIC | BMS | - | - | BMS | - |

| Technology | 0.18 m BCD | 0.18 m | 0.18 m | 0.16 m | 0.13 m | 0.8 m BiCMOS | 0.18 m |

| Supply Voltage (V) | 5 ± 10% | 3.5–5 | 1.8 ± 10% | 1.8 ± 10% | 3.3 | 5.2 | 2.7–3.3 |

| Reference Voltage (V) | 3.2768 | 3.11 | 1.1419 | 1.0875 | 1.16 | 3.657 | 1.2 |

| Reference Type | DC | DC | Switched Cap. | DC | DC | Switched Cap. | DC |

| Temp. Range (°C) | −40~125 | −40~130 | −40~125 | −40~125 | −40~150 | −40~110 | −10~110 |

| Trimmed TC (ppm/°C) | 0.81–1.46 | 4.6–6.3 | 3.3–5.5 | 5–12 | 5.78–13.5 | ±3 (3) | 5–15 |

| Volt. / (%) | 0.045@Room Temp. 0.049@Entire Temp. Range | - | +0.02, −0.12 (3) | ±0.15 (3) | 0.54 | - | - |

| Line Regulation (%/V) | 0.022 | 0.031 | - | - | 0.03 | - | 0.005 |

| Load Regulation (mV/mA) | 0.022 | - | - | - | - | - | - |

| Curvature Correction | Yes | Yes | Yes | Yes | Yes | No | Yes |

| Trimming | Yes | Yes | Yes | Yes | No | Yes | No |

| Output Stage | Yes | Yes | No | No | No | Yes | Yes |

| Current Consumption (A) | 144 | 108 | 17 | 55 | 120 | 750 | 150 |

| PSRR (dB) | −78@10 HZ | −92*@100 HZ | −76@DC | −74@DC | −82@10 Hz | −127@DC | −80@DC |

| Area (mm2) | 0.1125 | 0.2225 | 0.38 | 0.12 | 0.08 | 0.28 | 0.448 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xu, J.; Wang, W.; Lin, Y.; Ramiah, H.; Li, X. A 0.81–1.46 ppm/∘C High-Order Segmented Curvature-Compensation Bandgap Reference with Dynamic Element Matching Offset Cancellation for a Battery Management System. Electronics 2025, 14, 1322. https://doi.org/10.3390/electronics14071322

Xu J, Wang W, Lin Y, Ramiah H, Li X. A 0.81–1.46 ppm/∘C High-Order Segmented Curvature-Compensation Bandgap Reference with Dynamic Element Matching Offset Cancellation for a Battery Management System. Electronics. 2025; 14(7):1322. https://doi.org/10.3390/electronics14071322

Chicago/Turabian StyleXu, Jingkai, Wei Wang, Yude Lin, Harikrishnan Ramiah, and Xiaochao Li. 2025. "A 0.81–1.46 ppm/∘C High-Order Segmented Curvature-Compensation Bandgap Reference with Dynamic Element Matching Offset Cancellation for a Battery Management System" Electronics 14, no. 7: 1322. https://doi.org/10.3390/electronics14071322

APA StyleXu, J., Wang, W., Lin, Y., Ramiah, H., & Li, X. (2025). A 0.81–1.46 ppm/∘C High-Order Segmented Curvature-Compensation Bandgap Reference with Dynamic Element Matching Offset Cancellation for a Battery Management System. Electronics, 14(7), 1322. https://doi.org/10.3390/electronics14071322