Challenges in Fault Diagnosis of Nonlinear Circuits

Abstract

1. Introduction

2. Fault Diagnosis of Nonlinear Circuits

2.1. Testability and Test Selection

2.2. Simulation Before Test Methods and Artificial Intelligence-Based Approaches

2.3. Simulation After Test Methods

2.4. Fault Diagnosis of DC-DC Converters

3. Challenges in Fault Diagnosis of Nonlinear Circuits

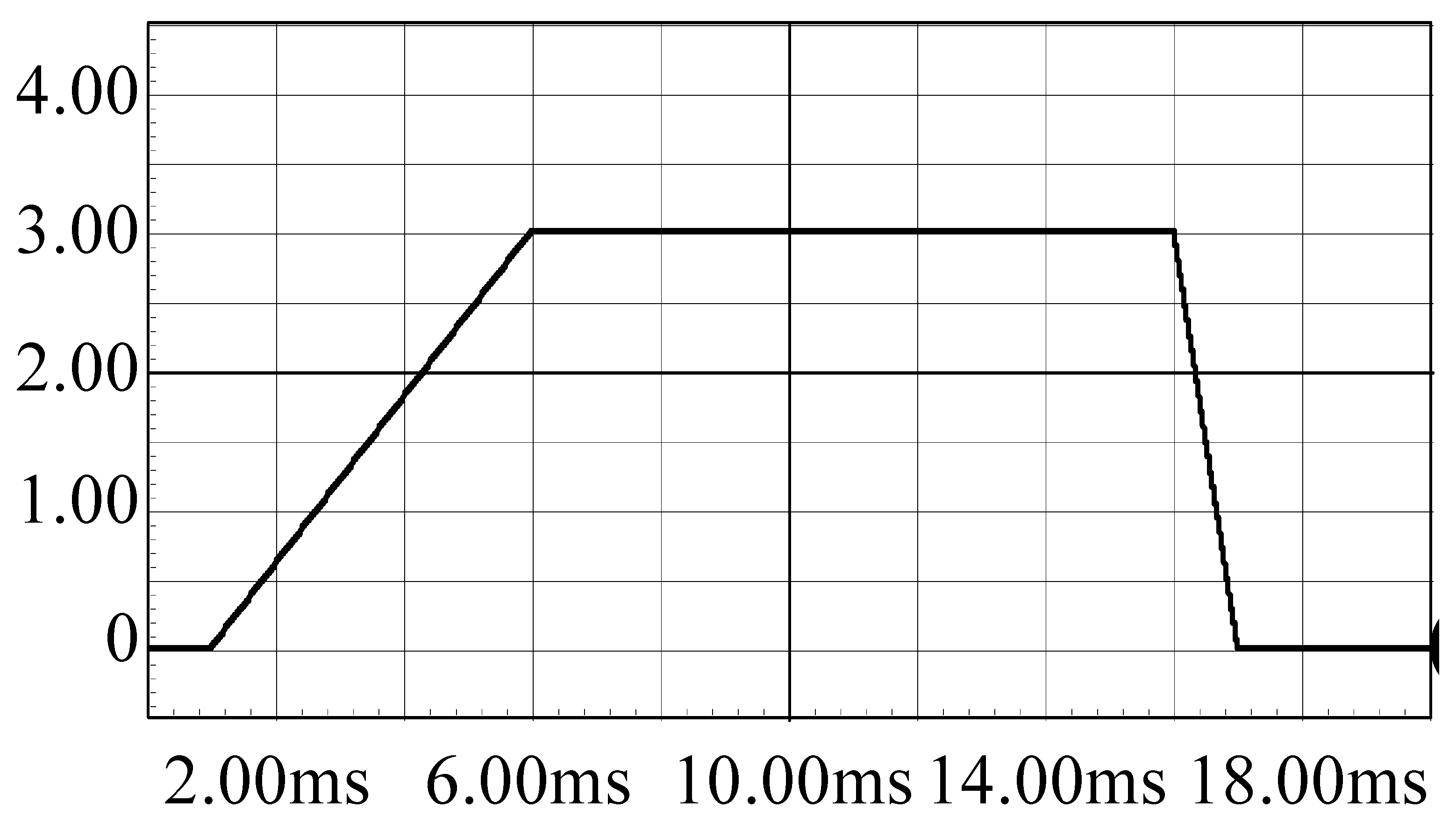

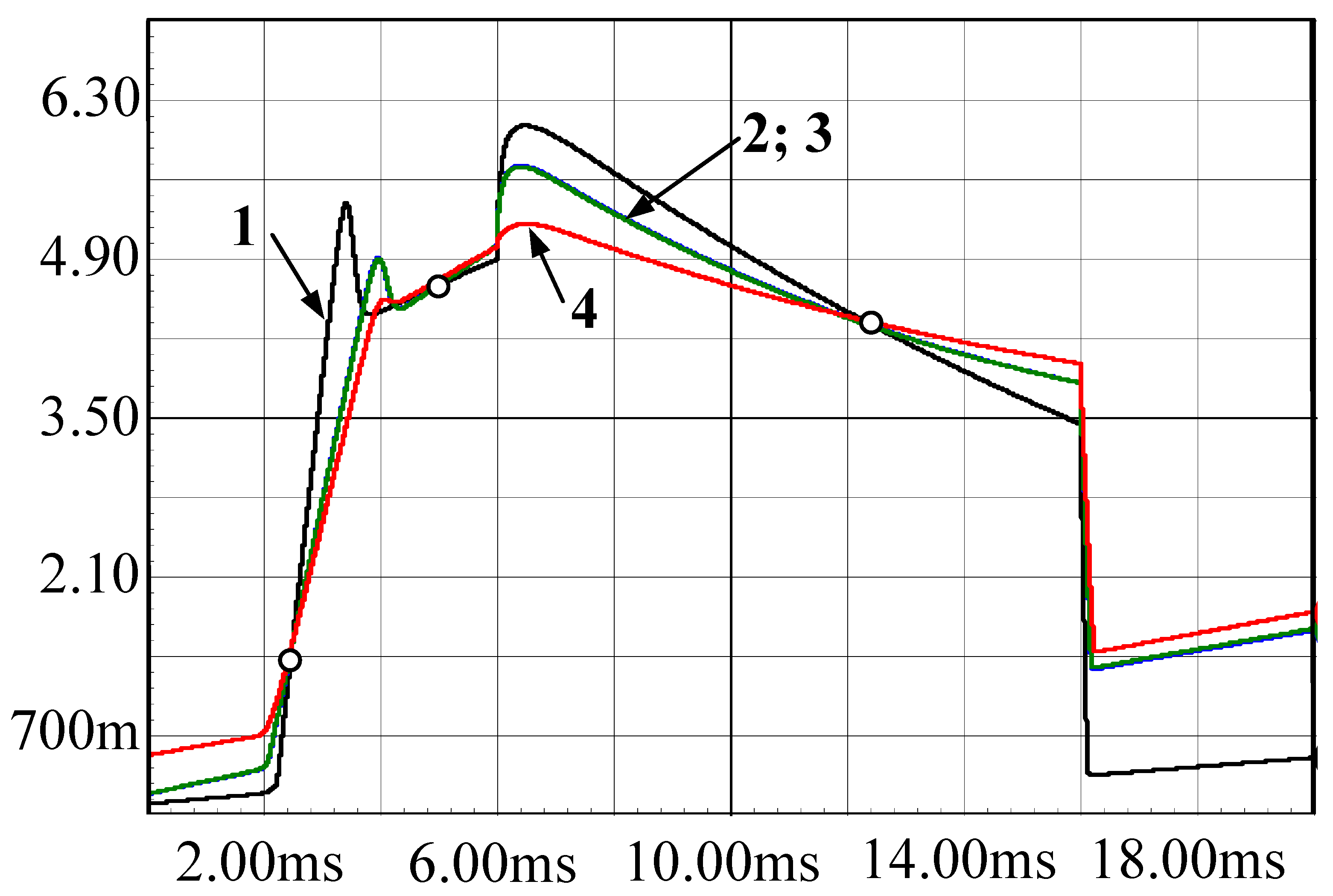

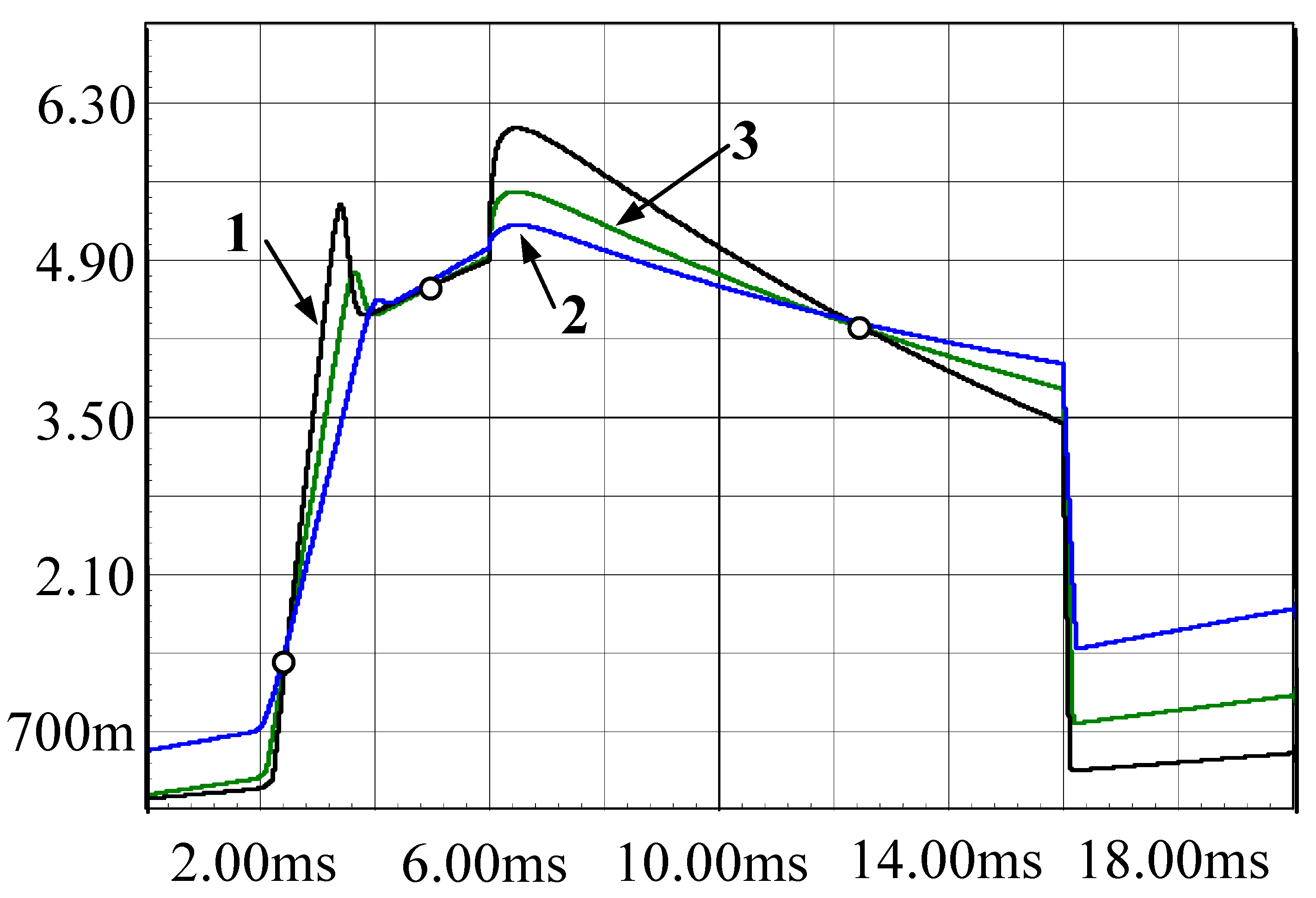

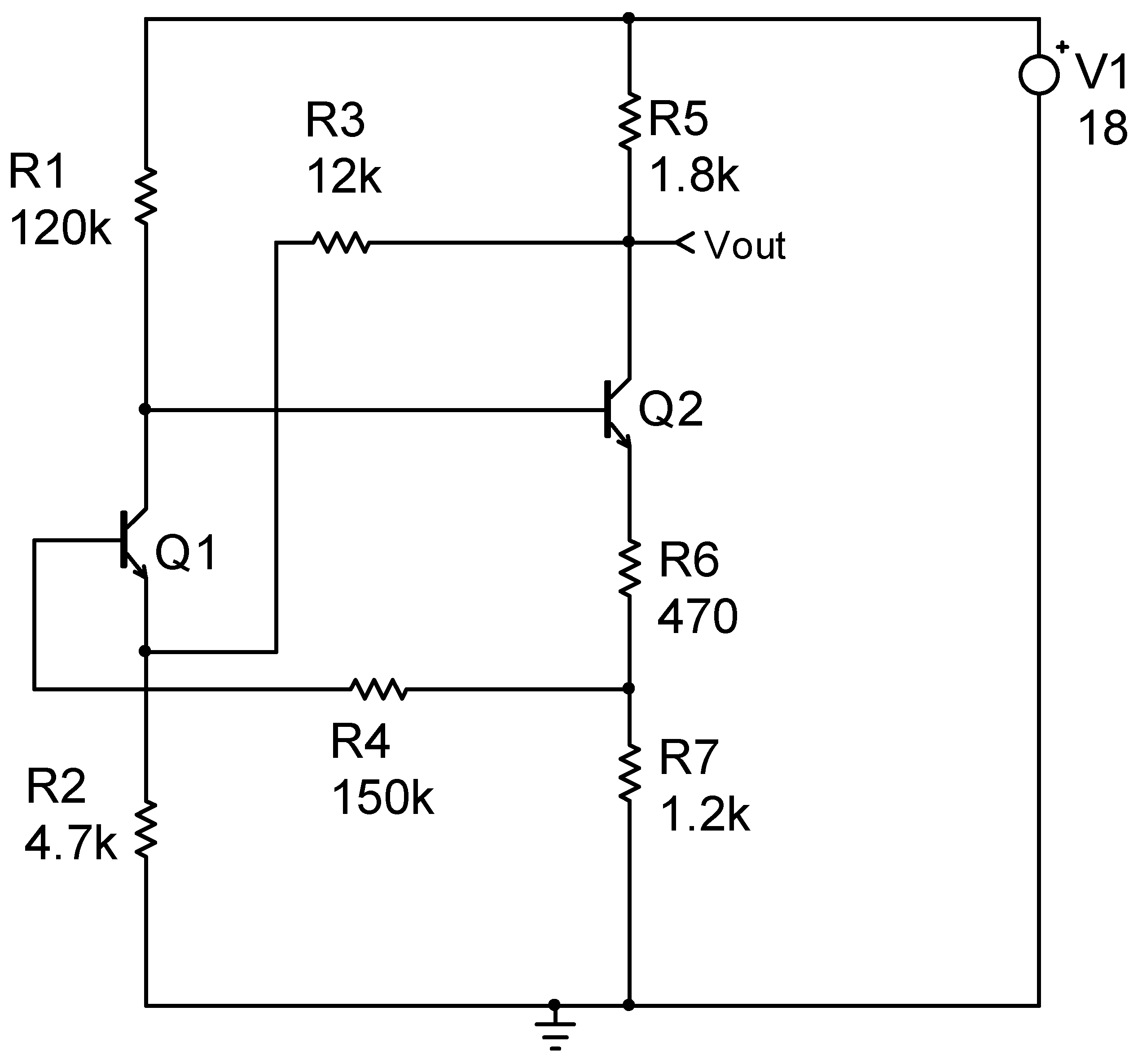

3.1. Ambiguity of Solutions in the Time Domain

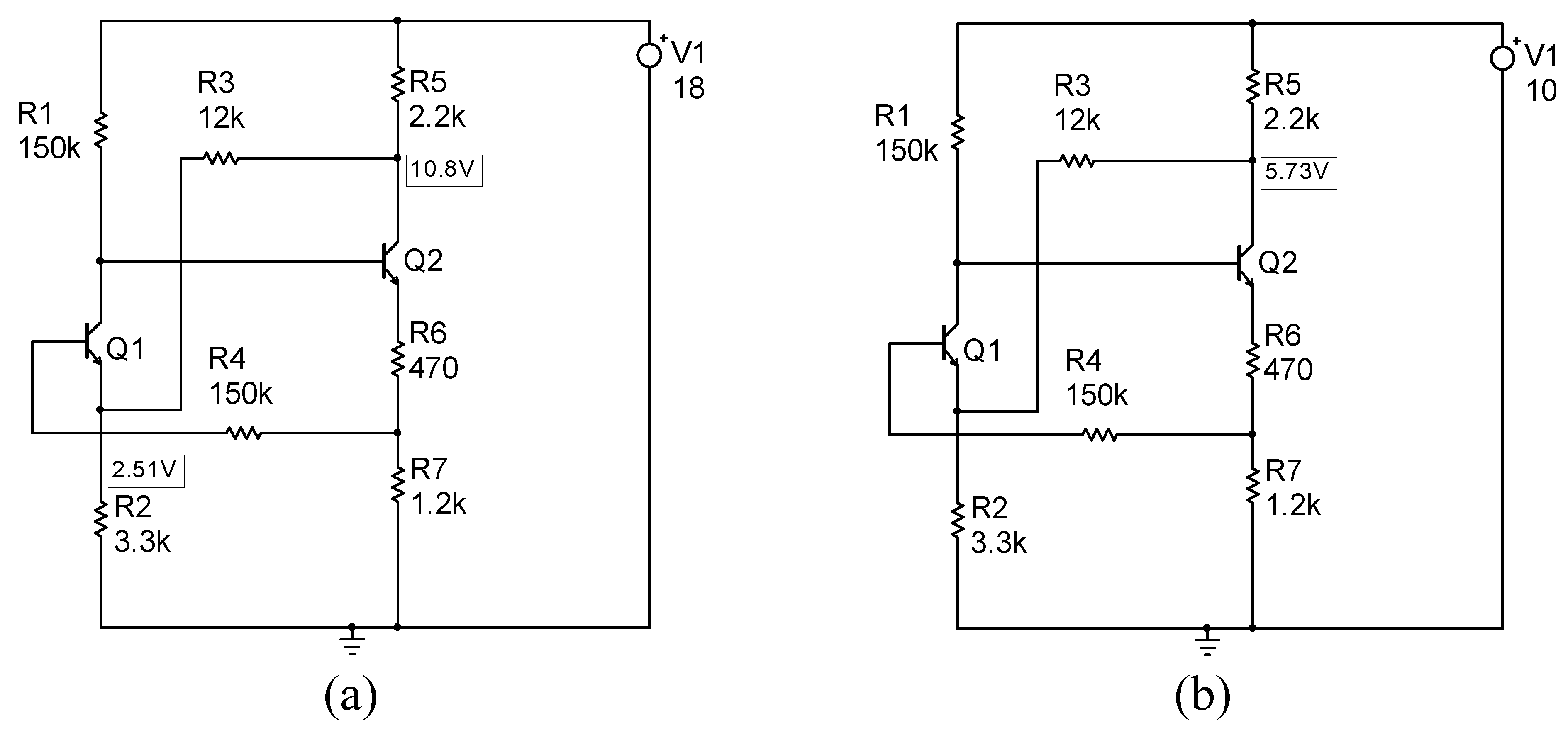

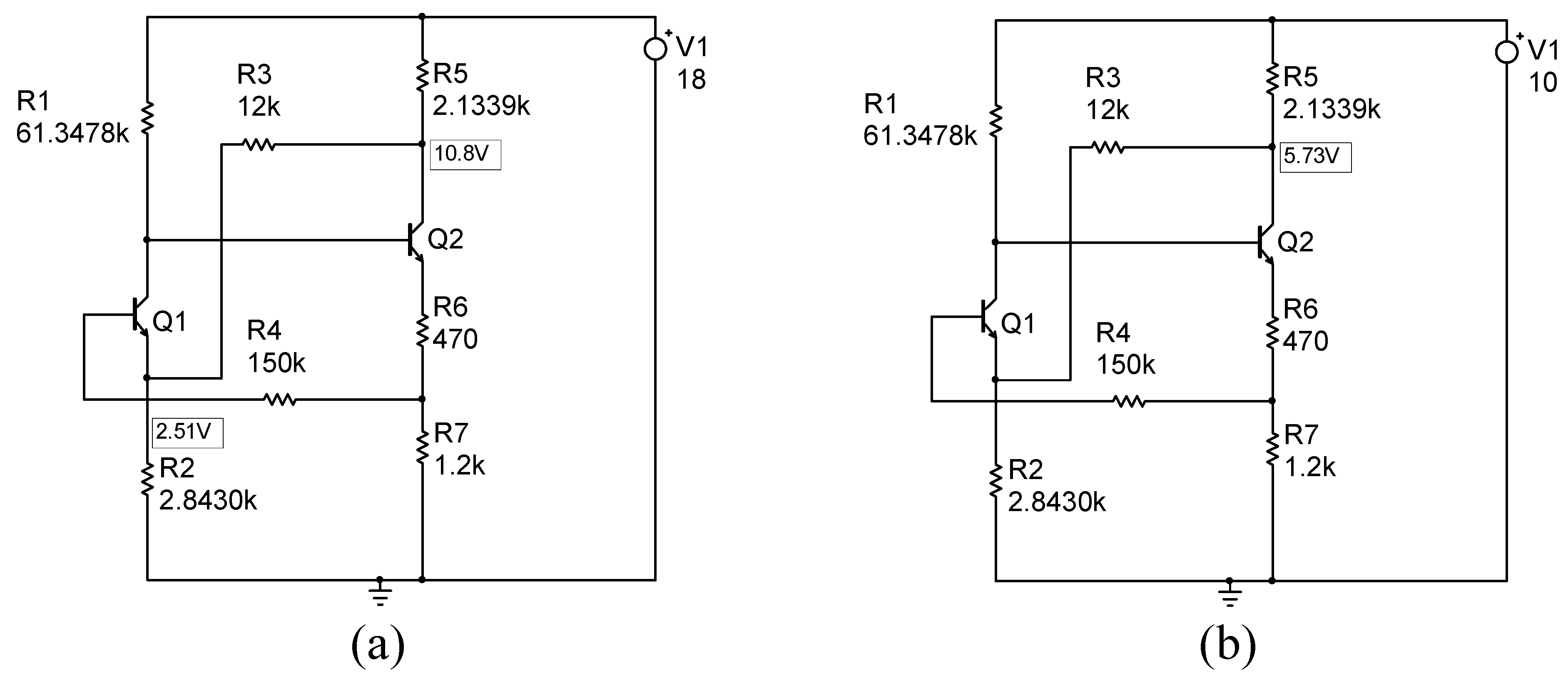

3.2. Ambiguity of Solutions in the DC Domain

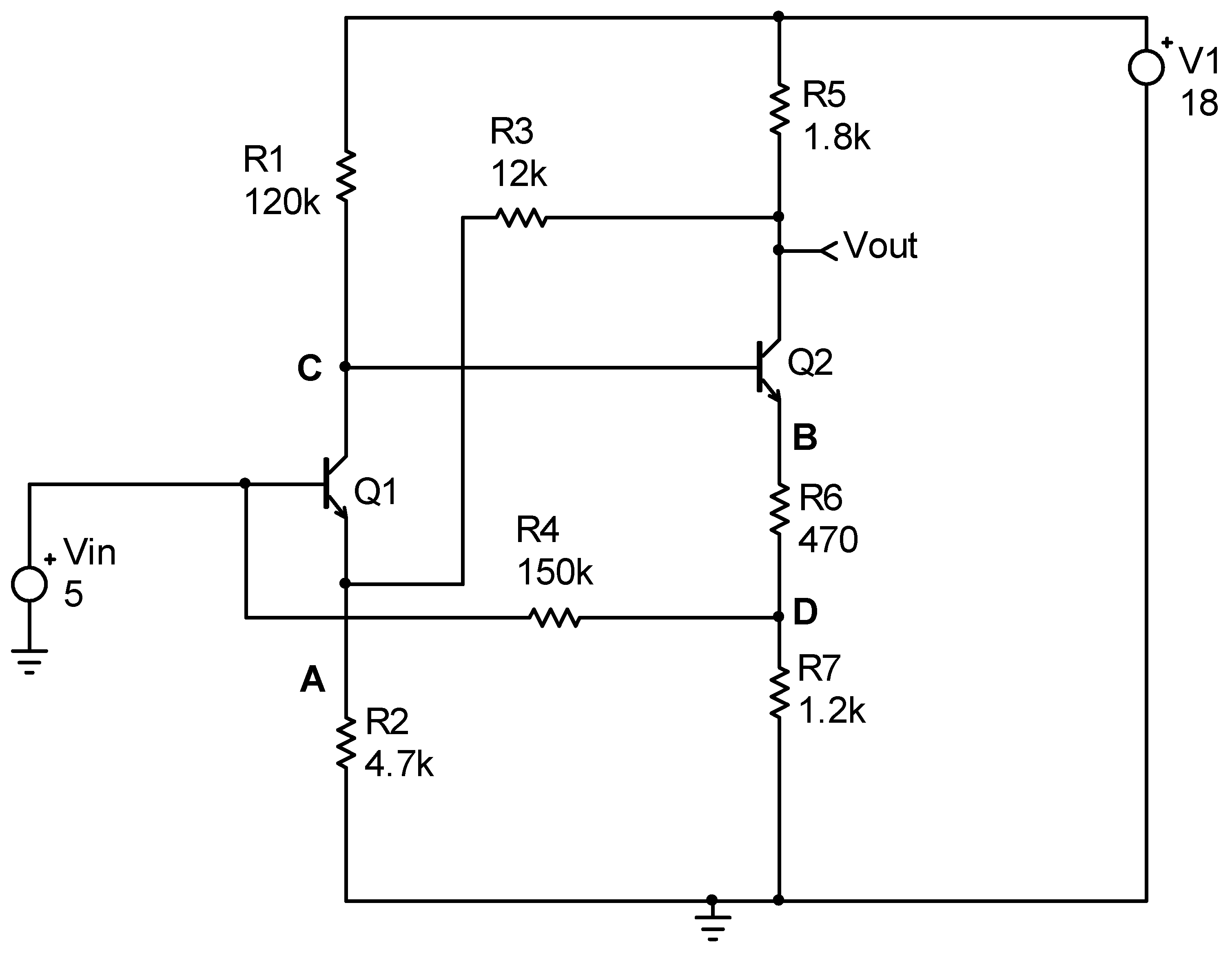

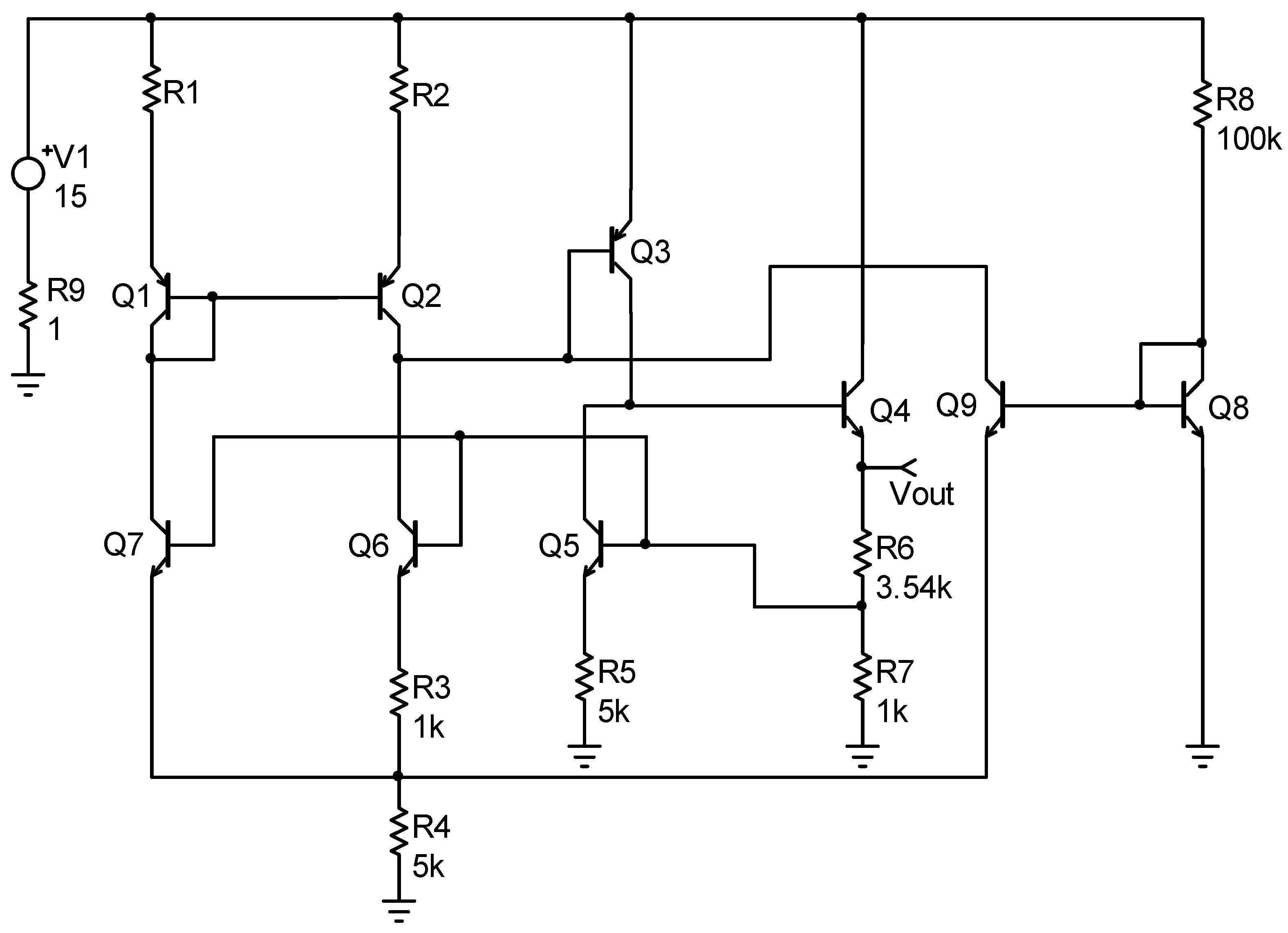

3.3. The Problem of Multiple Operating Point

3.4. The Issue of Self-Heating

4. Conclusions

Funding

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Abbreviations

| AC | Alternating Current |

| AI | Artificial Intelligence |

| ANN | Artificial Neural Network |

| BPNN | Back Propagation Neural Network |

| DC | Direct Current |

| FD | Fault Dictionary |

| FPGA | Field-Programmable Gate Array |

| HMM | Hidden Markov Model |

| IC | Integrated Circuit |

| LSSVM | Least Square Support Vector Machine |

| NN | Neural Network |

| NTE | Nonlinear Test Equation |

| PCA | Principal Component Analysis |

| PSO | Particle Swarm Optimization |

| PWL | Piecewise-Linear |

| SAT | Simulation After Test |

| SBT | Simulation Before Test |

| SVM | Support Vector Machine |

References

- Binu, D.; Kariyappa, B. A survey on fault diagnosis of analog circuits: Taxonomy and state of the art. AEU-Int. J. Electron. Commun. 2017, 73, 68–83. [Google Scholar] [CrossRef]

- Deng, Y.; Chen, T.; Zhang, D. Diagnosis of incipient faults in nonlinear analog circuits based on high order moment fractional transform. J. Electron. Test. 2020, 36, 485–498. [Google Scholar] [CrossRef]

- Kabisatpathy, P.; Barua, A.; Sinha, S. Fault diagnosis of analog integrated circuits. In Frontiers in Electronic Testing; Springer: Dordrecht, The Netherlands, 2005. [Google Scholar]

- Khemani, V.; Azarian, M.H.; Pecht, M.G. Learnable wavelet scattering networks: Applications to fault diagnosis of analog circuits and rotating machinery. Electronics 2022, 11, 451. [Google Scholar] [CrossRef]

- Yuan, H.; Shi, Y.; Li, L.; Ling, G.; Zeng, J.; Wang, Z. Fault diagnosis in analog circuits using a multi-input Convolutional Neural Network with feature attention. Computation 2025, 13, 94. [Google Scholar] [CrossRef]

- Bandler, J.; Salama, A. Fault diagnosis of analog circuits. Proc. IEEE 1985, 73, 1279–1325. [Google Scholar] [CrossRef]

- Hochwald, W.; Bastian, J. A dc approach for analog fault dictionary determination. IEEE Trans. Circuits Syst. 1979, 26, 523–529. [Google Scholar] [CrossRef]

- Deng, Y.; Shi, Y.; Zhang, W. Diagnosis of incipient faults in nonlinear analog circuits. Metrol. Meas. Syst. 2012, 19, 203–218. [Google Scholar] [CrossRef][Green Version]

- Gao, T.; Yang, J.; Jiang, S.; Li, Y. An incipient fault diagnosis method based on complex convolutional self-attention autoencoder for analog circuits. IEEE Trans. Ind. Electron. 2024, 71, 9727–9736. [Google Scholar] [CrossRef]

- Liu, X.; Yang, H.; Gao, T.; Yang, J. A novel incipient fault diagnosis method for analogue circuits based on an MLDLCN. Circuits Syst. Signal Process. 2023, 43, 684–710. [Google Scholar] [CrossRef]

- Liu, X.; Guo, X.; Yang, H. A novel analogue circuit incipient soft fault diagnosis method based on a multiscale fault diagnosis network. Circuits Syst. Signal Process. 2025, 1–20. [Google Scholar] [CrossRef]

- Yang, J.; Li, Y.; Gao, T. An incipient fault diagnosis method based on Att-GCN for analogue circuits. Meas. Sci. Technol. 2023, 34, 045002. [Google Scholar] [CrossRef]

- Fang, X.; Qu, J.; Liu, B.; Chai, Y. Overcoming limited fault data: Intermittent fault detection in analog circuits via improved GAN. IEEE Trans. Instrum. Meas. 2024, 73, 3500111. [Google Scholar] [CrossRef]

- Gao, S.; Zhao, K. Intermittent fault diagnosis of dynamic systems with model uncertainty and disturbance: An adaptive nondeterministic observer approach. IEEE Trans. Reliab. 2025, 74, 4131–4142. [Google Scholar] [CrossRef]

- Gao, S.; Zhao, K.; Si, W.; Wen, C. Time-varying threshold and signed-rectified regressor design of diagnosis observer for analog circuits with intermittent fault. IEEE Trans. Instrum. Meas. 2025, 74, 3510513. [Google Scholar] [CrossRef]

- Tadeusiewicz, M.; Hałgas, S.; Kuczynski, A. New aspects of fault diagnosis of nonlinear analog circuits. Int. J. Electron. Telecommun. 2015, 61, 83–93. [Google Scholar] [CrossRef]

- Prasad, V.C.; Babu, N.S.C. On minimal set of test nodes for fault dictionary of analog circuit fault diagnosis. J. Electron. Test. 1995, 7, 255–258. [Google Scholar] [CrossRef]

- Prasad, V.C.; Rao Pinjala, S.N. Fast algorithms for selection of test nodes of an analog circuit using a generalized fault dictionary approach. Circ. Syst. Signal Process. 1995, 14, 707–724. [Google Scholar] [CrossRef]

- Starzyk, J.; Liu, D.; Liu, Z.H.; Nelson, D.; Rutkowski, J. Entropy-based optimum test points selection for analog fault dictionary techniques. IEEE Trans. Instrum. Meas. 2004, 53, 754–761. [Google Scholar] [CrossRef]

- Luo, H.; Lu, W.; Wang, Y.; Wang, L. A new test point selection method for analog continuous parameter fault. J. Electron. Test. 2017, 33, 339–352. [Google Scholar] [CrossRef]

- Tang, X.; Xu, A.; Niu, S. KKCV-GA-based method for optimal analog test point selection. IEEE Trans. Instrum. Meas. 2017, 66, 24–32. [Google Scholar] [CrossRef]

- Khanlari, M.; Ehsanian, M. A test point selection approach for DC analog circuits with large number of predefined faults. Analog Integr. Circuits Signal Process. 2020, 102, 225–235. [Google Scholar] [CrossRef]

- Chang, Y.; Xu, X.; Deng, K.; Xu, Y.; Tu, B.; Gao, X.; Wei, Q. An analog circuit fault diagnosis method incorporating multi-objective selection of measurement nodes. Electronics 2025, 14, 1528. [Google Scholar] [CrossRef]

- Navid, N.; Willson, A. A theory and an algorithm for analog circuit fault diagnosis. IEEE Trans. Circ. Syst. 1979, 26, 440–457. [Google Scholar] [CrossRef]

- Stenbakken, G.; Souders, T.; Stewart, G. Ambiguity groups and testability. IEEE Trans. Instrum. Meas. 1989, 38, 941–947. [Google Scholar] [CrossRef]

- Liu, R.W. Testing and Diagnosis of Analog Circuits and Systems; Van Nostrand Reinhold: New York, NY, USA, 1991. [Google Scholar]

- Fenton, W.; McGinnity, T.; Maguire, L. Fault diagnosis of electronic systems using intelligent techniques: A review. IEEE Trans. Syst. Man Cybern. Part C 2001, 31, 269–281. [Google Scholar] [CrossRef]

- Chen, Y.; Peng, K.; Huang, D.; Tang, Q. Evaluating and optimizing conventional training circuits for analog fault diagnosis via transfer learning. IEEE Trans. Instrum. Meas. 2025, 74, 3549015. [Google Scholar] [CrossRef]

- Dieste-Velasco, M. Soft fault diagnosis in analog electronic circuits using supervised machine learning. Integration 2025, 104, 102482. [Google Scholar] [CrossRef]

- Du, X.; Jia, S.; Hu, Y.; Wang, Y. Fault diagnosis of analog circuits using an improved BiTCN combined with BiLSTM. J. Electron. Test. 2025, 41, 411–430. [Google Scholar] [CrossRef]

- Gao, J.; Guo, J.; Yuan, F.; Yi, T.; Zhang, F.; Shi, Y.; Li, Z.; Ke, Y.; Meng, Y. An exploration into the fault diagnosis of analog circuits using enhanced golden eagle optimized 1D-Convolutional Neural Network (CNN) with a time-frequency domain input and attention mechanism. Sensors 2024, 24, 390. [Google Scholar] [CrossRef]

- Hou, Z.; Liu, J.; Yu, S. Enhanced analog circuit fault diagnosis via continuous wavelet transform and dual-stream convolutional fusion. Sci. Rep. 2025, 15, 19828. [Google Scholar] [CrossRef]

- Puvaneswari, G. Parametric faults detection in analog circuits using variable ranking-based feature selection method and optimized SVM model. Meas. Sci. Rev. 2025, 25, 30–39. [Google Scholar] [CrossRef]

- Puvaneswari, G. SPOT faults: Parametric fault detection in linear analog circuit via sooty egret optimization based iterative decisioned CNN. Circuits Syst. Signal Process. 2025, 44, 7226–7250. [Google Scholar] [CrossRef]

- Singhal, M.; Ahmad, G. Fault Diagnosis in Analog Circuits Using Stacking Ensemble Machine Learning Approach. Circuits Syst. Signal Process. 2025, 44, 6255–6275. [Google Scholar] [CrossRef]

- You, D.; Liu, S.; Yuan, Y.; Zhang, Y. BCSSA-VMD and ICOA-ELM based fault diagnosis method for analogue circuits. Analog Integr. Circuits Signal Process. 2025, 123, 20. [Google Scholar] [CrossRef]

- Yue, Z.; He, L.; He, J.; Yang, G.; Yang, Y.; An, Y. A method of redundant feature suppression in circuit output positions for analog circuit soft and hard fault diagnosis. J. Electron. Test. 2025, 41, 441–465. [Google Scholar] [CrossRef]

- Zhou, X.; Tang, X.; Liang, W. A novel analog circuit fault diagnosis method based on multi-channel 1D-resnet and wavelet packet transform. Analog Integr. Circuits Signal Process. 2024, 121, 25–38. [Google Scholar] [CrossRef]

- Zhou, N.; Huang, J.; Zhao, Y.; Chen, S.; Zhao, J.; Long, F. Data-Driven Soft Fault Diagnosis for Analog Circuits Based on Contrastive Learning. IEEE Trans. Instrum. Meas. 2025, 74, 3559311. [Google Scholar] [CrossRef]

- Fedi, G.; Giomi, R.; Manetti, S.; Piccirilli, M. A symbolic approach for testability evaluation in fault diagnosis of nonlinear analog circuits. In Proceedings of the IEEE International Symposium on Circuits and Systems, Monterey, CA, USA, 31 May–3 June 1998; Volume 6, pp. 9–12. [Google Scholar] [CrossRef]

- Salama, A.; Starzyk, J.; Bandler, J. A unified decomposition approach for fault location in large analog circuits. IEEE Trans. Circuits Syst. 1984, 31, 609–622. [Google Scholar] [CrossRef]

- Starzyk, J.A.; Dai, H. A decomposition approach for testing large analog networks. J. Electron. Test. 1992, 3, 181–195. [Google Scholar] [CrossRef]

- Toczek, W.; Zielonko, R.; Adamczyk, A. A method for fault diagnosis of nonlinear electronic circuits. Measurement 1998, 24, 79–86. [Google Scholar] [CrossRef]

- Worsman, M.; Wong, M. Nonlinear circuit fault diagnosis with large change sensitivity. In Proceedings of the IEEE International Conference on Electronics, Circuits and Systems, Lisboa, Portugal, 7–10 September 1998; Volume 2, pp. 225–228. [Google Scholar] [CrossRef]

- Worsman, M.; Wong, M. Non-linear analog circuit fault diagnosis with large change sensitivity. Int. J. Circuit Theory Appl. 2000, 28, 281–303. [Google Scholar] [CrossRef]

- Rutkowski, J. A dc approach for analog fault dictionary determination. In Proceedings of the European Conference on Circuit Theory and Design, Davos, Switzerland, 30 August–3 September 1993; pp. 877–880. [Google Scholar]

- Rutkowski, J. The dc fault dictionary—A neural network approach. In Proceedings of the European Conference on Circuit Theory & Design, Istanbul, Turkey, 27–31 August 1995; pp. 295–298. [Google Scholar]

- Rutkowski, J.; Machniewski, J. Integer-code DC fault dictionary. In Proceedings of the IEEE International Symposium on Circuits and Systems), Geneva, Switzerland, 28–31 May 2000; Volume 5, pp. 713–716. [Google Scholar] [CrossRef]

- Catelani, M.; Gori, M. On the application of neural networks to fault diagnosis of electronic analog circuits. Measurement 1996, 17, 73–80. [Google Scholar] [CrossRef]

- Variyam, P.; Chatterjee, A. Specification-driven test generation for analog circuits. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2000, 19, 1189–1201. [Google Scholar] [CrossRef]

- Burdiek, B. Generation of optimum test stimuli for nonlinear analog circuits using nonlinear programming and time-domain sensitivities. In Proceedings of the Design, Automation and Test in Europe, Munich, Germany, 13–16 March 2001; pp. 603–608. [Google Scholar] [CrossRef]

- Chatterjee, S.; Chatterjee, A. Test generation based diagnosis of device parameters for analog circuits. In Proceedings of the Design, Automation and Test in Europe, Munich, Germany, 13–16 March 2001; pp. 596–602. [Google Scholar] [CrossRef]

- Spinks, S.J.; Chalk, C.D.; Bell, I.M.; Zwolinski, M. Generation and verification of tests for analog circuits subject to process parameter deviations. J. Electron. Test. 2004, 20, 11–23. [Google Scholar] [CrossRef]

- Robotycki, A.; Zielonko, R. Fault diagnosis of analog piecewise linear circuits based on homotopy. IEEE Trans. Instrum. Meas. 2002, 51, 876–881. [Google Scholar] [CrossRef]

- Tadeusiewicz, M.; Hałgas, S.; Korzybski, M. Multiple catastrophic fault diagnosis of analog circuits considering the component tolerances. Int. J. Circuit Theory Appl. 2012, 40, 1041–1052. [Google Scholar] [CrossRef]

- Tan, Y.; He, Y.; Cui, C.; Qiu, G. A novel method for analog fault diagnosis based on neural networks and genetic algorithms. IEEE Trans. Instrum. Meas. 2008, 57, 2631–2639. [Google Scholar] [CrossRef]

- Grzechca, D.; Golonek, T.; Rutkowski, J. Analog fault AC dictionary creation—The fuzzy set approach. In Proceedings of the IEEE International Symposium on Circuits and Systems, Island of Kos, Greece, 21–24 May 2006; pp. 5744–5747. [Google Scholar] [CrossRef]

- Aminian, F.; Aminian, M. Fault diagnosis of nonlinear analog circuits using neural networks with wavelet and Fourier transforms as preprocessors. J. Electron. Test. 2001, 17, 471–481. [Google Scholar] [CrossRef]

- He, Y.; Tan, Y.; Sun, Y. A neural network approach for fault diagnosis of large-scale analogue circuits. In Proceedings of the IEEE International Symposium on Circuits and Systems, Phoenix-Scottsdale, AZ, USA, 26–29 May 2002; Volume 1, pp. 153–156. [Google Scholar] [CrossRef]

- Long, B.; Tian, S.; Wang, H. Feature vector selection method using Mahalanobis distance for diagnostics of analog circuits based on LS-SVM. J. Electron. Test. 2012, 28, 745–755. [Google Scholar] [CrossRef]

- Li, Y.; Zhang, R.; Guo, Y.; Huan, P.; Zhang, M. Nonlinear soft fault diagnosis of analog circuits based on RCCA-SVM. IEEE Access 2020, 8, 60951–60963. [Google Scholar] [CrossRef]

- Lei, H.; Qin, K. Greedy randomized adaptive search procedure for analog test point selection. Analog Integr. Circuits Signal Process. 2014, 79, 371–383. [Google Scholar] [CrossRef]

- Bilski, A.; Wojciechowski, J. Automatic parametric fault detection in complex analog systems based on a method of minimum node selection. Int. J. Appl. Math. Comput. Sci. 2016, 26, 655–668. [Google Scholar] [CrossRef]

- Gao, Y.; Yang, C.; Tian, S.; Chen, F. Entropy based test point evaluation and selection method for analog circuit fault diagnosis. Math. Probl. Eng. 2014, 2014, 259430. [Google Scholar] [CrossRef]

- Tang, X.; Xu, A.; Li, R.; Zhu, M.; Dai, J. Simulation-based diagnostic model for automatic testability analysis of analog circuits. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2018, 37, 1483–1493. [Google Scholar] [CrossRef]

- Yin, S. Nonlinear analog circuit diagnosis based on Volterra series and neural network. In Proceedings of the International Conference on Wireless Communications Networking and Mobile Computing, Chengdu, China, 23–25 September 2010; pp. 1–3. [Google Scholar] [CrossRef]

- Deng, Y.; Shi, Y.; Zhang, W. An approach to locate parametric faults in nonlinear analog circuits. IEEE Trans. Instrum. Meas. 2012, 61, 358–367. [Google Scholar] [CrossRef]

- Shi, Y.; Deng, Y.; Zhang, W. Diagnosis of incipient faults in weak nonlinear analog circuits. Circuits Syst. Signal Process. 2013, 32, 2151–2170. [Google Scholar] [CrossRef]

- Deng, Y.; Chai, G. Soft fault feature extraction in nonlinear analog circuit fault diagnosis. Circuits Syst. Signal Process. 2016, 35, 4220–4248. [Google Scholar] [CrossRef]

- Deng, Y.; Liu, N. Soft fault diagnosis in analog circuits based on bispectral models. J. Electron. Test. 2017, 33, 543–557. [Google Scholar] [CrossRef]

- Yuan, L.; He, Y.; Huang, J.; Sun, Y. A new neural-network-based fault diagnosis approach for analog circuits by using kurtosis and entropy as a preprocessor. IEEE Trans. Instrum. Meas. 2010, 59, 586–595. [Google Scholar] [CrossRef]

- Tadeusiewicz, M.; Hałgas, S. A new approach to multiple soft fault diagnosis of analog BJT and CMOS circuits. IEEE Trans. Instrum. Meas. 2015, 64, 2688–2695. [Google Scholar] [CrossRef]

- Tadeusiewicz, M.; Hałgas, S. Diagnosis of soft spot short defects in analog circuits considering the thermal behaviour of the chip. Metrol. Meas. Syst. 2016, 23, 239–250. [Google Scholar] [CrossRef][Green Version]

- Tadeusiewicz, M.; Hałgas, S. A Method for local parametric fault diagnosis of a broad class of analog integrated circuits. IEEE Trans. Instrum. Meas. 2018, 67, 328–337. [Google Scholar] [CrossRef]

- Tadeusiewicz, M.; Kuczynski, A.; Hałgas, S. Spot defect diagnosis in analog nonlinear circuits with possible multiple operating points. J. Electron. Test. 2015, 31, 491–502. [Google Scholar] [CrossRef]

- Sindia, S.; Singh, V.; Agrawal, V.D. Parametric fault diagnosis of nonlinear analog circuits using polynomial coefficients. In Proceedings of the International Conference on VLSI Design, Bangalore, India, 3–7 January 2010; pp. 288–293. [Google Scholar] [CrossRef]

- Sindia, S.; Agrawal, V.; Singh, V. Parametric fault testing of non-linear analog circuits based on polynomial and V-transform coefficients. J. Electron. Test. 2012, 28, 757–771. [Google Scholar] [CrossRef]

- Sindia, S.; Agrawal, V.D. High sensitivity test signatures for unconventional analog circuit test paradigms. In Proceedings of the IEEE International Test Conference, Anaheim, CA, USA, 6–13 September 2013; pp. 1–10. [Google Scholar] [CrossRef]

- Li, Y.; Zio, E.; Lu, N.; Wang, X.; Jiang, B. Joint distribution-based test selection for fault detection and isolation under multiple faults condition. IEEE Trans. Instrum. Meas. 2021, 70, 3504013. [Google Scholar] [CrossRef]

- Feng, H.; Li, G.; Yu, J.; Ma, X.; Wang, J. Analog circuit fault diagnosis based on enhanced Harris Hawks optimization algorithm with RBF neutral network. Eng. Rep. 2023, 5, e12634. [Google Scholar] [CrossRef]

- Cui, Y.; Shi, J.; Wang, Z. Analog circuit test point selection incorporating discretization-based fuzzification and extended fault dictionary to handle component tolerances. J. Electron. Test. 2016, 32, 661–679. [Google Scholar] [CrossRef]

- Zhang, J. Fault diagnosis of nonlinear analog circuit based on generalized frequency response function and LSSVM classifier fusion. Math. Probl. Eng. 2020, 2020, 8274570. [Google Scholar] [CrossRef]

- Hałgas, S. Multiple soft fault diagnosis of nonlinear circuits using the fault dictionary approach. Bull. Pol. Acad. Sci. Tech. Sci. 2008, 56, 53–57. [Google Scholar]

- Vassios, V.D.; Hatzopoulos, A.T.; Papakostas, D.K. Improved fault detection of analog circuits by utilizing the fundamental RMS of the supply current fluctuation. In Proceedings of the International Conference on Modern Circuits and Systems Technologies, Athens, Greece, 28–30 June 2023; pp. 1–6. [Google Scholar] [CrossRef]

- Vassios, V.D.; Hatzopoulos, A.; Intzes, I.G.; Papakostas, D.K. Parametric fault detection of analog circuits by utilizing the fundamental RMS of the supply current fluctuation. In Proceedings of the International Conference on Modern Circuits and Systems Technologies, Sofia, Bulgaria, 26–28 June 2024; pp. 1–4. [Google Scholar] [CrossRef]

- Vassios, V.D.; Hatzopoulos, A.T.; Intzes, I.G.; Tsiakmakis, K.; Papakostas, D.K. A self-trained, low-complexity method for detecting faults in analog circuits. IEEE Trans. Instrum. Meas. 2025, 74, 3510813. [Google Scholar] [CrossRef]

- Yang, C.; Tian, S.; Liu, Z.; Huang, J.; Chen, F. Fault modeling on complex plane and tolerance handling methods for analog circuits. IEEE Trans. Instrum. Meas. 2013, 62, 2730–2738. [Google Scholar] [CrossRef]

- Amaral, T.G.; Pires, V.F.; Foito, D.; Cordeiro, A.; Rocha, J.I.; Chaves, M.; Pires, A.J.; Martins, J.F. A fault detection and diagnosis method based on the currents entropy indexes for the SRM drive with a fault tolerant multilevel converter. IEEE Trans. Ind. Appl. 2024, 60, 520–531. [Google Scholar] [CrossRef]

- Tadeusiewicz, M.; Hałgas, S.; Korzybski, M. An algorithm for soft-fault diagnosis of linear and nonlinear circuits. IEEE Trans. Circ. Syst. I Fundam. Theory Appl. 2002, 49, 1648–1653. [Google Scholar] [CrossRef]

- Tadeusiewicz, M.; Hałgas, S. Multiple soft fault diagnosis of BJT circuits. Metrol. Meas. Syst. 2014, 21, 663–674. [Google Scholar] [CrossRef]

- Tadeusiewicz, M.; Hałgas, S. A fault verification method for testing of analogue electronic circuits. Metrol. Meas. Syst. 2018, 25, 331–346. [Google Scholar] [CrossRef]

- Tadeusiewicz, M.; Hałgas, S. Integer algorithm: A useful tool for fault diagnosis of analog circuits. Circ. Syst. Signal Process. 2023, 42, 5121–5141. [Google Scholar] [CrossRef]

- Shahbazi, M.; Jamshidpour, E.; Poure, P.; Saadate, S.; Zolghadri, M.R. Open- and short-circuit switch fault diagnosis for nonisolated DC-DC converters using field programmable gate array. IEEE Trans. Ind. Electron. 2013, 60, 4136–4146. [Google Scholar] [CrossRef]

- Cardoso, A.; Bento, F. Diagnostics and fault tolerance in DC-DC converters and related industrial electronics technologies. Electronics 2023, 12, 2341. [Google Scholar] [CrossRef]

- Fontana, G.; Luchetta, A.; Manetti, S.; Piccirilli, M.C. A testability measure for DC-excited periodically switched networks with applications to DC-DC converters. IEEE Trans. Instrum. Meas. 2016, 65, 2321–2341. [Google Scholar] [CrossRef]

- Aizenberg, I.; Bindi, M.; Grasso, F.; Luchetta, A.; Manetti, S.; Piccirilli, M. Testability analysis in neural network based fault diagnosis of DC-DC converter. In Proceedings of the International Forum on Research and Technology for Society and Industry, Florence, Italy, 9–12 September 2019; pp. 265–268. [Google Scholar] [CrossRef]

- Bindi, M.; Piccirilli, M.C.; Luchetta, A.; Grasso, F.; Manetti, S. Testability evaluation in time-variant circuits: A new graphical method. Electronics 2022, 11, 1589. [Google Scholar] [CrossRef]

- Bindi, M.; Corti, F.; Grasso, F.; Luchetta, A.; Manetti, S.; Piccirilli, M.C.; Reatti, A. Failure prevention in DC-DC converters: Theoretical approach and experimental application on a Zeta converter. IEEE Trans. Ind. Electron. 2023, 70, 930–939. [Google Scholar] [CrossRef]

- Pazouki, E.; Abreu-Garcia, J.; Sozer, Y. Fault diagnosis method for DC-DC converters based on the inductor current emulator. In Proceedings of the IEEE Energy Conversion Congress and Exposition, Milwaukee, WI, USA, 18–22 September 2016; pp. 1–6. [Google Scholar] [CrossRef]

- Su, Q.; Wang, Z.; Xu, J.; Li, C.; Li, J. Fault detection for DC-DC converters using adaptive parameter identification. J. Frankl. Inst. 2022, 359, 5778–5797. [Google Scholar] [CrossRef]

- Han, W.; Cheng, L.; Han, W.; Yu, C.; Yin, Z.; Hao, Z.; Zhu, J. Incipient fault diagnosis for DC-DC converter based on multi-dimensional feature fusion. IEEE Access 2023, 11, 58822–58834. [Google Scholar] [CrossRef]

- Han, W.; Cheng, L.; Han, W.; Yu, C.; Hao, Z.; Yin, Z. Soft fault diagnosis for DC-DC converter based on improved ResNet-50. IEEE Access 2023, 11, 81157–81168. [Google Scholar] [CrossRef]

- Jia, Z.; Liu, Z.; Vong, C.M.; Wang, S.; Cai, Y. DC-DC buck circuit fault diagnosis with insufficient state data based on deep model and transfer strategy. Expert Syst. Appl. 2023, 213, 118918. [Google Scholar] [CrossRef]

- Ke, L.; Hu, G.; Yang, Y.; Liu, Y. Fault diagnosis for modular multilevel converter switching devices via multimodal attention fusion. IEEE Access 2023, 11, 135035–135048. [Google Scholar] [CrossRef]

- Li, Z.B.; Feng, X.Y.; Wang, L.; Xie, Y.C. DC-DC circuit fault diagnosis based on GWO optimization of 1DCNN-GRU network hyperparameters. Energy Rep. 2023, 9, 536–548. [Google Scholar] [CrossRef]

- Miao, J.; Liu, Y.; Yin, Q.; Zhang, G.; Yuan, Y. Research on the influence of signal sampling frequency on soft fault diagnosis accuracy of DC/DC converters. CPSS Trans. Power Electron. Appl. 2023, 8, 33–41. [Google Scholar] [CrossRef]

- Khater, F.; Aibeche, A.; Fellag, S.A.; Doghmane, M.Z.; Akroum, H. Failure identification and isolation of DC-DC boost converter using a sliding mode controller and adaptive threshold. Diagnostyka 2024, 25, 2024303. [Google Scholar] [CrossRef]

- Khan, S.S.; Wen, H. A comprehensive review of fault diagnosis and tolerant control in DC-DC converters for DC microgrids. IEEE Access 2021, 9, 80100–80127. [Google Scholar] [CrossRef]

- Xiao, Q.; Jin, Y.; Jia, H.; Tang, Y.; Cupertino, A.F.; Mu, Y.; Teodorescu, R.; Blaabjerg, F.; Pou, J. Review of fault diagnosis and fault-tolerant control methods of the modular multilevel converter under submodule failure. IEEE Trans. Power Electron. 2023, 38, 12059–12077. [Google Scholar] [CrossRef]

- ICAP4. Working with Model Libraries; Intusoft: San Pedro, CA, USA, 2000. [Google Scholar]

- IsSPICE4 Users Guides; Rev 04/08; Intusoft: Carson, CA, USA, 2008; Volume 1,2.

- Hałgas, S. Diagnosis of analog circuits: The problem of ambiguity of test equation solutions. Electronics 2024, 13, 684. [Google Scholar] [CrossRef]

| Period | Key Research Developments and Methodologies |

|---|---|

| 1970s–1980s | Analytical, topology, and circuit-equation-based methods [24]; sensitivity analysis; linearization of nonlinear circuits, PWL approach [40]; emergence of computer simulation; creation of early fault dictionaries [7], early parametric fault modeling to handle soft faults; decomposition methods [41]. |

| 1990s | Development of decomposition methods [42]; verification methods [43]; test point selection foundation [17,18]; large change sensitivity [44,45]; introduction of neural networks and wavelet transforms [46,47,48,49]; considering multiple operating points with PWL [26]. |

| 2000s | Test signal optimization [50,51,52,53]; homotopy methods [54]; adaptation of optimization methods [55] and data-driven methods, such as genetic algorithms [56] and fuzzy logic [57]; progress in automated feature extraction [58,59]. |

| 2010s | Use of SVMs for fault classification [60,61]; metaheuristic algorithms (GRASP [62], tabu search [63]); sophisticated graph methods [20,64]; integration of hybrid model-based and data-driven frameworks [20,63,65]; use of time-frequency and multi-domain analysis [61]; the Volterra series [8,66,67,68,69,70]; statistical models nd probabilistic models [2,8,61,68,69,71]; finding multiple solutions of test equations using homotopy-based methods [72,73,74,75]; polynomial models [76,77,78]. |

| 2020s–Present | Expansion of machine learning and deep learning (deep joint distribution [79], GAN, autoencoders [13], and wavelet scattering methods [4]); hybrid data-driven solution [4,79,80]. |

| Method | Domain/Representative Techniques | Strenghts | Drawbacks |

|---|---|---|---|

| [7] | DC, small signal AC/Fault dictionary | Utilizing fault history; stimuli and test points selection | Dependence on the engineer’s experience; single hard faults |

| [46,47,48] | DC/Fault dictionary; ANN | Using information channel–based method to select measurements; Hamming code outputs of ANN | Single hard faults |

| [49] | AC/Fault dictionary; ANN; linear regression | ANN acting as autoassociators; gradual faults | Limited single fault classes |

| [44,45] | DC, small signal AC/Fault dictionary; PWL models; Katzenelson’s algorithm | Extension of large change sensitivity to nonlinear circuits; soft and hard faults | Single faults; simple illustrative examples |

| [58] | Time/ANN; PCA | Utilizing wavelet and Fourier transform; hard and soft faults | Single faults; Limited fault classes; soft faults with presumed values |

| [59] | DC/BPNN | BPNN for subcircuits; hard and soft faults | Single faults; Limited fault classes; no guidelines for splitting into subcircuits |

| [57] | AC/Fuzzy expert system | Utilizing the sparsity of the sensitivity matrix | Single faults; fault detection only |

| [56] | DC, small signal AC/ANN; PWL models | Unified space characteristic of up to triple faults in linear circuits; multiple soft and hard faults | No in-depth coverage of nonlinear circuits |

| [83] | DC/Fault dictionary; section-wise PWL | Identification and estimation of multiple soft faults; concise mathematical description of n–dimensional surfaces | Necessity of solving nonlinear equations in identification process |

| [71] | Time/BPNN; statistical features | Application of higher-order statistical methods; soft and hard faults | Limited fault classes; assumed specific soft faults (% of nominal value); simple illustrative nonlinear example |

| [66] | Time/BPNN; Volterra series | Ranges of soft faults | Limited single fault classes; simple illustrative nonlinear example |

| [67] | Time/Fault dictionary; subband Volterra series; coherence | Hard and soft faults | Limited single fault classes and a few double faults; predefined values of soft faults |

| [60] | Time/Multiple LSSVM; Mahalanobis distance | Wavelet types, wavelet decomposition level, and normalization discussion; hard and soft faults; wide ranges of soft faults | Limited single fault classes; simple illustrative nonlinear example |

| [55] | DC/Fault dictionary; GA; linear programming | Multiple hard faults | Finite list of preselected faults; using simplex method in identification |

| [8,68] | Time/HMM; subband Volterra series; fractional correlation | Incipient faults; ranges of incipient faults | Limited single fault classes and a few double faults |

| [76,77,78] | Time/Fault dictionary; polynomial and V-transform coefficients | Effective detection of faults; simple procedure; single soft faults | Limited single fault classes; necessity of estimating the circuit’s response; fault detection only |

| [87] | AC/Fault dictionary; fault modeling on complex plane | Graphic visualization of signatures; wide range of soft faults | Limited single fault classes |

| [75] | DC/Fault dictionary; linear complementarity approach | Considering multiple operating points; local spot faults | Finite list of preselected faults; necessity of tracing and storing parametric characteristics; hybrid circuit description |

| [69,70] | Time/HMM; subband Volterra series; Wigner-Ville distribution; bispectral models | Hard and soft faults; ranges of soft faults | Limited single fault classes and a few double faults; narrow soft fault ranges |

| [2] | Time/Fault dictionary; high order moment fractional transform | Incipient faults belonging to predefined ranges; helpful to deal with aliasing | Limited single fault classes and a few double faults; high computational complexity |

| [82] | Time/Generalized frequency response function; LSSVM | Using fusion algorithm; soft faults | Preselected single faults (% of nominal value); simple illustrative nonlinear example |

| [61] | Time/Canonical correlation analysis; PCA; SVM; ReliefF algorithm | Fusion algorithm from statistical, time and frequency domain; soft faults | Limited single fault classes; Preselected single faults (% of nominal value) |

| [4] | Time/Learnable wavelet scattering networks; GA; SVM | Usefulness in diagnosing industrial faults; wide range of soft faults; one class for each parameter | Limited single fault classes and a few double faults |

| [80] | Time/RBF ANN; Enhanced Harris Hawks Optimization (EHHO) | Weights and thresholds of ANN optimized using EHHO; soft fault | Limited number of single faults |

| [88] | Time/Image analysis; entropy-based symmetry/asymmetry indexes | Detection and diagnosis for power semiconductor fault; multiple hard faults | Specific application–multilevel converters |

| [13] | Time/Generative adversarial network | Spatial Fourier convolution to enhance

detection performance; intermittent faults; concept of intermittent faults implementation | Resistive faults with preset values; limited number and location of faults |

| [84,85,86] | Time/Fault dictionary; Under/Over Voltage (UOV) algorithm | Monitoring of the fluctuations of the power supply current; low-complexity; hard/soft/incipient faults; large number of considered faults | Fault detection only |

| Method | Domain/Representative Techniques | Strenghts | Drawbacks |

|---|---|---|---|

| [41] | DC/Nodal decomposition; checking the consistency of KCL in the decomposed circuit; nearest neighbor rule | Large circuits; module-level fault diagnosis; necessary and almost sufficient conditions for subnetworks to be fault-free; fault verification to locate faults in faulty blocks; multiple soft faults; hard faults | Measurement nodes must include decomposition nodes; complex test procedure; lack of general decomposition procedure |

| [42] | Time/Decomposition method; QR factorization; sensitivity analysis | Large-scale analog and mixed-mode circuits; study the impact of modeling errors; subsystems analyzed using methods best suited to type of subcircuit; test equations prepared on subnetwork level; parameter identification problem locally solved; hard and soft faults | Internal sensitivities must be calculated before evaluating the test matrix; all decomposition nodes are accessed for measurements; only linear example |

| [26], ch.4 | DC/PWL approach | Consideration of polarization shift in nonlinear devices; diagnosis of nonlinear circuits with multiple operating points; reduced tableau equation; k-fault testability condition; soft faults | Simple semiconductor device models; two/three–segment PWL approximation |

| [43] | DC/PWL approach; verification method | Definition of a correlation indicator for individual faults and operating point consistence coefficient; two stage approach; tableau equation; soft faults | Single faults; access to many nodes required |

| [54] | DC/PWL approach; homotopy concept; verification method | Small number of hypothesis verifications; soft faults; fault localization and identification in one stage | Simple illustrative example; single faults |

| [89] | DC/linear–programming concept; verification method | Only phase one of the simplex method applies to checking the existence of a feasible solution; multiple soft faults | Access to many nodes required; faults up to ±20% of nominal value; fault localization only |

| [90] | DC/Block relaxation method; Newton–Raphson method | Multiple solutions of nonlinear test equation; multiple soft faults | BJT circuits; only one transistor considered as potentially faulty; large number of equations |

| [72] | DC/Extended systematic search method; verification method | Multiple soft faults; multiple solutions of nonlinear test equation; broad class of analog circuits; intricate transistors models | Time-consuming calculation process; complex sensitivity analyses required |

| [16] | DC/Homotopy-simplicial algorithm; restart procedure | Local and global multiple soft faults; multiple solutions of nonlinear test equation; broad class of analog circuits; intricate transistors models | Closed homotopy loop prevents continuation of calculations; In some cases homotopy path can be infinite spiral or bifurcation curve, time-consuming calculation process |

| [73] | DC/Optimization procedure based on the Fibonacci method; verification method | Consideration of chip thermal behavior; soft spot short defects | Single defects only; |

| [74] | DC/Homotopy concept; sensitivity analysis; verification method | Multiple soft faults; efficient iterative method; broad class of analog circuits; intricate transistors models | Small and middle-size circuits; complex sensitivity analyses required |

| [91] | DC/Powell’s minimization method; verification method | Multiple soft faults; no sensitivity analysis required | Effectiveness strongly depends on measurement accuracy; difficult to implement and less efficient for CMOS circuits designed in a sub-micrometre technology |

| [92] | DC/Integer algorithm; homotopy simplicial approach; verification method | Multiple soft faults; optimization method for constrained variables to initial simplex generation | Integer algorithm requires more simplices than the standard simplicial algorithm; method fails if divergence or slow convergence in DC analysis occurs |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hałgas, S. Challenges in Fault Diagnosis of Nonlinear Circuits. Electronics 2025, 14, 4427. https://doi.org/10.3390/electronics14224427

Hałgas S. Challenges in Fault Diagnosis of Nonlinear Circuits. Electronics. 2025; 14(22):4427. https://doi.org/10.3390/electronics14224427

Chicago/Turabian StyleHałgas, Stanisław. 2025. "Challenges in Fault Diagnosis of Nonlinear Circuits" Electronics 14, no. 22: 4427. https://doi.org/10.3390/electronics14224427

APA StyleHałgas, S. (2025). Challenges in Fault Diagnosis of Nonlinear Circuits. Electronics, 14(22), 4427. https://doi.org/10.3390/electronics14224427